# **Contents**

| Page | Section  | Title                                                                     |

|------|----------|---------------------------------------------------------------------------|

| 4    | 1.       | Introduction                                                              |

| 4    | 1.1.     | Features of the DRD 3515A                                                 |

| 4    | 1.2.     | System Overview                                                           |

|      |          |                                                                           |

| 6    | 2.       | Functional Overview                                                       |

| 6    | 2.1.     | The WorldSpace Signal                                                     |

| 6    | 2.2.     | General Signal Flow                                                       |

| 6    | 2.3.     | Power Supply Concept                                                      |

| 6    | 2.3.1.   | Digital Power Supply                                                      |

| 6    | 2.3.2.   | Analog Power Supply of the IF Section and the Oscillator                  |

| 6    | 2.3.3.   | Performance of the Quartz Oscillator                                      |

| 6    | 2.3.4.   | Analog Power Supplies for the Audio Parts                                 |

| 7    | 2.4.     | IF Frontend                                                               |

| 8    | 2.5.     | QPSK Demodulator                                                          |

| 8    | 2.6.     | Frame Synchronization and Demultiplexing                                  |

| 8    | 2.6.1.   | Synchronization to MFP and PRCP                                           |

| 8    | 2.6.2.   | TSCC Acquisition                                                          |

| 9    | 2.6.3.   | TDM Demultiplexing: Selection of Broadcast Channel                        |

| 9    | 2.7.     | Viterbi and Reed-Solomon Decoding                                         |

| 9    | 2.8.     | Broadcast Channel Output and Selection of an Additional Service Component |

| 9    | 2.9.     | Analog Audio                                                              |

| 12   | 3.       | Modes of Operation                                                        |

| 12   | 3.1.     | Interactions Between DRD 3515A and MAS 3506D                              |

| 12   | 3.2.     | Clock Concept                                                             |

| 12   | 3.3.     | Operation and Stand-By Modes                                              |

| 12   | 3.4.     | Power Up Sequence (2 Battery Operation)                                   |

| 12   | 3.5.     | Power Up Sequence (Operation Without DC/DC Converter)                     |

| 13   | 3.6.     | Power Down Sequence                                                       |

| 13   | 3.6.1.   | Full WorldSpace Operation                                                 |

| 13   | 3.6.2.   | Audio Amplifier Operation                                                 |

| 13   | 3.6.3.   | WorldSpace Operation Only                                                 |

| 13   | 3.6.4.   | Off                                                                       |

| 10   | 0.0.4.   | OII                                                                       |

| 15   | 4.       | Serial Control Interface                                                  |

| 15   | 4.1.     | I <sup>2</sup> C-Bus Interface                                            |

| 15   | 4.2.     | Register Overview                                                         |

| 18   | 4.3.     | Detailed Description of the Registers                                     |

| 18   | 4.3.1.   | Main Configuration Register GLB_CONFIG                                    |

| 19   | 4.3.2.   | IF Input Configuration                                                    |

| 19   | 4.3.3.   | IF Input: Analog Automatic Gain Control                                   |

| 19   | 4.3.4.   | QPSK Demodulator Carrier Frequency Offset                                 |

| 20   | 4.3.4.1. | QPSK Demodulator Receiving Quality Indicator                              |

| 20   | 4.3.5.   | QPSK Demodulator Timing Recovery Symbol Time.                             |

| 21   | 4.3.6.   | Analog Audio Gain                                                         |

| 22   | 4.4.     | Registers for Advanced Features                                           |

| 23   | 4.5.     | FEC Registers                                                             |

| 23   | 4.5.1.   | Conventions for the Command Description                                   |

|      |          | •                                                                         |

# Contents, continued

| Page | Section  | Title                                                   |

|------|----------|---------------------------------------------------------|

| 23   | 4.5.2.   | Detailed DRD 3515A Command Syntax                       |

| 23   | 4.5.2.1. | Idle Mode                                               |

| 24   | 4.5.2.2. | TSCC Mode                                               |

| 24   | 4.5.2.3. | BC Mode                                                 |

| 24   | 4.5.2.4. | MEM Read                                                |

| 24   | 4.5.2.5. | MEM Write                                               |

| 24   | 4.5.2.6. | Default Read                                            |

| 25   | 4.5.3.   | Memory Table                                            |

| 26   | 4.5.4.   | Standard Memory Cells                                   |

| 26   | 4.5.4.1. | Mute                                                    |

| 26   | 4.5.4.2. | Test Mode for BER Measurements                          |

| 26   | 4.5.4.3. | VMinDist                                                |

| 27   | 4.5.4.4. | Reed-Solomon Error Counter                              |

| 27   | 4.5.4.5. | Service Component Output of the DRD 3515A               |

| 27   | 4.5.4.6. | TSCC Information                                        |

| 27   | 4.5.5.   | Encryption Related Memory Cells                         |

| 28   | 5.       | Interface Specifications                                |

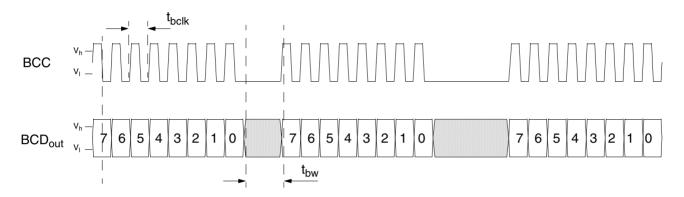

| 28   | 5.1.     | Broadcast Channel (BC) Interface                        |

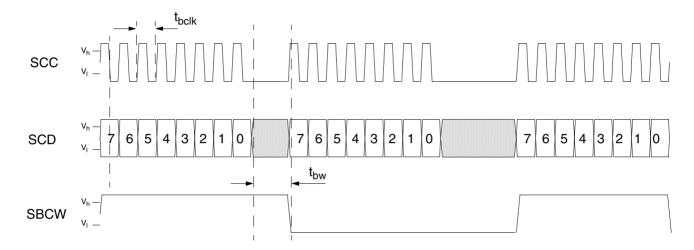

| 29   | 5.2.     | Service Component Interface                             |

| 29   | 5.3.     | Serial Audio Data Interface                             |

| 31   | 6.       | Specifications                                          |

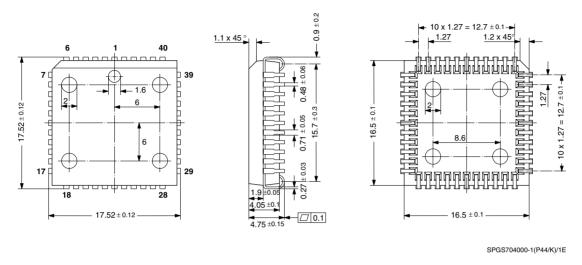

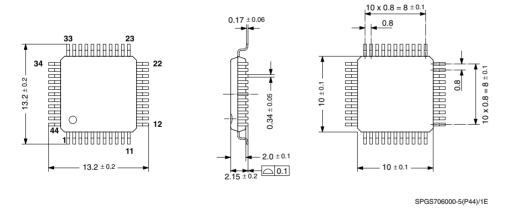

| 31   | 6.1.     | Outline Dimensions                                      |

| 32   | 6.2.     | Pin Connections and Short Descriptions                  |

| 34   | 6.3.     | Pin Descriptions                                        |

| 34   | 6.3.1.   | Power Supply Pins                                       |

| 34   | 6.3.1.1. | IF-Related Pins                                         |

| 34   | 6.3.1.2. | Analog Audio Pins                                       |

| 35   | 6.3.1.3. | Oscillator and Clock Pins                               |

| 35   | 6.3.1.4. | Digital Interface Section                               |

| 35   | 6.3.1.5. | Other Pins                                              |

| 38   | 6.4.     | Electrical Characteristics                              |

| 38   | 6.4.1.   | Absolute Maximum Ratings                                |

| 39   | 6.4.2.   | Recommended Operating Conditions                        |

| 41   | 6.4.3.   | Extended Operating Range                                |

| 42   | 6.4.4.   | Characteristics                                         |

| 48   | 7.       | Application Notes                                       |

| 48   | 7.1.     | Line Output Details                                     |

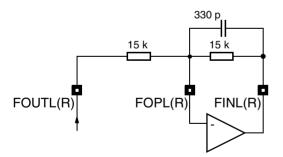

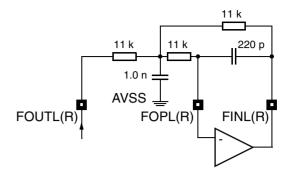

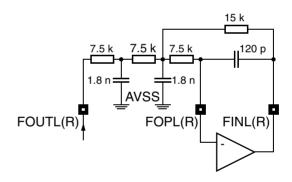

| 48   | 7.2.     | Recommended Low Pass Filters for Analog Outputs         |

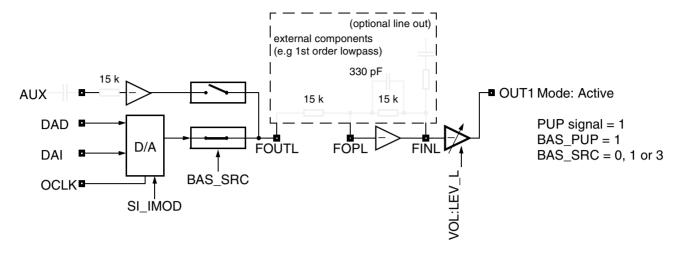

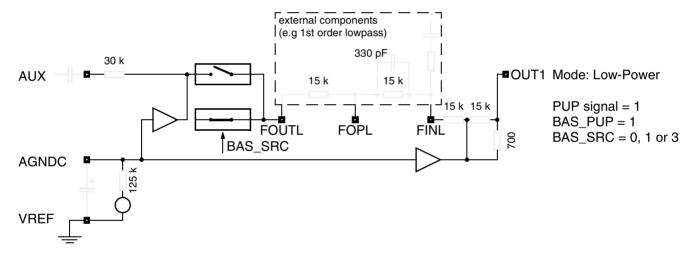

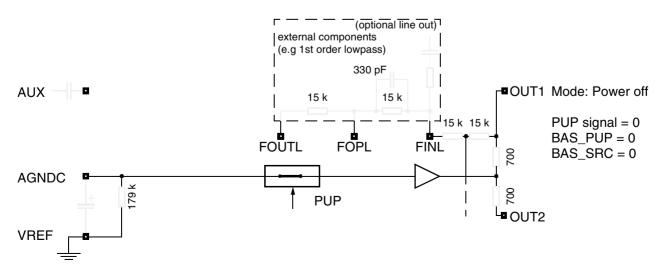

| 49   | 7.3.     | Equivalent Output Circuitry in 3 Different Analog Modes |

| 50   | 8.       | Data Sheet History                                      |

# StarMan<sup>™</sup> Channel Decoder for a WorldSpace<sup>™</sup> TDM Downlink Carrier

### 1. Introduction

The WorldSpace System is a satellite based digital radio service for direct to home transmission of digital radio programs to WorldSpace radios. The coverage areas of this service are Africa, South America, and parts of Asia.

The DRD 3515A is the part of Micronas' StarMan chipset for demodulating and decoding the signals from the WorldSpace satellites. It performs channel demodulation, error correction, demultiplexing and the separation of one Broadcast Channel (BC). The DRD 3515A additionally provides an embedded stereo D/A converter and an amplifier for headphones or a small loudspeaker. Together with the audio decoder MAS 3506D, a micro controller and an L-band tuner, the DRD 3515A allows the design of compact and low cost WorldSpace receivers.

# 1.1. Features of the DRD 3515A

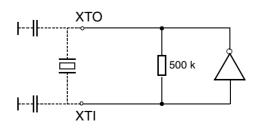

- Embedded 14.725 MHz crystal oscillator

- Two-battery cell (with DC/DC converter on the MAS 3506D) or three battery cell operation supported

- IF input with AGC and RSSI

- Digital I/Q splitting

- Fast synchronization strategy

- Crystal frequency offset compensation

- Embedded signal quality indication

- Demodulator status observable

- Stored TSCC information available in BC-mode

- Support of ES1 WorldSpace decrypting algorithm

- Full Broadcast Channel (BC) output available

- Optional serial output of one selected Service Component (SC)

- I<sup>2</sup>S input interface for decoded MPEG audio signals

- Stereo D/A converter: S/N > 90 dB, THD < 0.01 %

- Two auxiliary analog stereo inputs

- Baseband audio source selector matrix

- Stereo line output, amplifier for stereo headphones or small mono speaker with click reduction

- Various low power and stand-by functions

- I<sup>2</sup>C controller interface

## 1.2. System Overview

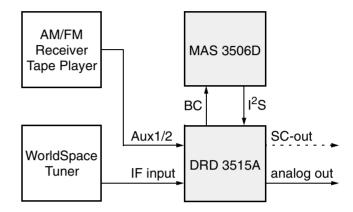

The Micronas StarMan chip set consists of the channel decoder DRD 3515A and the MPEG Layer 3 audio decoder MAS 3506D. All essential analog and digital building blocks for WorldSpace reception are provided on the Micronas chipset. Together with an L-band tuner and an appropriate controller this set builds a complete StarMan radio receiver.

Fig. 1-1: Standard application of StarMan chipset

Since the DRD 3515A also contains an audio amplifier for headphone or small loudspeaker operation, only a minimum of external components are necessary. The additional inputs for analog signals (e.g. conventional AM/FM receiver, tape etc.) make the amplifier accessible to these audio sources and thus considerably simplify the design of complete radio receivers.

The analog audio output of the WorldSpace signal can be supplied to an external stereo amplifier for higher power output. Also a digital audio signal in standard I<sup>2</sup>S format is provided for high end applications that may require an external D/A converter.

The complete WorldSpace Broadcast Channel (BC) is available as a serial output signal from the DRD 3515A and provides full access to all WorldSpace data by additional decoder modules. The additional Service Component (SC) output of the DRD 3515A may be useful in applications where a data and an audio channel are transmitted simultaneously. In this case the data component is directed to the SC output. The performance requirements for the data decoders are considerably lower for the Service Component because the demultiplexing of the BC-channel is already done inside the DRD 3515A. This function is independent from the audio Service Component extraction in the MAS 3506D.

Service Control Header data are available via I<sup>2</sup>C controller interface from the MAS 3506D.

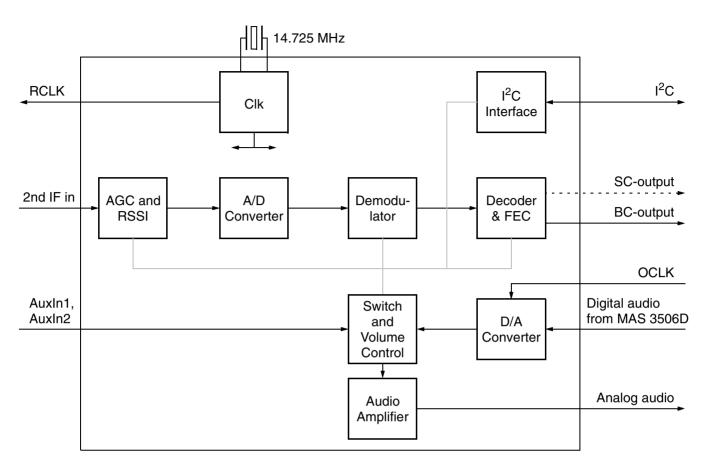

Fig. 1-2: Block diagram of the DRD 3515A

### 2. Functional Overview

# 2.1. The WorldSpace Signal

The WorldSpace satellite downlink carriers are QPSK-modulated. Every carrier transports a time division multiplex (TDM) signal with an overall gross bit rate of 3.68 Mbit/s. It consists of 96 Prime Rate Channels (PRC) with a gross (net) bit rate of 37.777 (16) kbit/s each and a frame header with the Master Frame Preamble (MFP, synchronization word) and the Time Slot Control Channel (TSCC, composition information).

One to eight of the Prime Rate Channels can be combined to yield one Broadcast Channels with a net bit rate of (1 ... 8) times 16 kbit/s (i.e. 16 ... 128 kbit/s).

The TDM data stream is assembled from all 96 Prime Rate Channels either at the main uplink station (transparent mode) or on the satellite by an on board baseband processor (processed mode). For the latter mode each radio station or service provider may separately uplink its own Broadcast Channel via FDMA (frequency division multiplex access).

Depending on the number of combined Prime Rate Channels each Broadcast Channel can be subdivided into one or more Service Components that may contain data services or compressed audio data.

# 2.2. General Signal Flow

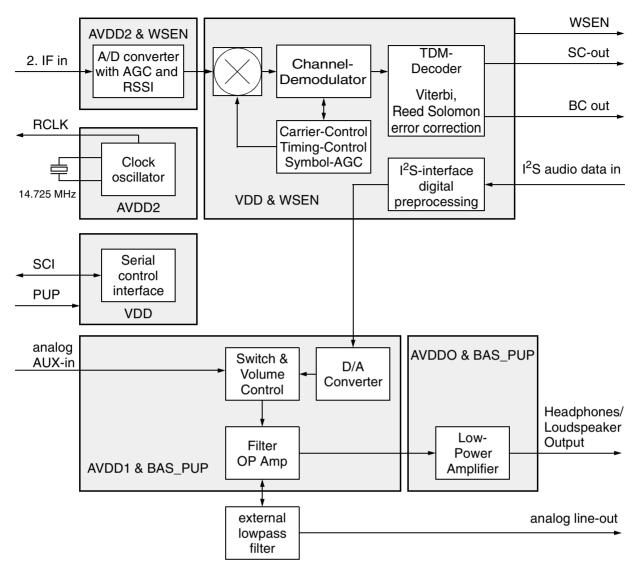

The general signal flow within the DRD 3515A is depicted in Figure 2–1. The shaded regions demonstrate the membership of building blocks to different power supply areas. These areas will be selected or deselected depending on the various operating modes of the device.

The input signal of the DRD 3515A is one 3.68 Mb/s QPSK modulated WorldSpace TDM downlink carrier, which is down converted to an IF center frequency of 1.84 MHz. After a digitally controlled analog AGC, the A/D-conversion is performed.

Carrier and signal tracking, I/Q-splitting, and QPSK-demodulation are established digitally.

The information about the required Prime Rate Channels for the chosen Broadcast Channel is identified by the external controller and transmitted to the TDM demultiplexer. The required PRCs are then extracted from the TDM data stream by the demultiplexer. Error correction is done by a Viterbi and a Reed-Solomon decoder. The Service Components contained in this Broadcast Channel may carry compressed audio signals compliant with the MPEG 2 Layer 3 standard or data services.

The MAS 3506D selects the wanted audio Service Component and decompresses the Layer 3 encoded audio. The digital audio signal is transmitted back to the DRD 3515A via an I<sup>2</sup>S serial interface for D/A conversion and amplification in the analog baseband block.

### 2.3. Power Supply Concept

All building blocks are implemented in low power CMOS technology. Two basic modes of operation are possible, a two battery operation using the DC/DC converter of the MAS 3506D, and a direct operation on three batteries or a stabilized power supply.

The DRD 3515A has 5 power supply regions.

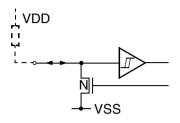

## 2.3.1. Digital Power Supply

The two digital sections (I<sup>2</sup>C interface and digital WorldSpace decoder blocks) are supplied via pin VDD. The interface part can be switched on via the pin PUP.

To activate the WorldSpace decoder parts the bit WSEN of the register GLB\_CNFG must be set in addition to the PUP signal. This will also cause the WSEN output pin to go to a "high" level.

# 2.3.2. Analog Power Supply of the IF Section and the Oscillator

The IF input section and the quartz oscillator are powered via pin AVDD2. While the clock oscillator is switched on by the PUP signal only, the IF input section needs the WSEN bit of GLB\_CNFG to be set in addition to PUP.

# 2.3.3. Performance of the Quartz Oscillator

If the tuner uses the quartz oscillator of the DRD 3515A as its master clock, it is highly recommended to use a well filtered supply voltage for the AVDD2 pin (e.g. a separate voltage stabilization) to avoid performance degradation of the oscillator due to power supply ripple.

# 2.3.4. Analog Power Supplies for the Audio Parts

The AVDD1 pin supplies the audio D/A converter, the analog switching and volume control parts. The AVDD0 pin supplies the audio amplifier. These parts can be enabled with the bit BAS\_PUP in register GLB CNFG.

Fig. 2–1: DRD 3515A power supply sections and necessary enabling signals. The PUP signal is required for all sections.

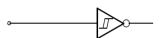

### 2.4. IF Frontend

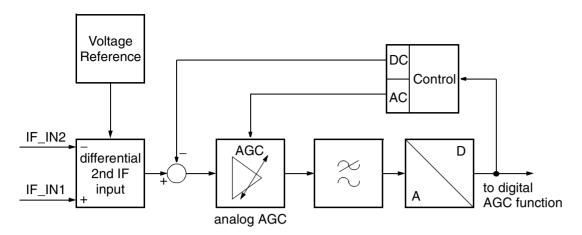

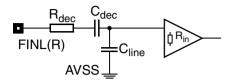

The 2nd IF input signal has a carrier frequency of 1.84 MHz and an amplitude between 15 mV and 500 mV. To use the full range of the A/D converter, a digitally controlled analog AGC and a DC offset compensation are used. The gain control leaves enough headroom for very noisy signals with high crestfactors. On the other hand the resolution of the A/D converter is high enough for the second AGC in the digital domain. The gain value of the analog AGC may be read by the micro controller to get the Received Signal Strength Indicator (RSSI, register DMD\_AAG\_AGC). The time constant of the control is designed to cope with different reception conditions and may be adjusted to situations like manual movement of the receiver or mobile operation.

The gain range of the analog AGC is 31 dB, this will cover all standard reception situations including handheld, mobile and home operation. In the case of very strong retransmission in the immediate neighborhood an additional AGC regulator should be provided in the L-band tuner circuit. A single 20 dB attenuation step is sufficient for this task. The controller should watch for a continuous IF input overflow via the DMD\_AAG\_AGC register and could then activate this additional attenuation.

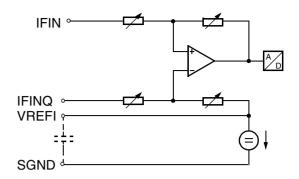

Fig. 2-2: Diagram of IF input section

### 2.5. QPSK Demodulator

The QPSK demodulator performs a digital I/Q splitting. A carrier frequency tracking loop and a symbol timing recovery loop are used for demodulation. The carrier tracking range covers carrier frequency offsets caused by crystal tolerances. Thus no carrier frequency feedback control to the tuner PLL is required. A second (pure digital) AGC controls the symbol amplitude for an optimal signal mapping for the subsequent error correction blocks. The phase uncertainty of QPSK modulation is compensated by evaluation of the Master Frame Preamble (MFP). The carrier recovery loop is optimized for operation with small C/N ratio. A fixed carrier frequency offset may be sent to the DRD 3515A after reset in order to compensate for a known frequency offset of the crystal. The quality of the QPSK demodulation may be obtained from the register DMD\_AGC\_RCVQU that displays the I/Q amplitude variance. This signal may be used to optimize the antenna pointing direction. All demodulation and synchronization parameters can be controlled via I<sup>2</sup>C bus.

## 2.6. Frame Synchronization and Demultiplexing

# 2.6.1. Synchronization to MFP and PRCP

The Master Frame Preamble (MFP) is used to synchronize the decoder to the frame of the incoming bitstream. The MFP-detector block additionally eliminates the 90° phase-ambiguity of the QPSK-signal. The MFP-detector has been designed to cope even with bad reception conditions.

The Prime Rate Channel Preambles (PRCP) identify the beginning of each of the 96 Prime Rate Channels (PRC).

For both the Master Frame Preamble detection and Prime Rate Channel Preamble (PRCP) detection dif-

ferent threshold values can be defined for the unsynchronized and synchronized state.

In order to minimize false alarms in the unsynchronized state the threshold value should be high. In the synchronized state though the threshold value should be lower to minimize misses. In this state false alarms are omitted by a windowing technique that only activates the detection circuit when the next preamble is expected. This technique allows to meet the rigid requirements of the WorldSpace specification.

The MFP/PRCP circuits are "synchronized" upon successful detection of the respective preambles. They return to the "unsynchronized" hunting state upon several misses of the respective preambles (see Table 4–13 on page 24).

In addition the MFP-detection returns to "unsynchronized" upon writing to register \$1B (synched threshold values), the PRCP-detection returns to "unsynchronized" upon writing to one of the 8 TDM-timeslot selection registers.

# 2.6.2. TSCC Acquisition

After initial synchronization an acquisition of the Time Slot Control Channel (TSCC) should be performed. The TSCC data will be error corrected and made available to the external controller. The TSCC contains information about all Broadcast Channels on the carrier and the time slots of the corresponding Prime Rate Channels (PRC). The TSCC data can be read out by the controller via the FEC data read register (FEC\_READ) immediately after they have been decoded. After one TSCC block is received, the DRD 3515A indicates the availability of the TSCC data at the SYNC output pin and in an FEC status register.

The TSCC acquisition is initiated after power-up and may be reinitiated via the FEC\_WRITE register at any

time. During TSCC acquisition the normal Broadcast data reception is inhibited (see Section 2.7. on page 9).

# 2.6.3. TDM Demultiplexing: Selection of Broadcast Channel

Depending on the read TSCC information the controller writes the Prime Rate Channel numbers for the wanted Broadcast Channel in ascending order into the corresponding registers of the DRD 3515A. Also the unused time slots have to be given an unique ID number; however, these unused slots must be disabled. The DRD 3515A must now be switched into the BC mode via register FEC\_WRITE. The demultiplexer takes the selected PRC time slots from the TDM data stream and passes their data to the subsequent forward error correction modules i.e. the Viterbi decoder and the Reed Solomon decoder.

The Service Control Header (SCH) is only available from the MAS 3506D.

# 2.7. Viterbi and Reed-Solomon Decoding

Forward error correction is done by an 1/2-rate Viterbi decoder followed by a Reed-Solomon decoder. These blocks are used either for Broadcast Channel data or for TSCC-data correction. Thus during acquisition of the TSCC normal Broadcast Channel reception is not possible. TSCC acquisition is usually only necessary after power-up. However, the TSCC information (194 bytes) is stored inside of the DRD 3515A and is available to the controller also in the Broadcast mode. This feature reduces the memory requirement for the system controller. The TSCC data will usually change only if the TDM data stream from the satellite is reconfigured.

The Viterbi decoder provides a signal quality information via the FEC\_WRITE/READ functions. This information may be used in addition to the RSSI (register DMD\_AAG\_AGC) or the QPSK demodulation quality (register DMD\_AGC\_RCVQU) for antenna orientation.

Via a flag accessible through the FEC\_WRITE/READ registers the Reed-Solomon decoder indicates whether the error correction was probably successful or failed due to a high input error rate.

# 2.8. Broadcast Channel Output and Selection of an Additional Service Component

The selected Broadcast Channel is sent via pins BCC and BCD to the MAS 3506D (input pins SIC and SID) for Service Component extraction and MPEG 2 Layer 3 audio decoding. The 2-wire BC-output may

also be used by external devices to process Broadcast Channels containing data other than audio.

In addition one Service Component can be selected and activated via the FEC\_WRITE command register. It is then sent to the 3 pin SC-output (SCC, SCD, SBCW). The additional word frame indication (SBCW) on the 3rd line simplifies the connection of optional data decoders. This SC output does not influence the selection of the audio Service Component in the MAS 3506D.

# 2.9. Analog Audio

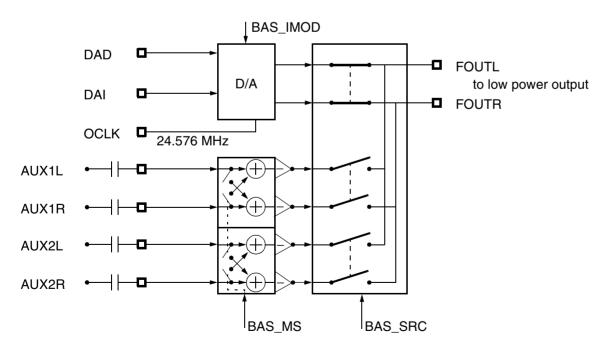

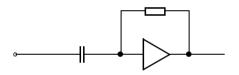

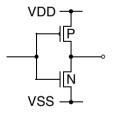

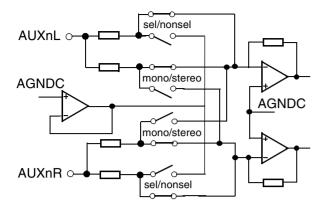

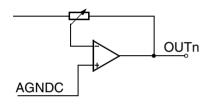

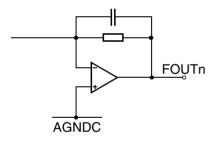

The backend of the DRD 3515A consists of a digital part that performs the D/A conversion of the World-Space audio signal, and an analog part with a signal switch matrix for additional auxiliary analog audio inputs, filter op amps, a line output, and two low power amplifiers for directly driving stereo headphones or a small monoaural loudspeaker, respectively.

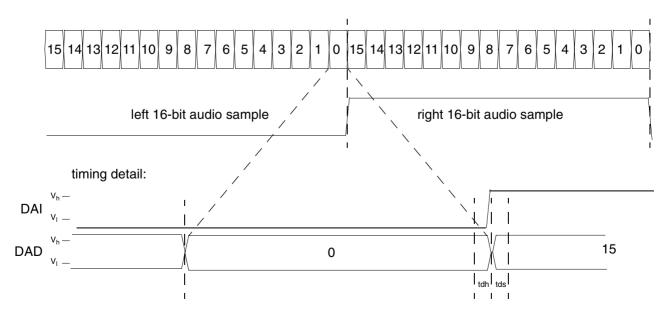

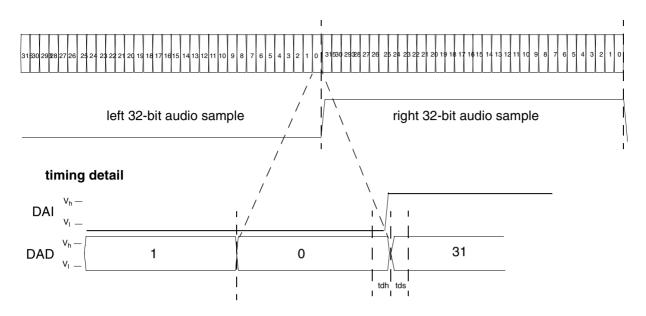

A digital input data signal from the MAS 3506D is passed to the D/A converter of the DRD 3515A in a 16 or 32-bit I<sup>2</sup>S-format. For high quality audio it is recommended to use the 32-bit mode of the I<sup>2</sup>S interface to make use of the full dynamic range provided by the Layer 3 audio transmission.

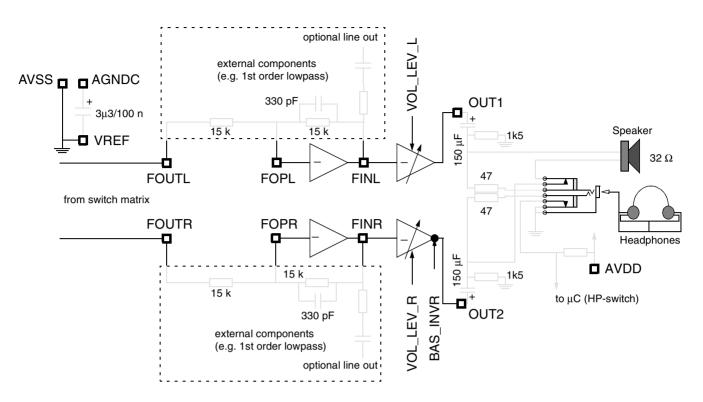

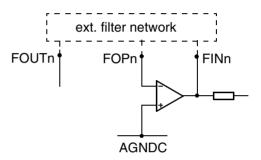

The D/A-converted signal passes a switch matrix, an analog volume control and a low power amplifier. In addition to the D/A converter, two external stereo signals AUX1 and AUX2 are connected to the switch matrix. The signal path is led over external pins FOUTL/R, FOPL/R and FINL/R to allow external filtering of the analog signals. The FINL/R pins are usable as line outputs (see Section 7.1. on page 48).

The low power amplifier output is provided at the OUT1 and OUT2 pins. If a loudspeaker is connected to these outputs the power amplifier for the right channel must be switched to inverse polarity. In order to optimize the available power the source of the two output amplifiers should be identical, i.e. a monoaural signal.

The stereo headphone requires external 47  $\Omega$  serial resistors in both channels.

A power-off mode for zero power consumption and a low power mode with a fast resume of normal operation is available to optimize battery operation. The 5 V option of the audio parts will result in higher output levels and a better S/N ratio.

The principle of the DRD 3515A baseband processing is shown in Figure 2–3 and Figure 2–4.

# **Audio Baseband Features**

- High quality stereo D/A-converter

- 2 auxiliary analog stereo input pairs

- Source selector switch

- Mono switch for aux-input pairs

- Op amp connections accessible for customizable lowpass filtering of the analog audio signals

- Stereo analog volume control with 93 dB volume range and mute function

- Integrated low power stereo amplifier

- Stereo headphone or mono loudspeaker operation

- Single ended operation with 3V or 5V power supply

- Power-down mode with fast resume of normal operation

- Click-reduction for power mode switching

Fig. 2-3: Audio input signal switch matrix

Fig. 2-4: Audio Baseband output amplifiers+

### 3. Modes of Operation

# 3.1. Interactions Between DRD 3515A and MAS 3506D

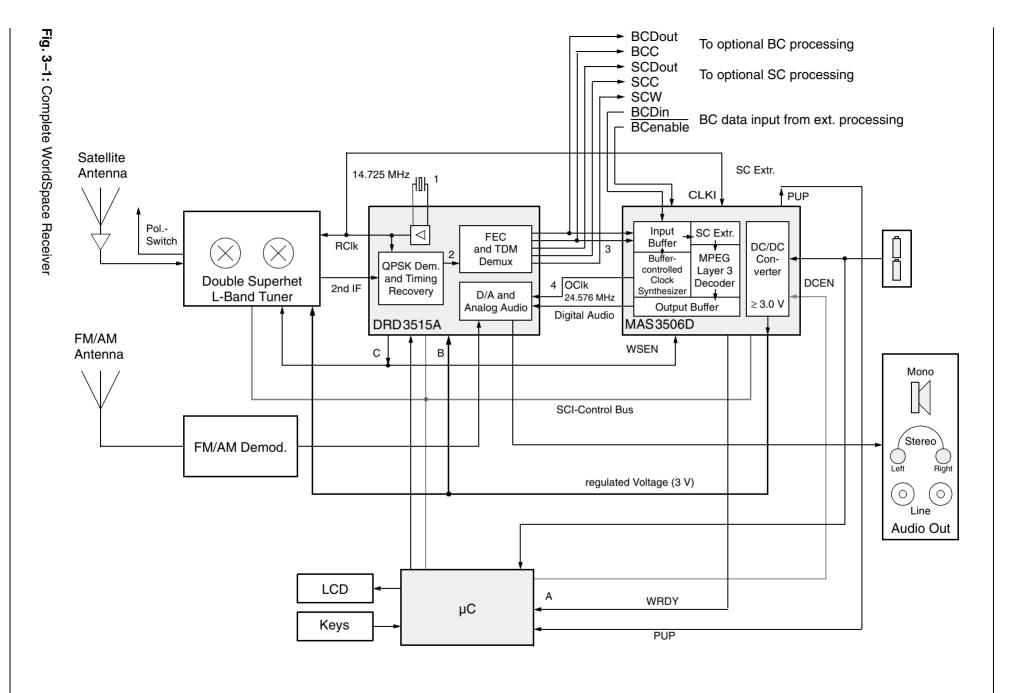

Both ICs, the DRD 3515A and the MAS 3506D are designed for joint operation. Both ICs interact very closely with respect to the system clock, the supply power concept and the corresponding operating modes. In Figure 3–1 a more detailed diagram shows how both chips are to be combined in a standard WorldSpace receiver.

# 3.2. Clock Concept

The complete chipset is driven by a single crystal at a frequency of 14.725 MHz. The DRD 3515A provides a crystal oscillator (1 in Fig. 3–1) and an appropriate clock buffer. The buffered clock output signal is provided at the RCLK pin. In order to reduce intermodulation with harmonics of the signal, it has a near-sinuosidal shape and a reduced voltage swing. This RCLK signal is also used to drive the digital parts of the tuner and the MAS 3506D. It can be directly connected to its input pin CLKI. In modes, where no MAS 3506D-operation is required, the RCLK signal may be switched off.

Since in the WorldSpace system the rate of the audio or user data channel is not locked to the Master Frame of the satellite (3), the MAS 3506D MPEG audio decoder has an own clock synthesizer which is driven by the DRD 3515A RCLK signal, but frequency-controlled by the data flow of the Broadcast Channel. The synthesizer locks its frequency to a multiple of the incoming BC data; its nominal frequency is 24.576 MHz. The synthesized 24.576 MHz is provided at the OCLK output of the MAS 3506D. This signal will be used as the master clock for the D/A converter in the DRD 3515A (signal 4 in Fig. 3–1).

Although the crystal frequency of 14.725 MHz is no exact submultiple of the L-band receiving frequencies, the selection of appropriate divisors in the PLL will result in a local oscillator frequency with sufficient accuracy (e.g. within 5 or 10 kHz of the target) that by far underbids the expected tolerances of the quartz crystal (50 ppm will result in a deviation of 75 kHz in the L-band).

### 3.3. Operation and Stand-By Modes

Different stand-by functions allow the operation of only those parts of the IC that are needed. The power concept (see Fig. 2–1 on page 7) of the MICRONAS StarMan chipset has been optimized for minimal power consumption with respect to the various operating modes of the chipset.

### 3.4. Power Up Sequence (2 Battery Operation)

In the DC/DC converter mode two external batteries with an expected voltage between 1.8 V and 3.0 V are connected to the DCSO pin of the MAS 3506D DC/DC converter via an inductance. The following sequence is executed after power up using the MAS 3506D DC/DC converter.

- The DC/DC converter and the power supervision start their operation upon a DCEN (DC enable) signal at the MAS 3506D.

- Wait for PUP (power up) output of MAS 3506D which indicates that sufficient output voltage is available.

- Activate PUP input signal at the DRD 3515A.

- The controller has to wait until the WRDY (World-Space ready) signal of the MAS 3506D is activated.

This signal indicates that the MAS 3506D has received a valid clock at the RCLK input, i.e. the crystal oscillator of the DRD 3515A is ramped up.

- Select operating mode by an appropriate I<sup>2</sup>C command (e.g. enable WorldSpace operation by setting the bit WSEN in the main configuration register of the DRD 3515A.)

- Enable the audio amplifier output (BAS\_PUP = 1) after the specified charging time of the output decoupling capacitors.

# 3.5. Power Up Sequence (Operation Without DC/ DC Converter)

Without the DC/DC converter a voltage between 3.0 V (absolute minimum 2.7 V) and 3.6 V is expected at the appropriate power supply input pins of both ICs. The DCSO input of the DC/DC converter must be connected to ground.

- The voltage supervision starts its operation upon a DCEN (DC enable) signal at the MAS 3506D.

- All other commands are as described in Section 3.4.

It is possible to directly connect the PUP output of the MAS 3506D to the PUP input of the DRD 3515A. However, if more sophisticated tasks are to be performed (e.g. battery voltage measurement with help of the power supervision circuit of the MAS 3506D), it is advised to route this line through the controller.

### 3.6. Power Down Sequence

- Mute the audio output.

- Switch audio input to DAC (BAS SRC = 00).

- Switch audio block into "low power mode" (BAS PUP = 0).

- Disable the PUP pin at the DRD 3515A.

- Disable the DCEN pin at the MAS 3506D.

# 3.6.1. Full WorldSpace Operation

All digital parts of the DRD 3515A are activated. After the power up sequence, the controller should set the WSEN bit. This will enable the WorldSpace decoder within the DRD 3515A and will validate the WSEN signal pin. This signal should be connected with the corresponding input of the MAS 3506D and with the "enable signals" of the tuner.

WSEN = 1,  $BAS_PUP = 1$ .

# 3.6.2. Audio Amplifier Operation

Only I<sup>2</sup>C bus, audio source selector, volume control, audio amplifier and crystal oscillator are active.

All digital functions except the I<sup>2</sup>C interface and the crystal oscillator can be powered down by setting WSEN to 0; thus the WorldSpace decoding functions of the DRD 3515A are put to stand-by and the WSEN output pin is forced to 0 which disables the audio decoding function of the MAS 3506D. This feature reduces the power consumption when only the audio amplifier and its co-functions (audio source selector, volume control) are needed to process external analog audio signals.

The audio baseband can additionally be switched into a "stand-by mode" (see Section on page 10).

WSEN = 0, BAS PUP = 1.

### 3.6.3. WorldSpace Operation Only

The analog functions (switch, volume control, amplifier) can be powered down by clearing the control bit BAS\_PUP. This yields operation of the WorldSpace decoder part up to the Broadcast Channel output.

WSEN = 1, BAS PUP = 0.

Although the current in the analog parts is reduced considerably, there is some current needed to resume very quickly to normal mode without any clicks.

It is recommended to switch the input source of the analog part to the D/A only while BAS\_PUP is 0! Otherwise there would exist an unavoidable path from the AUX-inputs to the outputs.

### 3.6.4. Off

By deactivating the PUP input signal the complete DRD 3515A is switched into zero power mode.

To avoid an unwanted DC path from the auxiliary audio inputs to the outputs it is recommended to switch the input source of the analog part to D/A (BAS\_SRC = 0) before deactivating the PUP pin.

### 4. Serial Control Interface

Communication between the DRD 3515A and the external controller is done via  $I^2C$  serial control interface.

# 4.1. I<sup>2</sup>C-Bus Interface

The DRD 3515A is equipped with an I<sup>2</sup>C-bus slave interface. It then may use I<sup>2</sup>C clock synchronization to slow down the interface if required. The I<sup>2</sup>C-bus interface uses one level of subaddresses: one I<sup>2</sup>C-bus address is used to address the IC and a subaddress selects one of the internal registers. The I<sup>2</sup>C-bus chip address is given below.

dev\_write = \$38 dev\_read = \$39

**Note:** The I<sup>2</sup>C address is subject to change

Table 4-1: Bits of I<sup>2</sup>C-address

| A6 | A5 | A4 | А3 | A2 | A1 | A0 | W/R |

|----|----|----|----|----|----|----|-----|

| 0  | 0  | 1  | 1  | 1  | 0  | 0  | 0/1 |

The registers of the DRD 3515A have 8 or 16-bit data size; 16-bit registers are accessed by reading/writing two 8-bit data words.

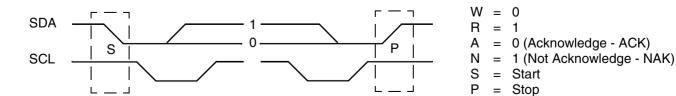

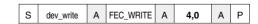

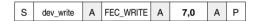

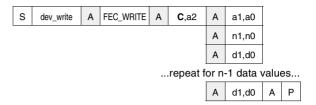

Fig. 4–1 shows I<sup>2</sup>C-bus protocols for read and write operations of the interface; the read operation requires an extra start condition and repetition of the chip address with read command set.

# 4.2. Register Overview

Table 4–2 gives definitions of the DRD 3515A control and status registers. The number of bits indicated for each register in the table is the number of bits implemented in hardware. Write registers that can be read back are indicated in Table 4–2.

A hardware reset initializes all control registers to 0. The automatic chip initialization after power on reset or a positive edge at the PUP pin loads a selected set of registers with the default values given in Table 4–2.

The register modes given in Table 4-2 are

w write only register

r/w read/write data register

r read data from DRD 3515A

The mnemonics used in the Micronas DRD 3515A demo software are given in the last column.

Example: 16-bit I2C write access

| S | dev_write | A subaddress |  | Α | high byte data | Α |   |

|---|-----------|--------------|--|---|----------------|---|---|

|   |           |              |  |   | low byte data  | Α | Р |

Example: 8-bit I<sup>2</sup>C read access

| S | dev_write | W | Α | subaddress | Α | S | dev_read | Α | low byte data | N | Р |

|---|-----------|---|---|------------|---|---|----------|---|---------------|---|---|

|---|-----------|---|---|------------|---|---|----------|---|---------------|---|---|

Fig. 4–1: I<sup>2</sup>C-Bus protocol

The following abbreviations have been used within register names and register bits.

| GLB_ | Global configuration                   | _AAG_  | Analog AGC              |

|------|----------------------------------------|--------|-------------------------|

| DMD_ | IF input and QPSK demodulator          | _AGC_  | Automatic gain control  |

| TDM_ | Time division demultiplexer            | _AMP_  | Amplifier               |

| FEC_ | Viterbi and Reed Solomon forward error | _BAS   | Analog audio baseband   |

|      | correction                             | _CLK_  | Clock                   |

| BAS_ | Analog audio baseband                  | _CNFG_ | Configuration           |

|      |                                        | _CNT_  | Count                   |

|      |                                        | _COEF_ | Coefficient             |

|      |                                        | _CR_   | Carrier recovery        |

|      |                                        | _CYIN_ | Carry input             |

|      |                                        | _DIS_  | Disable                 |

|      |                                        | _EN_   | Enable                  |

|      |                                        | _EQU_  | Equal                   |

|      |                                        | _FB_   | Feedback                |

|      |                                        | _LFSR_ | Pseudo-Random-Generator |

|      |                                        | _MFP_  | Master Frame Preamble   |

|      |                                        | _PR_   | Phase recovery          |

|      |                                        | _PRC_  | Prime Rate Channel      |

|      |                                        | _PUP_  | Power up                |

|      |                                        | _SELF_ | Self test               |

|      |                                        | _TH_   | Threshold               |

|      |                                        | _TR_   | Timing recovery         |

|      |                                        | _TS_   | Time slot               |

|      |                                        |        |                         |

Table 4–2: Register List

| I <sup>2</sup> C Sub-<br>address<br>(hex) | No of bits | R/W    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Default/<br>Target<br>values<br>(hex) | Name                                               |

|-------------------------------------------|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------|

| GLOBAL CO                                 | ONFIGUE    | RATION | GLB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |                                                    |

| 01                                        | 8          | W      | global configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                     | GLB_CONFIG                                         |

| IE INDUT OF                               | COTION     |        | $ \begin{array}{ll} \text{bit}[7] & \text{WorldSpace mode enable} \\ \text{bit}[6] & \text{select 5 V mode 0} = 3.3 \text{ V}, \ 1 = 5 \text{ V} \\ \text{bit}[5] & \text{l}^2 \text{S word length 0} = 16 \text{ bit}, \ 1 = 32 \text{ bit} \\ \text{bit}[4] & \text{audio power 0} = \text{low power}, \ 1 = \text{operation} \\ \text{bit}[3,2] & \text{input sel. 0} = \text{D/A}, \ 1 = \text{AUX1}, \ 2 = \text{N/A}, \\ 3 = \text{AUX2} \\ \text{bit}[1] & \text{mono/stereo for AUX inputs} \\ 0 = \text{stereo}, \ 1 = \text{mono} \\ \text{bit}[0] & \text{invert right power amplifier} \\ \end{array} $ | 0<br>0<br>0<br>0<br>0                 | WSEN SEL5V SI_IMOD BAS_PUP BAS_SRC BAS_MS BAS_INVR |

| IF INPUT SE                               |            | טואט   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <u> </u>                              |                                                    |

| 2E                                        | 8          | W      | analog AGC configuration  bit [7] reserved bit, keep '0' bit [6] reserved bit, keep '0' bit [5] reserved bit, keep '0' bit [4] input DC control loop enable bit [3] AGC control loop enable bit [2:0] AGC time constant                                                                                                                                                                                                                                                                                                                                                                                             | 19<br>0<br>0<br>0<br>1<br>1           | DMD_AAG_CNFG  AAG_DC_EN AAG_AGC_EN AAG_PARA_KI     |

| 2F                                        | 8          | r/w    | bit [4:0] analog AGC amplification set/return (target)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                                    | DMD_AAG_AGC                                        |

Table 4–2: Register List

| I <sup>2</sup> C Sub-<br>address<br>(hex) | No of bits           | R/W     | Function                                                                                                          | Default/<br>Target<br>values<br>(hex) | Name                               |  |  |  |

|-------------------------------------------|----------------------|---------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------|--|--|--|

| QPSK DEMO                                 | QPSK DEMODULATOR DMD |         |                                                                                                                   |                                       |                                    |  |  |  |

| 20                                        | 8                    | r/w     | carrier frequency offset (target)                                                                                 | 0                                     | DMD_CR_F                           |  |  |  |

| 26                                        | 8                    | r       | receiving quality (average I/Q amplitude variance) bit[7:4] receiving quality (target) bit[3:0] AGC-gain (target) | 2<br>0<br>2                           | DMD_AGC_RCVQU<br>RCVQU<br>AGC_GAIN |  |  |  |

| 28                                        | 8                    | r/w     | timing recovery symbol time (target)                                                                              | 0                                     | DMD_TR_TS                          |  |  |  |

| TDM_DEMU                                  | LTIPLE               | KER TDI | И                                                                                                                 |                                       |                                    |  |  |  |

| 11                                        | 8                    | r/w     | TDM time slot 1 bit [7] time slot 1 enable bit [6:0] time slot 1 channel ID (PRC number <1 96>)                   | 81<br>1<br>1                          | TDM_T_SLOT_1 TS_EN PRC             |  |  |  |

| 12                                        | 8                    | r/w     | TDM time slot 2 bit [7] time slot 2 enable bit [6:0] time slot 2 channel ID (PRC number)                          | 3<br>0<br>3                           | TDM_T_SLOT_2<br>TS_EN<br>PRC       |  |  |  |

| 13                                        | 8                    | r/w     | TDM time slot 3 bit [7] time slot 3 enable bit [6:0] time slot 3 channel ID (PRC number)                          | 5<br>0<br>5                           | TDM_T_SLOT_3 TS_EN PRC             |  |  |  |

| 14                                        | 8                    | r/w     | TDM time slot 4 bit [7] time slot 4 enable bit [6:0] time slot 4 channel ID (PRC number)                          | 7<br>0<br>7                           | TDM_T_SLOT_4 TS_EN PRC             |  |  |  |

| 15                                        | 8                    | r/w     | TDM time slot 5 bit [7] time slot 5 enable bit [6:0] time slot 5 channel ID (PRC number)                          | 9<br>0<br>9                           | TDM_T_SLOT_5 TS_EN PRC             |  |  |  |

| 16                                        | 8                    | r/w     | TDM time slot 6 bit [7] time slot 6 enable bit [6:0] time slot 6 channel ID (PRC number)                          | B<br>0<br>B                           | TDM_T_SLOT_6 TS_EN PRC             |  |  |  |

| 17                                        | 8                    | r/w     | TDM time slot 7 bit [7] time slot 7 enable bit [6:0] time slot 7 channel ID (PRC number)                          | D<br>0<br>D                           | TDM_T_SLOT_7 TS_EN PRC             |  |  |  |

| 18                                        | 8                    | r/w     | TDM time slot 8 bit [7] time slot 8 enable bit [6:0] time slot 8 channel ID (PRC number)                          | F<br>0<br>F                           | TDM_T_SLOT_8 TS_EN PRC             |  |  |  |

| FORWARD                                   | ERROR                | CORRE   | CTION FEC                                                                                                         |                                       |                                    |  |  |  |

| 30                                        | 8                    | w       | FEC command and data write register                                                                               |                                       | FEC_WRITE                          |  |  |  |

| 31                                        | 8                    | r       | FEC data read register                                                                                            | 0                                     | FEC_READ                           |  |  |  |

Table 4-2: Register List

| I <sup>2</sup> C Sub-<br>address<br>(hex) | No of<br>bits | R/W     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Default/<br>Target<br>values<br>(hex) | Name                                     |

|-------------------------------------------|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------|

| ANALOG BA                                 | ASEBAN        | ID AUDI | O BAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       |                                          |

| 40                                        | 16            | w       | audio volume control $ \begin{array}{ll} \text{bit [15]} & \text{set to '0'} \\ \text{bit [14]} & \text{Disable RCLK} \\ \text{bit [13:8]} & \text{analog audio volume level left:} \\ & 0 = \text{mute; } 1 = -75 \text{ dB; } 2\text{C}_h = 0 \text{ dB,} \\ 38_h = +18 \text{ dB} \\ \text{bit [7:6]} & \text{set to '0'} \\ \text{bit [5:0]} & \text{analog audio volume level right} \\ & 0 = \text{mute; } 1 = -75 \text{ dB; } 2\text{C}_h = 0 \text{ dB,} \\ 38_h = +18 \text{ dB} \\ \end{array} $ | 0<br>0<br>0<br>0<br>0                 | BAS_AUDIO  RCLK_OFF VOL_LEV_L  VOL_LEV_R |

# 4.3. Detailed Description of the Registers

### 4.3.1. Main Configuration Register GLB CONFIG

The main configuration register GLB\_CONFIG is used to enable/disable WorldSpace operation, different power modes and to control the analog audio backend.

Table 4-3: GLB\_CONFIG register (\$01, write)

| Bits               | Signal    | Comment                              |

|--------------------|-----------|--------------------------------------|

| [7]<br>Reset = 0   | WSEN<br>0 | WorldSpace enable disable WorldSpace |

|                    | 1         | enable WorldSpace                    |

| [6]<br>Reset = 0   | SEL5V     | select 5 V mode for the audio blocks |

|                    | 0         | 3.3 Volt mode<br>5 Volt mode         |

| [5]                | SI_IMOD   | I <sup>2</sup> S word length         |

| Reset = 0          | 0         | 16 bits<br>32 bits                   |

| [4]                | BAS_PUP   | power for audio                      |

| Reset = 0          | 0         | low power stand by normal operation  |

| [3,2]<br>Reset = 0 | BAS_SRC   | audio input selector                 |

| Reset = 0          | 0         | DAC<br>AUX1                          |

|                    | 2 3       | N/A<br>Aux2                          |

| [1]                | BAS_MS    | mono/stereo for AUX                  |

| Reset = 0          | 0 1       | stereo<br>mono                       |

| [0]                | BAS_INVR  | invert right audio channel           |

| Reset = 0          | 0         | off<br>on                            |

### WSEN

If set, the WorldSpace mode of the DRD 3515A is enabled and the WSEN signal is activated at the output. Disabling this bit powers down all digital parts that are used exclusively for WorldSpace decoding.

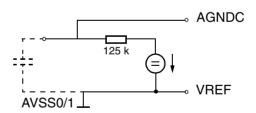

### - SEL5V

The SEL5V signal switches the internal bandgap reference voltage. In normal mode (SEL5V = 0) a power supply voltage of 3 V is expected for VSUP<sub>A</sub> (pins AVDD0/1) and the bandgap reference is switched to 1.5 V. If SEL5V = 1, a minimal power supply voltage of 4.5 V is expected for VSUP<sub>A</sub> (pins AVDD0/1) and the bandgap reference voltage is switched to 2.25 V. In the latter mode the signal level is increased by a factor of 1.5 (3.5 dB).

### - SI IMOD

The IMOD bit configures the I<sup>2</sup>S digital audio interface for different digital word lengths. In default mode, a word length of 16 bits/sample is expected. However, if additionally an external DAC is connected to the I<sup>2</sup>S output signal of the MAS 3506D, the full MPEG audio data resolution may be required. In this case the MAS 3506D will generate 32-bit samples. The special structure of the DRD 3515A digital input interface that uses only 2 input lines needs this additional information about the I<sup>2</sup>S word length.

### - BAS PUP

The BAS\_PUP bit enables full operation of the analog baseband processing. If the BAS\_PUP bit is cleared the analog baseband processing is switched into the low power stand by mode: The analog output is muted and the power consumption of the analog backend is reduced considerably. However, some parts are still working to provide a very fast resume of the full operation with minimum click.

# BAS\_SRC The BAS\_SRC bits select the DAC or one of the

AUX1/AUX2 input lines as shown in Fig. 2-3.

### - BAS MS

In normal operating mode stereo signals are expected. However, monoaural output may be required e.g. to optimize the output power of a single loudspeaker. If AUX signals are selected, they can be converted to a monoaural signal by setting the BAS\_MS bit. The BAS\_MS bit setting also affects the line output signal at FINL/R (see Fig. 2–3 on page 10).

For the D/A converter signal the mono conversion must be performed in the digital domain, i.e. in the MPEG audio decoder.

### - BAS INVR

The power amplifier for the right channel will be switched to inverted polarity by setting this bit. The inversion is required if a single loudspeaker is connected to the OUT1 and OUT2 pins. In this case the output amplifiers work in bridge mode to allow maximum difference voltage swing (see Fig. 2–4 on page 11).

# 4.3.2. IF Input Configuration

Table 4-4: DMD\_AAG\_CNFG (\$2E, write)

| Bits              | Signal                      | Comment                                                                                                   |

|-------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------|

| [4]<br>Reset = 1  | AAG_DC_EN                   | IF input DC control loop enable (see Fig. 2–2)                                                            |

|                   | 0                           | disable AGC DC loop<br>enable AGC DC loop                                                                 |

| [3]<br>Reset = 1  | AAG_AGC_EN 0 1              | IF input AGC enable disable AGC function enable AGC function                                              |

| [20]<br>Reset = 1 | AAG_PARA_KI 0 1 2 3 4 5 6 7 | AGC time constant 4.48 ms/dB 2.24 ms/dB 1.12 ms/dB 1.25 ms/dB 0.58 ms/dB 0.28 ms/dB 0.07 ms/dB 0.04 ms/dB |

## - AAG DC EN

The AAG\_DC\_EN bit enables or disables the automatic DC compensation (see Figure 2–2).

# - AAG\_AGC\_EN

The AAG\_AGC\_EN bit enables or disables the automatic gain control.

# - AAG PARA KI

By setting AAG\_PARA\_KI time constant register, the reaction of the AGC with respect to level changes of the IF-input signal can be modified. This is a useful option for adjusting the behavior to different reception environments.

## 4.3.3. IF Input: Analog Automatic Gain Control

Table 4-5: DMD AAG AGC register (\$2F, read/write)

| Bits              | Signal          | Comment                  |

|-------------------|-----------------|--------------------------|

| [40]<br>Reset = 0 | DMD_AAG<br>_AGC | read/write               |

|                   | 0<br>1          | 0 dB gain<br>1 dB gain   |

|                   | 30<br>31        | 30 dB gain<br>31 dB gain |

### DMD AAG AGC

If the AAG\_AGC\_EN bit is enabled, reading DMD\_AAG\_AGC returns a value that is inversely proportional to the signal strength of the IF input signal. If the AAG\_AGC\_EN bit is cleared, reading DMD\_AAG\_AGC returns the default value or the value that has been written previously. Writing to the DMD\_AAG\_AGC register is only of duration if the AAG\_AGC\_EN bit is set to 0.

## 4.3.4. QPSK Demodulator Carrier Frequency Offset

Table 4-6: DMD CR F register (\$20, read/write)

| Bits      | Signal       | Comment                           |

|-----------|--------------|-----------------------------------|

| [70]      | DMD_CR_F     | read/write IF frequency deviation |

| Reset = 0 | -128<br>-127 | –115 kHz<br>–114 kHz              |

|           | <br>0        | 0 kHz                             |

|           | 126<br>127   | 113 kHz<br>114 kHz                |

The DMD CR F sets/returns the actual input carrier frequency relative to the nominal IF-center frequency of 1.840 MHz. After synchronization to a WorldSpace channel, this register reflects a value that depends on the actual frequency deviation due to the accuracy and stability of the 14.725 MHz crystal and that of the tuner reference. This value can be stored into a non-volatile controller memory and rewritten to the DMD CR F register after power-up or re synchronization. This measure will considerably speed up carrier and timing synchronization for noisy channels. Reading the DMD CR F register in the power-down cycle and rewriting it with the same value in the power-up cycle will help the digital carrier frequency recovery to find the satellite signal.

# 4.3.4.1. QPSK Demodulator Receiving Quality Indicator

Table 4-7: DMD\_AGC\_RCVQU register (\$26, read)

| Bits  | Signal                                                           | Comment                                                                                         |

|-------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| [7:4] | RCVQU<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 15 | receiving quality (C/N) 40 dB 20 dB 17 dB 14 dB 12 dB 11 dB 9 dB 7 dB 6 dB 4 dB below threshold |

| [3:0] | AGC_GAIN 0 1 2 15                                                | gain of digital AGC not allowed Gain = 1/4 Gain = 2/4 Gain = 15/4                               |

The 4 MSBs of the register return the receiving quality indicated by the average I/Q amplitude variance as detected by the QPSK demodulator. The values of Table 4–19 on page 27 depend on the amplitude target of the digital AGC (AGC GAIN).

The values read out by the receiving quality evaluation are only meaningful, if the digital AGC is not in saturation.

The 4 LSBs of the register return the actual gain of the QPSK demodulator's digital AGC and phase recovery control.

# 4.3.5. QPSK Demodulator Timing Recovery Symbol Time.

**Table 4–8:** DMD TR TS register (\$28, read/write)

| Bits               | Signal    | Comment                                            |

|--------------------|-----------|----------------------------------------------------|

| [7:0]<br>Reset = 0 | DMD_TR_TS | f <sub>symb-crystal</sub> - f <sub>symb-recv</sub> |

| -105 <sub>d</sub>  |           | –184 Hz                                            |

| <br>-1<br>0<br>1   |           | <br>–1.75 Hz<br>0 Hz<br>1.75 Hz                    |

| <br>105            |           | 184 Hz                                             |

The DMD\_TR\_TS sets/returns the internal symbol timing standard offset that locks on the symbol timing of the incoming data stream which is nominally 1.84 MHz. After synchronization to a WorldSpace channel, this register reflects a value that depends on the actual frequency deviation due to the accuracy and stability of the 14.725 MHz crystal. This value can be stored into a non-volatile controller memory and rewritten to the DMD\_TR\_TS register after power-up or re synchronization. This measure will considerably speed up timing synchronization especially for noisy channels. Values should not exceed the range given above.

- TDM Time Slot Registers.

Table 4-9: TDM\_T\_SLOT\_n (\$12 ... \$18, write)

| Bits                                      | Signal | Comment                             |

|-------------------------------------------|--------|-------------------------------------|

| [7] Reset = 0 (Reset = 1 for register 11) | TS_EN  | enable time slot n                  |

| [6:0]<br>Different<br>reset<br>values     | PRC    | Prime Rate Channel ID number <1 96> |

- A requested Broadcast Channel may consist of 1 or more (up to 8) Prime Rate Channels. The according PRC ID numbers are documented in the TSCC information.

- The PRC numbers for the requested Broadcast Channel must be deposited in the lowest TDM\_T\_SLOT registers in ascending order. These time slots must be enabled by setting bit TS\_EN.

- If the BC consists of less than 8 PRCs the controller must also deposit Prime Rate Channel numbers to all unused TDM\_T\_SLOT registers as well. These PRC numbers must be unique (one number must only occur once) and different from those used to build the requested BC. Unused TDM\_T\_SLOT registers must be disabled (i.e. TS\_EN = 0).

- Writing to one of the TDM\_T\_SLOT registers will set the PRC preamble detection algorithm to the "unsynched" state (see Table 4–13 on page 24).

During normal reception these registers must not be written.

# 4.3.6. Analog Audio Gain

Table 4-10: BAS\_AUDIO (\$40, write)

| Bits      | Signal          | Comment                         |

|-----------|-----------------|---------------------------------|

| [14]      | RCLK_OFF        | disable RCLK                    |

|           | 0               | RCLK available<br>RCLK disabled |

| [13:8]    | VOL_LEV_L       | Analog volume left              |

| Reset = 0 | 0<br>1<br>2     | Mute<br>-75.0 dB<br>-72.0 dB    |

|           | 7<br>8<br>9     |                                 |

|           | <br>44<br>45    | <br>0.0 dB<br>+1.5 dB           |

|           | 55<br>56        | +16.5 dB<br>+18.0 dB            |

| [5:0]     | VOL_LEV_R       | Analog volume right             |

| Reset = 0 | 0<br>1<br>2     | Mute<br>-75.0 dB<br>-72.0 dB    |

|           | <br>7<br>8<br>9 |                                 |

|           | <br>44<br>45    | <br>0.0 dB<br>+1.5 dB           |

|           | 55<br>56        | +16.5 dB<br>+18.0 dB            |

- RCLK\_OFF is used to disable the RCLK output signal.

- VOL\_LEV\_L/R bits are used to control the volumes of the audio amplifiers. For loudspeaker operation the amplification of both channels must be equal.

- For best loudspeaker performance it is recommended (but not mandatory) to use a mono audio source by either selecting the proper audio matrix mixing coefficients in the MAS 3506D or by setting the BAS\_MS bit in the GLB\_CONFIG register for AUX input sources. Note that the line outputs will also be affected by these settings.

# 4.4. Registers for Advanced Features

The following registers are only needed for advanced features such as adjusting the demodulation parameters to special situations (e.g. car radio) or different than the recommended hardware configuration (e.g.

2nd IF spectrum not mirrored). The use of these registers is not needed for normal WorldSpace operation and thus they should normally be left at their default values.

Table 4-11: Register list for advanced features

| I <sup>2</sup> C Sub-<br>address<br>(hex) | No of bits           | R/W     | Function                                                                                                              | Default/<br>Target<br>values<br>(hex) | Name                                     |  |

|-------------------------------------------|----------------------|---------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------|--|

| IF INPUT S                                | F INPUT SECTION DMD  |         |                                                                                                                       |                                       |                                          |  |

| 2D                                        | 8                    | r/w     | DC value of digitized input signal (target)                                                                           | 0                                     | DMD_AAG_DC                               |  |

| QPSK DEM                                  | QPSK DEMODULATOR DMD |         |                                                                                                                       |                                       |                                          |  |

| 21                                        | 8                    | r/w     | carrier recovery amplitude validation threshold                                                                       | 41                                    | DMD_CR_A_TH                              |  |

| 22                                        | 8                    | r/w     | phase validation threshold                                                                                            | 52                                    | DMD_CR_P_TH                              |  |

|                                           |                      |         | bit [7:6] Viterbi gain<br>bit [5:0] phase threshold                                                                   | 1<br>12                               | PR_VGAIN<br>CR_P_TH                      |  |

| 23                                        | 8                    | r/w     | frequency validation threshold                                                                                        | 0C                                    | DMD_CR_F_TH                              |  |

|                                           |                      |         | bit [7] TWTA compensation bit 0 (LSB) bit [6] spectrum of IF input signal not mirrored bit [5:0] frequency threshold  | 0<br>0<br>0C                          | TWTA_COMP_0<br>PR_CONJ<br>CR_F_TH        |  |

| 24                                        | 8                    | r/w     | carrier and phase recovery control                                                                                    | AC                                    | DMD_CR_PARA                              |  |

|                                           |                      |         | bit [7] select downsampling in MTA filter between 8 and 4                                                             | 1                                     | CR_PARA_4                                |  |

|                                           |                      |         | bit [6] TWTA compensation bit 1 bit [5:3] frequency control loop bit [2:0] I-part of phase recovery control loop      | 0<br>5<br>4                           | TWTA_COMP_1<br>CR_PARA_F<br>CR_PARA_P_KI |  |

| 25                                        | 8                    | r/w     | amplitude target of digital AGC                                                                                       | 4B                                    | DMD_AGC_A_TGT                            |  |

| 27                                        | 8                    | r/w     | digital AGC and phase recovery control                                                                                | 2C                                    | DMD_AGC_PARA                             |  |

|                                           |                      |         | bit [7] TWTA compensation bit 2 (MSB) bit [6] select downsampling in MTA filter between 64 and 32                     | 0                                     | TWTA_COMP_2<br>AGC_PARA_32               |  |

|                                           |                      |         | bit [5:3] I-part of digital AGC control loop<br>bit [2:0] P-part of phase recovery control loop                       | 5<br>3                                | AGC_PARA_A<br>CR_PARA_P_KP               |  |

| 29                                        | 8                    | w       | timing recovery control                                                                                               | 19                                    | DMD_TR_PARA                              |  |

|                                           |                      |         | bit [6] select downsampling in MTA filter between 16 and 8                                                            | 0                                     | TR_PARA_8                                |  |

|                                           |                      |         | bit [5:3] P-part of timing recovery control loop<br>bit [2:0] I-part of timing recovery control loop                  | 3                                     | TR_PARA_TS_KP<br>TR_PARA_TS_KI           |  |

| TDM_DEM                                   | JLTIPLE              | XER TDI | И                                                                                                                     |                                       |                                          |  |

| 19                                        | 16                   | w       | TDM synchronization unsynched threshold values                                                                        | 4C27                                  | TDM_TH_USYNC                             |  |

|                                           |                      |         | bit [15] set to '0' bit [14:8] Master Frame Preamble (MFP) threshold (in unsynchronized state)                        | 0<br>4C                               | MFP_TH_USYNC                             |  |

|                                           |                      |         | bit [7] set to '0' bit [6] set to '0' bit [5:0] Prime Rate Channel (PRC) preamble threshold (in unsynchronized state) | 0<br>0<br>27                          | PRC_TH_USYNC                             |  |

Table 4-11: Register list for advanced features

| I <sup>2</sup> C Sub-<br>address<br>(hex) | No of bits | R/W | Function                                                                    | Default/<br>Target<br>values<br>(hex) | Name        |

|-------------------------------------------|------------|-----|-----------------------------------------------------------------------------|---------------------------------------|-------------|

| 1B                                        | 16         | w   | TDM synchronization synched threshold values                                | 4021                                  | TDM_TH_SYNC |

|                                           |            |     | bit [14:8] Master Frame Preamble (MFP) threshold in synchronized state      | 40                                    | MFP_TH_SYNC |

|                                           |            |     | bit [5:0] Prime Rate Channel (PRC) preamble threshold in synchronized state | 21                                    | PRC_TH_SYNC |

### 4.5. FEC Registers

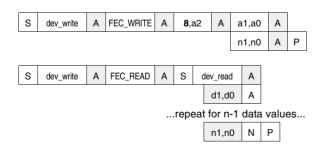

The FEC Data Read and Write registers have a different functionality in the register space of the DRD 3515A. The FEC registers give access to all function of the internal FEC-processor that performs the error correcting tasks (i.e. Viterbi decoding and Reed-Solomon decoding). Some additional tasks like ES1 decryption and Time Slot Control Channel (TSCC) decoding are also done by this processor. It is controlled by using a special command syntax. These I<sup>2</sup>C commands allow the micro controller to access internal states, RAM contents and hidden internal hardware control registers. The following commands are supported by the DRD 3515A.

Table 4-12: Basic FEC controller commands

| Code | Command   | Comment                   |  |

|------|-----------|---------------------------|--|

| \$4x | idle mode | select idle mode          |  |

| \$6x | TSCC mode | switch into TSCC mode     |  |

| \$7x | BC-mode   | switch into BC-mode       |  |

| \$8x | Mem-Read  | read from internal memory |  |

| \$Cx | Mem-Write | write to internal memory  |  |

The FEC data register control interface is also used for low bit rate data transmission, i.e. the transfer of TSCC data. The synchronization between controller and DRD 3515A will be initiated by the signal on the SYNC pin or by monitoring the status (at the cost of a higher work load for the controller).

The DRD 3515A embedded processor scans the FEC register periodically and checks for pending or new commands. However, due to some time critical firmware parts a certain latency time for the response has to be expected.

### 4.5.1. Conventions for the Command Description

The description of the various commands use the following formalism:

- A data value is split into 4-bit nibbles which are numbered beginning with 0 for the least significant nibble.

- Data values in nibbles are always shown in hexadecimal notation indicated by a preceding "\$".

- A hexadecimal 16-bit number d is written e.g. as d = \$7C63, its four nibbles are:

d3 = \$7, d2 = \$C, d1 = \$6, d0 = \$3

- Abbreviations used in the following descriptions

- a address

- d data value

- n byte count value

- o offset value

- x don't care

| S  | Start                    | (please see Figure 4–1) |

|----|--------------------------|-------------------------|

| Λ. | A a l : a a : l a al a a |                         |

A Acknowledge N Not acknowledge

P Stop

dev\_write \$38 dev\_read \$39

FEC\_WRITE \$30 (these addresses are listed FEC\_READ \$31 in Table 4–2 on page 16)

## 4.5.2. Detailed DRD 3515A Command Syntax

# 4.5.2.1. Idle Mode

Switch DRD 3515A into idle mode. In idle mode neither BC decoding nor TSCC decoding is performed and the DRD 3515A will generate no output at the Broadcast Channel or Service Component output pins.

#### 4.5.2.2. TSCC Mode

Switch DRD 3515A into TSCC mode. In TSCC mode no BC decoding is performed and the DRD 3515A will generate no output at the Broadcast Channel or Service Component output pins. The TSCC-data of the Broadcast Channel are extracted and stored for readout by the controller (Section 4.5.4.6. on page 27). After having decoded the TSCC-data successfully the DRD 3515A will indicate this via the SYNC signal and switch into idle mode.

The TSCC mode is the default mode of the DRD 3515A after power-on reset.

### 4.5.2.3. BC Mode

Switch DRD 3515A into BC mode. In BC mode Broadcast Channel decoding is performed and the DRD 3515A will generate output at the Broadcast Channel output pins and - if an SC is selected - also at the Service Component output pins. Before switching into BC-mode the TDM\_T\_SLOT registers should be written accordingly. In BC mode the SYNC signal indicates that a new SCH has been detected. This signal may be used for calculation of decryption keys.

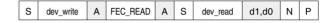

### 4.5.2.4. MEM Read

This command is e.g. required for reading the TSCC data.

Read data starting at address  $\mathbf{a} = (a2,a1,a0)$  from the internal memory of the DRD 3515A FEC-processor.

For the exact procedure to read the TSCC-data please refer to Section 4.5.4.6. on page 27.

### 4.5.2.5. MEM Write

Write data starting at address  $\mathbf{a} = (a2,a1,a0)$  to the internal memory of the DRD 3515A FEC-processor.

### 4.5.2.6. Default Read

The Default Read command immediately returns the content of the main status register of the DRD 3515A in the variable  $\mathbf{d}=(d1,d0)$ . The Default Read is the fastest way to get information from the DRD 3515A and may be used for polling of the FEC-processor status.

Table 4-13: Main Status Register