# Microcomputer Components

8-Bit CMOS Microcontroller

# C515C-8E

Addendum to C515C User's Manual 08.96

Rev. 1.0 05.97

| C515C-8E - Addendum to C515C User's Manual V1.0 05.97 |                                        |  |  |  |  |  |  |  |

|-------------------------------------------------------|----------------------------------------|--|--|--|--|--|--|--|

| <b>Revision History :</b>                             | Original Version                       |  |  |  |  |  |  |  |

| Previous Releases                                     | : none                                 |  |  |  |  |  |  |  |

| Page / Chapters                                       | Subjects (changes since last revision) |  |  |  |  |  |  |  |

|                                                       |                                        |  |  |  |  |  |  |  |

#### Contents

#### Page

| 1                                                  | Introduction                                                                                                                                                                               |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2                             | Extended Functionality of the C515C-8E       3         Second Pin for Wake-up from Software Power Down       3         Switch-off Capability of the CAN Controller       4                 |

| <b>3</b><br>3.1<br>3.2                             | Programming Configuration       5         Pin Configuration of OTP Programming Mode       6         Pin Definitions in OTP Programming Mode       7                                        |

| <b>4</b><br>4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3  | Programming Mode Selection9Basic Programming Mode Selection9OTP Memory Access Mode Selection10Program / Read OTP Memory Bytes11Lock Bits Programming / Read13Access of Version Bytes15     |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | Device Specifications16Absolute Maximum Ratings16DC Characteristics17A/D Converter Characteristics19AC Characteristics21OTP Memory Programming Mode Characteristics28Package Information33 |

| 6                                                  | Addendum                                                                                                                                                                                   |

#### 1 Introduction

The C515C-8E is the OTP version in the C515C-8R microcontroller with a one-time programmable 64K byte program memory. With the C515C-8E fast programming cycles are achieved (1 byte in 100  $\mu$ sec). Also several levels of OTP memory protection can be selected. The basic functionality of the C515C-8E as a microcontroller is upward compatible to the C515C-8R (ROM part) or C515C-L (romless part) functionality.

Additionally, the functionality of the C515C-8E has been upgraded by two features :

- the wake-up from software power down mode can, additionally to the external pin P3.2/INT0 wake-up capability, also be triggered alternatively by a second pin P4.7/RXDC.

- for power consumption reasons the on-chip CAN controller can be switched off during normal operating mode of the C515C-8E.

This document describes in detail the C515C-8E programming interface. The description of the detailed microcontroller functions of the C515C is given in the "C515C User's Manual 08.96".

#### 2 Extended Functionality of the C515C-8E

#### 2.1 Second Pin for Wake-up from Software Power Down

Additionally to pin P3.2/INT0 of the C515C-8R, the C515C-8E provides a second pin (P4.7/RXDC) which can be used alternatively for the wake-up from software power down mode operation. The selection of the port pin for the wake-up function is controlled by bit WS in SFR PCON1. PCON1 is a mapped SFR at address  $88_{\text{H}}$  and can only be accessed when bit RMAP (bit 4 in SFR SYSCON (B1<sub>H</sub>)) is set.

See pages 9-7 and 9-8 of the C515C User's Manual 08.96 for detailed description of the wake-up sequence. The timing for the wake-up sequence of pin P4.7/RXDC is identical to the timing for pin P3.2/INT0.

#### Special Function Register PCON1 (Mapped Address 88<sub>H)</sub>

Reset Value : 0XX0XXXXB

| Bit No.         | MSB  |   |   |    |   |   |   | LSB |       |

|-----------------|------|---|---|----|---|---|---|-----|-------|

|                 | 7    | 6 | 5 | 4  | 3 | 2 | 1 | 0   | _     |

| <sup>88</sup> H | EWPD | _ | _ | WS | _ | _ | _ | _   | PCON1 |

| Symbol | Function                                                                                                                                                                                            |  |  |  |  |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| EWPD   | External wake-up from power down enable bit<br>Setting EWPD before entering software power down mode, enables the<br>external wake-up from software power down mode capability of the C515C-<br>8E. |  |  |  |  |  |  |

| WS     | Wake-up from software power down mode source select<br>WS = 0 : wake-up via pin P3.2/INT0 selected (default after reset)<br>WS = 1 : wake-up via pin P4.7/RXDC selected                             |  |  |  |  |  |  |

| _      | Reserved bits for future use. Read by CPU returns undefined values.                                                                                                                                 |  |  |  |  |  |  |

#### 2.2 Switch-off Capability of the CAN Controller

For power consumption reasons the on-chip CAN controller can be switched off during normal operating mode of the C515C-8E by setting bit CSWO in SFR SYSCON. When the CAN controller is switched off its clock signal is turned off and the operation of the CAN controller is stopped. This switch-off state of the CAN controller is equal to its state in software power down mode. Any message transfer is interrupted. In order to ensure that the CAN controller is not stopped while sending a dominant level ("0") on the CAN bus, the microcontroller should set bit INIT in the Control Register prior to setting bit CSWO. The C515C-8E can check, if a transmission is in progress by reading bits TXRQ and NEWDAT in the message objects and bit TXOK in the Control Register. After clearing bit CSWO again the CAN controller has to be reconfigured.

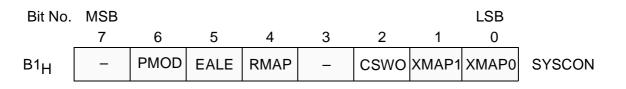

#### Special Function Register SYSCON (Address B1<sub>H</sub>) Reset Value : XX100001<sub>B</sub>

The functions of the shaded bits are not described in this section.

| Bit  | Function                                                                                                                                   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| _    | Reserved bits for future use. Read by CPU returns undefined values.                                                                        |

| CSWO | CAN controller switch-off bit<br>CSWO = 0 : CAN controller is enabled (default after reset).<br>CSWO = 1 : CAN controller is switched off. |

When the C515C-8E is put into software power down mode, bit CSWO is not affected. This means, when software power down mode is entered with CAN controller switched off, the CAN controller stays in switch-off state after the wake-up from software power down mode has been left\*.

#### 3 Programming Configuration

During normal program execution the C515C-8E behaves like the C515C-8R/C515C-L. For programming of the device, the C515C-8E must be put into the programming mode. This typically is done not in-system but in a special programming hardware. In the programming mode the C515C-8E operates as a slave device similar as an EPROM standalone memory device and must be controlled with address/data information, control lines, and an external 11.5 V programming voltage.

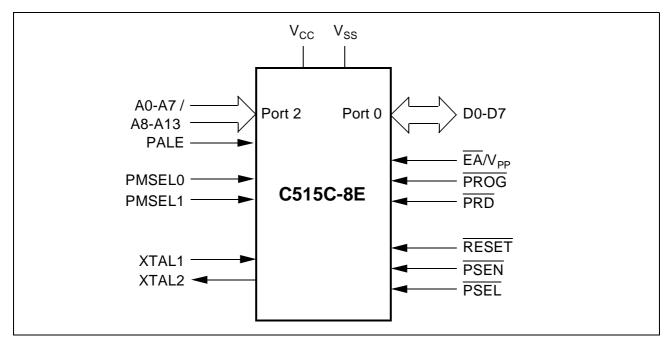

In the programming mode port 0 provides the bidirectional data lines and port 2 is used for the multiplexed address inputs. The upper address information at port 2 is latched with the signal PALE. For basic programming mode selection the inputs RESET, PSEN, EA/V<sub>PP</sub>, ALE, PMSEL1/0, and PSEL are used. Further, the inputs PMSEL1,0 are required to select the access types (e.g. program/verify data, write lock bits, ....) in the programming mode. In programming mode V<sub>CC</sub>/V<sub>SS</sub> and a clock signal at the XTAL pins must be applied to the C515C-8E. The 11.5 V external programming voltage is applied to the EA/V<sub>PP</sub> pin.

**Figure 1** shows the pins of the C515C-8E which are required for controlling of the OTP programming mode.

Figure 1

Programming Mode Configuration

#### 3.1 Pin Configuration of OTP Programming Mode

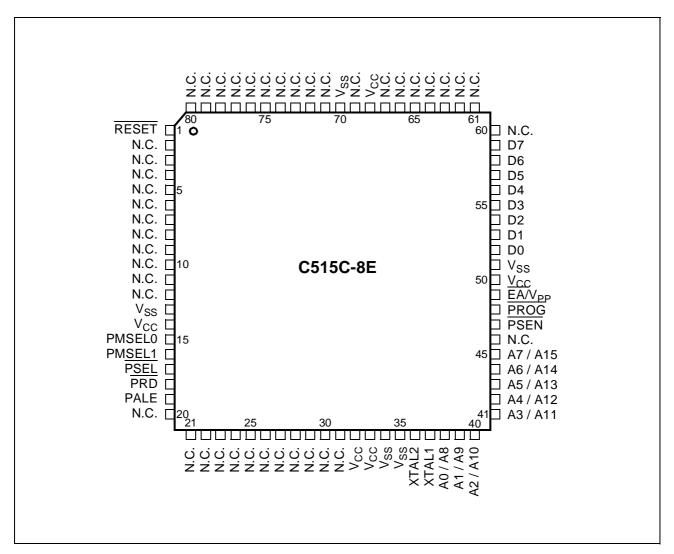

Figure 2 shows the detailed pin configuration (P-MQFP-44-2 package) of the C515C-8E in programming mode.

#### Figure 2 Pin Configuration of the C515C-8E in OTP Programming Mode (Top View)

#### 3.2 Pin Definitions in OTP Programming Mode

The following **table 1** contains the functional description of all C515C-8E pins which are required for OTP memory programming

Table 1

| Symbol            | Pin Number | I/O*) | ) Function                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                         |                              |  |  |  |  |

|-------------------|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|--|

| RESET             | 1          | I     | <b>Reset</b><br>This input must be at static "0" (active) level during the whole<br>programming mode.                                                                                                                                                                    |                                                                                                                                                                                                                                                                         |                              |  |  |  |  |

| PMSEL0<br>PMSEL1  | 15<br>16   |       | These pins an<br>programming<br>rising edge of                                                                                                                                                                                                                           | <b>Programming mode selection pins</b><br>These pins are used to select the different access modes in<br>programming mode. PMSEL1,0 must satisfy a setup time to the<br>rising edge of PALE. When the logic level of PMSEL1,0 is<br>changed, PALE must be at low level. |                              |  |  |  |  |

|                   |            |       | PMSEL1                                                                                                                                                                                                                                                                   | PMSEL0                                                                                                                                                                                                                                                                  | Access Mode                  |  |  |  |  |

|                   |            |       | 0                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                       | Reserved                     |  |  |  |  |

|                   |            |       | 0                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                       | Read version bytes           |  |  |  |  |

|                   |            |       | 1                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                       | Program/read lock bits       |  |  |  |  |

|                   |            |       | 1                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                       | Program/read OTP memory byte |  |  |  |  |

| PSEL              | 17         | I     | <b>Basic programming mode select</b><br>This input is used for the basic programming mode selection<br>and must be switched according <b>figure 3</b> .                                                                                                                  |                                                                                                                                                                                                                                                                         |                              |  |  |  |  |

| PRD               | 18         | I     | <b>Programming mode read strobe</b><br>This input is used for read access control for OTP memory read, version byte read, and lock bit read operations.                                                                                                                  |                                                                                                                                                                                                                                                                         |                              |  |  |  |  |

| PALE              | 19         | I     | <b>Programming address latch enable</b><br>PALE is used to latch the high address lines. The high address<br>lines must satisfy a setup and hold time to/from the falling edge<br>of PALE. PALE must be at low level whenever the logic level of<br>PMSEL1.0 is changed. |                                                                                                                                                                                                                                                                         |                              |  |  |  |  |

| XTAL2             | 36         | I     | XTAL2<br>Input to the oscillator amplifier.                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                         |                              |  |  |  |  |

| XTAL1             | 37         | 0     | <b>XTAL1</b><br>Output of the inverting oscillator amplifier.                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                         |                              |  |  |  |  |

| A0/A8 -<br>A7/A15 | 38 - 45    | I     | Address lines<br>P2.0-7 are used as multiplexed address input lines A0-A7 and<br>A8-A15. A8-A15 must be latched with PALE.                                                                                                                                               |                                                                                                                                                                                                                                                                         |                              |  |  |  |  |

\*) I = Input

O = Output

#### Table 1 Pin Definitions and Functions in Programming Mode (cont'd)

| Symbol             | Pin Number                              | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|-----------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSEN               | 47                                      | I     | <b>Program store enable</b><br>This input must be at static "0" level during the whole<br>programming mode.                                                                                                                                                                                                                                                                                                         |

| PROG               | 48                                      | 1     | <b>Programming mode write strobe</b><br>This input is used in programming mode as a write strobe for<br>OTP memory program and lock bit write operations. During<br>basic programming mode selection a low level must be applied<br>to PROG.                                                                                                                                                                        |

| EA/V <sub>PP</sub> | 49                                      | 1     | <b>External Access / Programming voltage</b><br>This pin must be at 11.5 V ( $V_{PP}$ ) voltage level during<br>programming of an OTP memory byte or lock bit. During an<br>OTP memory read operation this pin must be at high level ( $V_{IH}$ ).<br>This pin is also used for basic programming mode selection. At<br>basic programming mode selection a low level must be applied<br>to $\overline{EA}/V_{PP}$ . |

| D0 - 7             | 52 - 58                                 | I/O   | <b>Data lines 0-7</b><br>During programming mode, data bytes are read or written from<br>or to the C515C-8E via the bidirectional D0-7 which are located<br>at port 0.                                                                                                                                                                                                                                              |

| V <sub>SS</sub>    | 13, 34, 35,<br>51, 70                   | _     | <b>Circuit ground potential</b><br>must be applied to these pins in programming mode.                                                                                                                                                                                                                                                                                                                               |

| V <sub>cc</sub>    | 14, 32, 33,<br>50, 69                   | -     | <b>Power supply terminal</b><br>must be applied to these pins in programming mode.                                                                                                                                                                                                                                                                                                                                  |

| N.C.               | 2-12, 20-31,<br>46, 60-67, 69,<br>71-80 | _     | <b>Not Connected</b><br>These pins should not be connected in programming mode.                                                                                                                                                                                                                                                                                                                                     |

\*) I = Input O = Output

#### 4 Programming Mode Selection

The selection for the OTP programming mode can be separated into two different parts :

- Basic programming mode selection

- Access mode selection

With the basic programming mode selection the device is put into the mode in which it is possible to access the OTP memory through the programming interface logic. Further, after selection of the basic programming mode, OTP memory accesses are executed by using one of the access modes. These access modes are OTP memory byte program/read, version byte read, and program/read lock byte operations.

#### 4.1 Basic Programming Mode Selection

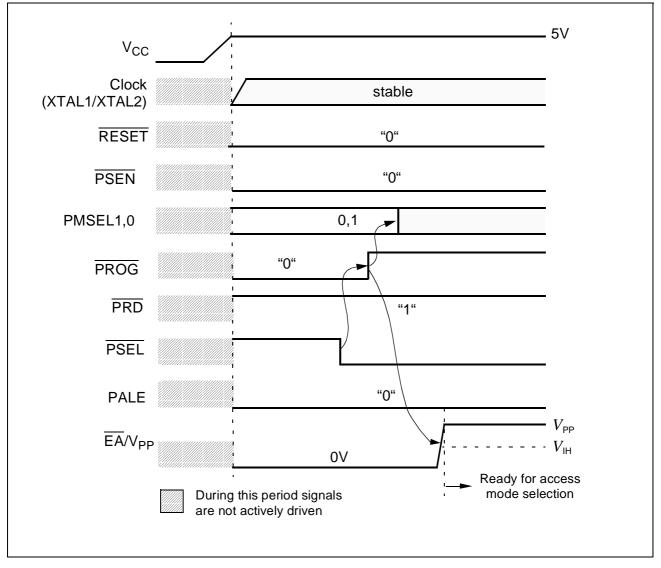

The basic programming mode selection scheme is shown in figure 3.

#### Figure 3 Basic Programming Mode Selection

The basic programming mode is selected by executing the following steps :

- With a stable V<sub>CC</sub> and a clock signal applied to the XTAL pins; the RESET and PSEN pins are set to "0" level.

- PROG, PALE, PMSEL1 and EA/V<sub>PP</sub> are set to "0" level; PRD, PSEL, and PMSEL0 are set to "1" level.

- PSEL is set to from "1" to "0" level and thereafter PROG is switched to "1" level.

- PMSEL1,0 can now be changed; after EA/V<sub>PP</sub> has been set to V<sub>IH</sub> high level or to V<sub>PP</sub> the OTP memory is ready for access.

The pins  $\overrightarrow{\text{RESET}}$  and  $\overrightarrow{\text{PSEN}}$  must stay at static "0" signal level during the whole programming mode. With a falling edge of  $\overrightarrow{\text{PSEL}}$  the logic state of  $\overrightarrow{\text{PROG}}$  and  $\overrightarrow{\text{EA}/V}_{\text{PP}}$  is internally latched. These two signals are now used as programming write pulse signal ( $\overrightarrow{\text{PROG}}$ ) and as programming voltage input pin  $V_{\text{PP}}$ . After the falling edge of  $\overrightarrow{\text{PSEL}}$ ,  $\overrightarrow{\text{PSEL}}$  must stay at "0" state during all programming operations.

#### 4.2 OTP Memory Access Mode Selection

When the C515C-8E has been put into the programming mode using the basic programming mode selection, several access modes of the OTP memory programming interface are available. The conditions for the different control signals of these access modes are listed in **table 2**.

### Table 2

|                         | EA/             | <b></b> |     | PMSEL |   | Address                     | Data      |  |

|-------------------------|-----------------|---------|-----|-------|---|-----------------------------|-----------|--|

| Access Mode             | V <sub>PP</sub> | PROG    | PRD | 1     | 0 | (Port 2)                    | (Port 0)  |  |

| Program OTP memory byte | V <sub>PP</sub> |         | Н   | н     | Н | A0-7                        | D0-7      |  |

| Read OTP memory byte    | V <sub>IH</sub> | Н       |     |       |   | A8-15                       |           |  |

| Program OTP lock bits   | V <sub>PP</sub> |         | Н   | н     | L | -                           | D1,D0 see |  |

| Read OTP lock bits      | V <sub>IH</sub> | Н       |     |       |   |                             | table 3   |  |

| Read OTP version byte   | V <sub>IH</sub> | Н       | Ţ   | L     | Н | Byte addr.<br>of sign. byte | D0-7      |  |

#### Access Modes Selection

The access modes from the table above are basically selected by setting the two PMSEL1,0 lines to the required logic level. The PROG and PRD signal are the write and read strobe signal. Data is transferred via port 0 and addresses are applied to port 2.

The following sections describe the details of the different access modes.

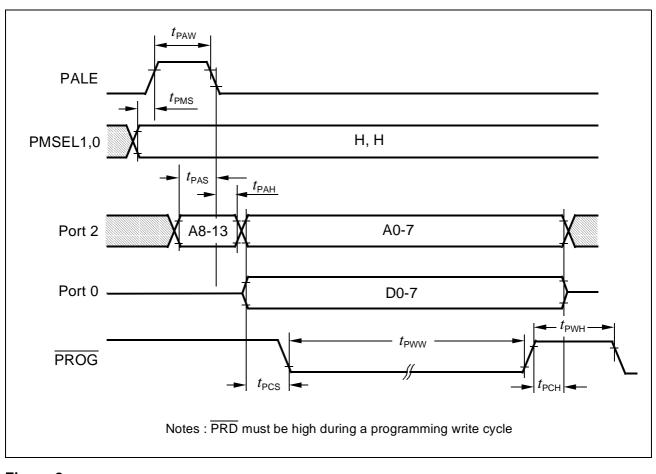

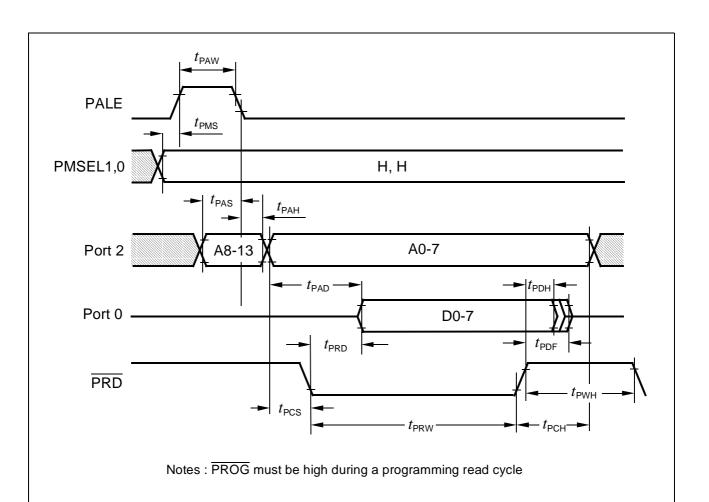

#### 4.2.1 Program / Read OTP Memory Bytes

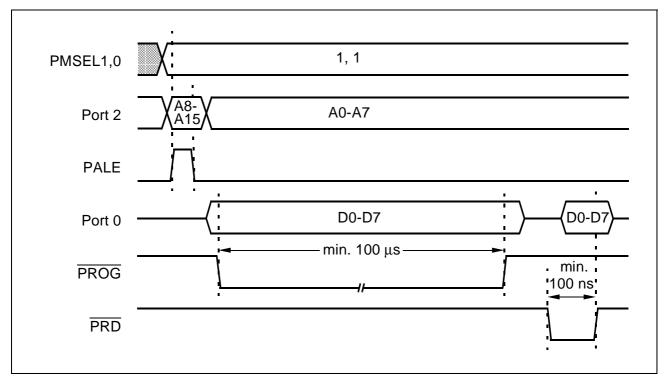

The program/read OTP memory byte access mode is defined by PMSEL1,0 = 1,1. It is initiated when the PMSEL1,0 = 1,1 is valid at the rising edge of PALE. With the falling edge of PALE the upper addresses A8-A15 of the 16-bit OTP memory address are latched. After A8-A15 has been latched, A0-A7 is put on the address bus (port 2). A0-A7 must be stable when PROG is low or PRD is low. If subsequent OTP address locations are accessed with constant address information at the high address lines A8-15, A8-A15 must only be latched once (page address mechanism).

**Figure 4** shows a typical OTP memory programming cycle with a following OTP memory read operation. In this example A0-A15 of the read operation are identical to A8-A15 of the preceeding programming operation.

#### Figure 4 Programming / Verify OTP Memory Access Waveform

If the address lines A8-A15 must be updated, PALE must be activated for the latching of the new A8-A15 value. Control, address, and data information must only be switched when the PROG and PRD signals are at high level. The PALE high pulse must always be executed if a different access mode has been used prior to the actual access mode.

## SIEMENS

**Figure 5** shows a waveform example of the program/read mode access for several OTP memory bytes. In this example OTP memory locations  $3FD_H$  to  $400_H$  are programmed. Thereafter, OTP memory locations  $400_H$  and  $3FD_H$  are read.

| PMSEL1,0 |    |        |        |        | 1, 1 |        |        |    |      |   |

|----------|----|--------|--------|--------|------|--------|--------|----|------|---|

| PALE     |    |        |        | [      |      |        |        | Л  |      |   |

|          | ↓  | 3FD    | 3FE    | 3FF    | ↓    | 400    | 400    | ↓  | 3FD  | Ì |

| Port 2   | 03 | FD     | FE     | FF     | 04   | 00     | 00     | 03 | FD   |   |

| Port 0   |    | Data 1 | Data 2 | Data 3 |      | Data 4 | Data 4 |    | Data | 1 |

| PROG     |    | ٦,٢    | ,      | ,      |      | ,      |        |    |      |   |

| PRD      |    |        |        |        |      |        |        |    |      |   |

|          |    |        |        |        |      |        |        |    |      |   |

#### Figure 5

Typical OTP Memory Programming/Verify Access Waveform

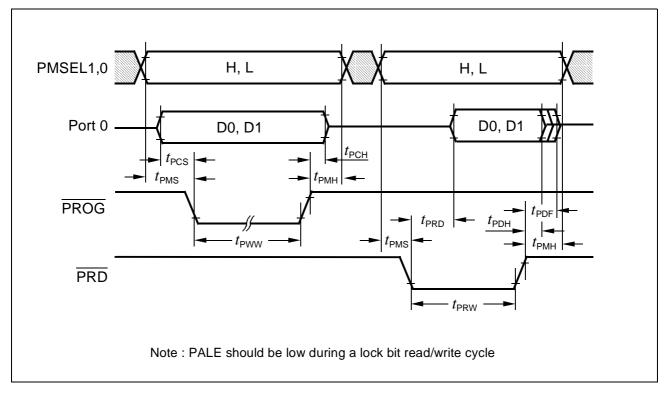

#### 4.2.2 Lock Bits Programming / Read

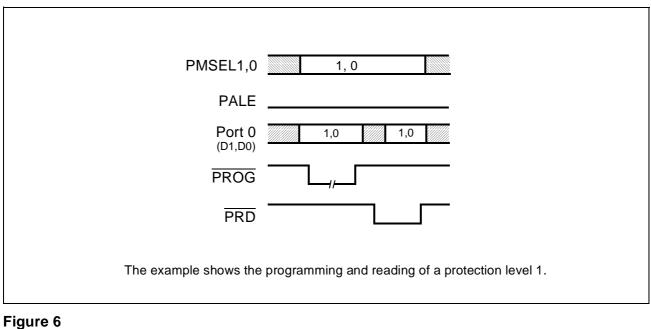

The C515C-8E has two programmable lock bits which, when programmed according **table 3**, provide four levels of protection for the on-chip OTP code memory. The state of the lock bits can also be read.

#### Table 3 Lock Bit Protection Types

| Lock Bits at D1,D0 |    | Protection | Protection Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D1                 | D0 | Level      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1                  | 1  | Level 0    | The OTP lock feature is disabled. During normal operation of the C515C-8E, the state of the $\overline{EA}$ pin is not latched on reset.                                                                                                                                                                                                                                                                                                                                                     |

| 1                  | 0  | Level 1    | During normal operation of the C515C-8E, MOVC instructions<br>executed from external program memory are disabled from<br>fetching code bytes from internal memory. EA is sampled and<br>latched on reset. An OTP memory read operation is only<br>possible according to ROM verification mode 2, as it is defined<br>for a protected ROM version of the C515C-8R (see OTP<br>verification mode 2 on page 27). Further programming of the<br>OTP memory is disabled (reprogramming security). |

| 0                  | 1  | Level 2    | Same as level 1, but also OTP memory read operation using ROM verification mode 2 is disabled.                                                                                                                                                                                                                                                                                                                                                                                               |

| 0                  | 0  | Level 3    | Same as level 2; but additionally external code execution by<br>setting EA=low during normal operation of the C515C-8E is no<br>more possible.<br>External code execution, which is initiated by an internal<br>program (e.g. by an internal jump instruction above the ROM<br>boundary), is still possible.                                                                                                                                                                                 |

**Note :** A 1 means that the lock bit is unprogrammed. 0 means that lock bit is programmed.

For a OTP verify operation at protection level 1, the C515C-8E must be put into the ROM verification mode 2. This mode is selected as defined in the C515C User' Manual 08.96 at pages 4-11 and 4-12.

If a device is programmed with protection level 2 or 3, it is no more possible to verify the OTP content of a customer rejected (FAR) OTP device.

When a protection level has been activated by programming of the lock bits, the basic programming mode must be left for activation of the protection mechanisms. This means, after the activation of a protection level further OTP program/verify operations are still possible if the basic programming mode is maintained.

**Figure 6** shows the waveform of a lock bit write/read access. For a simple drawing, the  $\overline{PROG}$  pulse is shortened. In reality, for Lock Bit programming, a 100µs  $\overline{PROG}$  low puls must be applied.

### Write/Read Lock Bit Waveform

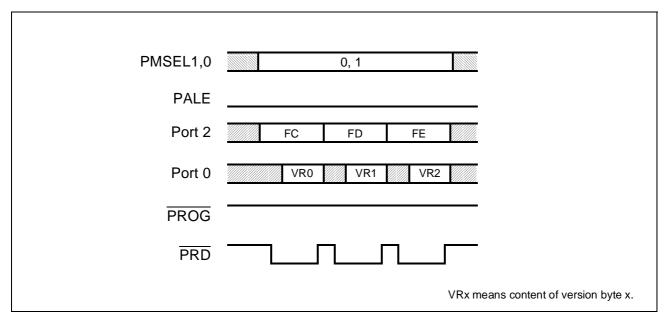

#### 4.2.3 Access of Version Bytes

The C515C-8E provides three version bytes at address locations  $FC_H$ ,  $FD_H$ , and  $FE_H$ . The information stored in the version bytes, is defined by the mask of each microcontroller step, Therefore, the version bytes can be read but not written. The three version bytes hold information as manufacturer code, device type, and stepping code.

For reading of the version bytes the control lines must be used according **table 2** and **figure 7**. The address of the version byte must be applied at the port 1 address lines. PALE must not be activated.

#### Figure 7 Read Version Byte(s) Waveform

Version bytes are typically used by programming systems for adapting the programming firmware to specifc device characteristics such as OTP size etc.

Note: The 3 version bytes are implemented in a way that they can be also read during normal program execution mode as a mapped SFR when bit RMAP in SFR SYSCON is set. The SFR addresses of the version bytes in normal mode are identical to the addresses which are used in programming mode. Therefore, in normal operating mode of the C515C-8E, the SFR locations which hold the signature bytes are also referenced as version registers.

The first step of the C515C-8E will contain the following information at the signature bytes :

| Name                                | Address         | Value           |

|-------------------------------------|-----------------|-----------------|

| Version Byte 0 = Version Register 0 | FCH             | C5 <sub>H</sub> |

| Version Byte 1 = Version Register 1 | FD <sub>H</sub> | 95 <sub>H</sub> |

| Version Byte 2 = Version Register 2 | FEH             | 01 <sub>H</sub> |

Future steppings of the C515C-8E will typically have a different version byte 2 (incremented value).

#### 5 Device Specifications

#### 5.1 Absolute Maximum Ratings

| Ambient temperature under bias ( $T_{\rm A}$ )<br>Storage temperature ( $T_{\rm ST}$ )                                             |     |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Voltage on $V_{\rm CC}$ pins with respect to ground ( $V_{\rm SS}$ )<br>Voltage on any pin with respect to ground ( $V_{\rm SS}$ ) |     |

| Input current on any pin during overload condition<br>Absolute sum of all input currents during overload condition                 |     |

| Power dissipation                                                                                                                  | TBD |

#### Note:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage of the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for longer periods may affect device reliability. During overload conditions ( $V_{IN} > V_{CC}$  or  $V_{IN} < V_{SS}$ ) the Voltage on  $V_{CC}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

#### 5.2 DC Characteristics

$V_{\rm CC} = 5 \text{ V} + 10\%, -15\%; V_{\rm SS} = 0 \text{ V}$

$T_{\rm A} = 0$  to 70 °C  $T_{\rm A} = -40$  to 85 °C  $T_{\rm A} = -40$  to 110 °C

for the SAB-C515C-8E for the SAF-C515C-8E for the SAH-C515C-8E

| Parameter                                                                                                                               | Symbol                                                          | Limit Values                                                                                                      |                                                                                                                               | Unit             | Test Condition                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------|

|                                                                                                                                         |                                                                 | min.                                                                                                              | max.                                                                                                                          |                  |                                                                                                                 |

| Input low voltages<br>all exc. EA/V <sub>PP</sub> , RESET, HWPD<br>EA/V <sub>PP</sub> pin<br>RESET and HWPD pins<br>Port 5 in CMOS mode | $V_{\rm IL}$<br>$V_{\rm IL1}$<br>$V_{\rm IL2}$<br>$V_{\rm ILC}$ | - 0.5<br>- 0.5<br>- 0.5<br>- 0.5                                                                                  | $\begin{array}{c} 0.2 \ V_{\rm CC} - 0.1 \\ 0.2 \ V_{\rm CC} - 0.3 \\ 0.2 \ V_{\rm CC} + 0.1 \\ 0.3 \ V_{\rm CC} \end{array}$ | V<br>V<br>V<br>V | -<br>-<br>-                                                                                                     |

| Input high voltages<br>all except XTAL2, RESET, and<br>HWPD)<br>XTAL2 pin<br>RESET and HWPD pins<br>Port 5 in CMOS mode                 | $V_{\rm IH}$<br>$V_{\rm IH1}$<br>$V_{\rm IH2}$<br>$V_{\rm IHC}$ | $\begin{array}{c} 0.2 \ V_{\rm CC} + 0.9 \\ 0.7 \ V_{\rm CC} \\ 0.6 \ V_{\rm CC} \\ 0.7 \ V_{\rm CC} \end{array}$ | $V_{cc} + 0.5$<br>$V_{cc} + 0.5$<br>$V_{cc} + 0.5$<br>$V_{cc} + 0.5$                                                          | V<br>V<br>V<br>V | -<br>-<br>-                                                                                                     |

| Output low voltages<br>Ports 1, 2, 3, 4, 5, 7 (incl. CMOS)<br>Port 0, ALE, PSEN, CPUR<br>P4.1, P4.3 in push-pull mode                   | $V_{\rm OL}$<br>$V_{\rm OL1}$<br>$V_{\rm OL3}$                  | -<br>-<br>-                                                                                                       | 0.45<br>0.45<br>0.45                                                                                                          | V<br>V<br>V      | $I_{OL}$ = 1.6 mA <sup>1)</sup><br>$I_{OL}$ = 3.2 mA <sup>1)</sup><br>$I_{OL}$ = 3.75 mA <sup>1)</sup>          |

| Output high voltages<br>Ports 1, 2, 3, 4, 5, 7<br>Port 0 in external bus mode,                                                          | V <sub>OH</sub><br>V <sub>OH2</sub>                             | 2.4<br>0.9 V <sub>cc</sub><br>2.4                                                                                 | -                                                                                                                             | V<br>V<br>V      | $I_{OH} = -80 \ \mu A$<br>$I_{OH} = -10 \ \mu A^{)}$<br>$I_{OH} = -800 \ \mu A^{2)}$                            |

| ALE, PSEN, CPUR<br>Port 5 in CMOS mode<br>P4.1, P4.3 in push-pull mode                                                                  | $V_{ m OH2}$<br>$V_{ m OHC}$<br>$V_{ m OH3}$                    | $\begin{array}{c} 0.9 \ V_{\rm CC} \\ 0.9 \ V_{\rm CC} \\ 0.9 \ V_{\rm CC} \end{array}$                           | -<br>-<br>-                                                                                                                   | V<br>V<br>V      | $I_{OH} = -80 \ \mu A^{2}$<br>$I_{OH} = -800 \ \mu A^{2}$<br>$I_{OH} = -800 \ \mu A$<br>$I_{OH} = -833 \ \mu A$ |

| Logic 0 input current<br>Ports 1, 2, 3, 4, 5, 7                                                                                         | $I_{IL}$                                                        | - 10                                                                                                              | - 70                                                                                                                          | μA               | $V_{\rm IN}$ = 0.45 V                                                                                           |

| Logical 0-to-1 transition current<br>Ports 1, 2, 3, 4, 5, 7                                                                             | I <sub>TL</sub>                                                 | - 65                                                                                                              | - 650                                                                                                                         | μA               | $V_{\rm IN} = 2  \rm V$                                                                                         |

| Input leakage current Port 0,<br>EA/V <sub>PP</sub> , P6, HWPD, AIN0-7                                                                  | I <sub>LI</sub>                                                 | _                                                                                                                 | ± 1                                                                                                                           | μA               | $0.45 < V_{\rm IN} < V_{\rm CC}$                                                                                |

| Inp <u>ut low c</u> urrent<br>To RESET for reset<br>XTAL2<br>PE/SWD                                                                     | $I_{L12}$ $I_{L13}$ $I_{L14}$                                   | -<br>-<br>-                                                                                                       | - 100<br>- 15<br>- 20                                                                                                         | μΑ<br>μΑ<br>μΑ   | $V_{\rm IN} = 0.45 \ {\rm V}$<br>$V_{\rm IN} = 0.45 \ {\rm V}$<br>$V_{\rm IN} = 0.45 \ {\rm V}$                 |

| Pin capacitance                                                                                                                         | C <sub>IO</sub>                                                 | -                                                                                                                 | 10                                                                                                                            | pF               | $f_{\rm c}$ = 1 MHz,<br>$T_{\rm A}$ = 25 °C                                                                     |

| Overload current                                                                                                                        | I <sub>OV</sub>                                                 | -                                                                                                                 | ±5                                                                                                                            | mA               | 7) 8)                                                                                                           |

| Programming voltage                                                                                                                     | $V_{\rm PP}$                                                    | 10.9                                                                                                              | 12.1                                                                                                                          | V                | 11.5 V ± 5%                                                                                                     |

| Parameter                                                          | Symbol                 | Limit Values       |      | Unit | <b>Test Condition</b>               |

|--------------------------------------------------------------------|------------------------|--------------------|------|------|-------------------------------------|

|                                                                    |                        | typ. <sup>9)</sup> | max. |      |                                     |

| Power supply current:                                              |                        |                    |      |      |                                     |

| Active mode, 6 MHz <sup>6)</sup>                                   | <i>I</i> <sub>CC</sub> | TBD                | TBD  | mA   | $V_{\rm CC}$ = 5 V, <sup>4)</sup>   |

| Idle mode, 6 MHz <sup>6)</sup>                                     | I <sub>CC</sub>        | TBD                | TBD  | mA   | $V_{\rm CC} = 5  \rm V,  ^{5)}$     |

| Active mode, 10 MHz <sup>6)</sup>                                  | I <sub>CC</sub>        | TBD                | TBD  | mA   | $V_{\rm CC} = 5  {\rm V},  {}^{4)}$ |

| Idle mode, 10 MHz <sup>6)</sup>                                    | I <sub>CC</sub>        | TBD                | TBD  | mA   | $V_{\rm CC}$ = 5 V, <sup>5)</sup>   |

| Power-down mode                                                    | $I_{PD}$               | -                  | 50   | μA   | $V_{\rm CC}$ = 25.5 V <sup>3)</sup> |

| Power supply current at $\overline{EA}/V_{PP}$ in programming mode | I <sub>CCP</sub>       | -                  | 30   | mA   |                                     |

- Capacitive loading on ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub> of ALE and port 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operation. In the worst case (capacitive loading > 100 pF), the noise pulse on ALE line may exceed 0.8 V. In such cases it may be desirable to qualify ALE with a schmitt-trigger, or use an address latch with a schmitt-trigger strobe input.

- 2) Capacitive loading on ports 0 and 2 may cause the  $V_{OH}$  on ALE and  $\overline{PSEN}$  to momentarily fall below the 0.9  $V_{CC}$  specification when the address lines are stabilizing.

- 3)  $I_{PD}$  (power-down mode) is measured under following conditions: EA = RESET = Port 0 = Port 6 =  $V_{CC}$ ; XTAL1 = N.C.; XTAL2 =  $V_{SS}$ ;  $\overline{PE}/SWD = V_{SS}$ ;  $\overline{HWPD} = V_{CC}$ ;  $V_{AGND} = V_{SS}$ ;  $V_{AREF} = V_{CC}$ ; all other pins are disconnected.  $I_{PD}$  (hardware power-down mode) is independent of any particular pin connection.

- 4) I<sub>CC</sub> (active mode) is measured with: <u>XTAL2 driven with</u> t<sub>CLCH</sub>, t<sub>CHCL</sub> = 5 ns , V<sub>IL</sub> = V<sub>SS</sub> + 0.5 V, V<sub>IH</sub> = V<sub>CC</sub> - 0.5 V; XTAL1 = N.C.; EA = PE/SWD = Port 0 = Port 6 = V<sub>CC</sub>; HWPD = V<sub>CC</sub>; RESET = V<sub>SS</sub>; all other pins are disconnected.

- 5)  $I_{CC}$  (idle mode) is measured with all output pins disconnected and with all peripherals disabled; <u>XTAL2</u> driven with  $t_{CLCH}$ ,  $t_{CHCL} = 5$  ns,  $V_{IL} = V_{SS} + 0.5$  V,  $V_{IH} = V_{CC} - 0.5$  V; XTAL1 = N.C.; <u>RESET</u> =  $V_{CC}$ ; EA =  $V_{SS}$ ; Port0 =  $V_{CC}$ ; all other pins are disconnected;

- 6)  $I_{CC max}$  at other frequencies is given by: active mode: TBD idle mode: TBD where  $f_{osc}$  is the oscillator frequency in MHz.  $I_{CC}$  values are given in mA and measured at  $V_{CC}$  = 5 V.

- 7) Overload conditions occur if the standard operating conditions are exceeded, ie. the voltage on any pin exceeds the specified range (i.e.  $V_{OV} > V_{CC} + 0.5$  V or  $V_{OV} < V_{SS} 0.5$  V). The supply voltage  $V_{CC}$  and  $V_{SS}$  must remain within the specified limits. The absolute sum of input currents on all port pins may not exceed 50 mA.

- 8) Not 100% tested, guaranteed by design characterization

- 9) The typical  $I_{CC}$  values are periodically measured at  $T_{A}$  = +25 °C but not 100% tested.

#### 5.3 A/D Converter Characteristics

$V_{\rm CC}$  = 5 V + 10%, - 15%;  $V_{\rm SS}$  = 0 V

$T_{\rm A} = 0$  to 70 °C  $T_{\rm A} = -40$  to 85 °C  $T_{\rm A} = -40$  to 110 °C

for the SAB-C515C-8E for the SAF-C515C-8E for the SAH-C515C-8E

4 V  $\leq V_{\text{AREF}} \leq V_{\text{CC}}$ +0.1 V ;  $V_{\text{SS}}$ -0.1 V  $\leq V_{\text{AGND}} \leq V_{\text{SS}}$ +0.2 V

| Parameter                                       | Symbol            | Limi       | Limit Values                                              |     | Test Condition                                                |  |

|-------------------------------------------------|-------------------|------------|-----------------------------------------------------------|-----|---------------------------------------------------------------|--|

|                                                 |                   | min.       | max.                                                      |     |                                                               |  |

| Analog input voltage                            | $V_{AIN}$         | $V_{AGND}$ | $V_{AREF}$                                                | V   | 1)                                                            |  |

| Sample time                                     | t <sub>S</sub>    | -          | 16 x <i>t</i> <sub>IN</sub><br>8 x <i>t</i> <sub>IN</sub> | ns  | Prescaler $\div$ 8<br>Prescaler $\div$ 4 <sup>2)</sup>        |  |

| Conversion cycle time                           | t <sub>ADCC</sub> | -          | 96 x t <sub>IN</sub><br>48 x t <sub>IN</sub>              | ns  | Prescaler $\div$ 8<br>Prescaler $\div$ 4 <sup>3)</sup>        |  |

| Total unadjusted error                          | $T_{\sf UE}$      | -          | ± 2                                                       | LSB | $V_{SS}$ +0.5V $\leq V_{IN} \leq V_{CC}$ -0.5V <sup>4</sup> ) |  |

| Internal resistance of reference voltage source | R <sub>AREF</sub> | -          | t <sub>ADC</sub> / 250<br>- 0.25                          | kΩ  | <i>t</i> <sub>ADC</sub> in [ns] <sup>5) 6)</sup>              |  |

| Internal resistance of analog source            | R <sub>ASRC</sub> | -          | t <sub>s</sub> / 500<br>- 0.25                            | kΩ  | <i>t</i> <sub>s</sub> in [ns] <sup>2) 6)</sup>                |  |

| ADC input capacitance                           | $C_{AIN}$         | _          | 50                                                        | pF  | 6)                                                            |  |

Notes see next page.

#### **Clock calculation table :**

| Clock Prescaler<br>Ratio | ADCL | <sup>t</sup> ADC    | t <sub>S</sub>       | tADCC                |

|--------------------------|------|---------------------|----------------------|----------------------|

| ÷8                       | 1    | 8 x t <sub>IN</sub> | 16 x t <sub>IN</sub> | 96 x t <sub>IN</sub> |

| ÷ 4                      | 0    | 4 x t <sub>IN</sub> | 8 x t <sub>IN</sub>  | 48 x t <sub>IN</sub> |

Further timing conditions :  $t_{ADC} min = 500 ns$

$t_{IN} = 1 / f_{OSC} = t_{CLP}$

#### Notes:

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- 2) During the sample time the input capacitance C<sub>AIN</sub> can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach their final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result.

- This parameter includes the sample time t<sub>S</sub>, the time for determining the digital result and the time for the calibration. Values for the conversion clock t<sub>ADC</sub> depend on programming and can be taken from the table on the previous page.

- 4) T<sub>UE</sub> is tested at V<sub>AREF</sub> = 5.0 V, V<sub>AGND</sub> = 0 V, V<sub>CC</sub> = 4.9 V. It is guaranteed by design characterization for all other voltages within the defined voltage range.

If an overload condition occurs on maximum 2 not selected analog input pins and the absolute sum of input overload currents on all analog input pins does not exceed 10 mA, an additional conversion error of 1/2 LSB is permissible.

- 5) During the conversion the ADC's capacitance must be repeatedly charged or discharged. The internal resistance of the reference source must allow the capacitance to reach their final voltage level within the indicated time. The maximum internal resistance results from the programmed conversion timing.

- 6) Not 100% tested, but guaranteed by design characterization.

#### 5.4 AC Characteristics

$V_{\rm CC}$  = 5 V + 10%, - 15%;  $V_{\rm SS}$  = 0 V

| V | $T_{\rm A}$ = 0 to 70 °C       | for the SAB-C515C-8E |

|---|--------------------------------|----------------------|

|   | $T_{\rm A}$ = $-40$ to 85 °C   | for the SAF-C515C-8E |

|   | $T_{\rm A}$ = $-$ 40 to 110 °C | for the SAH-C515C-8E |

( $C_{L}$  for port 0, ALE and  $\overline{PSEN}$  outputs = 100 pF;  $C_{L}$  for all other outputs = 80 pF)

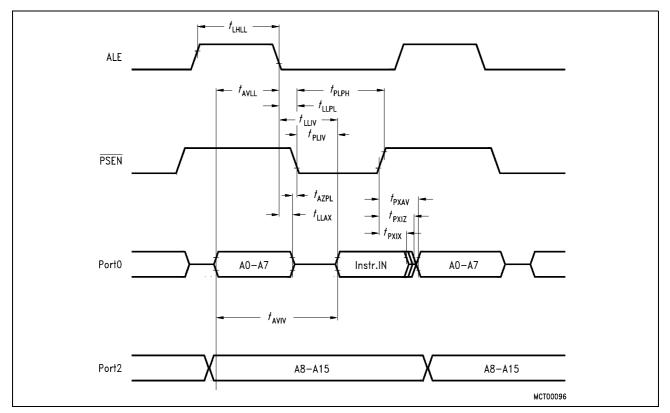

#### **Program Memory Characteristics**

| Parameter                          | Symbol                   | Limit Values                             |      |                                              |                                    |    |

|------------------------------------|--------------------------|------------------------------------------|------|----------------------------------------------|------------------------------------|----|

|                                    |                          | 10-MHz clock<br>Duty Cycle<br>0.4 to 0.6 |      | Variable Clock<br>1/CLP = 2 MHz to<br>10 MHz |                                    |    |

|                                    |                          | min.                                     | max. | min.                                         | max.                               |    |

| ALE pulse width                    | t <sub>LHLL</sub>        | 60                                       | -    | CLP - 40                                     | _                                  | ns |

| Address setup to ALE               | <i>t</i> <sub>AVLL</sub> | 15                                       | _    | TCL <sub>Hmin</sub> -25                      | -                                  | ns |

| Address hold after ALE             | t <sub>LLAX</sub>        | 15                                       | _    | TCL <sub>Hmin</sub> -25                      | _                                  | ns |

| ALE to valid instruction in        | t <sub>LLIV</sub>        | _                                        | 113  | -                                            | 2 CLP - 87                         | ns |

| ALE to PSEN                        | t <sub>LLPL</sub>        | 20                                       | _    | TCL <sub>Lmin</sub> -20                      | _                                  | ns |

| PSEN pulse width                   | t <sub>PLPH</sub>        | 115                                      | -    | CLP+<br>TCL <sub>Hmin</sub> -30              | _                                  | ns |

| PSEN to valid instruction in       | t <sub>PLIV</sub>        | -                                        | 75   | _                                            | CLP+<br>TCL <sub>Hmin</sub> - 65   | ns |

| Input instruction hold after PSEN  | t <sub>PXIX</sub>        | 0                                        | _    | 0                                            | _                                  | ns |

| Input instruction float after PSEN | t <sub>PXIZ</sub> *)     | _                                        | 30   | -                                            | TCL <sub>Lmin</sub> -10            | ns |

| Address valid after PSEN           | t <sub>PXAV</sub> *)     | 35                                       | _    | TCL <sub>Lmin</sub> - 5                      | _                                  | ns |

| Address to valid instruction in    | t <sub>AVIV</sub>        | -                                        | 180  | _                                            | 2 CLP +<br>TCL <sub>Hmin</sub> -60 | ns |

| Address float to PSEN              | t <sub>AZPL</sub>        | 0                                        |      | 0                                            | -                                  | ns |

\*) Interfacing the C515C to devices with float times up to 35 ns is permissible. This limited bus contention will not cause any damage to port 0 drivers.

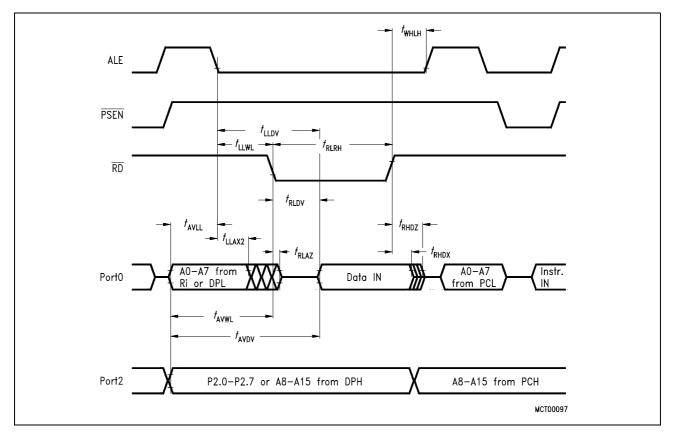

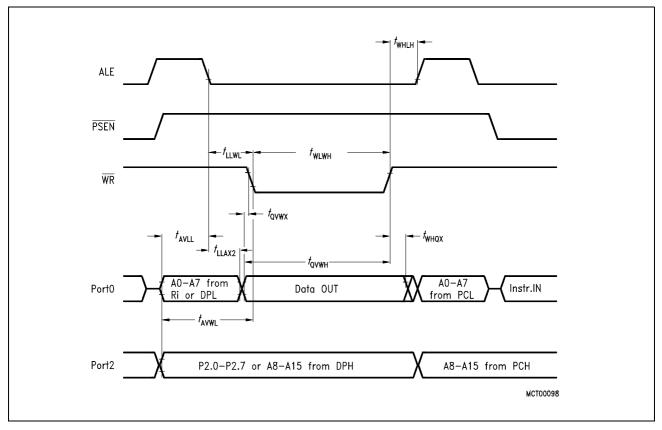

#### **External Data Memory Characteristics**

| Parameter                         | Symbol                   | Limit Values                                |      |                                      |                                     |    |  |

|-----------------------------------|--------------------------|---------------------------------------------|------|--------------------------------------|-------------------------------------|----|--|

|                                   |                          | 10-MHz<br>clock<br>Duty Cycle<br>0.4 to 0.6 |      | Variabl<br>1/CLP= 2 Mi               |                                     |    |  |

|                                   |                          | min.                                        | max. | min.                                 | max.                                |    |  |

| RD pulse width                    | t <sub>RLRH</sub>        | 230                                         | _    | 3 CLP - 70                           | -                                   | ns |  |

| WR pulse width                    | t <sub>WLWH</sub>        | 230                                         | -    | 3 CLP - 70                           | -                                   | ns |  |

| Address hold after ALE            | t <sub>LLAX2</sub>       | 48                                          | _    | CLP - 15                             | -                                   | ns |  |

| RD to valid data in               | t <sub>RLDV</sub>        | -                                           | 150  | _                                    | 2 CLP+<br>TCL <sub>Hmin</sub> - 90  | ns |  |

| Data hold after RD                | t <sub>RHDX</sub>        | 0                                           |      | 0                                    | -                                   | ns |  |

| Data float after RD               | t <sub>RHDZ</sub>        | _                                           | 80   | _                                    | CLP - 20                            | ns |  |

| ALE to valid data in              | t <sub>LLDV</sub>        | _                                           | 267  | _                                    | 4 CLP - 133                         | ns |  |

| Address to valid data in          | $t_{\rm AVDV}$           | -                                           | 285  | -                                    | 4 CLP +<br>TCL <sub>Hmin</sub> -155 | ns |  |

| ALE to WR or RD                   | t <sub>LLWL</sub>        | 90                                          | 190  | CLP +<br>TCL <sub>Lmin</sub> - 50    | CLP+<br>TCL <sub>Lmin</sub> + 50    | ns |  |

| Address valid to WR               | <i>t</i> <sub>AVWL</sub> | 103                                         | _    | 2 CLP - 97                           | -                                   | ns |  |

| WR or RD high to ALE high         | t <sub>WHLH</sub>        | 15                                          | 65   | TCL <sub>Hmin</sub> - 25             | TCL <sub>Hmin</sub> + 25            | ns |  |

| Data valid to WR transition       | <i>t</i> <sub>QVWX</sub> | 5                                           | _    | TCL <sub>Lmin</sub> - 35             | -                                   | ns |  |

| Data setup before $\overline{WR}$ | t <sub>QVWH</sub>        | 218                                         | -    | 3 CLP +<br>TCL <sub>Lmin</sub> - 122 | -                                   | ns |  |

| Data hold after WR                | t <sub>WHQX</sub>        | 13                                          | -    | TCL <sub>Hmin</sub> - 27             | -                                   | ns |  |

| Address float after RD            | t <sub>RLAZ</sub>        | _                                           | 0    | _                                    | 0                                   | ns |  |

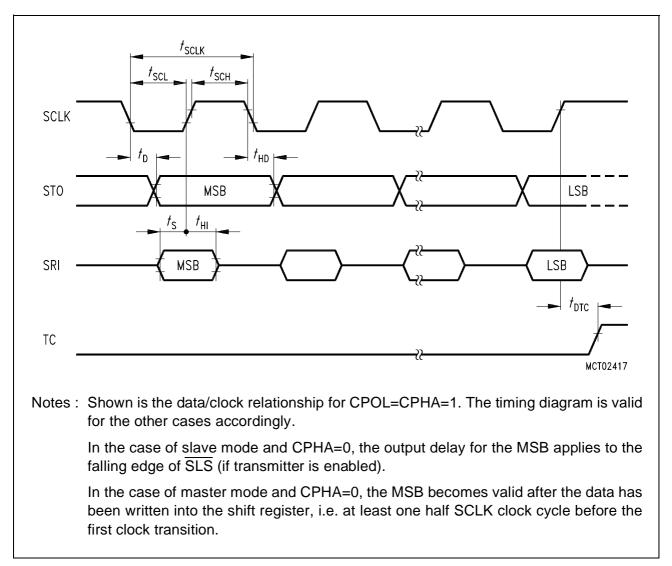

#### **SSC Interface Characteristics**

| Parameter                      | Symbol            |      | Unit  |    |

|--------------------------------|-------------------|------|-------|----|

|                                |                   | min. | max.  |    |

| Clock Cycle Time : Master Mode | t <sub>SCLK</sub> | 0.8  | _     | μs |

| Slave Mode                     | t <sub>SCLK</sub> | 1.0  | -     | μs |

| Clock high time                | t <sub>SCH</sub>  | 360  | -     | ns |

| Clock low time                 | t <sub>SCL</sub>  | 360  | -     | ns |

| Data output delay              | t <sub>D</sub>    | -    | 100   | ns |

| Data output hold               | t <sub>HO</sub>   | 0    | _     | ns |

| Data input setup               | t <sub>S</sub>    | 100  | -     | ns |

| Data input hold                | t <sub>HI</sub>   | 100  | _     | ns |

| TC bit set delay               | t <sub>DTC</sub>  | _    | 8 CLP | ns |

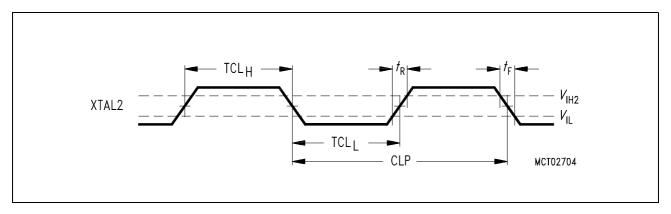

#### External Clock Drive at XTAL2

| Parameter S           | Symbol           |      | ock = 10 MHz<br>/cle 0.4 to 0.6 | Variable (<br>1/CLP = 2 | Unit                    |    |

|-----------------------|------------------|------|---------------------------------|-------------------------|-------------------------|----|

|                       |                  | min. | max.                            | min.                    | max.                    |    |

| Oscillator period     | CLP              | 100  | 100                             | 100                     | 500                     | ns |

| High time             | TCL <sub>H</sub> | 40   | _                               | 40                      | CLP-TCL <sub>L</sub>    | ns |

| Low time              | TCL∟             | 40   | _                               | 40                      | CLP-TCL <sub>H</sub>    | ns |

| Rise time             | t <sub>R</sub>   | _    | 12                              | -                       | 12                      | ns |

| Fall time             | t <sub>F</sub>   | _    | 12                              | -                       | 12                      | ns |

| Oscillator duty cycle | DC               | 0.4  | 0.6                             | 40 / CLP                | 1 - 40 / CLP            | —  |

| Clock cycle           | TCL              | 40   | 60                              | CLP * DC <sub>min</sub> | CLP * DC <sub>max</sub> | ns |

Note: The 10 MHz values in the tables are given as an example for a typical duty cycle variation of the oscillator clock from 0.4 to 0.6.

#### **Program Memory Read Cycle**

#### Data Memory Read Cycle

## SIEMENS

#### Data Memory Write Cycle

#### **External Clock Cycle**

#### **SSC Timing**

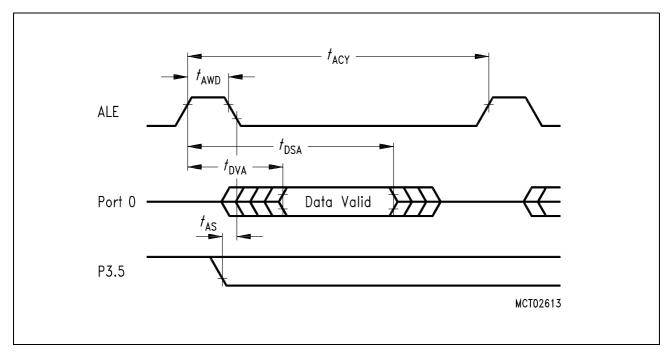

#### **OTP Verification Mode 2 (for Memory Verification in OTP Protection Level 1)**

| Parameter             | Symbol                  |       | Unit            |       |     |

|-----------------------|-------------------------|-------|-----------------|-------|-----|

|                       |                         | min.  | typ             | max.  |     |

| ALE pulse width       | <i>t</i> <sub>AWD</sub> | _     | CLP             | _     | ns  |

| ALE period            | t <sub>ACY</sub>        | _     | 6 CLP           | _     | ns  |

| Data valid after ALE  | t <sub>DVA</sub>        | _     | -               | 2 CLP | ns  |

| Data stable after ALE | t <sub>DSA</sub>        | 4 CLP | -               | _     | ns  |

| P3.5 setup to ALE low | t <sub>AS</sub>         | _     | t <sub>CL</sub> | _     | ns  |

| Oscillator frequency  | 1/ CLP                  | 4     | _               | 6     | MHz |

#### **ROM/OTP Verification Mode 2**

#### 5.5 OTP Memory Programming Mode Characteristics

$V_{\rm CC}$  = 5 V ± 10 %;  $V_{\rm PP}$  = 11.5 V ± 5 %;  $T_{\rm A}$  = 25 °C ± 10 °C

| Parameter                                         | Symbol            | L    | Unit |    |

|---------------------------------------------------|-------------------|------|------|----|

|                                                   |                   | min. | max. |    |

| ALE pulse width                                   | t <sub>PAW</sub>  | 35   | _    | ns |

| PMSEL setup to ALE rising edge                    | t <sub>PMS</sub>  | 10   | _    |    |

| Address setup to ALE, PROG, or PRD falling edge   | t <sub>PAS</sub>  | 10   | -    | ns |

| Address hold after ALE, PROG, or PRD falling edge | t <sub>PAH</sub>  | 10   | -    | ns |

| Address, data setup to PROG or PRD                | t <sub>PCS</sub>  | 100  | _    | ns |

| Address, data hold after PROG or PRD              | t <sub>PCH</sub>  | 0    | _    | ns |

| PMSEL setup to PROG or PRD                        | t <sub>PMS</sub>  | 10   | _    | ns |

| PMSEL hold after PROG or PRD                      | t <sub>PMH</sub>  | 10   | _    | ns |

| PROG pulse width                                  | t <sub>PWW</sub>  | 100  | -    | μs |

| PRD pulse width                                   | t <sub>PRW</sub>  | 100  | -    | ns |

| Address to valid data out                         | t <sub>PAD</sub>  | _    | 75   | ns |

| PRD to valid data out                             | t <sub>PRD</sub>  | -    | 20   | ns |

| Data hold after PRD                               | t <sub>PDH</sub>  | 0    | _    | ns |

| Data float after PRD                              | t <sub>PDF</sub>  | -    | 20   | ns |

| PROG high between two consecutive PROG low pulses | t <sub>PWH1</sub> | 1    | -    | μs |

| PRD high between two consecutive PRD low pulses   | t <sub>PWH2</sub> | 100  |      | ns |

| XTAL clock period                                 | t <sub>CLKP</sub> | TBD  |      | ns |

## SIEMENS

Figure 8 Programming Code Byte - Write Cycle Timing

C515C-8E

## SIEMENS

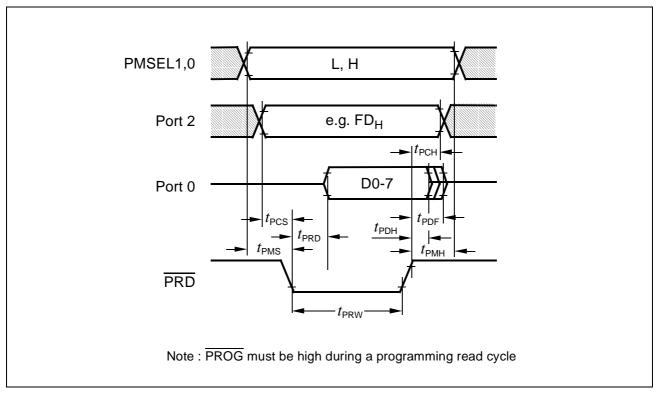

#### Figure 9 Verify Code Byte - Read Cycle Timing

C515C-8E

#### Figure 10 Lock Bit Access Timing

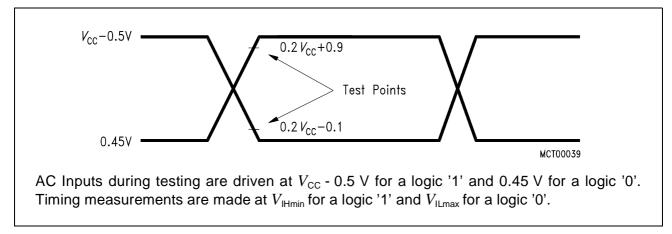

#### AC Testing: Input, Output Waveforms

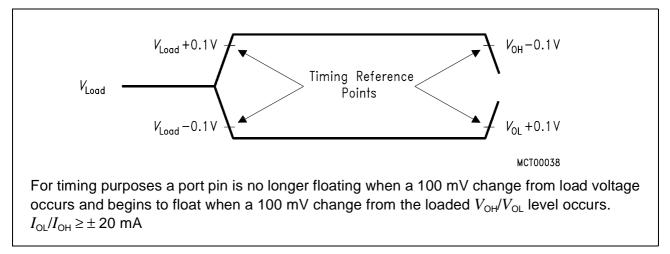

#### **AC Testing : Float Waveforms**

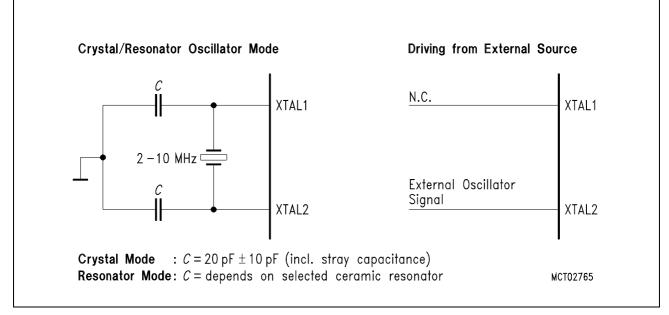

#### **Recommended Oscillator Circuits for Crystal Oscillator**

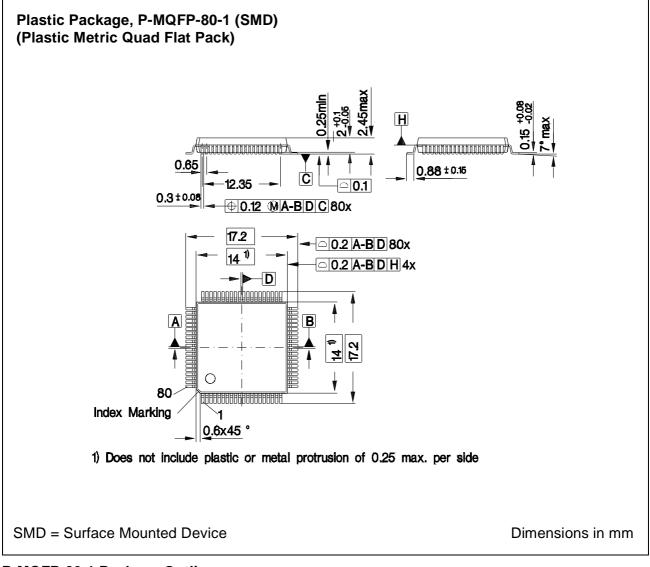

#### 5.6 Package Information

P-MQFP-80-1 Package Outline

#### 6 Addendum

#### Table 4

Cross Reference of Pins in Normal/Programming Mode

| Pin Number | Pin in Normal Mode | Pin in Programming Mode |

|------------|--------------------|-------------------------|

| 1          | RESET              | RESET                   |

| 15         | PMSEL0             | P3.0                    |

| 16         | PMSEL1             | P3.1                    |

| 17         | PSEL               | P3.2                    |

| 18         | PRD                | P3.3                    |

| 19         | PALE               | P3.4                    |

| 36         | XTAL2              | XTAL2                   |

| 37         | XTAL1              | XTAL1                   |

| 38 - 45    | A0/A8 - A7/A15     | P2.0 - P2.7             |

| 47         | PSEN               | PSEN                    |

| 48         | PROG               | ALE                     |

| 49         | EA/V <sub>PP</sub> | ĒĀ                      |

| 52 - 59    | D0 - D7            | P0.0 - P0.7             |