# 32 K $\times$ 8 Very Low Power CMOS SRAM Rad Tolerant

## Introduction

The M65656G is a very low power CMOS static RAM organized as  $32768 \times 8$  bits.

Atmel Wireless & Microcontrollers brings the solution for applications where fast computing is as mandatory as low consumption, such as aerospace electronics, portable instruments or embarked systems.

Using an array of six transistors (6T) memory cells, the M65656G combines an extremely low standby supply

current (Typical value =  $0.1 \ \mu$ A) with a fast access time at 40 ns. The high stability of the 6T cell provides excellent protection against soft errors due to noise.

Extra protection against heavy ions is given by the use of an epitaxial layer of a P substrate.

The M65656G is processed according to the methods of the latest revision of the MIL STD 883 (class B or S), ESA SCC 9000 and QML.

## Features

- Access time 40, 55 ns

- Very low power consumption active : 50 mW (typ) standby : 0.5  $\mu$ W (typ) data retention : 0.4  $\mu$ W (typ)

- Wide temperature range :  $-55 \text{ to} + 125^{\circ}\text{C}$

- 300 and 600 mils width package

- TTL compatible inputs and outputs

- Asynchronous

- Single 5 volt supply

- Equal cycle and access time

- Gated inputs : no pull-up/down resistors are required

## Interface

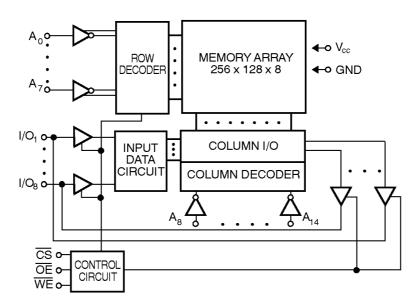

#### **Block Diagram**

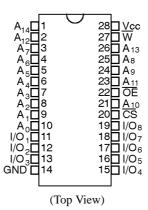

## **Pin Configuration**

Side Brazed 300 mils 28 pins Multilayer Flat Pack 28 pins 400 mils

#### **Pin Names**

| A <sub>0</sub> -A <sub>14</sub> : Address inputs |              | $\overline{\text{CS}}$ :  | Chip-Select   |

|--------------------------------------------------|--------------|---------------------------|---------------|

| I/O0-I/O7 :                                      | Input/Output | $\overline{\mathbf{W}}$ : | Write Enable  |

| V <sub>CC</sub> :                                | Power        | $\overline{OE}$ :         | Output Enable |

| GND :                                            | Ground       |                           |               |

## Truth Table

| CS | W | ŌĒ | INPUTS/<br>OUTPUTS | MODE                    |

|----|---|----|--------------------|-------------------------|

| Н  | Х | Х  | Z                  | Deselect/<br>POWER-DOWN |

| L  | Н | L  | DATA OUT           | Read                    |

| L  | L | Х  | DATA IN            | Write                   |

| L  | Н | Н  | Z                  | Output Disable          |

L = low, H = high, X = H or L, Z = high impedance

## **Electrical Characteristics**

## **Absolute Maximum Ratings**

| Supply voltage to GND potential : | $\dots \dots \dots -0.3 \text{ V to} + 7.0 \text{ V}$ |

|-----------------------------------|-------------------------------------------------------|

| Input or Output voltage applied : | (Gnd - 0.3 V) to $(Vcc + 0.3 V)$                      |

| Storage temperature :            | $\dots \dots \dots -65 \text{ °C to} + 150 \text{ °C}$ |

|----------------------------------|--------------------------------------------------------|

| Electro static discharge voltage |                                                        |

|                                  | METHOD 3015)                                           |

## **Operating Range**

|          | OPERATING VOLTAGE        | OPERATING TEMPERATURE |

|----------|--------------------------|-----------------------|

| Military | $V_{CC} = 5 V \pm 10 \%$ | -55 °C to $+125$ °C   |

## **DC Operating Conditions**

| PARAMETER | DESCRIPTION        | MINIMUM | TYPICAL | MAXIMUM   | UNIT |

|-----------|--------------------|---------|---------|-----------|------|

| Vcc       | Supply voltage     | 4.5     | 5.0     | 5.5       | V    |

| Gnd       | Ground             | 0.0     | 0.0     | 0.0       | V    |

| VIL (1)   | Input low voltage  | - 0.3   | 0.0     | 0.8       | V    |

| VIH(1)    | input high voltage | 2.2     | -       | Vcc + 0.3 | V    |

**Note :** 1. VIH max = Vcc + 0.3 V, VIL min = -0.3 V or -1.0 pulse 50 ns.

#### Capacitance

| PARAMETER | DESCRIPTION        | MINIMUM | TYPICAL | MAXIMUM | UNIT |

|-----------|--------------------|---------|---------|---------|------|

| Cin (2)   | Input capacitance  | _       | _       | 8       | pF   |

| Cout (2)  | Output capacitance | -       | _       | 12      | pF   |

Note: 2.  $TA = 25^{\circ}C$ , f = 1 MHz, Vcc = 5.0 V, these parameters are not tested.

#### **DC Parameter**

| PARAMETER | DESCRIPTION            | MINIMUM | TYPICAL | MAXIMUM | UNIT |

|-----------|------------------------|---------|---------|---------|------|

| IIX (3)   | Input leakage current  | - 1.0   | _       | 1.0     | μΑ   |

| IOZ(3)    | Output leakage current | - 1.0   | _       | 1.0     | μΑ   |

| VOL (4)   | Output low voltage     | -       | _       | 0.4     | v    |

| VOH (4)   | Output high voltage    | 2.4     | _       | _       | v    |

**Notes :** 3. Gnd < Vin < Vcc, Gnd < Vout < Vcc Output disabled.

4. Vcc min, IOL = 4 mA, IOH = -1.0 mA.

#### Consumption

| SYMBOL     | PARAMETER                | M65656G<br>V - 45 | M65656G<br>V - 55 | UNIT | VALUE |

|------------|--------------------------|-------------------|-------------------|------|-------|

| ICCSB (5)  | Standby supply current   | 5                 | 5                 | mA   | max   |

| ICCSB1 (6) | Standby supply current   | 100               | 100               | μΑ   | max   |

| ICCOP (7)  | Operating supply current | 85                | 85                | mA   | max   |

**Notes :** 5.  $\overline{CS} \ge VIH$ ,  $Vin \ge VIH$  or  $Vin \le VIL$ .

6.  $\overline{\text{CS}} \ge \text{Vcc} - 0.3 \text{ V}$ , Iout = 0 mA. Vin  $\ge \text{Vcc} - 0.3 \text{ V}$  or Vin  $\le 0.3 \text{ V}$ .

7. Vcc max, Iout = 0 mA, Vin = Gnd/Vcc. Duty cycle 100 %, F = 5 MHz, derating = 12 mA/MHz.

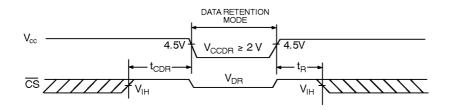

#### **Data Retention Mode**

MHS CMOS RAM's are designed with battery backup in mind. Data retention voltage and supply current are guaranteed over temperature. The following rules insure data retention :

- 1. Chip select  $(\overline{CS})$  must be held high during data retention; within Vcc to Vcc 0.2 V.

- 2. Output Enable  $(\overline{OE})$  should be held high to keep the RAM outputs high impedance, minimizing power dissipation.

- 3. CS must be kept between Vcc -0.3 V and 70 % of Vcc during the power up and power down transitions.

- 4. The RAM can begIn operation > TR after Vcc reaches the minimum operating voltage (4.5 V).

#### Timing

## **Data Retention Characteristics**

| PARAMETER   | DESCRIPTION                                   | MINIMUM   | TYPICAL (8) | MAXIMUM | UNIT |

|-------------|-----------------------------------------------|-----------|-------------|---------|------|

| VCCDR       | Vcc for data retention                        | 2.0       | _           | _       | V    |

| TCDR        | Chip deselect to data retention time          | 0.0       | _           | _       | ns   |

| TR          | Operation recovery time                       | TAVAV (9) | -           | _       | ns   |

| ICCDR1 (10) | Data retention current<br>@ 2.0 V : M-65656GV |           | 0.1         | 80      | μΑ   |

| ICCDR2 (10) | Data retention current<br>@ 3.0 V : M-65656GV |           | 0.3         | 90      | μΑ   |

Notes : 8.  $TA = 25^{\circ}C$ .

9. TAVAV = Read cycle time.

10.  $\overline{CS} = Vcc$ , Vin = Gnd/Vcc, this parameter is only tested at Vcc = 2 V.

## **AC Parameters**

## **AC Conditions**

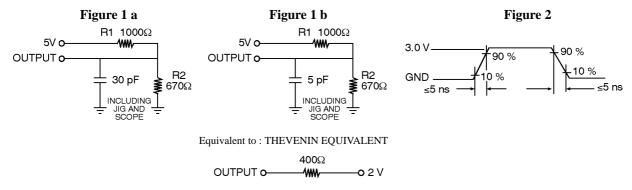

| Input pulse levels : | Input timing reference levels : 1.5 V |

|----------------------|---------------------------------------|

| Input rise : 5 ns    | Output load : See fig. 1a, 1b         |

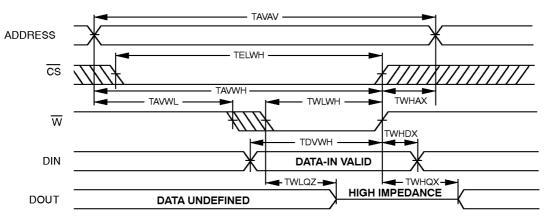

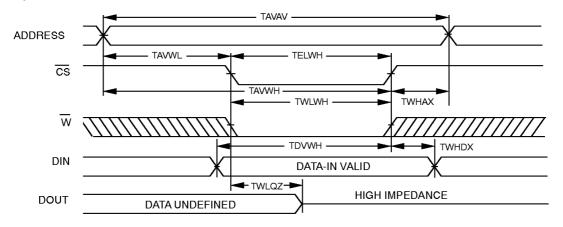

## Write Cycle

| SYMBOL              | PARAMETER                                        | M65656G<br>- 40        | M65656G<br>- 55 | UNIT | VALUE |

|---------------------|--------------------------------------------------|------------------------|-----------------|------|-------|

| TAVAV               | Write cycle time                                 | 40                     | 55              | ns   | min   |

| TAVWL               | Address set-up time                              | 0                      | 0               | ns   | min   |

| TAVWH               | Address valid to end of write                    | 30                     | 40              | ns   | min   |

| TDVWH               | Data set-up time                                 | 22                     | 25              | ns   | min   |

| TELWH               | $\overline{\text{CS}}$ low to write end          | 30                     | 40              | ns   | min   |

| TWLQZ (11)          | Write low to high Z                              | 15                     | 20              | ns   | max   |

| TWLWH               | Write pulse width                                | 30                     | 40              | ns   | min   |

| TWHAX               | Address hold to end of write                     | 0                      | 0               | ns   | min   |

| TWHDX               | Data hold time                                   | 0                      | 0               | ns   | min   |

| TWHQX (11)          | Write high to low Z                              | 0                      | 0               | ns   | min   |

| Notes: 11. Specifie | d with $C_L = 5 \text{ pF}$ (see figure 1b). Gua | ranteed but not tested |                 | ·    | •     |

#### Write Cycle 1 : $\overline{W}$ Controlled (note 12)

## Write Cycle 2 : $\overline{CS}$ Controlled (note 12)

**Note :** 12. The internal write time of the memory is defined by the overlap of  $\overline{CS}$  LOW and  $\overline{W}$  LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input setup and hold timing should be referenced to the rising edge of the signal that terminates the write. Data out is high impedance if  $\overline{OE} = VIH$ .

#### **AC Test Loads and Waveforms**

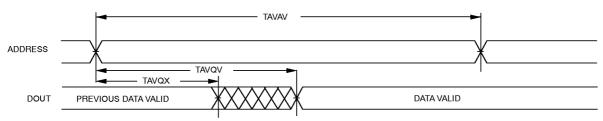

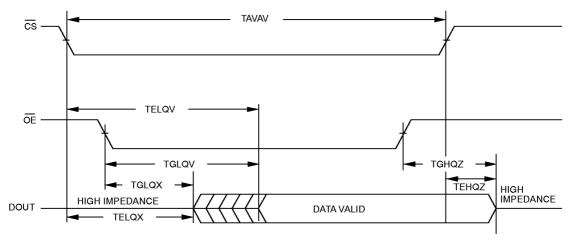

## **Read Cycle**

| SYMBOL    | PARAMETER                             | M65656G<br>- 40 | M65656G<br>- 55 | UNIT | VALUE |

|-----------|---------------------------------------|-----------------|-----------------|------|-------|

| TAVAV     | Read cycle time                       | 40              | 55              | ns   | min   |

| TAVQV     | Address access time                   | 40              | 55              | ns   | max   |

| TAVQX     | Address valid to low Z                | 5               | 5               | ns   | min   |

| TELQV     | Chip-select access time               | 40              | 55              | ns   | max   |

| TELQX(13) | $\overline{CS}$ low to low Z          | 5               | 5               | ns   | min   |

| TEHQZ(13) | $\overline{\text{CS}}$ high to high Z | 15              | 15              | ns   | max   |

| TGLQV     | Output Enable access time             | 20              | 25              | ns   | max   |

| TGLQX(13) | $\overline{OE}$ low to low Z          | 5               | 5               | ns   | min   |

| TGHQZ(13) | $\overline{\text{OE}}$ high to high Z | 15              | 20              | ns   | max   |

Notes : 13. Specified with  $C_L = 5 \text{ pF}$  (see figure 1b). Guaranteed but not tested.

# M65656G

## Read Cycle nb 1 (notes 14, 15)

## Read Cycle nb 2 (notes 14, 16)

- **Notes :** 14.  $\overline{W}$  is high for read cycle.

- 15. Device is continuously selected  $\overline{CS} \& \overline{OE} = VIL$ .

- 16. Address valid prior to or coincident with  $\overline{CS}$  transition low.

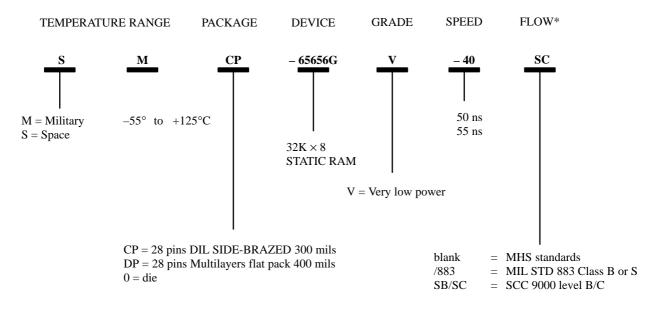

## **Ordering Information**

\* For ordering in QML quality level, use the QML PIN according to SMD number (to be defined).

The information contained herein is subject to change without notice. No responsibility is assumed by Atmel Wireless & Microcontrollers for using this publication and/or circuits described herein : nor for any possible infringements of patents or other rights of third parties which may result from its use.