### **OKI** Semiconductor

This version: Jan. 1998

Previous version: May. 1997

### **MSM98P05**

Built-in 2-Mbit OTP ROM Voice Synthesis IC

### GENERAL DESCRIPTION

The MSM98P05 is a PCM voice synthesis IC with built-in 2-Mbit OTP (One Time PROM). This IC employs OKI nonlinear PCM methods and contains a current mode 10-bit D/A converter and a low-pass filter.

External control has been made easy by the built-in edit ROM that can form sentences by linking phrases.

With the stand-alone mode/microcontroller interface mode switching pin, the MSM98P05 can support various applications.

The products with build-in OTP are suited to applications to be produced in small quantities in a wide variery or those to be delivered with an early deadline. Demand like these, that is, production in small quantities in a wide variety and delivery with an early deadline is what the MSM9800 family of products with built-in mask ROM cannot meet.

### **FEATURES**

- 8-bit OKI nonlinear PCM method

- Built-in edit ROM

- Random playback function

- Sampling frequency : 4.0 kHz/5.3 kHz/6.4 kHz/8.0 kHz/10.6 kHz/12.8 kHz/

16.0 kHz

Note: If RC oscillation is selected, 10.6 kHz, 12.8 kHz, and

16.0 kHz cannot be selected.

• Maximum number of phrases : 63 (Microcontroller interface mode)

56 (Stand-alone mode)

- Built-in current mode 10-bit D/A converter

- Built-in low-pass filter (LPF)

- Standby function

- RC oscillation (256 kHz)/ceramic oscillation (4.096 MHz) selectable

- Package options:

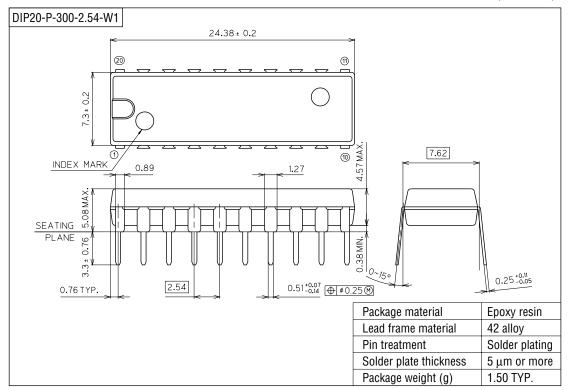

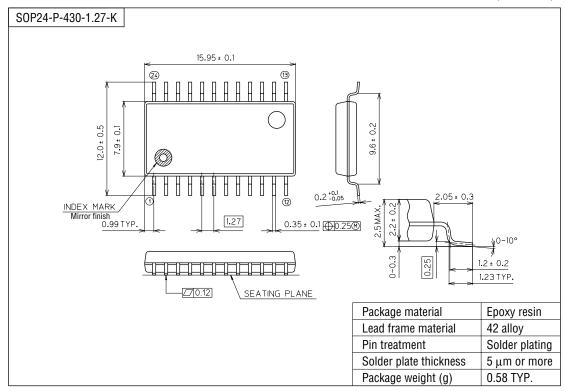

20-pin plastic DIP (DIP20-P-300-2.54-W1) (Product name: MSM98P05RS) 24-pin plastic SOP (SOP24-P-430-1.27-K) (Product name: MSM98P05GS-K)

# STAND-ALONE MODE (CPU/STD: "L" level)

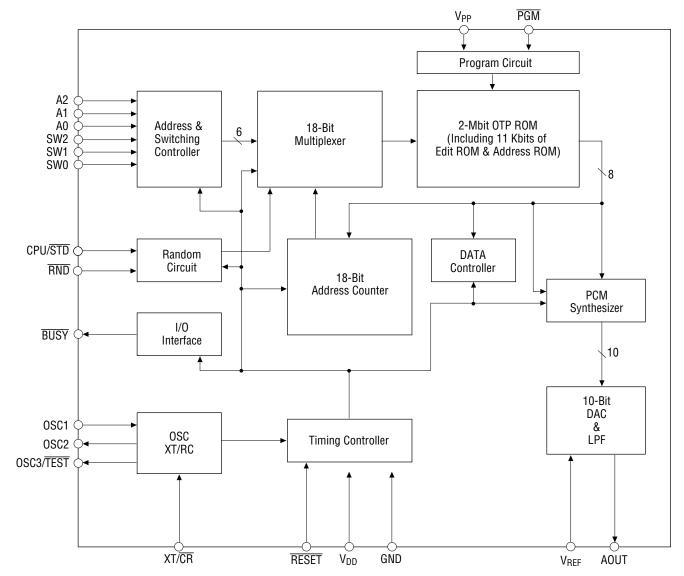

### **BLOCK DIAGRAM**

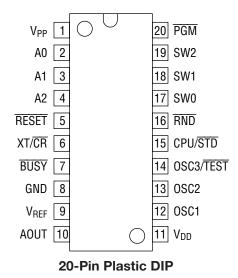

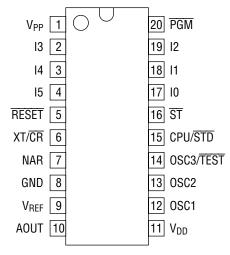

### PIN CONFIGURATION (TOP VIEW)

Note: Applies to MSM98P05RS

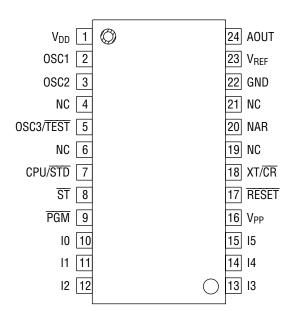

24-Pin Plastic SOP

Note: Applies to MSM98P05GS-K

### **PIN DESCRIPTIONS**

| Pin |     |                  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-----|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP | SOP | Symbol           | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5   | 17  | RESET            | I    | The IC enters the standby state if this pin is set to "L" level. At this time, oscillation stops and AOUT drives a current of 0mA and becomes GND level, then the IC returns to the initial state. This IC has a built-in power-on reset circuit. To operate power-on reset correctly, apply the power within 1 ms up to $V_{DD}$ . If the power cannot be applied within 1 ms, apply a $\overline{RESET}$ pulse during power-on. This pin has an internal pull-up resistor. |

| 7   | 20  | BUSY             | 0    | Outputs "L" level while voice is being played back. In "H" level when power is turned ON.                                                                                                                                                                                                                                                                                                                                                                                    |

| 6   | 18  | XT/CR            | I    | XT/RC switching pin. Set to "H" level if ceramic oscillation is used. Set to "L" level if RC oscillation is used.                                                                                                                                                                                                                                                                                                                                                            |

| 15  | 7   | CPU/STD          | ı    | Microcontroller interface/stand-alone mode switching pin. Set to "L" level if the IC is used in stand-alone mode.                                                                                                                                                                                                                                                                                                                                                            |

| 9   | 23  | V <sub>REF</sub> | I    | Volume setting pin. If this pin is set to GND level, the maximum amplitude is delivered. If this pin is set to $V_{DD}$ level, the minimum amplitude is delivered. This pin is internally connected to a pull-down resistor of approx. 10 $k\Omega$ during IC operation.                                                                                                                                                                                                     |

| 10  | 24  | AOUT             | 0    | Voice output pin.  The voice signals are output as current changes. A logic "L" is output from this pin in standby state.                                                                                                                                                                                                                                                                                                                                                    |

| 8   | 22  | GND              | _    | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11  | 1   | V <sub>DD</sub>  | _    | Power supply pin. Insert a bypass capacitor of 0.1 $\mu F$ or more between $V_{DD}$ and GND pins.                                                                                                                                                                                                                                                                                                                                                                            |

| 12  | 2   | 0SC1             | I    | Ceramic oscillator connection pin when ceramic oscillation is selected.  RC connection pin when RC oscillation is selected.  Input from this pin if external clock is used.                                                                                                                                                                                                                                                                                                  |

| 13  | 3   | OSC2             | 0    | Ceramic oscillator connection pin when ceramic oscillation is selected.  RC connection pin when RC oscillation is selected.  Leave this pin open if external clock is used.  Outputs "L" level in standby state.                                                                                                                                                                                                                                                             |

| 14  | 5   | OSC3/TEST        | 0    | Leave this pin open when ceramic oscillation is used. RC connection pin when RC oscillation is selected. Outputs "H" level in standby state when RC oscillation is selected.                                                                                                                                                                                                                                                                                                 |

| 16  | 8   | RND              | I    | Random playback starts if $\overline{\text{RND}}$ pin is set to "L" level.  Fetches addresses from random address generation circuit in the IC at fall of $\overline{\text{RND}}$ . Set to "H" level when the random playback function is not used.  This pin has internal pull-up resistor.                                                                                                                                                                                 |

| Pin   |       | Comple ed       | T    | Description                                                                   |

|-------|-------|-----------------|------|-------------------------------------------------------------------------------|

| DIP   | SOP   | Symbol          | Туре | Description                                                                   |

|       | 10-12 | SW0 - SW2       | I    | Phrase input pins corresponding to playback sound.                            |

| 17-19 |       |                 |      | If input changes, SW0 to SW2 pins fetch addresses after 16 ms and start voice |

|       |       |                 |      | synthesis. Each of these pins has internal pull-down resistor.                |

| 2-4   | 13-15 | A0 - A2         | I    | Phrase input pins corresponding to playback sound.                            |

| 2-4   |       |                 |      | A0 input becomes invalid if the random playback function is used.             |

| 1     | 16    | V <sub>PP</sub> | _    | Power supply pin for writing to the built-in OTP.                             |

| 20    | 9     | PGM             | ı    | Interface pin for writing to the built-in OTP.                                |

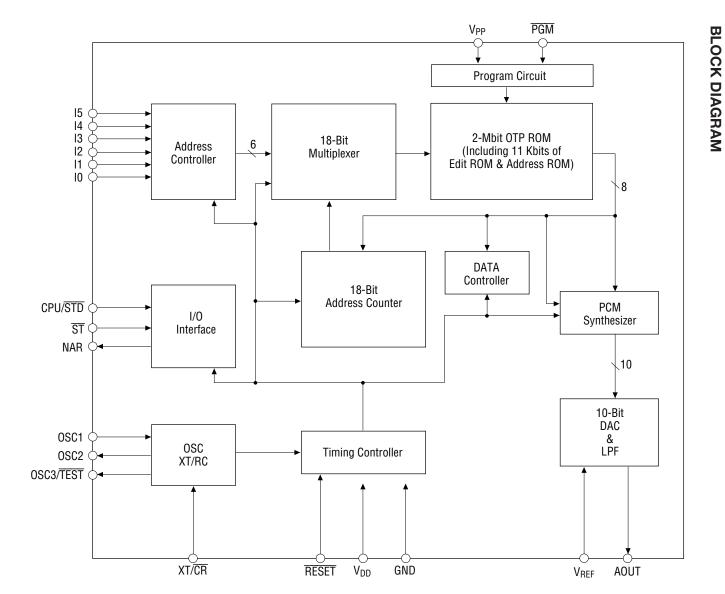

## MICROCONTROLLER INTERFACE MODE (CPU/STD: "H" level)

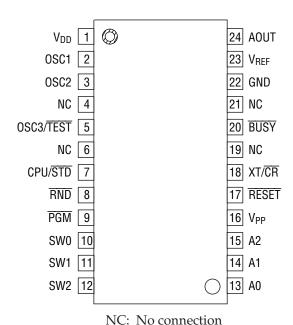

### **PIN CONFIGURATION (TOP VIEW)**

20-Pin Plastic DIP

Note: Applies to MSM98P05RS

NC: No connection

24-Pin Plastic SOP

Note: Applies to MSM98P05GS-K

### **PIN DESCRIPTIONS**

| Pin          |       | 0                | _    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|-------|------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP          | SOP   | Symbol           | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5            | 17    | RESET            | I    | The IC enters the standby state if this pin is set to "L" level. At this time, oscillation stops and AOUT drives a current of 0mA and becomes GND level, then the IC returns to the initial state. This IC has a built-in power-on reset circuit. To operate power-on reset correctly, apply the power within 1 ms up to $V_{DD}$ . If the power cannot be applied within 1ms, apply a $\overline{RESET}$ pulse during power-on. This pin has an internal pull-up resistor. |

| 7            | 20    | NAR              | 0    | Signal output pin that indicates whether the register in the address controller to latch the 10-15 addresses (see Block Diagram) is idle. NAR at "H" level indicates that the LATCH is empty and $\overline{ST}$ input is enabled.                                                                                                                                                                                                                                          |

| 6            | 18    | XT/CR            | I    | XT/RC switching pin. Set to "H" level if ceramic oscillation is used. Set to "L' level if RC oscillation is used.                                                                                                                                                                                                                                                                                                                                                           |

| 15           | 7     | CPU/STD          | I    | Microcontroller interface/stand-alone mode switching pin. Set to "H" level if the IC is used in microcontroller interface mode.                                                                                                                                                                                                                                                                                                                                             |

| 9            | 23    | V <sub>REF</sub> | I    | Volume setting pin. If this pin is set to GND level, the maximum amplitude is delivered. If this pin is set to $V_{DD}$ level, the minimum amplitude is delivered. This pin is internally connected to a pull-down resistor of approx. 10 k $\Omega$ during IC operation.                                                                                                                                                                                                   |

| 10           | 24    | AOUT             | 0    | Voice output pin.  The voice signals are output as current changes. A logic "L" is output from this pin in standby state.                                                                                                                                                                                                                                                                                                                                                   |

| 8            | 22    | GND              | _    | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11           | 1     | V <sub>DD</sub>  | _    | Power supply pin. Insert a bypass capacitor of 0.1 $\mu F$ or more between this pin and the GND pin.                                                                                                                                                                                                                                                                                                                                                                        |

| 12           | 2     | 0SC1             | I    | Ceramic oscillator connection pin when ceramic oscillation is selected.  RC connection pin when RC oscillation is selected.  Input from this pin if external clock is used.                                                                                                                                                                                                                                                                                                 |

| 13           | 3     | 0SC2             | 0    | Ceramic oscillator connection pin when ceramic oscillation is selected.  RC connection pin when RC oscillation is selected.  Leave this pin open if external clock is used.  Outputs "L" level in standby state.                                                                                                                                                                                                                                                            |

| 14           | 5     | OSC3/TEST        | 0    | Leave this pin open when ceramic oscillation is used. RC connection pin when RC oscillation is selected. Outputs "H" level in standby state when RC oscillation is selected.                                                                                                                                                                                                                                                                                                |

| 16           | 8     | ST               | I    | Voice synthesis starts at fall of $\overline{ST}$ , and addresses I0 to I5 are fetched at rise of $\overline{ST}$ . Input $\overline{ST}$ when NAR, the status signal, is at "H" level. This pin has internal pull-up resistor.                                                                                                                                                                                                                                             |

| 17-19<br>2-4 | 10-15 | 10 - 15          | I    | Phrase input pins corresponding to vocalized sound.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1            | 16    | $V_{PP}$         | _    | Power supply pin for writing to the built-in OTP.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 20           | 9     | RGM              | ı    | Interface pin for writing to the built-in OTP.                                                                                                                                                                                                                                                                                                                                                                                                                              |

### **PACKAGE DIMENSIONS**

(Unit: mm)

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).