# **Preliminary Information**

## **Features**

- AAL1 Segmentation Reassembly device capable of simultaneously processing up to 2048 bidirectional VCs

- AAL1 cell format for "Structured DS1/E1 N x 64kbps Service" as per ATM Forum AF-VTOA-0078.000 "Circuit Emulation Services Interoperability Specifications" (Nx64 Basic Service, DS1 Nx64 Service with CAS, and E1 Nx64 Service with CAS)

- Two UTOPIA ports (Level 2, 16-bit, 50 MHz) with loopback function for dual fibre ring applications

- Third UTOPIA port for connection to an external AAL5 SAR processor, or for chaining multiple MT90503 or MT90500 devices

- Flexible aggregation capabilities (Nx64) to allow any combination of 64 Kbps

- TDM bus provides 32 bidirectional serial TDM

streams at 2.048, 4.096, or 8.192 Mbps for up to 4096 TDM 64 Kbps channels

- Compatible with H.100 and H.110 interfaces

- TDM to ATM Transmission latency less than 250 μs

- Support for clock recovery Adaptive Clock Recovery, Synchronous Residual Time Stamp (SRTS) or external

- Support master and slave TDM bus clock operation

- 8- or 16-bit microprocessor port, configurable to Motorola or Intel timing

- Master clock rate up to 80 MHz

- Single power supply device (3.3V)

- IEEE 1149 (JTAG) interface

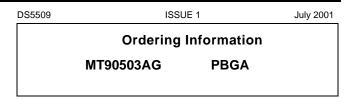

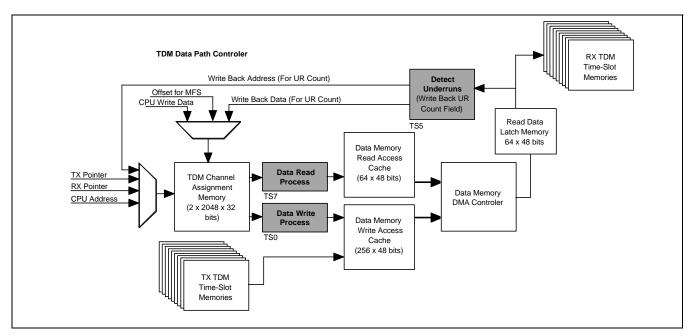

Figure 1 - Functional Block Diagram

# **Description**

The MT90503 is an AAL1 SAR, which offers a highly integrated solution for interfacing telecom bus-based systems with ATM networks. The device has the capability of simultaneously processing 2048 bidirectional channels of 64 kbps. The MT90503 can be connected directly to an H.100 or H.110 compatible bus. The device also offers the capability of using Channel Associated Signalling (CAS) to support Circuit Emulation Service (CES) for Structured Data Transfer (SDT).

The interface to the TDM port is provided by a TDM bus, which consists of 32 bidirectional serial TDM data streams at 2.048, 4.096, or 8.192 Mbps, therefore allowing for 2048 bidirectional TDM channels operating at 64 kbps. This TDM bus is compatible with the ECTF H.100 and H.110 specifications.

The interface to the ATM domain is provided by three UTOPIA ports (Ports A, B, and C). All three of the UTOPIA ports can operate in ATM (master) or PHY (slave) mode. Port A can also be configured as Level 2 M-PHY mode.

## **Applications**

- ATM Access and Multiplexing Equipment

- Switching Platforms that provide internetworking between TDM and ATM

- ATM Edge Switches

- ATM uplink for expansion of COs, PBXs, or open switching platforms using an adjunct ATM switch

- Integrated Digital Loop Carrier (IDLC)

- SONET or SDH Add and Drop Multiplexers (ADM)

- Next Generation Digital Loup Carrier (NGDIC)

- Digital Subscriber Line Access Multiplexer DSLAM with Gateway

# **Switching Feature**

Cells coming in from any of the UTOPIA ports can be switched to any other port. The user has the option to change the VPI and VCI fields.

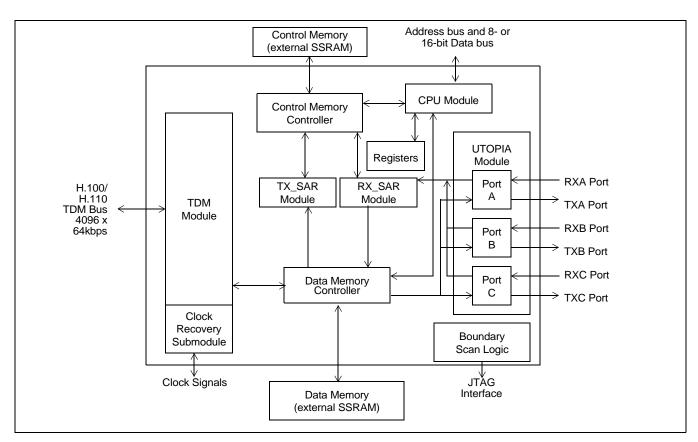

Figure 2 - ATM Switch

| 1.0 Introduction                                              | 7  |

|---------------------------------------------------------------|----|

| 1.1 Functional Overview of the MT90503                        | 7  |

| 2.0 Features Detailed Description                             | 9  |

| 2.1 UTOPIA Interface                                          | 9  |

| 2.2 TDM Interface                                             | 9  |

| 2.3 Clock Recovery                                            | 9  |

| 2.4 ATM SAR                                                   |    |

| 2.5 Required External Components                              |    |

| 2.6 Particular Modes of Operation                             | 10 |

| 2.7 Miscellaneous                                             |    |

| 2.8 Power                                                     | 11 |

| 3.0 Pin Designations and Descriptions                         | 13 |

| 4.0 Functional Description                                    | 26 |

| 4.1 CPU Interface                                             | 26 |

| 4.1.1 CPU Interrupts                                          |    |

| 4.1.1.1 Example Interrupt Flow                                | 26 |

| 4.1.1.1 Interrupt Initialisation                              | 26 |

| 4.1.1.1.2 Interrupt Servicing                                 | 27 |

| 4.1.2 Intel/Motorola Interface                                | 27 |

| 4.1.2.1 Extended Indirect Accessing                           |    |

| 4.1.2.1.1 Extended Indirect Writes                            |    |

| 4.1.2.1.2 Extended Indirect Reads                             |    |

| 4.1.2.2 Extended Direct Accessing                             |    |

| 4.1.2.2.1 Extended Direct Writes                              |    |

| 4.1.3 MT90503 Reset Procedure                                 |    |

| 4.2 TDM Module                                                |    |

| 4.2.1 TDM Bus Interface                                       |    |

| 4.2.2 TDM Bus Clocking Mechanism                              |    |

| 4.2.3 TDM Datapath                                            |    |

| 4.2.4 TDM Channel Association Structures                      |    |

| 4.2.4.1 Non CAS Operation                                     |    |

| 4.2.4.2 CAS Operation                                         |    |

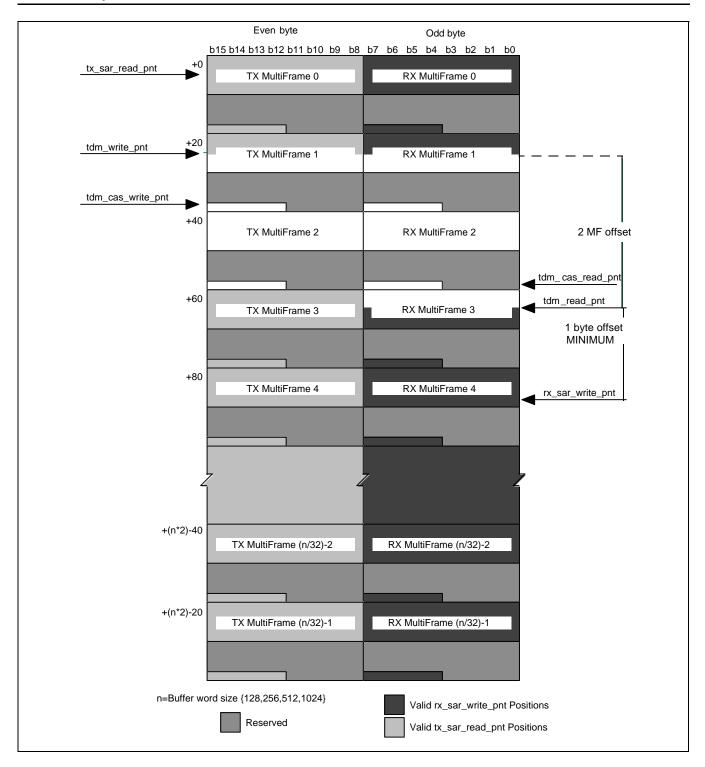

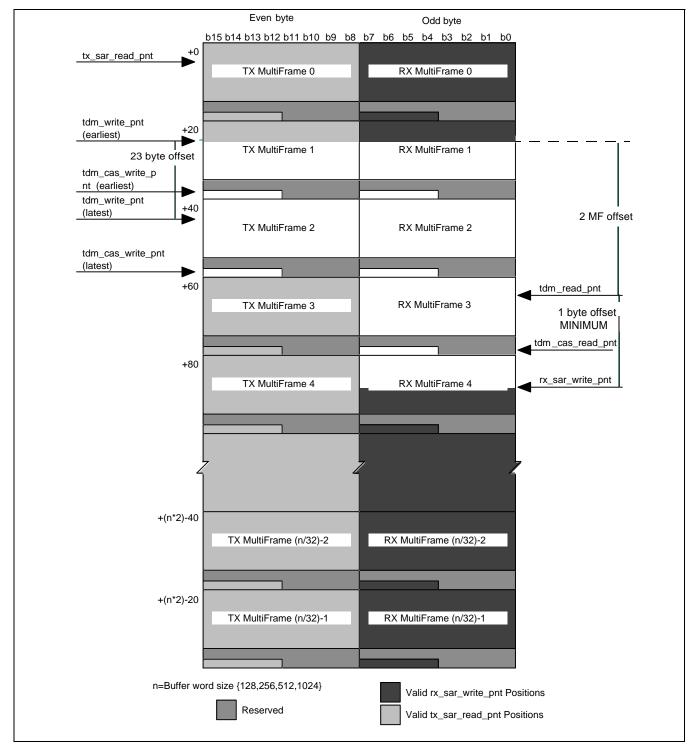

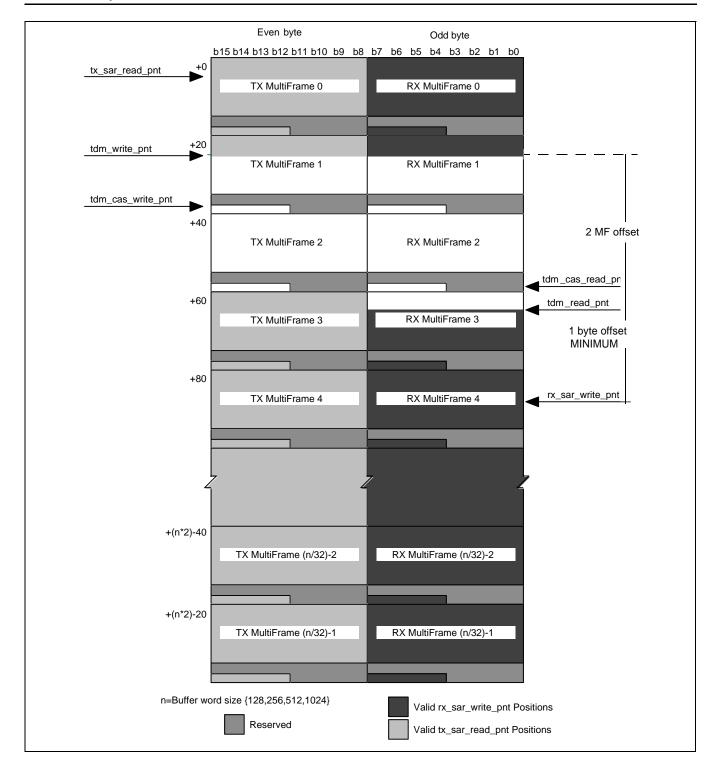

| 4.2.5 TDM Circular Buffers                                    |    |

| 4.2.6 TDM Circular Buffer Pointers                            |    |

| 4.2.6.1 Non-multiframing mode                                 |    |

| 4.2.6.2 E1/T1 Multiframing (standard)                         |    |

| 4.3 TX_SAR Module                                             |    |

| 4.3.1 Overview                                                |    |

| 4.3.1.1 Support and Trunking for Different Types of ATM Cells | 51 |

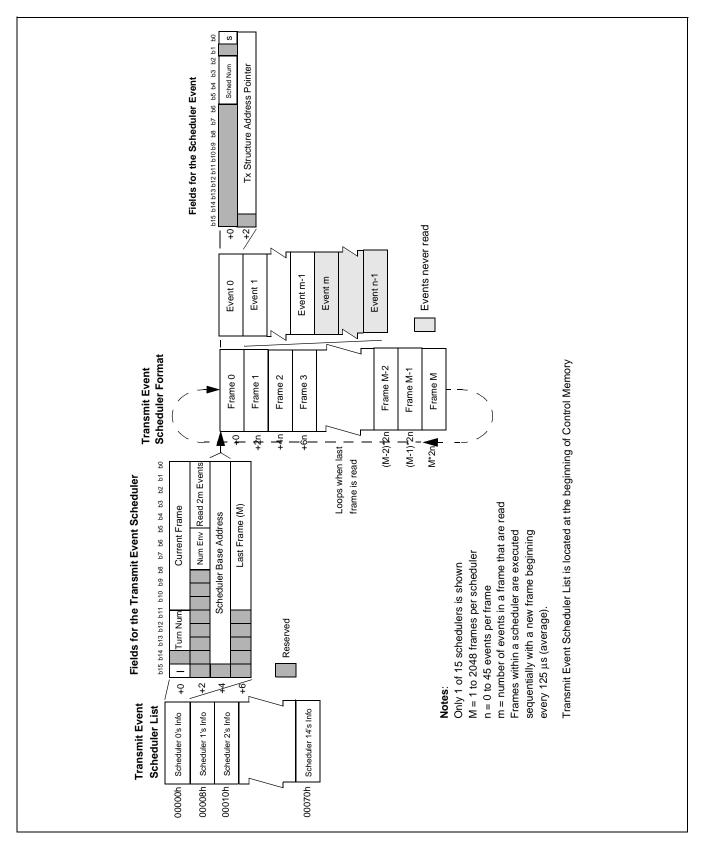

| 4.3.2 TX_SAR Event Schedulers                                 | 52 |

| 4.3.2.1 Overview                                              |    |

| 4.3.2.2 The Transmit Event Scheduler Process                  |    |

| 4.3.2.3 Transmit Event Scheduler Fields Description           |    |

| 4.3.2.4 Scheduler Events Fields Description                   |    |

| 4.3.2.5 Bandwidth Limitations for Transmit Scheduler Events   |    |

| 4.3.3 Out of Bandwidth Error                                  |    |

| 4.3.3.1 Percent of Bandwidth Register                         |    |

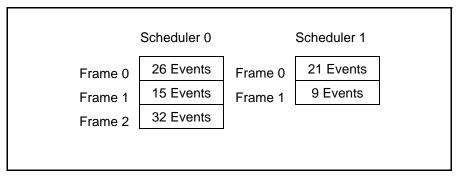

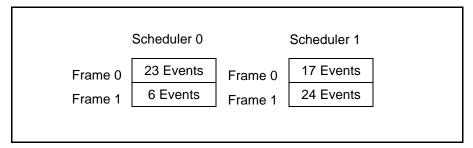

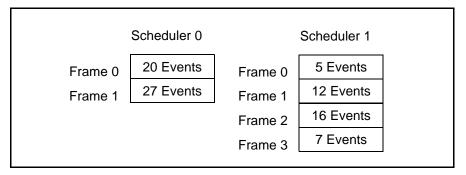

| 4.3.3.2 Distribution of Events by Software                    |    |

| 4.3.4 Manning of the Transmit Event Scheduler                 | 57 |

| 4.3.5 TX_SAR Control Structures                                      | 59  |

|----------------------------------------------------------------------|-----|

| 4.3.5.1 TX SAR Control Structure Fields                              |     |

| 4.3.6 Miscellaneous TX_SAR Features                                  |     |

| 4.3.6.1 T1 with CAS and E1 with CAS Cell Format Mapping              |     |

| 4.3.6.2 Support of Partially-Filled Cells                            |     |

| 4.3.6.3 TX_SAR FIFO                                                  | 64  |

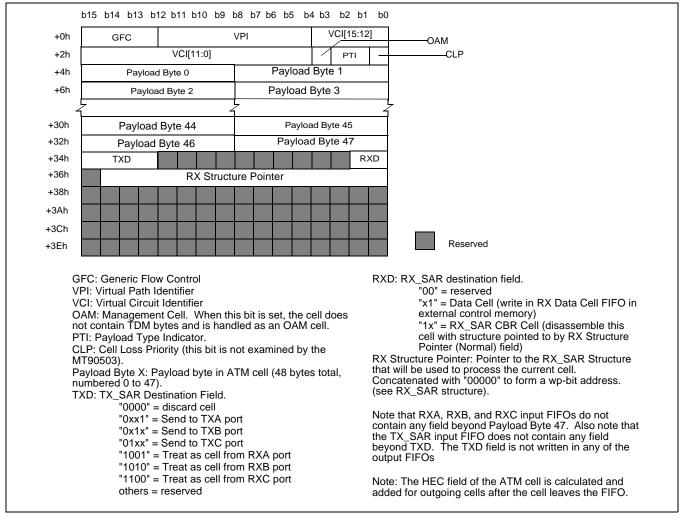

| 4.4 RX_SAR Module                                                    | 65  |

| 4.4.1 Treatment of Data Cells                                        | 65  |

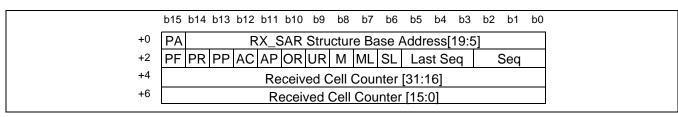

| 4.4.2 Control Structure                                              | 65  |

| 4.4.3 Errors                                                         | 70  |

| 4.4.4 Error Report Structure                                         | 71  |

| 4.5 UTOPIA Module                                                    | 73  |

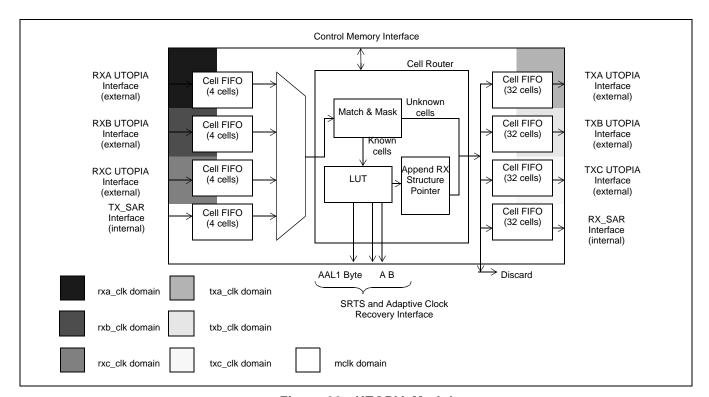

| 4.5.1 Overview                                                       | 73  |

| 4.5.2 UTOPIA Interfaces                                              | 73  |

| 4.5.3 Errors on received cells                                       | 74  |

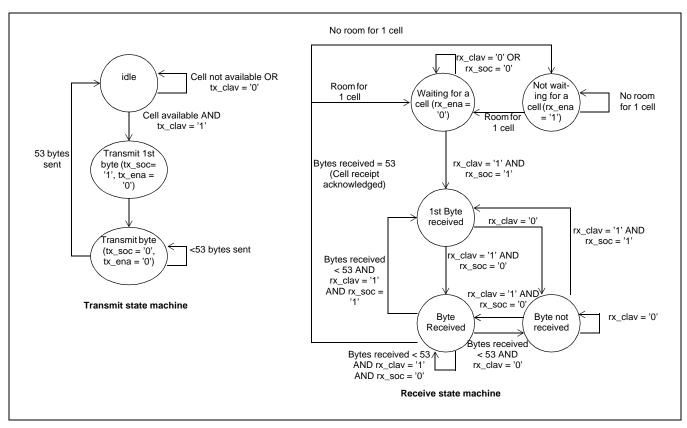

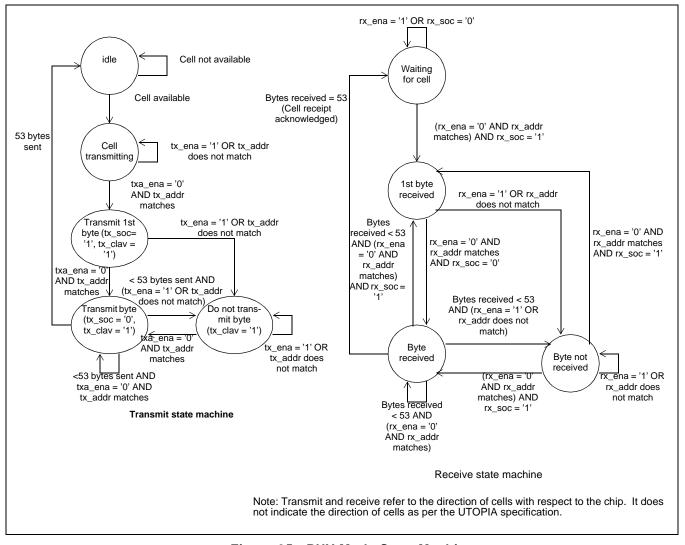

| 4.5.4 Transmit and Receive State Machines for ATM and PHY Modes      | 75  |

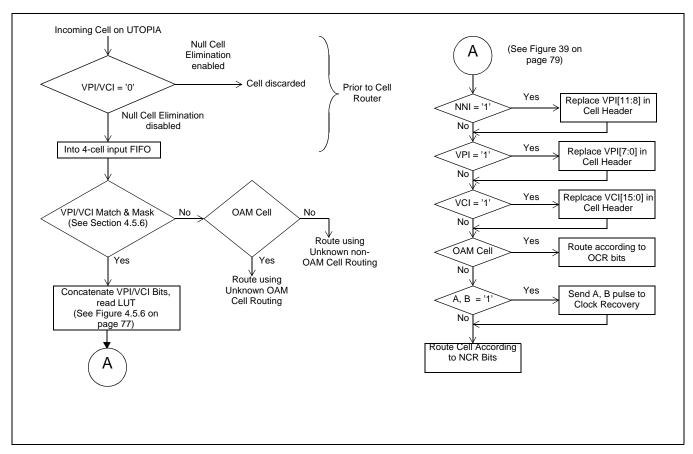

| 4.5.5 Cell Router                                                    | 76  |

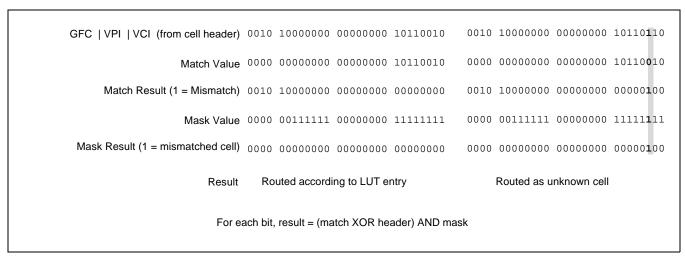

| 4.5.6 Mask & Match for cell routing                                  | 77  |

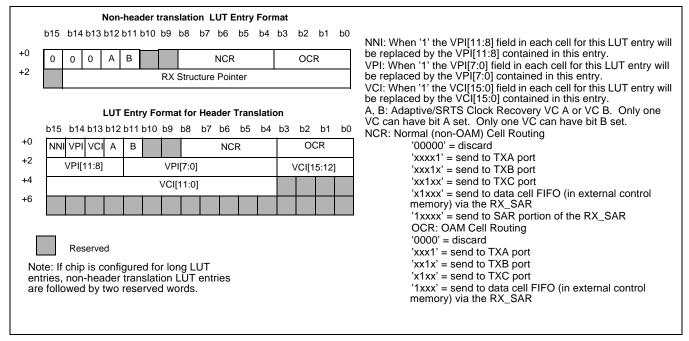

| 4.5.6.1 Look-Up Tables Entries                                       |     |

| 4.5.6.2 LUT Addressing                                               |     |

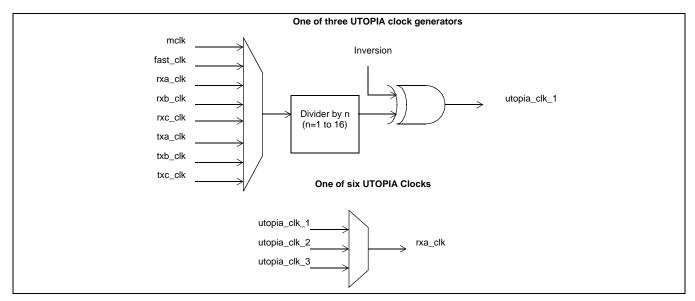

| 4.5.6.3 UTOPIA Clocks                                                | 80  |

| 4.5.7 LED Operation                                                  |     |

| 4.5.8 UTOPIA Flow Control                                            |     |

| 4.5.9 External Interface Signals                                     |     |

| 4.6 Clock Recovery Module                                            |     |

| 4.6.1 Overview                                                       |     |

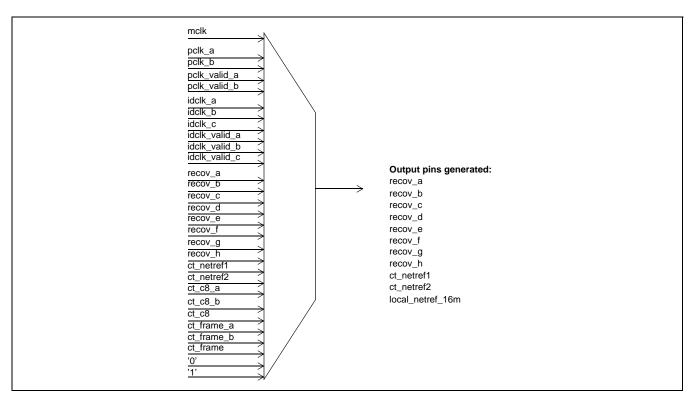

| 4.6.1.1 Two Point Generation Modules                                 |     |

| 4.6.1.2 One SRTS (synchronous residual time stamp) Generating Module |     |

| 4.6.1.3 Three Integer Divisor Clock Modules                          |     |

| 4.6.1.4 Two Precise Clock Modules                                    |     |

| 4.6.2 Multiplexers                                                   |     |

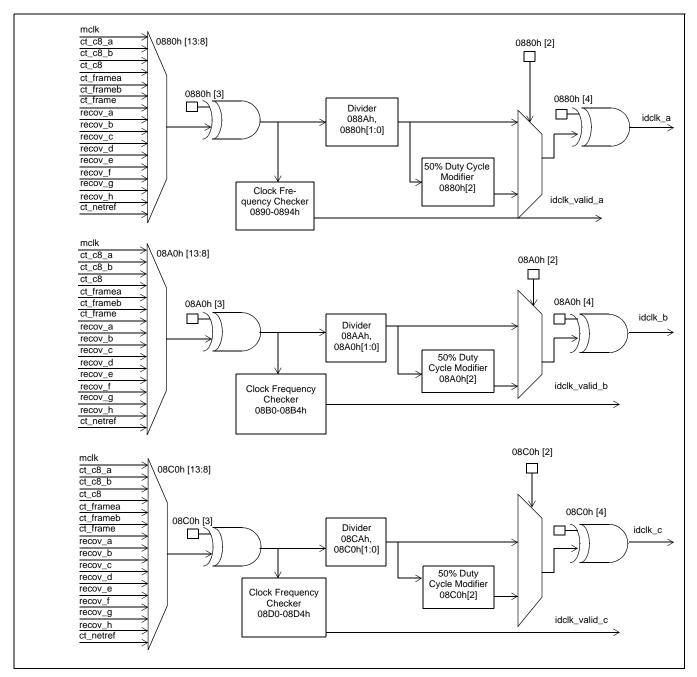

| 4.6.3 Integer Divisor Clocks (idclk)                                 |     |

| 4.6.4 Precise Clocks (pclk)                                          |     |

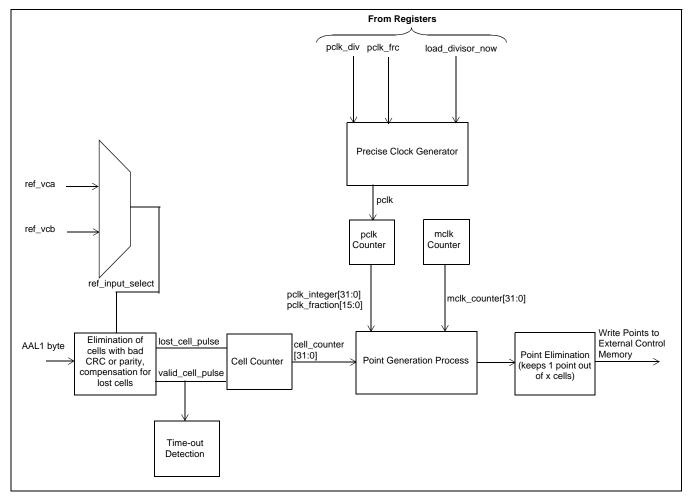

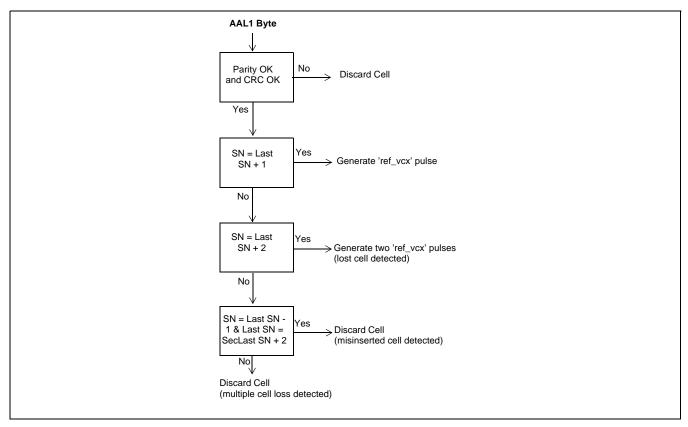

| 4.6.5 Point Generation                                               |     |

| 4.6.6 Adaptive Clock Recovery                                        |     |

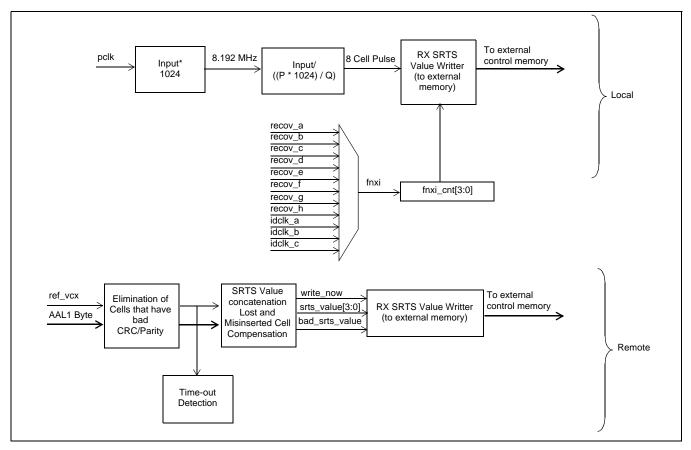

| 4.6.6.1 SRTS Clock Recovery                                          |     |

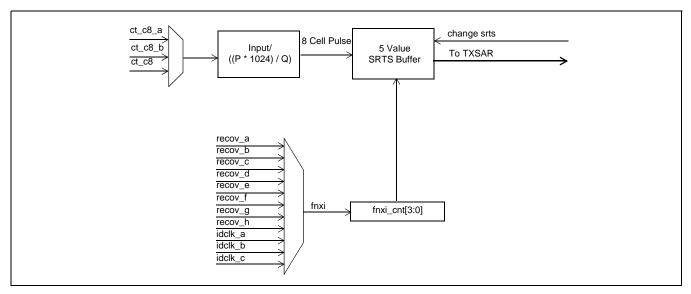

| 4.6.7 SRTS Transmission                                              |     |

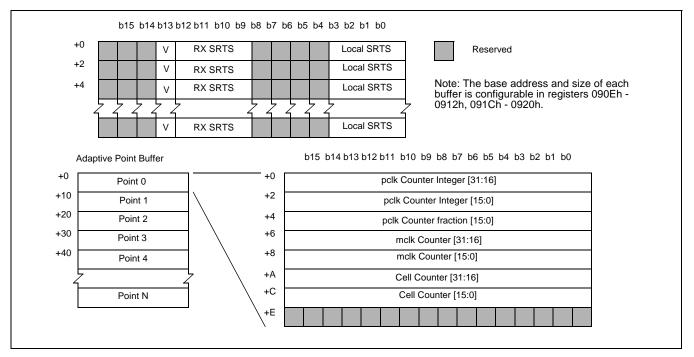

| 4.6.8 External Memory Point Format                                   |     |

| 4.7 Memory Controllers                                               |     |

| 4.7.1 Data Memory                                                    |     |

| 4.7.2 Control Memory                                                 |     |

| 4.7.3 Data Memory Controller                                         |     |

| 4.7.4 Control Memory Controller                                      |     |

|                                                                      |     |

| 5.0 Memory Map                                                       | 97  |

| 5.1 Register Overview                                                | 97  |

| 5.2 Detailed Register Description                                    |     |

| 5.2.1 CPU Registers                                                  | 97  |

| 5.2.2 Main Registers                                                 | 105 |

| 5.2.3 Utopia Registers                                               | 115 |

| 5.2.4 TDM Registers                                                  |     |

| 5.2.5 TX_SAR Registers                                               |     |

| 5.2.6 Scheduler Registers                                            | 154 |

# **Preliminary Information**

| 5.2.7 RX_SAR Registers                    | 158 |

|-------------------------------------------|-----|

| 5.2.8 Clock Registers                     |     |

| 5.2.9 Miscellaneous Registers             | 188 |

| 5.2.10 H.100 Registers                    | 196 |

| 6.0 Statistics                            | 199 |

| 6.1 TDM statistics                        | 199 |

| 6.2 TX SAR statistics                     | 199 |

| 6.3 RX SAR statistics                     | 199 |

| 6.4 UTOPIA statistics                     | 199 |

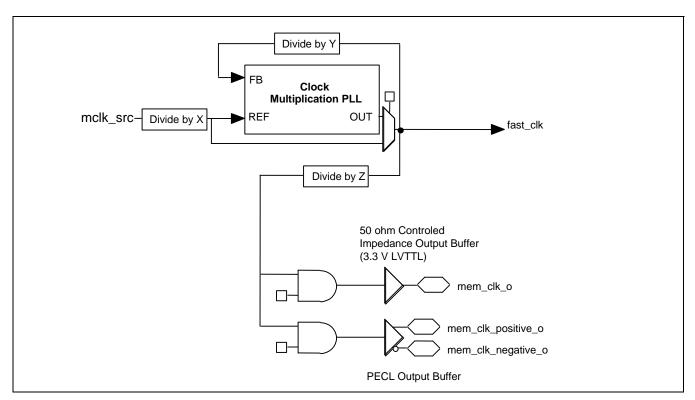

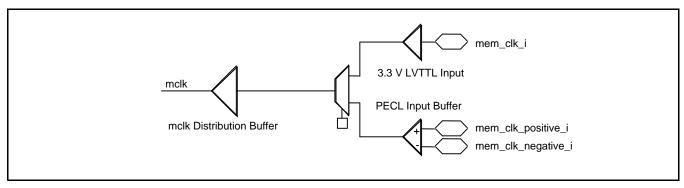

| 7.0 Programming The mem_clk PLL           | 200 |

| 8.0 Electrical Specifications             | 203 |

| 8.1 DC Characteristics                    | 203 |

| 8.1.1 Precautions During Power Sequencing | 205 |

| 8.1.2 Precautions During Power Failure    |     |

| 8.1.3 Pull-ups                            |     |

| 8.2 H.110 Diode Clamp Rail                |     |

| 8.3 AC Characteristics                    | 205 |

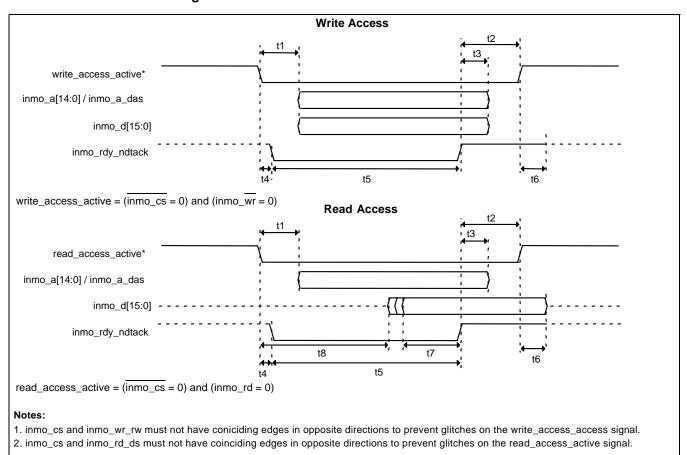

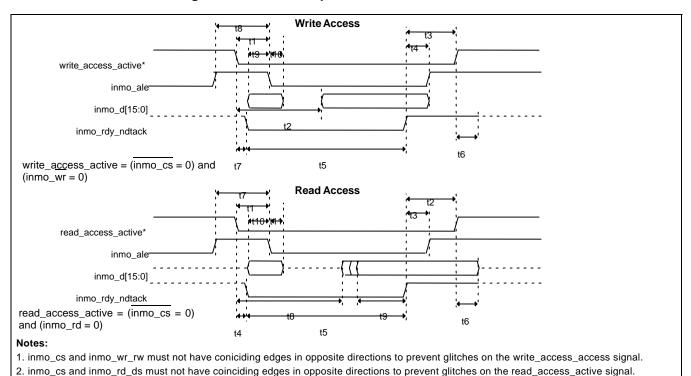

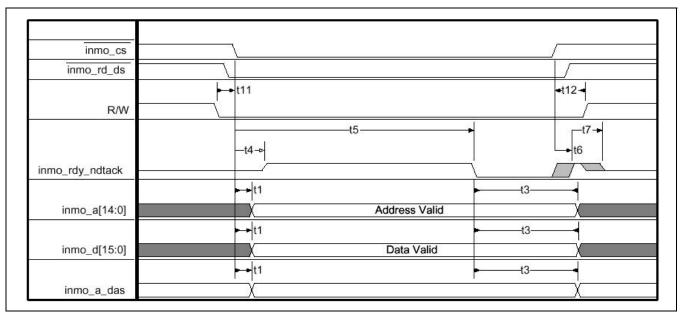

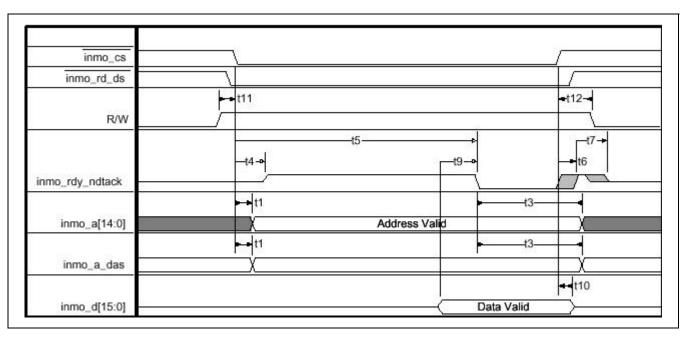

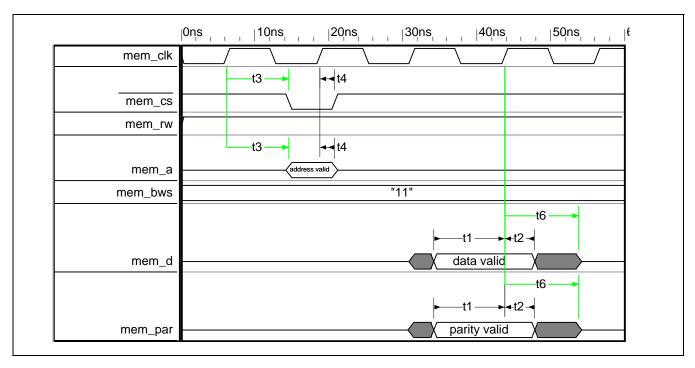

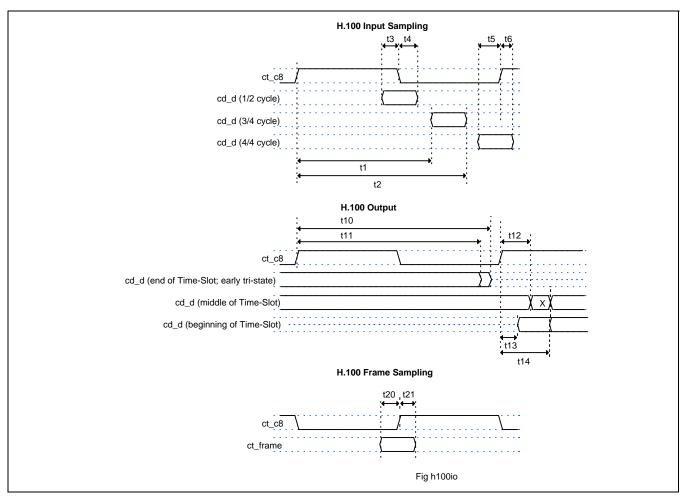

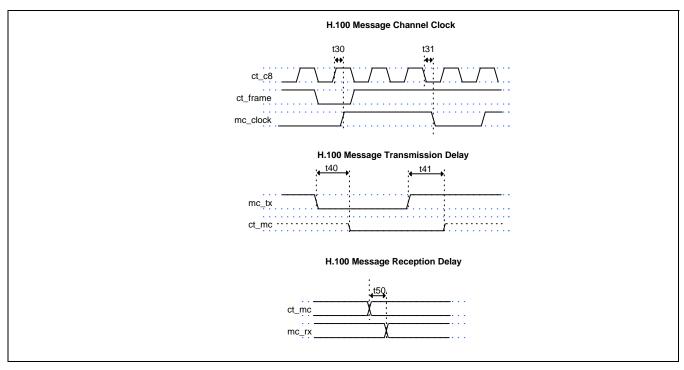

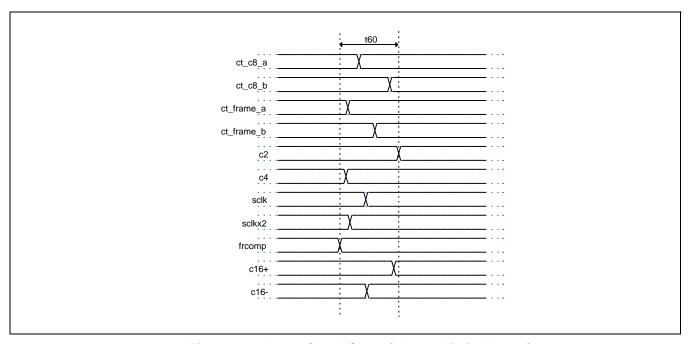

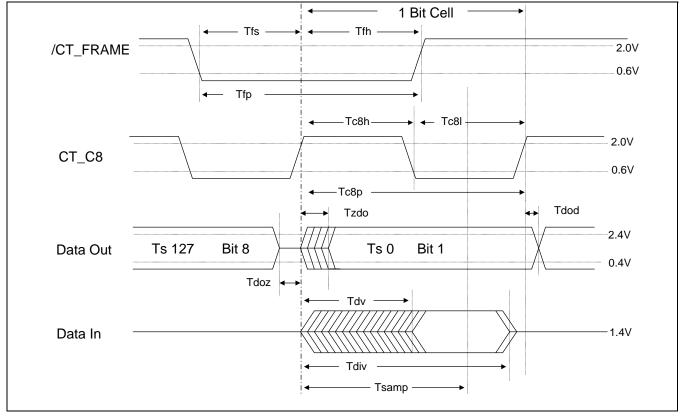

| 9.0 Interface Timing                      | 207 |

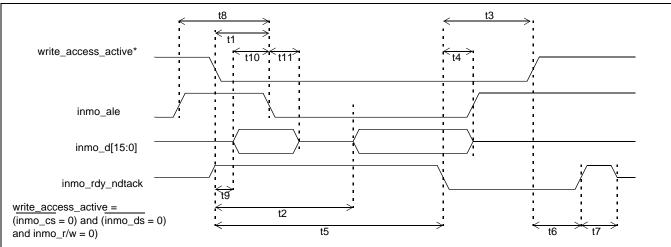

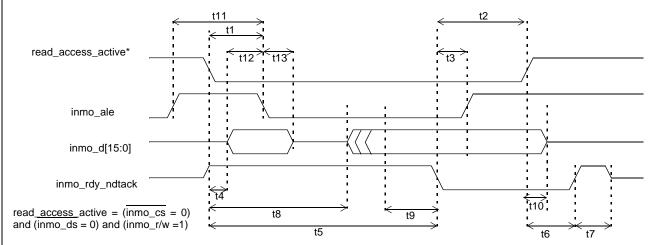

| 9.1 CPU Interface Timing                  | 207 |

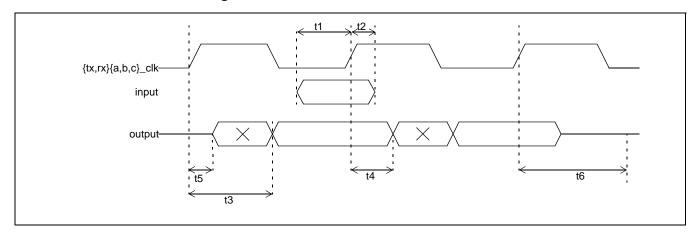

| 9.2 UTOPIA Interface Timing               | 215 |

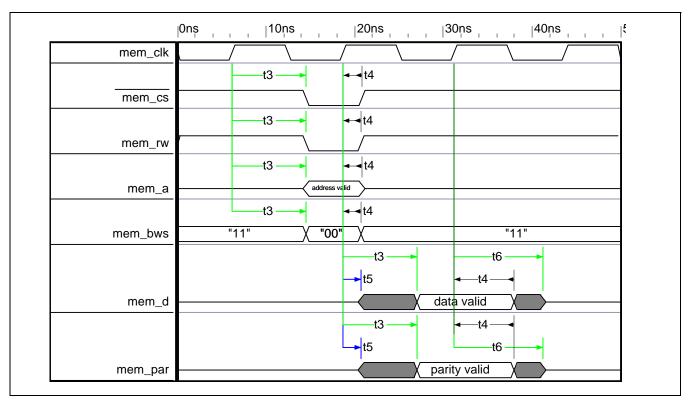

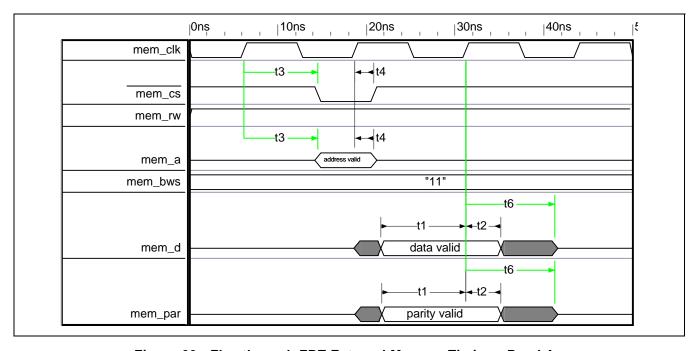

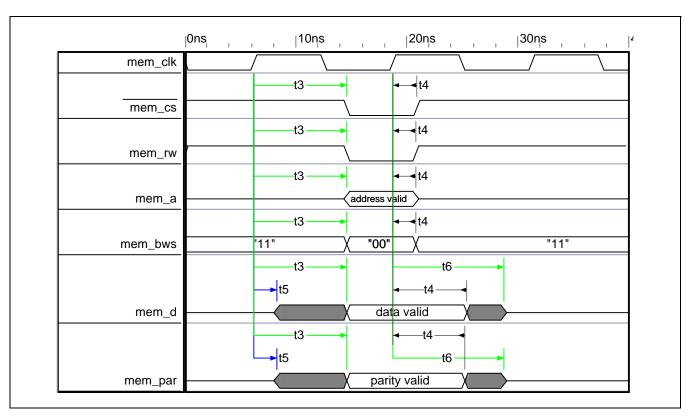

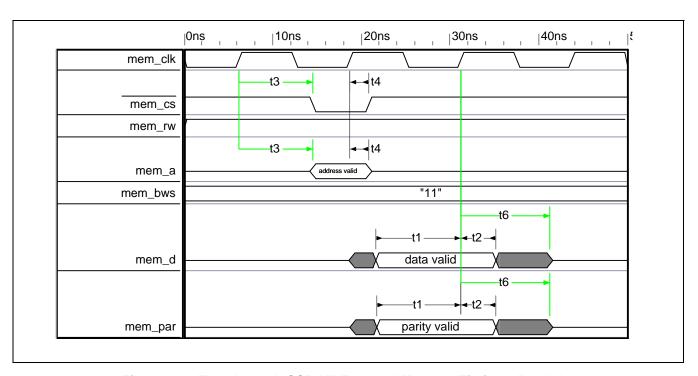

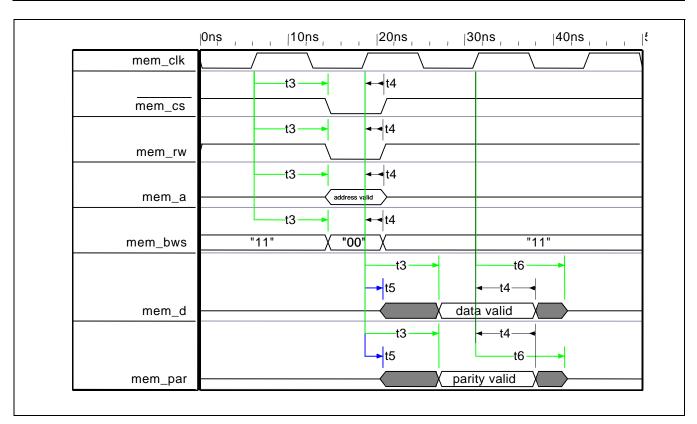

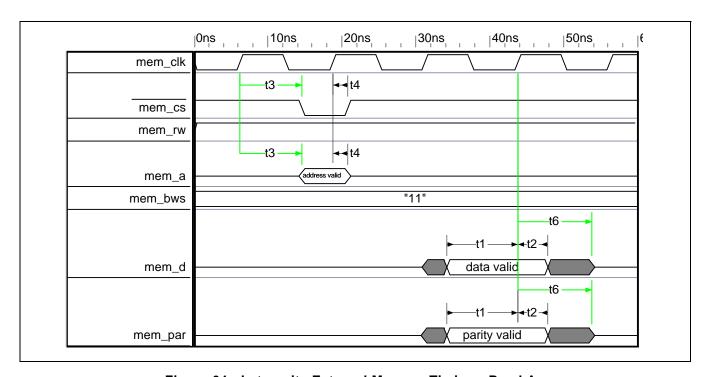

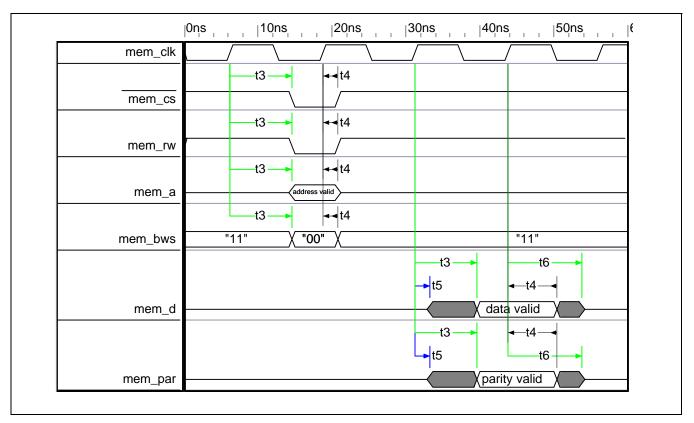

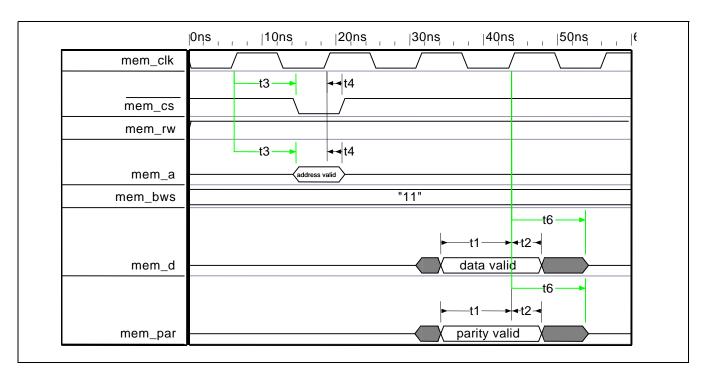

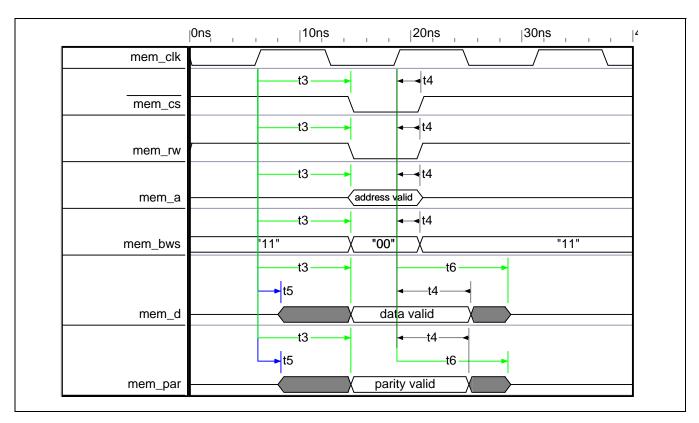

| 9.3 External Memory Timing                |     |

| 9.4 H.100/H.110 Interface Timing          |     |

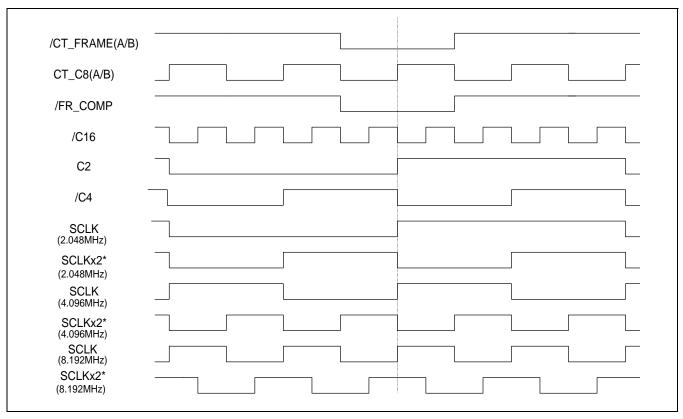

| 9.5 H.100/H.110 Clocking Signals          | 224 |

| 10.0 Glossary of Terms                    | 227 |

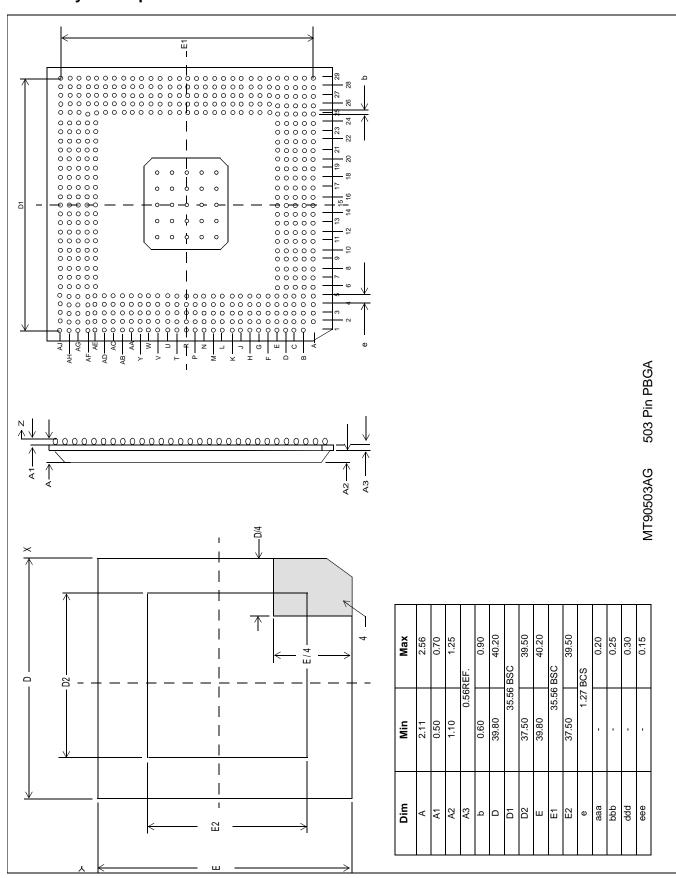

| 11.0 Physical Specification               | 231 |

## 1.0 Introduction

#### 1.1 Functional Overview of the MT90503

The MT90503 is an AAL1 SAR, which offers a highly integrated solution for interfacing telecom bus-based systems with ATM networks. The device has the capability of simultaneously processing 2048 bi-directional channels of 64 Kbps. The MT90503 can be connected directly to an H.100 or H.110 compatible bus. The device also offers the capability of using Channel Associated Signalling (CAS) to support Circuit Emulation Service (CES) for Structured Data Transfer (SDT).

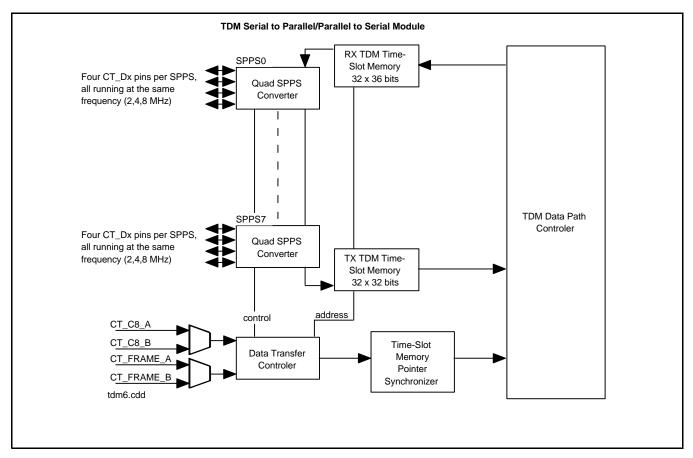

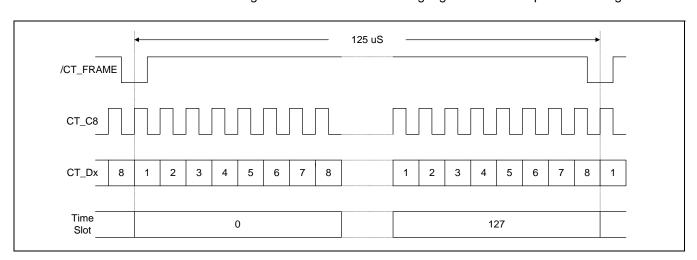

The interface to the TDM port is provided by a TDM bus, which consists of 32 bi-directional serial TDM data streams at 2.048, 4.096, or 8.192 Mbps, therefore allowing for 2048 bi-directional TDM channels operating at 64 kbps. This TDM bus is compatible with the ECTF H.100 and H.110 specifications.

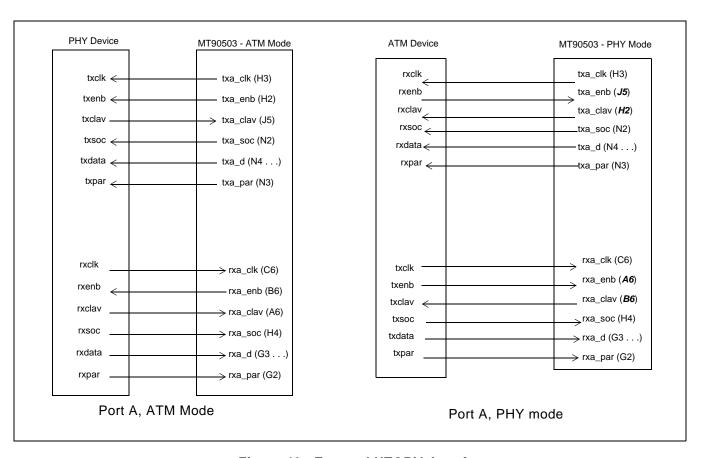

The interface to the ATM domain is provided by three UTOPIA ports (Ports A, B, and C). All three of the UTOPIA ports can operate in ATM (master) or PHY (slave) mode.

Port A is a UTOPIA Level 2 interface which can operate at up to 50 MHz using a 16- or an 8-bit data bus. This port is capable of operating in ATM-mode (single-PHY), in PHY-mode (slave-mode or level 1), or in slave MPHY-mode (Level 2).

Port B is a UTOPIA Level 2 interface, which can operate at up to 50 MHz using a 16- or an 8-bit data bus but does not support bus addressing. This port is capable of operating in ATM-mode (single-PHY), in PHY-mode (slave-mode).

Port C is a UTOPIA Level 1 interface which can operate at up to 50 MHz using an 8-bit data bus. This port is capable of operating in ATM-mode (master-mode), or in PHY-mode (slave-mode). The MT90503 is capable of performing a UTOPIA loopback from any incoming UTOPIA port to any outgoing UTOPIA port, including a loopback to the port of origin. The loopback capability could be used for dual fibre ring applications.

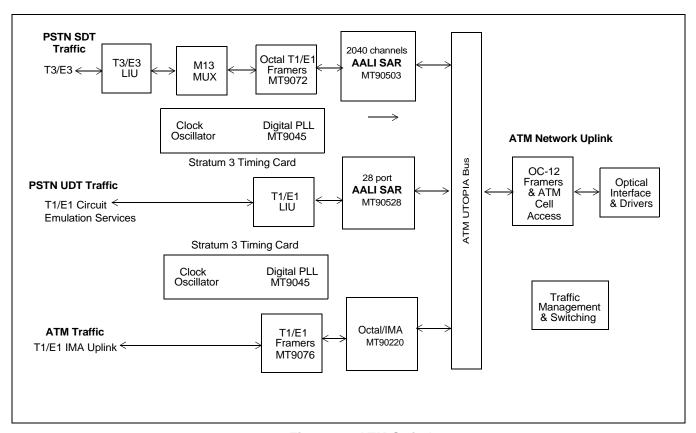

Figure 3 - Transmit Data Flow - TDM to UTOPIA

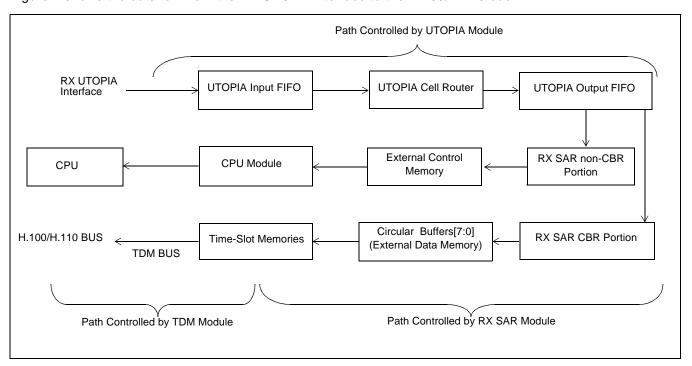

Figure 4 shows the dataflow from the RX UTOPA interface to the H.100/H.110 bus.

Figure 4 - Receive Data Flow - UTOPIA to TDM

# 2.0 Features Detailed Description

#### 2.1 UTOPIA Interface

- Contains 3 UTOPIA ports with transmit and receive interfaces:

- Port A: 16-bit or 8-bit UTOPIA Level 2, ATM mode (single-PHY) or PHY mode (single or multi-PHY). Accepts data rates up to 622 Mb/s.

- Port B: 16-bit or 8-bit UTOPIA Level 2 without bus addressing, ATM mode or PHY mode (restricted to 8-bit when Port A is in multi-PHY mode). Accepts data rates up to 622 Mb/s.

- Port C: 8-bit UTOPIA, ATM mode or PHY mode

- Supports cell switching through daisy chained SAR/PHY devices via the UTOPIA interface (AAL5 SARs, AAL1 SARs such as MT90503, and AAL2 SARs such as MT90502).

- Supports both UNI and NNI header formats.

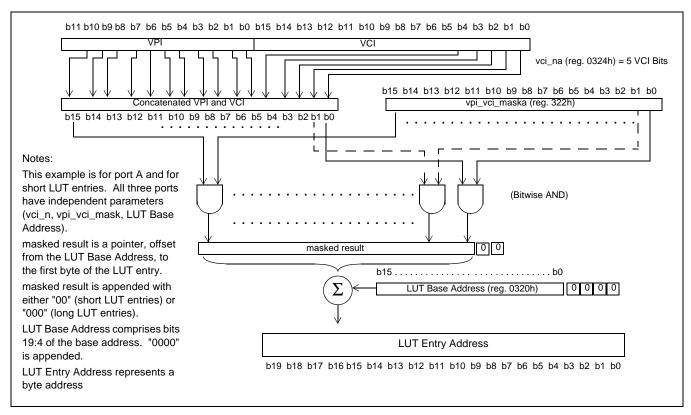

- Supports any combination of VCI/VPI concatenation up to 16 bits in ATM Receive direction.

- Supports up to 65536 Virtual Circuits Per UTOPIA Port in ATM Receive direction.

- Rapid timing reference cell processing in Receive/Segmentation direction

- Can eliminate null cells (VPI = 0, VCI = 0) received at UTOPIA A, B, and C port inputs.

- Filters received cells before accessing VCC Look Up Table (LUT).

- UTOPIA VCC loopback for bi-directional ring functionality (from RX A to TX B and from RX B to TX A).

- Per-VCC User cell and OAM cell destination control (for VCs that have a LUT entry).

- Per-UTOPIA-port User cell and OAM cell destination control (for VCs that do not have a LUT entry).

#### 2.2 TDM Interface

- H.100/H.110 compatable.

- Low latency TDM bus to TDM bus loopback of up to 2048 channels.

- Programmable value for the null-octet inserted during underrun situation.

- Receive buffer replay capability or silent pattern insertion for underrun situations.

- Support of CAS and MFS for DS1(ESF) and E1.

- Automatic Detection of a change in the CAS value, for CAS received in ATM cells, and CAS received from TDM bus.

## 2.3 Clock Recovery

- SRTS clock recovery:

- Dual reference VCs (for redundancy).

- Broadcast SRTS VCs in Transmit /Segmentation direction.

- Adaptive clock recovery:

- Dual reference VCs (for redundancy).

- Limited jitter, precision enhanced, MCLK (chip clock) to 8 kHz dividers.

- Direct 8 kHz clock recovery:

- Can generate an 8 kHz reference using one of 8 multipurpose timing reference pins.

- Supports all n \* 8 kHz input reference, (1.544 MHz, 2.048 MHz, 19.44 MHz, etc.) up to 12500 \* 8 kHz.

- Output high time and low time of the 8 kHz reference output can be modified relative to input signal.

- The eight multipurpose timing reference pins can be used to support many possible clock recovery configurations, including the following reference signals: SEC8K (MVIP), ATM8K (to/from PHY25 or from PHY155), FNXI (SRTS), CT\_NETREF (for CT-Bus).

- Can generate a 20 MHz clock for an external PLL, e.g. MT9042 or MT9044 (output on one of the multipurpose timing reference pin).

#### 2.4 ATM SAR

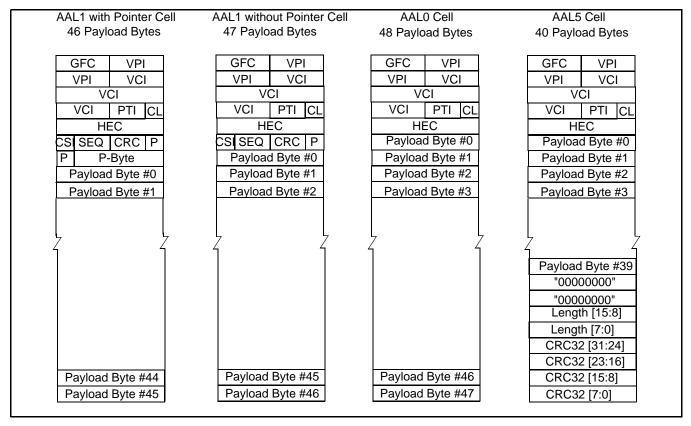

- Supports AAL1 (with pointer, or without pointer byte), CBR-AAL0, and CBR-AAL5 (AAL5-VTOA) Cell formats.

- Supports partially filled cells, with fills from 4 to 47 bytes.

- AAL1 cell format for "Structured DS1/E1 Nx64 Kbit/s Service" as per ATM Forum AF-VTOA-0078.000

"Circuit Emulation Services Interoperability Specification" (Nx64 Basic Service, DS1 Nx64 Service with CAS, and E1 Nx64 Service with CAS).

- VCs carrying 1 to 2048 TDM channels.

- TDM to ATM Transmission latency less than 250 μs (when minimum voice latency desired, and strict multiframe alignment of voice with CAS not required).

- TDM to ATM Transmission latency less than 3.25 ms (when strict multiframe alignment of voice with CAS required).

- ATM to TDM Reception latency less than CDV + 250 μs (when minimum voice latency desired, and strict multiframe alignment of voice with CAS not required).

- ATM to TDM Reception latency less than CDV + 6.250 ms (when strict multiframe alignment of voice with CAS required).

- Per VCC monitoring (Receive/Reassembly direction):

- CDV Monitoring and Delay Correction Fields.

- Single cell loss, multiple cell loss, cell misinsertion, AAL1 parity, AAL1-CRC, P-byte Parity, P-Byte Out-of-Range error bits.

- Cell Arrival Counter.

- Underrun Slip Counter.

- Overrun Slip Counte.r

- Per VCC monitoring (Transmit/Segmentation direction):

- Cell Transmission Counter.

- Single received cell loss compensated, replacing the payload with a programmable null-octet.

- Support segmentation and reassembly of 2048 full duplex TDM channels (2048 without CAS, subtract one TDM channel for each CAS channel carried).

- Support of up to  $\pm 61$  ms of CDV in non-multiframing mode,  $\pm 45$  ms in T1 with strict multiframing,  $\pm 29$  ms in E1 with strict multiframing.

- AAL0 Cell Generation / Reception for software implemented SAR function (cell buffer can contain up to 1024 cells).

- Percentage of bandwidth usage register (Transmit/Segmentation direction).

## 2.5 Required External Components

- 28K/256K/512K x 18 Control Memory (can be used in up to 2 banks).

- Maximum addressable control memory: 1 MB.

- 128K/256K/512K x 18 Data Memory (can be used in up to 4 banks).

- Maximum addressable data memory: 4 MB.

- 8 kHz to 16/19.44/32 MHz PLL.

- Clock driver for mem\_clk\_o.

## 2.6 Particular Modes of Operation

- Test modes

- TX SAR to RX SAR internal loop-back of some VCs, while MT90503 is running.

- TDM Bus Internal loop-back.

- TDM Bus External loop-back.

## 2.7 Miscellaneous

- Motorola/Intel CPU Interface (paged memory accesses).

- Programmable Maximum number of Interrupts per second.

- Multipurpose I/Os.

- LED pin generation for UTOPIA Interface.

- Parity bits on memory and UTOPIA interfaces to ensure clocking and memory access integrity.

- CPU-based OAM cell treatment.

- JTAG (IEEE 1149) Test Access Port.

- MCLK speed of 80 MHz.

- Global reset pin with I/O tri-state.

- Global power-down and tri-state.

## 2.8 Power

- 3.3V core and I/O supply.

- All I/Os are 3.3V with 5 V tolerance.

- TDM pins are PCI 5V signalling tolerant (when PCI clamp rail tied to 5 V).

# 3.0 Pin Designations and Descriptions

The following tables identify each pin of the MT90503 device's main functional areas. A description of each pin is also provided.

#### Notes:

- 1 All outputs are +3.3 V<sub>DC</sub>

- 2 All input and output pins that are designated (F) can withstand 5 V<sub>DC</sub> being applied to them.

- 3 All input and output pins that are designated (F) are tested with a 50 pF load unless otherwise specified.

- Designations under the "rst" (reset condition) table column are: X = undefined; Z = high impedance;  $1 = \text{high (+3.3 V}_{DC})$ .

- 5 I/O types include: Output (O), Input (I), Bidirectional (I/O), Power (PWR) and Ground (GND).

- 6 All buses have pins listed in order from MSB to LSB.

**GND pins:** A2, A4, A7, A8, A9, A12, A15, A18, A21, A22, A23, A25, A26, A28, B1, B29, D1, D26, D29, E1, E6, E29, G1, G29, H1, H29, J1, J29, L11, L13, L15, L17, L19, M1, M29, N11, N13, N15, N17, N19, R1, R11, R13, R17, R19, R29, T29, U11, U13, U15, U17, U19, V1, W11, W13, W15, W17, W19, AA1, AA29, AB1, AB29, AC1, AD5, AD25, AE1, AE13, AE29, AF1, AF29, AG29, AH1, AH2, AH28, AJ2, AJ4, AJ7, AJ8, AJ9, AJ12, AJ15, AJ18, AJ21, AJ22, AJ23, AJ25, AJ26, AJ28

**VDD 3.3V pins**: A3, A5, A10, A11, A14, A16, A19, A20, A27, A29, B2, C1, C29, K1, K29, L1, L29, P1, P29, T1, V29, W1, W29, Y1, Y29, AC29, AG1, AH3, AH29, AJ1, AJ3, AJ5, AJ10, AJ11, AJ14, AJ16, AJ19, AJ20, AJ27, AJ29

**Pins not connected:** A13, B3, B4, B7, B8, B9, B12, B13, B14, B15, B16, C3, C4, C7, C8, C9, C12, C13, C14, C15, D6, D7, D8, D9, D12, D13, D14, D15, D24, E5, E8, E9, E12, E13, E14, E15, E25, M5, M28, T25, W25, AB25, AE4, AE5, AE23, AE25, AF2, AF23, AE22

| Pin                                                                                                  | rst | Name                          | 1/0 | Туре          | Description                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------|-----|-------------------------------|-----|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AE18, AF18, AG18,<br>AH18, AE19, AF19,<br>AG19, AH19, AF20,<br>AG20, AH20, AE21,<br>AF21, AG21, AH21 | Z   | inmo_a [14:0]                 | I   | TTL (F)       | Intel/Motorola interface address bus. Can be used as a GPI.                                                                                                                                                                  |

| AE14, AF14, AG14,<br>AH14, AG15, AH15,<br>AE16, AF16                                                 | Z   | inmo_d [7:0]                  | I/O | TTL, 4 mA (F) | Intel/Motorola interface data bus, low bits                                                                                                                                                                                  |

| AE12, AF12, AG12,<br>AH12, AF13, AG13,<br>AH13,AJ13,                                                 | Z   | inmo_d[15:8]                  | I/O | TTL, 4 mA (F) | Intel/Motorola interface data bus, high bits. Can be used as a GPIO if an 8 bit CPU Interface is used.                                                                                                                       |

| AF11                                                                                                 |     | mclk_src                      | I   | TTL (F)       | Master Clock Source. An external clock that is multiplied to generate mclk.                                                                                                                                                  |

| AE11                                                                                                 |     | reset                         | 1   | Schmitt (F)   | General Reset                                                                                                                                                                                                                |

| AJ17                                                                                                 | Z   | inmo_a_das                    | I   | TTL, 4 mA (F) | Direct Access Select. '1' selects the direct access space. '0' selects the indirection registers contained in the CPU interface. This pin can be connected to a[15] of an address bus but does not behave as an address pin. |

| AH17                                                                                                 | Z   | inmo_cs                       | I   | TTL, 4 mA (F) | Intel/Motorola interface chip select                                                                                                                                                                                         |

| AG17                                                                                                 |     | inmo_ale                      | I   | TTL (F)       | Intel/Motorola interface address latch enable                                                                                                                                                                                |

| AF17                                                                                                 |     | inmo_wr_r/w                   | Ι   | TTL (F)       | Intel write or Motorola read/write                                                                                                                                                                                           |

| AH16                                                                                                 |     | inmo_rd_ds                    | I   | TTL (F)       | Intel read or Motorola data strobe                                                                                                                                                                                           |

| AG16                                                                                                 | Z   | inmo_rdy_ <mark>ndtack</mark> | 0   | TTL, 8 mA (F) | Intel/Motorola interface ready/data acknowledge. This pin is active high for Intel (rdy) and active low for Motorola (ndtack).                                                                                               |

| AE20                                                                                                 |     | cpu_mode[0]                   | I   | TTL (F)       | CPU Interface Mode Select Bit 0. The CPU Interface Mode Select bits must be hardwired.                                                                                                                                       |

| AG22                                                                                                 |     | cpu_mode[1]                   | I   | TTL (F)       | CPU Interface Mode Select Bit 1.                                                                                                                                                                                             |

| AH22                                                                                                 |     | cpu_mode[2]                   | ı   | TTL (F)       | CPU Interface Mode Select Bit 2.                                                                                                                                                                                             |

| AF22                                                                                                 |     | cpu_mode[3]                   | I   | TTL (F)       | CPU Interface Mode Select Bit 3.                                                                                                                                                                                             |

| AH11                                                                                                 | Z   | interrupt1                    | 0   | 4 mA (F)      | frequency-controllable global interrupt                                                                                                                                                                                      |

| AG11                                                                                                 | Z   | interrupt2                    | 0   | 4 mA (F)      | instant global interrupt                                                                                                                                                                                                     |

Table 1 - CPU Bus Interface Pins

| Pin                                                                                                                           | rst | Name                             | I/O          | Туре      | Description                                                           |

|-------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|--------------|-----------|-----------------------------------------------------------------------|

| AG23, AH23,<br>AE24, AF24,<br>AG24, AH24, AJ24,<br>AF25, AG25,<br>AH25, AG26,<br>AH26, AH27,<br>AA26, AA27, AA28,<br>W27, W28 | Х   | cmem_a [17:0]                    | 0            | 4 mA      | Control memory address bus                                            |

| W26                                                                                                                           | 1   | 1. cmem_a [18]<br>2. cmem_cs [1] | 1. O<br>2. O | 4 mA      | Control memory address bus     Control memory chip select 1.          |

| AG28, AF27,<br>AE26, AE28,<br>AD27, AC26,<br>AC28, AB27, AF28,<br>AE27, AD26,<br>AC25, AC27,<br>AB26, AB28, AA25              | Z   | cmem_d[15:0]                     | I/O          | TTL, 4 mA | Control memory data bus.                                              |

| Y25                                                                                                                           | 1   | cmem_cs[0]                       | 0            | 4 mA      | Control memory chip select 0                                          |

| Y27                                                                                                                           | Х   | cmem_bws[0]                      | 0            | 4 mA      | Control memory byte write select 0.                                   |

| Y26                                                                                                                           | Х   | cmem_bws[1]                      | 0            | 4 mA      | Control memory byte write select 1.                                   |

| Y28                                                                                                                           | Х   | cmem_r/w                         | 0            | 4 mA      | Control Memory R/W. This signal is only used for late write memories. |

| AG27, AF26                                                                                                                    | Z   | cmem_par[1:0]                    | I/O          | TTL, 4 mA | Control Memory Parity 1:0                                             |

**Table 2 - Control Memory Bus Interface Pins**

| Pin                                                                                                             | rst | Name         | I/O | Туре      | Description                                                        |

|-----------------------------------------------------------------------------------------------------------------|-----|--------------|-----|-----------|--------------------------------------------------------------------|

| T28, K26, V28,<br>U29, T27, T26,<br>R28, K25, J27,<br>J26, H28, H27,<br>L25, H25, J28,<br>G27, F25, F27,<br>F29 | Х   | dmem_a[18:0] | 0   | 4 mA      | Data memory address bus                                            |

| P25, N28, N26,<br>M27, L28, L26,<br>K28, K27, P28,<br>P26, N29, N27,<br>N25, M26, L27,<br>M25                   | Z   | dmem_d[15:0] | I/O | TTL, 4 mA | Data memory data bus                                               |

| U25                                                                                                             | Х   | dmem_rw      | 0   | 4 mA      | Data Memory R/W. This signal is only used for late write memories. |

| U26                                                                                                             | Х   | dmem_bws[0]  | 0   | 4 mA      | Data memory byte write select 0.                                   |

| U27                                                                                                             | Х   | dmem_bws[1]  | 0   | 4 mA      | Data memory byte write select 1.                                   |

Table 3 - Data Memory Bus Interface Pins

| U28 | 1 | dmem_cs[0]  | 0   | 4 mA      | Data memory chip select 0 |

|-----|---|-------------|-----|-----------|---------------------------|

| V27 | 1 | dmem_cs[1]  | 0   | 4 mA      | Data memory chip select 1 |

| V26 | 1 | dmem_cs[2]  | 0   | 4 mA      | Data memory chip select 2 |

| V25 | 1 | dmem_cs[3]  | 0   | 4 mA      | Data memory chip select 3 |

| R27 | Z | dmem_par[0] | I/O | TTL, 4 mA | Data memory parity 0      |

| P27 | Z | dmem_par[1] | I/O | TTL, 4 mA | Data memory parity 1      |

Table 3 - Data Memory Bus Interface Pins

| Pin  | rst | Name               | I/O | Туре | Description                          |

|------|-----|--------------------|-----|------|--------------------------------------|

| AD29 |     | mem_clk_i          | I   | TTL  | Data and Control memory clocks       |

| AD28 | Х   | mem_clk_o          | 0   | 4 mA | Data and Control memory clocks       |

| R26  |     | mem_clk_positive_i | 1   | PECL | Data and Control memory clocks, PECL |

| R25  |     | mem_clk_negative_i | 1   | PECL | Data and Control memory clocks, PECL |

| AF15 | Х   | mem_clk_positive_o | 0   | PECL | Data and Control memory clocks, PECL |

| AE15 | Х   | mem_clk_negative_o | 0   | PECL | Data and Control memory clocks, PECL |

Table 4 - Data and Control Memory Clock Pins

| Pin                                                                                                                                                                                    | rst | Name       | I/O | Туре                  | Description                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----|-----------------------|---------------------------------------|

| B17, A17, E22, D17,<br>B19, B18, E16, C18,<br>C16, C20, E18,<br>E17, D16, E21, B22,<br>B21, B20, B23, E19,<br>C19, D23, D22,<br>C22, D19, C24,<br>B24, A24, E20, C21,<br>B26, C23, D21 | Z   | ct_d[31:0] | I/O | PCI (F)               | H.100/H.110 serial data bus           |

| G25                                                                                                                                                                                    | Z   | ct_netref1 | I/O | Schmitt, 12 mA<br>(F) | H.100/H.110 Network Reference 1.      |

| G26                                                                                                                                                                                    | Z   | ct_netref2 | I/O | Schmitt, 12 mA<br>(F) | H.100/H.110 Network Reference 2.      |

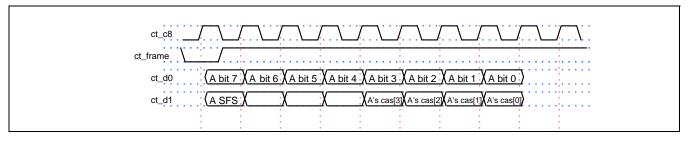

| C28                                                                                                                                                                                    | Z   | ct_c8_a    | I/O | Schmitt, 12 mA<br>(F) | H.100/H.110 8 MHz clock A             |

| B28                                                                                                                                                                                    | Z   | ct_c8_b    | I/O | Schmitt, 12 mA<br>(F) | H.100/H.110 8 MHz clock B             |

| C27                                                                                                                                                                                    | Z   | ct_frame_a | I/O | Schmitt, 12 MA<br>(F) | H.100/H.110 Frame pulse A             |

| C26                                                                                                                                                                                    | Z   | ct_frame_b | I/O | Schmitt, 12 MA<br>(F) | H.100/H.110 Frame pulse B             |

| E26                                                                                                                                                                                    | Z   | ct_fr_comp | 0   | 12 mA (F)             | H.100/H.110 compatibility frame pulse |

| D27                                                                                                                                                                                    | Z   | ct_c2      | 0   | 12 mA (F)             | MVIP 90-bit clock                     |

Table 5 - H.100/H.110 Bus Interface Pins

| Pin | rst | Name      | I/O | Туре              | Description                                                                                                                                       |

|-----|-----|-----------|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| D28 | Z   | ct_c4     | 0   | 12 mA (F)         | MVIP 90-bit clock times two                                                                                                                       |

| E23 | Z   | ct_c16-   | 0   | 12 mA (F)         | H-MVIP 16 MHz clock                                                                                                                               |

| D25 | Z   | ct_c16+   | 0   | 12 mA (F)         | H-MVIP 16 MHz clock                                                                                                                               |

| E27 | Z   | ct_sclk   | 0   | 12 mA (F)         | SCBUS system clock                                                                                                                                |

| E28 | Z   | ct_sclkx2 | 0   | 12 mA (F)         | SCBUS system clock times two                                                                                                                      |

| F26 |     | ct_mc     | I/O | TTL,<br>12 mA (F) | H.100/H.110 Message Channel. Open<br>Collector output.                                                                                            |

| E24 | Х   | mc_clock  | 0   | 4 mA (F)          | H.100/H.110 Message Channel extracted clock. 2 MHz. Nominal duty cycle: 62% high, 38% low.                                                        |

| B27 |     | mc_tx     | I   | TTL (F)           | H.100/H.110 Message channel transmit data. When this signal is '0', the MT90503 will drive ct_mc low. When '1', the MT90503 will not drive ct_mc. |

| C25 | Х   | mc_rx     | 0   | 4 mA (F)          | H.100/H.110 Message channel receive data. The level of this pin directly reflects the value of ct_mc.                                             |

| B25 |     | ct_vdd5_0 | I   |                   | 5V power supply used in PCI Buffers of the ct_d[31:0] signals. Can also be connected to 3V power supply.                                          |

| D20 |     | ct_vdd5_1 | 1   |                   | See ct_vdd5_0.                                                                                                                                    |

| D18 |     | ct_vdd5_2 | 1   |                   | See ct_vdd5_0.                                                                                                                                    |

| C17 |     | ct_vdd5_3 | I   |                   | See ct_vdd5_0.                                                                                                                                    |

Table 5 - H.100/H.110 Bus Interface Pins (continued)

| Pin | rst | Name    | I/O | Туре          | Description                                                   |

|-----|-----|---------|-----|---------------|---------------------------------------------------------------|

| E10 | Z   | recov_a | I/O | TTL, 4 mA (F) | Clock recovery general I/O A. This pin can be used as a GPIO. |

| D10 | Z   | recov_b | I/O | TTL, 4 mA (F) | Clock recovery general I/O B. This pin can be used as a GPIO. |

| C10 | Z   | recov_c | I/O | TTL, 4 mA (F) | Clock recovery general I/O C. This pin can be used as a GPIO. |

| B10 | Z   | recov_d | I/O | TTL, 4 mA (F) | Clock recovery general I/O D. This pin can be used as a GPIO. |

| E11 | Z   | recov_e | I/O | TTL, 4 mA (F) | Clock recovery general I/O E. This pin can be used as a GPIO. |

| D11 | Z   | recov_f | I/O | TTL, 4 mA (F) | Clock recovery general I/O F. This pin can be used as a GPIO. |

| C11 | Z   | recov_g | I/O | TTL, 4 mA (F) | Clock recovery general I/O G. This pin can be used as a GPIO. |

| B11 | Z   | recov_h | I/O | TTL, 4 mA (F) | Clock recovery general I/O H. This pin can be used as a GPIO. |

**Table 6 - Clock Recovery Pins**

| Pin Switch rst Name I/O Type Descriptio |  |

|-----------------------------------------|--|

|-----------------------------------------|--|

**Table 7 - Test Pins**

| AE17 | 0 |   | global_tri_state | I | TTL (F)       | (PU) Should be 1 for functional mode, 0 for tristate. |

|------|---|---|------------------|---|---------------|-------------------------------------------------------|

| AH5  | 1 |   | tck              | I | TTL (F)       | JTAG Test Clock. Should be 0 when not in use          |

| AG5  | 1 |   | tdi              | I | TTL (F)       | JTAG Test Data In. Should be 0 when not in use        |

| AH4  | 1 | Х | tdo              | 0 | TTL, 4 mA (F) | JTAG Test Data Out                                    |

| AG4  | 1 |   | tms              | I | TTL (F)       | JTAG Test Mode Select. Should be 0 when not in use.   |

| AE7  | 1 |   | trst             | I | TTL (F)       | JTAG Test Reset. Should be 0 when not in use.         |

Table 7 - Test Pins

| Pin                               | rst          | Name                             | I/O        | Туре           | Description                                                                                                                                                     |

|-----------------------------------|--------------|----------------------------------|------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H3                                | Z            | txa_clk                          | I/O        | TTL, 4 mA (F)  | UTOPIA Port A TX Clock                                                                                                                                          |

| C6                                | Z            | rxa_clk                          | I/O        | TTL, 4 mA (F)  | UTOPIA Port A RX Clock                                                                                                                                          |

| C2                                |              | phya_alm                         | I          | TTL (F)        | PHY alarm A This pin can also act as a GPI.                                                                                                                     |

| D2                                | Z            | phya_rx_led                      | I/O        | TTL, 12 mA (F) | LED signal. When the LED is on, this pin will be '0'. When the LED is off, this pin will be tri-state. This pin can also act as a GPIO.                         |

| H5                                | Z            | phya_tx_led                      | I/O        | TTL, 12 mA (F) | LED signal. When LED is on, this pin will be '0'. When the LED is off, this pin will be tri-state. This pin can also act as a GIPO.                             |

| J5                                |              | 1. <u>txa_clav</u><br>2. txa_enb | 1.I<br>2.I | TTL (F)        | UTOPIA Port A TX Cell Available (in ATM)     UTOPIA Port A TX Enable (in PHY)                                                                                   |

| H2                                | 1.Z<br>2.Z   | 1. txa_enb<br>2. txa_clav        | 1.0<br>2.0 | 4 mA (F)       | UTOPIA Port A TX Enable (in ATM). This pin must be pulled-up externally.     UTOPIA Port A TX Cell Available (in PHY). This pin must be pulled-down externally. |

| N2                                | Z            | txa_soc                          | 0          | 4 mA (F)       | UTOPIA Port A TX Start of Cell                                                                                                                                  |

| L5, K2, K3, K4,<br>K5, J2, J3, J4 | Z            | txa_data[7:0]                    | 0          | 4 mA (F)       | UTOPIA Port A TX Data bus                                                                                                                                       |

| N4, N5, M2, M3,<br>M4, L2, L3, L4 | Z            | txa_data[15:8]                   | I/O        | TTL, 4 mA (F)  | UTOPIA Port A TX Data bus Each of these pins can be used as a GPIO.                                                                                             |

| N3                                | Z            | txa_par                          | 0          | 4 mA (F)       | UTOPIA Port A TX Parity                                                                                                                                         |

| A6                                |              | 1. <u>rxa_clav</u><br>2. rxa_enb | 1.I<br>2.I | TTL (F)        | UTOPIA Port A RX Cell Available (in ATM)     UTOPIA Port A RX Enable (in PHY)                                                                                   |

| B6                                | 1. Z<br>2. Z | 1. rxa_enb<br>2. rxa_clav        | 1.0        | 4 mA (F)       | UTOPIA Port A RX Enable (in ATM). This pin must be pulled-up externally.     UTOPIA Port A RX Cell Available (in PHY). This pin must be pulled-down externally. |

| H4                                |              | rxa_soc                          | ı          | TTL (F)        | UTOPIA Port A RX Start of Cell                                                                                                                                  |

| E2, E3, E4, D3,<br>D4, D5, C5, B5 |              | rxa_data[7:0]                    | I          | TTL (F)        | UTOPIA Port A RX Data bus                                                                                                                                       |

| G3, G4, G5, F1,<br>F2, F3, F4, F5 |              | rxa_data[15:8]                   | 1          | TTL (F)        | UTOPIA Port A RX Data bus<br>Each of these pins can be used as a GPI.                                                                                           |

| G2                                |              | rxa_par                          | I          | TTL (F)        | UTOPIA Port A RX Parity                                                                                                                                         |

**Table 8 - UTOPIA Interface Pins**

| Pin                                      | rst        | Name                                        | I/O        | Туре           | Description                                                                                                                                                        |

|------------------------------------------|------------|---------------------------------------------|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W4                                       | Z          | txb_clk                                     | I/O        | TTL, 4 mA      | UTOPIA Port B TX Clock                                                                                                                                             |

| N1                                       | Z          | rxb_clk                                     | I/O        | TTL, 4 mA (F)  | UTOPIA Port B RX Clock                                                                                                                                             |

| AB5                                      |            | phyb_alm                                    | I          | TTL (F)        | PHY alarm B<br>This pin can also act as a GPI.                                                                                                                     |

| W5                                       | Z          | phyb_rx_led                                 | I/O        | TTL, 12 mA (F) | LED signal. When LED is on, this pin will be '0'. When the LED is off, this pin will be tri-state. This pin can also act as a GPIO.                                |

| Т5                                       | Z          | phyb_tx_led                                 | I/O        | TTL, 12 mA (F) | LED signal. When LED is on, this pin will be '0'. When the LED is off, this pin will be tri-state. This pin can also act as a GPIO.                                |

| W2                                       |            | 1. txb_clav<br>2. txb_enb                   | 1.I<br>2.I | TTL (F)        | UTOPIA Port B TX Cell Available (in ATM)     UTOPIA Port B TX Enable (in PHY)                                                                                      |

| W3                                       | 1Z<br>2Z   | 1. txb_enb<br>2. txb_clav                   | 1.0<br>2.0 | 4 mA (F)       | UTOPIA Port B TX Enable (in ATM) This pin must be pulled-up externally.     UTOPIA Port B TX Cell Available (in PHY).     This pin must be pulled-down externally. |

| AD2                                      | Z          | txb_soc                                     | 0          | 4 mA (F)       | UTOPIA Port B TX Start of Cell                                                                                                                                     |

| AA2, AA3, AA4,<br>AA5, Y2, Y3,<br>Y4, Y5 | Z          | txb_data[7:0]                               | 0          | 4 mA (F)       | UTOPIA Port B TX Data bus                                                                                                                                          |

| AC3, AC4, AG2,<br>AB2, AB3, AB4          | Z          | txb_data[13:8]                              | I/O        | TTL, 4 mA (F)  | UTOPIA Port B TX Data bus Each of these pins can be used as a GPIO.                                                                                                |

| AC2                                      | Z          | 1. txb_data<br>[14]<br>2. rxa_addr[4]       | 1.O<br>2.I | TTL, 4 mA (F)  | UTOPIA Port B TX Data bus     UTOPIA Port A RX Address 4     This pins can be used as a GPIO.                                                                      |

| AD4                                      | Z          | 1. txb_data [15]<br>2. txa_addr[4]          | 1.0<br>2.I | TTL, 4 mA (F)  | UTOPIA Port B TX Data bus     UTOPIA Port A TX Address 4     This pin can be used as a GPIO.                                                                       |

| AD3                                      | Z          | txb_par                                     | 0          | 4 mA (F)       | UTOPIA Port B TX Parity                                                                                                                                            |

| P4                                       |            | 1. <u>rxb_clav</u><br>2. rxb_enb            | 1.I<br>2.I | TTL (F)        | UTOPIA Port B RX Cell Available (in ATM)     UTOPIA Port B RX Enable (in PHY)                                                                                      |

| P5                                       | 1.Z<br>2.Z | 1. rxb_enb<br>2. rxb_clav                   | 1.0<br>2.0 | 4 mA (F)       | UTOPIA Port B RX Enable (in ATM). This pin must be pulled-up externally.     UTOPIA Port B RX Cell Available (in PHY). This pin must be pulled-down externally.    |

| V2                                       |            | rxb_soc                                     | I          | TTL (F)        | UTOPIA Port B RX Start of Cell                                                                                                                                     |

| T3, T4, R2, R3,<br>R4, R5, P2, P3        |            | rxb_data [7:0]                              | I          | TTL (F)        | UTOPIA Port B RX Data bus                                                                                                                                          |

| U3, U4, U5, T2                           |            | 1. rxb_data [11:8]<br>2. rxa_addr [3:0]     | 1.l<br>2.l | TTL (F)        | 1.UTOPIA Port B RX Data bus<br>2. UTOPIA Port A RX Address bus                                                                                                     |

| V4, V5, U1, U2                           |            | 1. rxb_data<br>[15:12]<br>2. txa_addr [3:0] | 1.l<br>2.l | TTL (F)        | UTOPIA Port B RX Data bus     UTOPIA Port A TX Address bus                                                                                                         |

| V3                                       |            | rxb_par                                     | 1          | TTL (F)        | UTOPIA Port B RX Parity                                                                                                                                            |

| AG10                                     | Z          | txc_clk                                     | I/O        | TTL, 4 mA (F)  | UTOPIA Port C TX Clock                                                                                                                                             |

| AF7                                      | Z          | rxc_clk                                     | I/O        | TTL, 4 mA (F)  | UTOPIA Port C RX Clock                                                                                                                                             |

Table 8 - UTOPIA Interface Pins (continued)

| Pin                                          | rst          | Name                      | I/O        | Туре     | Description                                                                                                                                                     |

|----------------------------------------------|--------------|---------------------------|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AE10                                         |              | 1. txc_clav<br>2. txc_enb | 1.I<br>2.I | TTL (F)  | UTOPIA Port C TX Cell Available (in ATM).     UTOPIA Port C TX Enable (in PHY).                                                                                 |

| AF10                                         | 1. Z<br>2. Z | 1. txc_enb<br>2. txc_clav | 1.0<br>2.0 | 4 mA (F) | UTOPIA Port C TX Enable (in ATM). This pin must be pulled-up externally.     UTOPIA Port C TX Cell Available (in PHY). This pin must be pulled-down externally. |

| AH9                                          | Z            | txc_soc                   | 0          | 4 mA (F) | UTOPIA Port C TX Start of Cell                                                                                                                                  |

| AG9, AF9, AE9,<br>AH8, AG8, AF8,<br>AE8, AH7 | Z            | txc_data[7:0]             | 0          | 4 mA (F) | UTOPIA Port C TX Data bus                                                                                                                                       |

| AG7                                          | Z            | txc_par                   | 0          | 4 mA (F) | UTOPIA Port C TX Parity                                                                                                                                         |

| AH6                                          |              | 1. rxc_clav<br>2. rxc_enb | 1.I<br>2.I | TTL (F)  | UTOPIA Port C RX Cell Available (in ATM)     UTOPIA Port C RX Enable (in PHY)                                                                                   |

| AJ6                                          | 1. Z<br>2. Z | 1. rxc_enb<br>2. rxc_clav | 1.0<br>2.0 | 4 mA (F) | UTOPIA Port C RX Enable (in ATM). This pin must be pulled-up externally.     UTOPIA Port C RX Cell Available (in PHY). This pin must be pulled-down externally. |

| AG6                                          | 1.Z          | rxc_soc                   | I          | TTL (F)  | UTOPIA Port C RX Start of Cell                                                                                                                                  |

| AF6, AE6, AF5,<br>AF4, AE2, AE3,<br>AF3, AD1 |              | rxc_data[7:0]             | 1          | TTL (F)  | UTOPIA Port C RX Data bus                                                                                                                                       |

| AH10                                         |              | rxc_par                   | I          | TTL (F)  | UTOPIA Port C RX Parity                                                                                                                                         |

Table 8 - UTOPIA Interface Pins (continued)

| Pin | rst | Name       | 1/0 | Туре | Description                                                                                                    |

|-----|-----|------------|-----|------|----------------------------------------------------------------------------------------------------------------|

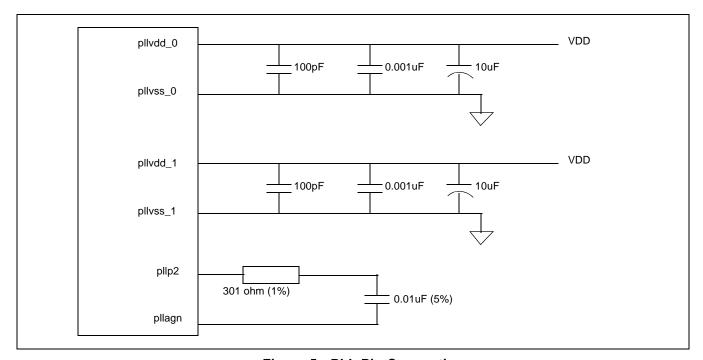

| J25 |     | pllvss_110 | I   |      | VSS pin for the CT PLL. See Figure 5, "PLL Pin Connections," on page 25 for recommended connections.           |

| F28 |     | Pllvdd_110 | I   |      | VDD pin for the CT PLL. See Figure 5, "PLL Pin Connections," on page 25 for recommended connections.           |

| H26 |     | PIIIp2_110 | I   |      | Loop-filter pin for the CT PLL. See Figure 5, "PLL Pin Connections," on page 25 for recommended connections.   |

| G28 |     | pllagn_110 | 0   |      | Analog Ground pin for the CT PLL. See Figure 5, "PLL Pin Connections," on page 25 for recommended connections. |

| AC5 |     | pllvss_300 | I   |      | VSS pin for the FC PLL. See Figure 5, "PLL Pin Connections," on page 25 for recommended connections.           |

| AG3 |     | pllvdd_300 | I   |      | VDD pin for the FC PLL. See Figure 5, "PLL Pin Connections," on page 25 for recommended connections.           |

Table 9 - Phase Lock Loop (PLL) Pins

| Pin | rst | Name     | I/O | Туре | Description                                        |

|-----|-----|----------|-----|------|----------------------------------------------------|

| E7  |     | proc_out | 0   |      | Process Monitor Pin Output. Must not be connected. |

**Table 10 - Process Monitor Pins**

| Pin | Location                  |

|-----|---------------------------|

| A2  | GND                       |

| А3  | VDD                       |

| A4  | GND                       |

| A5  | VDD                       |

| A6  | 1. rxa_clav<br>2. rxa_enb |

| A7  | GND                       |

| A8  | GND                       |

| A9  | GND                       |

| A10 | VDD                       |

| A11 | VDD                       |

| A12 | GND                       |

| A13 | N/C                       |

| A14 | VDD                       |

| A15 | GND                       |

| A16 | VDD                       |

| A17 | ct_d[30]                  |

| A18 | GND                       |

| A19 | VDD                       |

| A20 | VDD                       |

| A21 | GND                       |

| A22 | GND                       |

| A23 | GND                       |

| A24 | ct_d[5]                   |

| A25 | GND                       |

| A26 | GND                       |

| A27 | VDD                       |

| A28 | GND                       |

| A29 | VDD                       |

| B1  | GND                       |

| B2  | VDD                       |

| В3  | N/C                       |

| B4  | N/C                       |

| B5  | rxa_data[0]               |

| B6  | 1. rxa_enb<br>2. rxa_clav |

| Pin | Location    |

|-----|-------------|

|     |             |

| B9  | N/C         |

| B10 | recov_d     |

| B11 | recov_h     |

| B12 | N/C         |

| B13 | N/C         |

| B14 | N/C         |

| B15 | N/C         |

| B16 | N/C         |

| B17 | ct_d[31]    |

| B18 | ct_d[26]    |

| B19 | ct_d[27]    |

| B20 | ct_d[15]    |

| B21 | ct_d[16]    |

| B22 | ct_d[17]    |

| B23 | ct_d[14]    |

| B24 | ct_d[6]     |

| B25 | ct_vdd5_0   |

| B26 | ct_d[2]     |

| B27 | mc_tx       |

| B28 | ct_c8_b     |

| B29 | GND         |

| C1  | VDD         |

| C2  | phya_alm    |

| C3  | N/C         |

| C4  | N/C         |

| C5  | rxa_data[1] |

| C6  | rxa_clk     |

| C7  | N/C         |

| C8  | N/C         |

| C9  | N/C         |

| C10 | recov_c     |

| C11 | recov_g     |

| C12 | N/C         |

| C13 | N/C         |

| Pin | Location    |

|-----|-------------|

| C16 | ct_d[23]    |

| C17 | ct_vdd5_3   |

| C18 | ct_d[24]    |

| C19 | ct_d[12]    |

| C20 | ct_d[22]    |

| C21 | ct_d[3]     |

| C22 | ct_d[9]     |

| C23 | ct_d[1]     |

| C24 | ct_d[7]     |

| C25 | mc_rx       |

| C26 | ct_frame_b  |

| C27 | ct_frame_a  |

| C28 | ct_c8_a     |

| C29 | VDD         |

| D1  | GND         |

| D2  | phya_rx_led |

| D3  | rxa_data[4] |

| D4  | rxa_data[3] |

| D5  | rxa_data[2] |

| D6  | N/C         |

| D7  | N/C         |

| D8  | N/C         |

| D9  | N/C         |

| D10 | recov_b     |

| D11 | recov_f     |

| D12 | N/C         |

| D13 | N/C         |

| D14 | N/C         |

| D15 | N/C         |

| D16 | ct_d[19]    |

| D17 | ct_d[28]    |

| D18 | ct_vdd5_2   |

| D19 | ct_d[8]     |

| D20 | ct_vdd5_1   |

|     | T           |

|-----|-------------|

| Pin | Location    |

| D23 | ct_d[11]    |

| D24 | N/C         |

| D25 | ct_c16+     |

| D26 | GND         |

| D27 | ct_c2       |

| D28 | ct_c4       |

| D29 | GND         |

| E1  | GND         |

| E2  | rxa_data[7] |

| E3  | rxa_data[6] |

| E4  | rxa_data[5] |

| E5  | N/C         |

| E6  | GND         |

| E7  | proc_out    |

| E8  | N/C         |

| E9  | N/C         |

| E10 | recov_a     |

| E11 | recov_e     |

| E12 | N/C         |

| E13 | N/C         |

| E14 | N/C         |

| E15 | N/C         |

| E16 | ct_d[25]    |

| E17 | ct_d[20]    |

| E18 | ct_d[21]    |

| E19 | ct_d[13]    |

| E20 | ct_d[4]     |

| E21 | ct_d[18]    |

| E22 | ct_d[29]    |

| E23 | ct_c16-     |

| E24 | mc_clock    |

| E25 | N/C         |

| E26 | ct_fr_comp  |

| E27 | ct_sclk     |

Table 11 - Pin Names Listed by Location

| Pin | Location                  |

|-----|---------------------------|

| В7  | N/C                       |

| B8  | N/C                       |

| F1  | rxa_data[12]              |

| F2  | rxa_data[11]              |

| F3  | rxa_data[10]              |

| F4  | rxa_data[9]               |

| F5  | rxa_data[8]               |

| F25 | dmem_a[2]                 |

| F26 | ct_mc                     |

| F27 | dmem_a[1]                 |

| F28 | Pllvdd_110                |

| F29 | dmem_a[0]                 |

| G1  | GND                       |

| G2  | rxa_par                   |

| G3  | rxa_data[15]              |

| G4  | rxa_data[14]              |

| G5  | rxa_data[13]              |

| G25 | ct_netref1                |

| G26 | ct_netref2                |

| G27 | dmem_a[3]                 |

| G28 | pllagn_110                |

| G29 | GND                       |

| H1  | GND                       |

| H2  | 1. txa_enb<br>2. txa_clav |

| Н3  | txa_clk                   |

| H4  | rxa_soc                   |

| H5  | phya_tx_led               |

| H25 | dmem_a[5]                 |

| H26 | PIIIp2_110                |

| H27 | dmem_a[7]                 |

| H28 | dmem_a[8]                 |

| H29 | GND                       |

| Pin | Location                  |

|-----|---------------------------|

| C14 | N/C                       |

| C15 | N/C                       |

| J3  | txa_data[1]               |

| J4  | txa_data[0]               |

| J5  | 1. txa_clav<br>2. txa_enb |

| J25 | pllvss_110                |

| J26 | dmem_a[9]                 |

| J27 | dmem_a[10]                |

| J28 | dmem_a[4]                 |

| J29 | GND                       |

| K1  | VDD                       |

| K2  | txa_data[6]               |

| K3  | txa_data[5]               |

| K4  | txa_data[4]               |

| K5  | txa_data[3]               |

| K25 | dmem_a[11]                |

| K26 | dmem_a[17]                |

| K27 | dmem_d[8]                 |

| K28 | dmem_d[9]                 |

| K29 | VDD                       |

| L1  | VDD                       |

| L2  | txa_data[10]              |

| L3  | txa_data[9]               |

| L4  | txa_data[8]               |

| L5  | txa_data[7]               |

| L11 | GND                       |

| L13 | GND                       |

| L15 | GND                       |

| L17 | GND                       |

| L19 | GND                       |

| L25 | dmem_a[6]                 |

| L26 | dmem_d[10]                |

| Pin | Location                  |  |  |  |

|-----|---------------------------|--|--|--|

| D21 | ct_d[0]                   |  |  |  |

| D22 | ct_d[10]                  |  |  |  |

| L29 | VDD                       |  |  |  |

| M1  | GND                       |  |  |  |

| M2  | txa_data[13]              |  |  |  |

| МЗ  | txa_data[12]              |  |  |  |

| M4  | txa_data[11]              |  |  |  |

| M5  | N/C                       |  |  |  |

| M25 | dmem_d[0]                 |  |  |  |

| M26 | dmem_d[2]                 |  |  |  |

| M27 | dmem_d[12]                |  |  |  |

| M28 | N/C                       |  |  |  |

| M29 | GND                       |  |  |  |

| N1  | rxb_clk                   |  |  |  |

| N2  | txa_soc                   |  |  |  |

| N3  | txa_par                   |  |  |  |

| N4  | txa_data[15]              |  |  |  |

| N5  | txa_data[14]              |  |  |  |

| N11 | GND                       |  |  |  |

| N13 | GND                       |  |  |  |

| N15 | GND                       |  |  |  |

| N17 | GND                       |  |  |  |

| N19 | GND                       |  |  |  |

| N25 | dmem_d[3]                 |  |  |  |

| N26 | dmem_d[13]                |  |  |  |

| N27 | dmem_d[4]                 |  |  |  |

| N28 | dmem_d[14]                |  |  |  |

| N29 | dmem_d[5]                 |  |  |  |

| P1  | VDD                       |  |  |  |

| P2  | rxb_data[1]               |  |  |  |

| P3  | rxb_data[0]               |  |  |  |

| P4  | 1. rxb_clav<br>2. rxb_enb |  |  |  |

| Pin | Location                          |  |  |  |

|-----|-----------------------------------|--|--|--|

| E28 | ct_sclkx2                         |  |  |  |

| E29 | GND                               |  |  |  |

| P26 | dmem_d[6]                         |  |  |  |

| P27 | dmem_par[1]                       |  |  |  |

| P28 | dmem_d[7]                         |  |  |  |

| P29 | VDD                               |  |  |  |

| R1  | GND                               |  |  |  |

| R2  | rxb_data[5]                       |  |  |  |

| R3  | rxb_data[4]                       |  |  |  |

| R4  | rxb_data[3]                       |  |  |  |

| R5  | rxb_data[2]                       |  |  |  |

| R11 | GND                               |  |  |  |

| R13 | GND                               |  |  |  |

| R17 | GND                               |  |  |  |

| R19 | GND                               |  |  |  |

| R25 | mem_clk_negative_i                |  |  |  |

| R26 | mem_clk_positive_i                |  |  |  |

| R27 | dmem_par[0]                       |  |  |  |

| R28 | dmem_a[12]                        |  |  |  |

| R29 | GND                               |  |  |  |

| T1  | VDD                               |  |  |  |

| T2  | 1. rxb_data[8]                    |  |  |  |

|     | 2. rxa_addr[0]                    |  |  |  |

| Т3  | rxb_data[7]                       |  |  |  |

| T4  | rxb_data[6]                       |  |  |  |

| T5  | phyb_tx_led                       |  |  |  |

| T25 | N/C                               |  |  |  |

| T26 | dmem_a[13]                        |  |  |  |

| T27 | dmem_a[14]                        |  |  |  |

| T28 | dmem_a[18]                        |  |  |  |

| T29 | GND                               |  |  |  |

| U1  | 1. rxb_data[13]<br>2. txa_addr[1] |  |  |  |

| U2  | 1. rxb_data[12]<br>2. txa_addr[0] |  |  |  |

Table 11 - Pin Names Listed by Location (continued)

| Pin | Location                         |  |  |  |  |

|-----|----------------------------------|--|--|--|--|

| J1  | GND                              |  |  |  |  |

| 01  | CND                              |  |  |  |  |

| J2  | txa_data[2]                      |  |  |  |  |

|     |                                  |  |  |  |  |

| U5  | 1. rxb_data[9]<br>2. rxa_addr[1] |  |  |  |  |

| U11 | GND                              |  |  |  |  |

| U13 | GND                              |  |  |  |  |

| U15 | GND                              |  |  |  |  |

| U17 | GND                              |  |  |  |  |

| U19 | GND                              |  |  |  |  |

| U25 | dmem_rw                          |  |  |  |  |

| U26 | dmem_bws[0]                      |  |  |  |  |

| U27 | dmem_bws[1]                      |  |  |  |  |

| U28 | dmem_cs[0]                       |  |  |  |  |

| U29 | dmem_a[15]                       |  |  |  |  |

| V1  | GND                              |  |  |  |  |

| V2  | rxb_soc                          |  |  |  |  |

| V3  | rxb_par                          |  |  |  |  |

| V4  | 1. rxb_data[15] 2. txa_addr[3]   |  |  |  |  |

| V5  | 1. rxb_data[14]                  |  |  |  |  |

| ••  | 2. txa_addr[2]                   |  |  |  |  |

| V25 | dmem_cs[3]                       |  |  |  |  |

| V26 | dmem_cs[2]                       |  |  |  |  |

| V27 | dmem_cs[1]                       |  |  |  |  |

| V28 | dmem_a[16]                       |  |  |  |  |

| V29 | VDD                              |  |  |  |  |

| W1  | VDD                              |  |  |  |  |

| W2  | 1. txb_clav<br>2. txb_enb        |  |  |  |  |

| W3  | 1. txb_enb                       |  |  |  |  |

| W4  | 2. txb_clav                      |  |  |  |  |

| W5  | txb_clk                          |  |  |  |  |

| W11 | phyb_rx_led GND                  |  |  |  |  |

|     | UND                              |  |  |  |  |

| Pin  | Location                       |

|------|--------------------------------|

| L27  | dmem_d[1]                      |

| L28  | dmem_d[11]                     |

| W26  | 1. cmem_a[18]<br>2. cmem_cs[1] |

| W27  | cmem_a[1]                      |

| W28  | cmem_a[0]                      |

| W29  | VDD                            |

| Y1   | VDD                            |

| Y2   | txb_data[3]                    |

| Y3   | txb_data[2]                    |

| Y4   | txb_data[1]                    |

| Y5   | txb_data[0]                    |

| Y25  | cmem_cs[0]                     |

| Y26  | cmem_bws[1]                    |

| Y27  | cmem_bws[0]                    |

| Y28  | cmem_rw                        |

| Y29  | VDD                            |

| AA1  | GND                            |

| AA2  | txb_data[7]                    |

| AA3  | txb_data[6]                    |

| AA4  | txb_data[5]                    |

| AA5  | txb_data[4]                    |

| AA25 | cmem_d[0]                      |

| AA26 | cmem_a[4]                      |

| AA27 | cmem_a[3]                      |

| AA28 | cmem_a[2]                      |

| AA29 | GND                            |

| AB1  | GND                            |

| AB2  | txb_data[10]                   |

| AB3  | txb_data[9]                    |

| AB4  | txb_data[8]                    |

| Pin  | Location                          |  |  |  |  |  |

|------|-----------------------------------|--|--|--|--|--|

| P5   | 1. rxb_enb                        |  |  |  |  |  |

|      | 2. rxb_clav                       |  |  |  |  |  |

| P25  | dmem_d[15]                        |  |  |  |  |  |

| AB28 | cmem_d[1]                         |  |  |  |  |  |

| AB29 | GND                               |  |  |  |  |  |

| AC1  | GND                               |  |  |  |  |  |

| AC2  | 1. txb_data[14]<br>2. rxa_addr[4] |  |  |  |  |  |

| AC3  | txb_data[13]                      |  |  |  |  |  |

| AC4  | txb_data[12]                      |  |  |  |  |  |

| AC5  | pllvss_300                        |  |  |  |  |  |

| AC25 | cmem_d[4]                         |  |  |  |  |  |

| AC26 | cmem_d[10]                        |  |  |  |  |  |

| AC27 | cmem_d[3]                         |  |  |  |  |  |

| AC28 | cmem_d[9]                         |  |  |  |  |  |

| AC29 | VDD                               |  |  |  |  |  |

| AD1  | rxc_data[0]                       |  |  |  |  |  |

| AD2  | txb_soc                           |  |  |  |  |  |

| AD3  | txb_par                           |  |  |  |  |  |

| AD4  | 1. txb_data[15]<br>2. txa_addr[4] |  |  |  |  |  |

| AD5  | GND                               |  |  |  |  |  |

| AD25 | GND                               |  |  |  |  |  |

| AD26 | cmem_d[5]                         |  |  |  |  |  |

| AD27 | cmem_d[11]                        |  |  |  |  |  |

| AD28 | mem_clk_o                         |  |  |  |  |  |

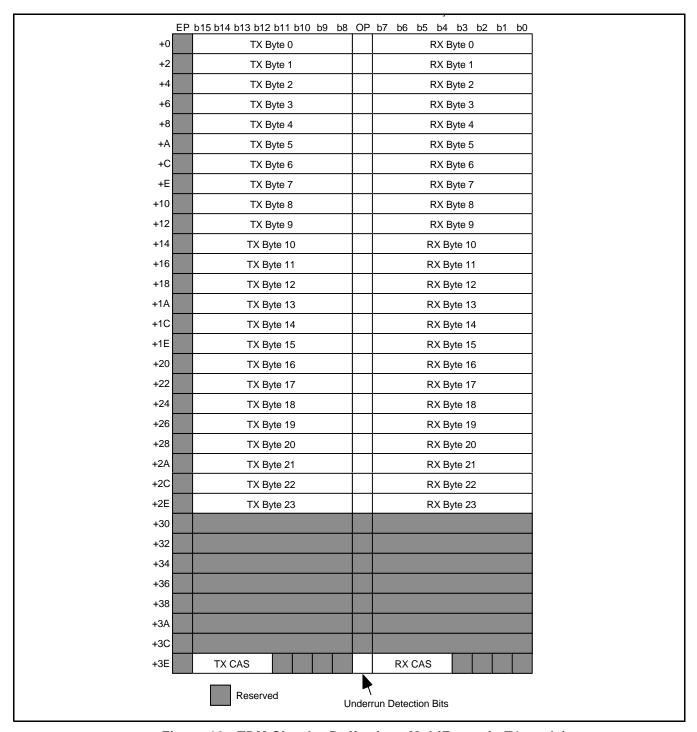

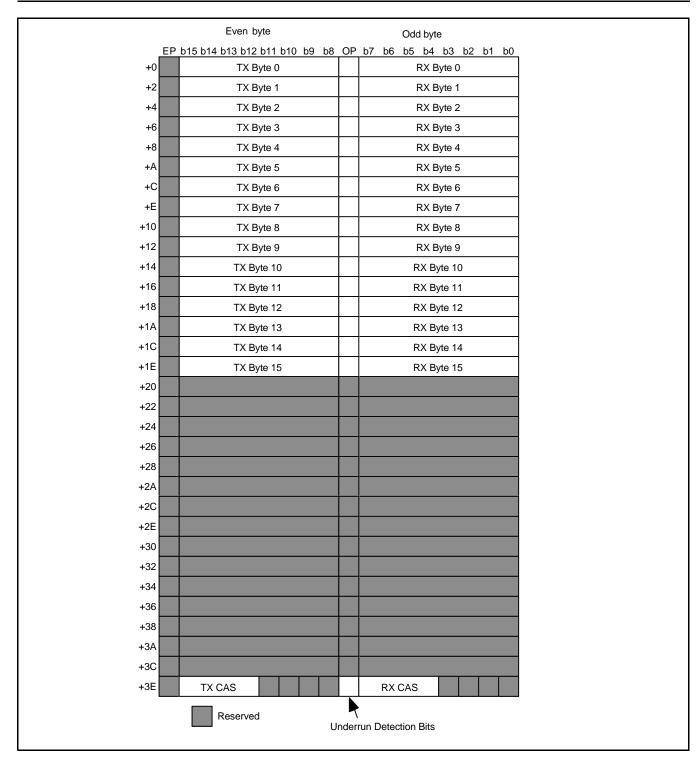

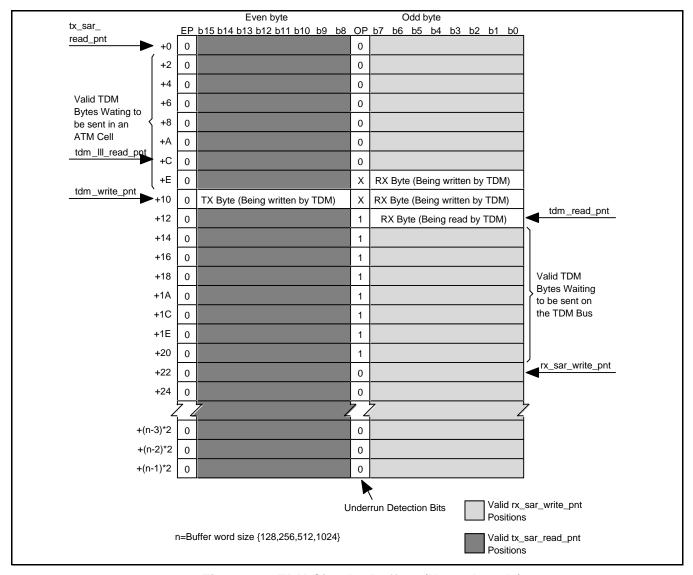

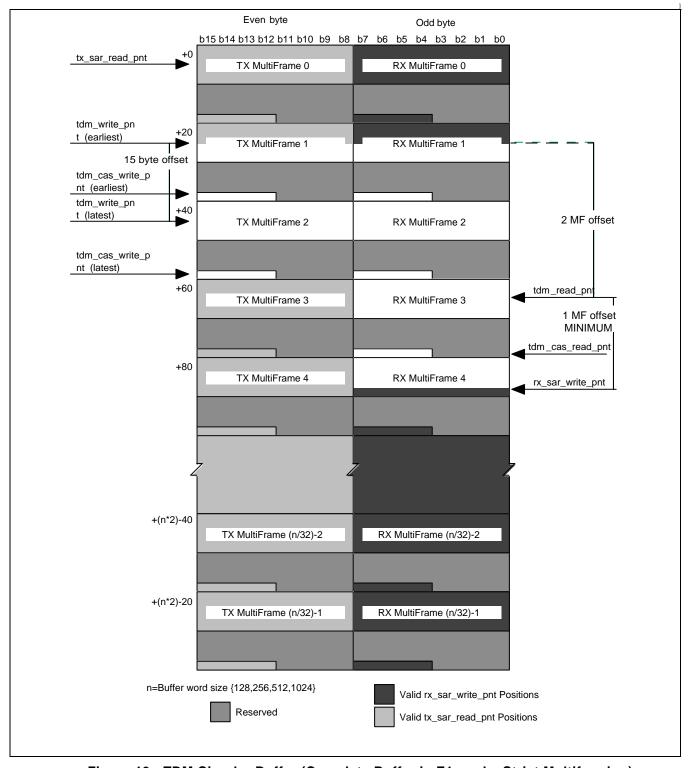

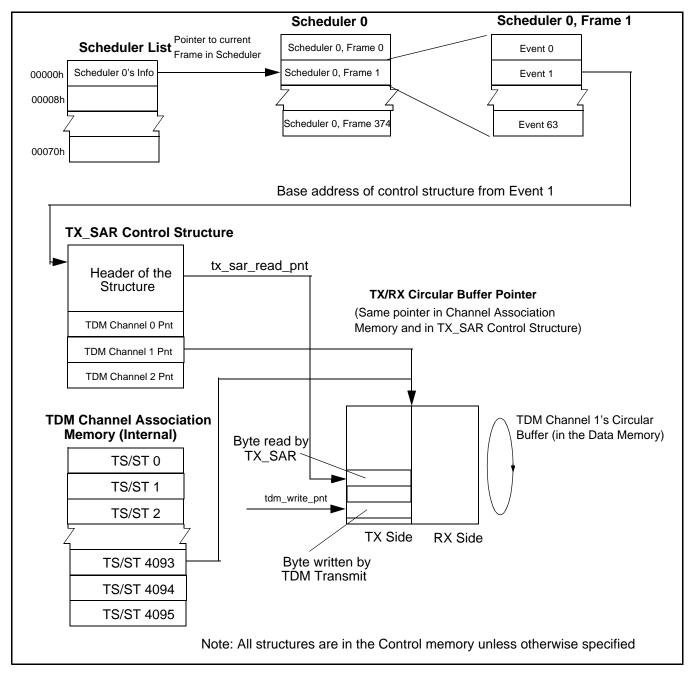

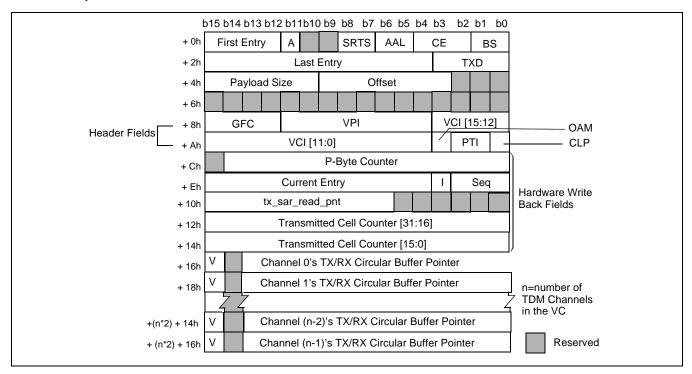

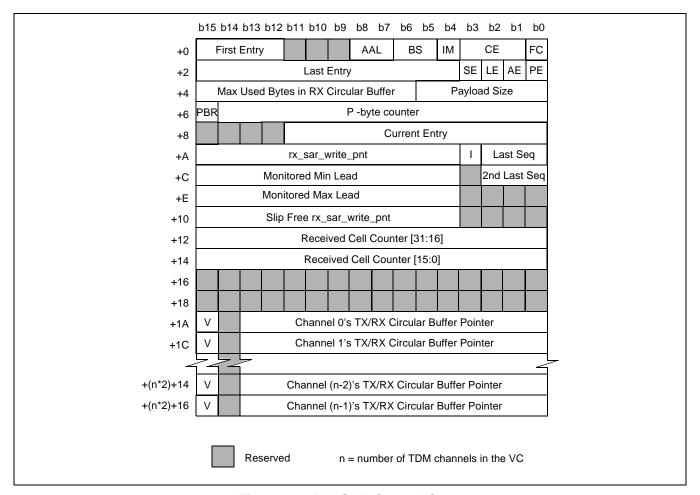

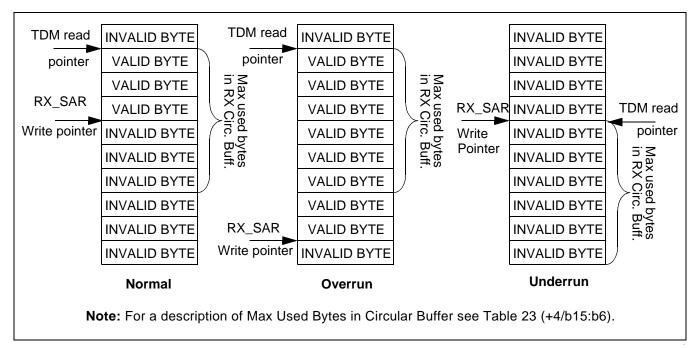

| AD29 | mem_clk_i                         |  |  |  |  |  |