# FRRATA

# TO THE TSB12C01A 1394 LINK LAYER CONTROLLER DATA MANUAL

(TEXAS INSTRUMENTS LITERATURE NO. SLLS219A, FEBRUARY 1997)

This document contains corrections and additions to information in the TSB12C01A data manual (TI Literature Number SLLS219A, February 1997), also included in IEEE 1394 Circuits Data Book, 1997 (TI Literature Number SLLD004).

## general

- a. Electrical isolation as described in Appendix J of IEEE 1394–1995 is not supported by the TSB12C01APZ. TI has an improved isolation technique, and that is the recommended isolation solution.

- Please see Galvanic Isolation of the IEEE 1394-1995 Serial Bus (TI Literature Number SLLA011).

- b. The receiving TSB12C01A will not receive:

- a lock response with no data and an error rcode

- a read response with no data and an error rcode

- c. In systems using the TSB11C01, the phy-link I/F may hang when a request to send ISO data (an LREQ to the phy layer) occurs during a narrow window after the end of the transmission of a cycle start packet.

A similar problem may occur if a status is sent from the phy to the link in a very narrow window just as or just after a LREQ is sent from the link to the phy. This may cause the phy/link interface to hang in the HOLD state.

The suggested work around for both is:

- Write the first iso data quadlet to ITF\_First, and write quadlets 2 to (n-1) to ITF\_Continue. This data is now queued up.

- Wait for CyDne, then immediately write the final quadlet to ITF\_Continue\_&\_Update. This final quadlet must be written before the end of the current 125 microsecond ISO period to ensure the packet will go out on the next ISO period. Be aware of how much time may be consumed by the PC servicing interrupts. If an interrupt requires too much time, it should be masked out during the writes to the ITF.

- The data will go out on the next iso cycle.

- d. The received acknowledge speed decode logic is incorrect when receiving an acknowledge for an asynchronous packet sent at S200 and S400 data rates. The TSB12C01A transmits and receives data packets at S200 or S400 properly, but the acknowledge packet for an asynchronous transmit is not correctly decoded. This can result in the transmitting node not being able to receive or correctly receive an acknowledge (see the first item under addition information, below).

- e. The self\_id period is currently terminated by an arbitration reset gap. It should be a subaction gap; this has not caused any known problems.

- The receiver will always return an ack code of ack\_complete to an asynchronous write request that was not busied off. It will send the busy ack code for a busy state on the receiving node, and will send all other types of acknowledges.

- g. The TSB12C01A cannot receive 0-length iso packets.

- h. The receiver does not check available space in the GRF properly when receiving self id packets. After the GRF is full, the incoming self-ID packets are lost.

- i. Fast back-to-back writes to the transmit FIFOs of the TSB12C01A may cause overwriting of the previously written quadlet of data before it has been placed into the transmit FIFO if there is activity on the PHY/Link interface. This may occur even if the host has waited until CA– was asserted before attempting another write.

- The workaround is to wait a minimum of 3 BCLK cycles after CA-is asserted between each write to the ITF or ATF.

- j. There is a small possibility that a FIFO contention might occur as a result of activity on both the Host/Link interface and Phy/Link interface. A contention could occur if the final quadlet written to a transmit FIFO is confirmed exactly when a quadlet is being written from 1394 into the GRF. This contention could result in a data quadlet arriving in the Phy/Link interface not being written into the GRF.

- The workaround is to write the final quadlet into the ATF or ITF when the TSB12C01A is not in receive mode. The suggested mechanism to do this is to wait until the GRFEMP terminal is set (or bit 15 of the GRF Status register is set) before writing the final quadlet into the ATF or ITF.

#### additional information

- k. A false header error will be reported on receipt of a phy configuration packet if the TSB12C01A misinterprets the phy config packet as a data packet addressed its node. The TSB12C01A on a particular node will issue a header error if the first 16 bits of a phy configuration packet (PHY config packet id + phy\_ID + force\_root bit flag + set gap\_count flag + gap\_count) happen to match that node's destination id (bus number + node number).

- The suggested work around is to assign bus numbers that all have the msb = 1. Since the all-ones case is reserved for addressing the local bus, this leaves only 511 available unique bus IDs. This is a result of the wording of the IEEE 1394 Standard.

- I. The RxDta interrupt bit is currently set whenever a data quadlet has been received by the GRF. This generates a large number of interrupts. In a future revision of this device, this interrupt will be changed such that it only occurs when a complete packet has been received by the GRF.

# **TSB12C01A Document Changes**

- aa. Make the following change to Figure 2–2, *TSB12C01 Terminal Functions* on page 2–5 of the first revision of the TSB12C01A data manual (TI literature number SLLS219) *ONLY:*

- Change CYDNE to CYDNE by removing the overbar from the CYDNE signal name. The signal CYDNE is an active-HIGH signal and should not be shown with an overbar.

Revision A of the document, SLLS219**A**, is correct, both standalone and as part of the *IEEE 1394 Circuits Data Book*, 1997, TI literature number SLLD004.

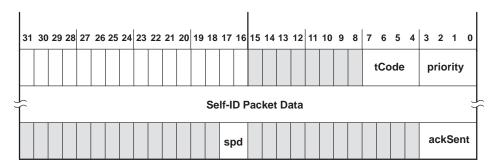

bb. Replace the *Receive Self-ID* paragraph, figure, and table where indicated in the specified documents, with the following paragraph, figure, and table.

### 4-X Receive Self-ID

The format of the receive Self-ID packet is shown in Figure 4–Y. The first quadlet is the packet header with the special tCode of Eh. The quadlets that follow are a concatenation of all the received Self-ID packets, followed by the final packet status quadlet.

Figure 4-Y. Receive Self-ID Format

Table 4-Z. Receive Self-ID Functions

| FIELD NAME          | DESCRIPTION                                                                                                                                    |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| tCode               | This field carries the special transaction code of 1110b.                                                                                      |

| priority            | This field carries the priority level for this packet.                                                                                         |

| Self-ID packet data | This field contains a concatenation of all the Self-ID packets received.                                                                       |

| spd                 | This field indicates the speed at which this packet was sent. All Self-ID packets are sent at the base rate of 100 Mbps. spd = 00 for 100 Mbps |

| ackSent             | This field holds the acknowledge sent by the receiver for this packet.                                                                         |

Where Paragraph 4–X, Figure 4–Y, and Table 4–Z are:

TSB12C01A Data Manual, TI Literature Number SLLS219, September 1995, page 4–8: Paragraph 4–7 Receive Self-ID, Figure 4–10, and Table 4–10

TSB12C01A Data Manual, Revision A, TI Literature Number SLLS219A, February 1997, page 4–9: Paragraph 4–8 Receive Self-ID, Figure 4–11, and Table 4–11

IEEE 1394 Circuits Data Book, 1997, TI Literature Number SLLD004, June 1997, TSB12C01A Data Manual, Revision A, February 1997, data book page 2–41: Paragraph 4–8 Receive Self-ID, Figure 4–11, and Table 4–11

(This page has been left blank intentionally.)

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current and complete.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1998, Texas Instruments Incorporated