# TSB42AA4/TSB42AB4 (ceLynx)

IEEE 1394.a Consumer Electronics Link Layer Controller

# Data Manual

June 2000

Mixed Signal Products

SLLS341A

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated

## **Contents**

| Se | ction                          |            | Title                                            | Page |  |

|----|--------------------------------|------------|--------------------------------------------------|------|--|

| 1  | Introdu                        | iction     |                                                  | 1–1  |  |

|    | 1.1 Device Package Information |            |                                                  |      |  |

|    | 1.2                            |            | ces                                              | 1–1  |  |

| 2  | ceLynx                         |            | ew                                               | 2–1  |  |

|    | 2.1                            |            | Description                                      |      |  |

|    | 2.2                            | -          | atures                                           |      |  |

|    | 2.3                            | -          | ion Information                                  |      |  |

|    | 2.4                            |            | Functional Block Diagram                         |      |  |

|    | 2.5                            | Pin Assi   | gnments                                          | 2-7  |  |

|    |                                | 2.5.1      | Pin Descriptions                                 | 2-7  |  |

| 3  | Externa                        | al Interfa | ıces                                             | 3–1  |  |

|    | 3.1                            |            | ntroller Interface (MCIF)                        | 3–1  |  |

|    |                                | 3.1.1      | Read Operation                                   |      |  |

|    |                                | 3.1.2      | Write Operation                                  | 3–4  |  |

|    |                                | 3.1.3      | Critical Timing                                  | 3–6  |  |

|    |                                | 3.1.4      | Host Interface - Multistrobe Mode                | 3–7  |  |

|    | 3.2                            | High-Sp    | eed Data Interface (HSDI)                        | 3–10 |  |

|    |                                | 3.2.1      | Data Bus Modes                                   |      |  |

|    |                                | 3.2.2      | Stream Modes                                     | 3–11 |  |

|    |                                | 3.2.3      | Data Block Synchronization Modes                 | 3–12 |  |

|    |                                | 3.2.4      | HSDI Functional Timing – Write                   |      |  |

|    |                                | 3.2.5      | HSDI Functional Timing for Multistream Modes     |      |  |

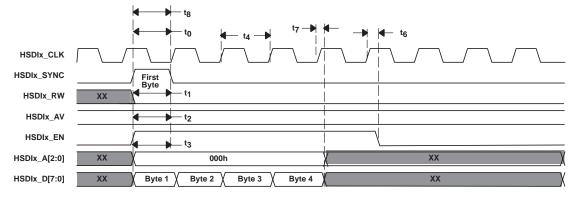

|    |                                | 3.2.6      | HSDI Critical Timing                             |      |  |

|    | 3.3                            | PHY-Lin    | k Interface                                      |      |  |

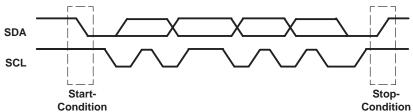

|    | 3.4                            | Two-Wir    | e Serial Interface                               | 3–18 |  |

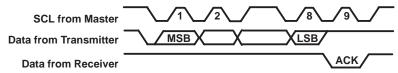

|    |                                | 3.4.1      | Two-Wire Serial Interface Bus Protocol           | 3–18 |  |

|    |                                | 3.4.2      | ceLynx/Two-Wire Serial Interface-EEPROM-Protocol |      |  |

|    |                                | 3.4.3      | EEPROM Data Format                               |      |  |

|    | 3.5                            | Block He   | eader                                            | 3-20 |  |

|    |                                | 3.5.1      | Header Addressing                                | 3-20 |  |

|    |                                | 3.5.2      | Header - Last Block Bit                          |      |  |

|    | 3.6                            | CFR Ad     | dress Location and Bit Assignment                |      |  |

|    | 3.7                            |            | s: Serial STAT0 and Serial STAT1 Registers       |      |  |

|    |                                | 3.7.1      | Operation                                        |      |  |

| 4  | Interna                        |            | ons                                              | 4–1  |  |

|    | 4.1                            |            | ffers                                            |      |  |

|    |                                | 4.1.1      | Byte Stacking and Endianness                     |      |  |

|    |                                | 4.1.2      | Buffer Overflow/Underflow Status                 |      |  |

|    |                                |            |                                                  |      |  |

|   |        | 4.1.3 Data Buffer Setup                             | 4–1  |  |  |  |  |

|---|--------|-----------------------------------------------------|------|--|--|--|--|

|   | 4.2    | Time Stamping and Aging                             | 4–2  |  |  |  |  |

|   |        | 4.2.1 Time Stamp and Aging for MPEG2 Data           | 4–3  |  |  |  |  |

|   |        | 4.2.2 Time Shifting Application                     | 4–4  |  |  |  |  |

|   |        | 4.2.3 Time Stamp on Transmit to 1394 – DV Data      | 4–5  |  |  |  |  |

|   |        | 4.2.4 Time Stamp Determination on Receive – DV Data | 4–6  |  |  |  |  |

|   | 4.3    | ceLynx Interrupt Structure                          | 4–7  |  |  |  |  |

|   | 4.4    | PID Filtering                                       | 4–8  |  |  |  |  |

|   |        | 4.4.1 PID Filtering Configuration Registers         | 4–9  |  |  |  |  |

|   |        | 4.4.2 PID Filter Example                            | 4–9  |  |  |  |  |

|   | 4.5    | Isochronous Packet Insertion, Transmit Only         | 4–11 |  |  |  |  |

|   |        | 4.5.1 Functional Overview                           | 4–11 |  |  |  |  |

|   |        | 4.5.2 Packet Insertion Configuration Registers      | 4–12 |  |  |  |  |

|   |        | 4.5.3 Packet Insertion Example                      | 4–12 |  |  |  |  |

| 5 | ceLynx | x Data Formats                                      | 5–1  |  |  |  |  |

|   | 5.1    | Asynchronous Transmit                               | 5–1  |  |  |  |  |

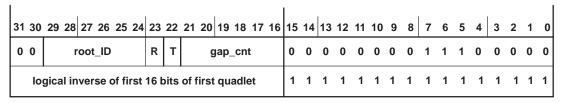

|   |        | 5.1.1 Quadlet Transmit                              | 5–2  |  |  |  |  |

|   |        | 5.1.2 Block Transmit                                | 5–3  |  |  |  |  |

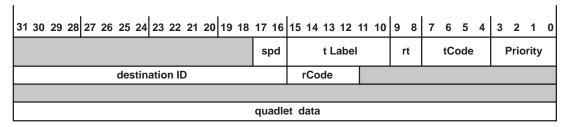

|   | 5.2    | Asynchronous Receive                                | 5–4  |  |  |  |  |

|   |        | 5.2.1 Quadlet Receive                               | 5–6  |  |  |  |  |

|   |        | 5.2.2 Block Receive                                 | 5–8  |  |  |  |  |

|   | 5.3    | Asynchronous Acknowledge Buffer                     | 5–9  |  |  |  |  |

|   | 5.4    | · ·                                                 | 5–10 |  |  |  |  |

|   |        |                                                     | 5–11 |  |  |  |  |

|   |        |                                                     | 5–11 |  |  |  |  |

|   | 5.5    | · · · · · · · · · · · · · · · · · · ·               | 5–12 |  |  |  |  |

|   |        | 5.5.1 MPEG2 DVB Data                                | 5–12 |  |  |  |  |

|   |        | 5.5.2 DirecTV™ Data                                 | 5–15 |  |  |  |  |

|   |        |                                                     | 5–19 |  |  |  |  |

|   |        |                                                     | 5–23 |  |  |  |  |

|   |        | 5.5.5 DV Transmit                                   | 5–24 |  |  |  |  |

|   | 5.6    | Unformatted Isochronous Data                        | 5–24 |  |  |  |  |

|   |        | 5.6.1 Unformatted Isochronous Transmit              | 5–24 |  |  |  |  |

|   |        | 5.6.2 Unformatted Isochronous Receive               | 5–25 |  |  |  |  |

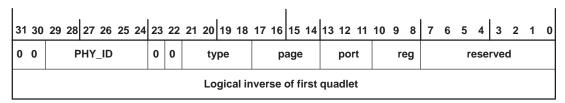

|   | 5.7    | PHY Configuration Packet                            | 5–26 |  |  |  |  |

|   | 5.8    | _                                                   | 5–27 |  |  |  |  |

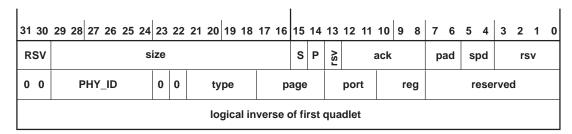

|   |        | 5.8.1 Remote Access Packet                          | 5–27 |  |  |  |  |

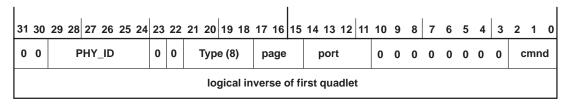

|   |        |                                                     | 5–28 |  |  |  |  |

|   |        | • •                                                 | 5–28 |  |  |  |  |

|   |        |                                                     | 5–29 |  |  |  |  |

|   |        |                                                     | 5–30 |  |  |  |  |

|   | 5.9    |                                                     | 5–30 |  |  |  |  |

| 6 |        | er Map Detail                                       | 6–1  |  |  |  |  |

|   | 6.1    | Register Description Notes                          |      |  |  |  |  |

|   | 6.2    | Endianess                                           | 6–1  |  |  |  |  |

|   |        |                                                     |      |  |  |  |  |

|   |         | 6.2.1      | System Information CFR Map                                                           | 6–2  |

|---|---------|------------|--------------------------------------------------------------------------------------|------|

|   |         | 6.2.2      | SYS CFR Bit Descriptions                                                             | 6–3  |

|   | 6.3     | Link Laye  | er Controller CFR Map                                                                | 6–14 |

|   |         | 6.3.1      | Link CFR Bit Descriptions                                                            | 6–14 |

|   | 6.4     | High-Spe   | ed Data Interface A CFR Map                                                          | 6–21 |

|   |         | 6.4.1      | HSDI A Bit Descriptions                                                              | 6-22 |

|   | 6.5     | High-Spe   | ed Data Interface B CFR Map                                                          | 6–29 |

|   |         | 6.5.1      | HSDI B Bit Descriptions                                                              | 6-30 |

|   | 6.6     | Data Buff  | er CFR Map                                                                           | 6–37 |

|   |         | 6.6.1      | Data Buffer Bit Descriptions                                                         | 6–38 |

|   | 6.7     | Transmit   | Data Path CFR Map                                                                    | 6-56 |

|   |         | 6.7.1      | TXDP Header Register Descriptions                                                    | 6–65 |

|   | 6.8     | Receive [  | Data Path CFR Map                                                                    | 6–70 |

|   |         | 6.8.1      | RXDP Bit Descriptions                                                                | 6–71 |

| 7 | Electri | cal Charac | cteristics                                                                           | 7–1  |

|   | 7.1     | Absolute   | Maximum Ratings Over Free-Air Temperature Range                                      | 7–1  |

|   | 7.2     | Recomme    | ended Operating Conditions                                                           | 7–2  |

|   | 7.3     |            | Characteristics Over Recommended Ranges of Supply Voltage ating Free-Air Temperature | 7–2  |

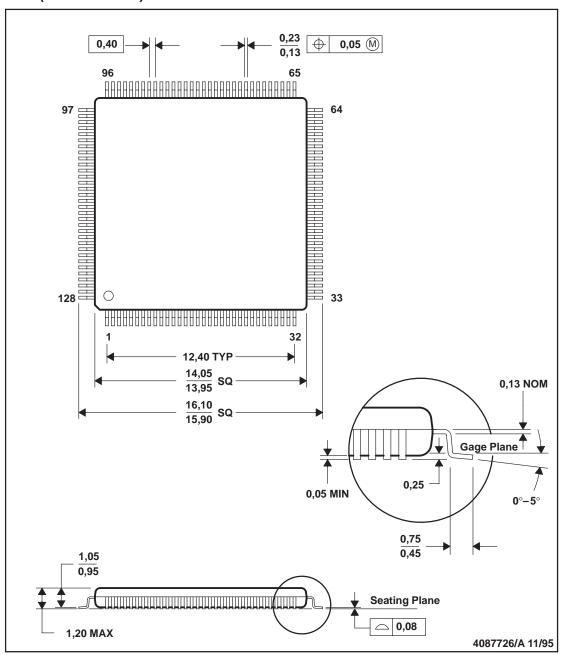

| 8 | Mecha   |            | mation                                                                               | 8–1  |

## **List of Illustrations**

| Figure Title                                                           | Page |

|------------------------------------------------------------------------|------|

| 2-1 Home Entertainment System Interconnect With Content Protection     | 2-3  |

| 2–2 Simultaneous Playback and Record of Video (Full Duplex)            | 2–4  |

| 2–3 Picture in Picture Capability Inside Digital TV                    | 2–4  |

| 2–4 Graphics Overlay From Digital STB to DTV                           | 2–5  |

| 2–5 Time-Shift Application                                             | 2–5  |

| 2–6 ceLynx Functional Block Diagram                                    | 2–6  |

| 3–1 Interface Between ceLynx and 68000-Style Processor                 | 3–2  |

| 3–2 16-Bit Read                                                        | 3–3  |

| 3–3 32-Bit Read                                                        | 3–3  |

| 3–4 16-Bit Write                                                       | 3–4  |

| 3–5 32-Bit Write                                                       | 3–5  |

| 3–6 Microcontroller Interface Critical Write Timing                    | 3–6  |

| 3–7 Microcontroller Interface Critical Read Timing                     | 3–7  |

| 3–8 Microcontroller Host Interface Connection Diagram                  |      |

| 3–9 Host Port Multistrobe Timing - Write Operation                     | 3–8  |

| 3–10 Host Port Multistrobe Timing - Read Operation                     | 3–9  |

| 3–11 Multistrobe Mode - Write Critical Timing                          | 3–9  |

| 3–12 Multistrobe Mode - Read Critical Timing                           | 3–9  |

| 3–13 High-Speed Data Interface                                         | 3–11 |

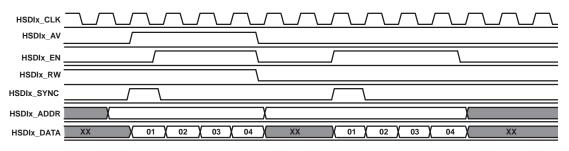

| 3–14 HSDI Single Stream Mode Example                                   |      |

| 3–15 HSDI Read, Byte Wide Data Bus, Sync Mode A                        | 3–14 |

| 3–16 HSDI Read, Byte Wide Data Bus, Sync Mode B                        | 3–14 |

| 3–17 HSDI Read, Byte Wide Data Bus, Sync Mode C                        | 3–14 |

| 3–18 HSDI Read, Serial Data Bus, Sync Mode B                           | 3–15 |

| 3–19 HSDI Write, Byte Wide Data Bus, Sync Mode A                       | 3–15 |

| 3–20 HSDI Write, Byte Wide Data Bus, Sync Mode B                       | 3–15 |

| 3–21 HSDI Write, Byte Wide Data Bus, Sync Mode C                       | 3–16 |

| 3–22 HSDI Write, Serial Data Bus, Sync Mode B                          | 3–16 |

| 3–23 Functional Timing for Multistream Mode (Read and Write)           |      |

| 3–24 HSDI Interface Critical Timing                                    | 3–17 |

| 3–25 Two-Wire Serial Interface Bus Protocol                            | 3–19 |

| 3–26 EEPROM Protocol Device Address Format and Typical Write Operation | 3–19 |

| 3–27 EEPROM Protocol Typical Read Operation                            | 3–19 |

| 3–28 Block Format for EEPROM                                   | 3–20 |

|----------------------------------------------------------------|------|

| 3–29 EEPROM Header Format                                      | 3–20 |

| 4–1 Data Buffer Default Settings                               | 4–2  |

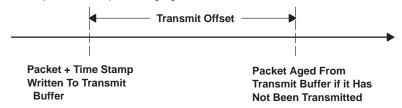

| 4–2 MPEG2 Transmit and Aging                                   | 4–3  |

| 4–3 MPEG2 Receive, Release, and Aging                          | 4–3  |

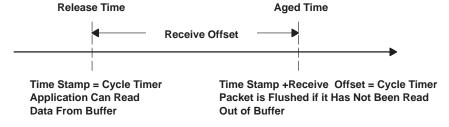

| 4–4 Determination of Transmit Time Stamp                       | 4–4  |

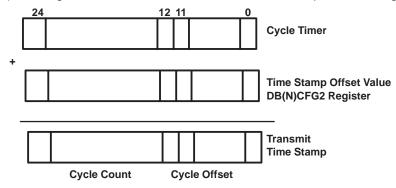

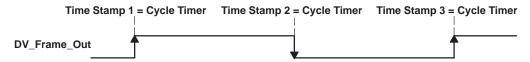

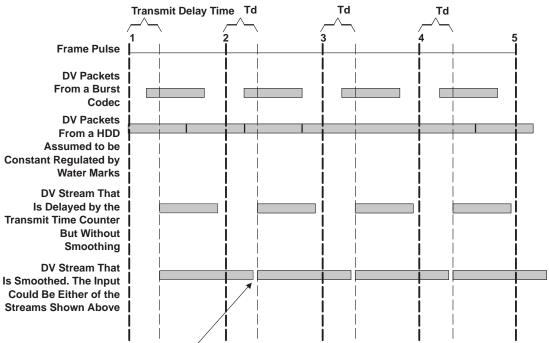

| 4–5 DV Transmit Timing                                         | 4–5  |

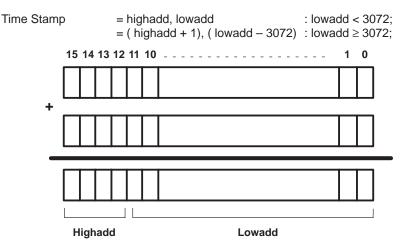

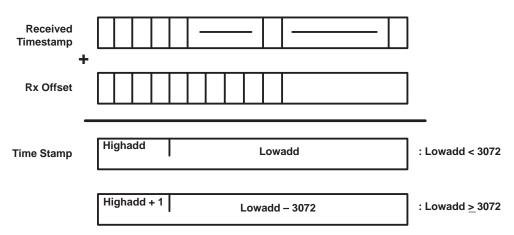

| 4-6 Determination of Highadd and Lowadd                        | 4–6  |

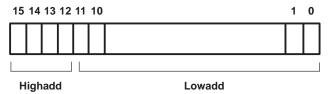

| 4–7 Time Stamp Value for Lowadd <3072                          | 4–6  |

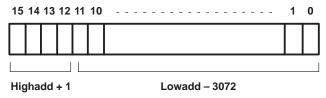

| 4–8 Time Stamp Value for Lowadd ≥3072                          | 4–6  |

| 4–9 DV Transmit Timing                                         | 4–6  |

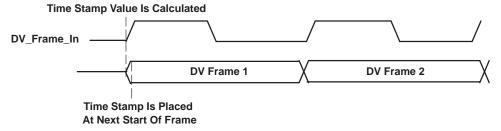

| 4–10 Time Stamp Calculation DV Data Received                   | 4–7  |

| 4–11 Interrupt Hierarchy                                       | 4–8  |

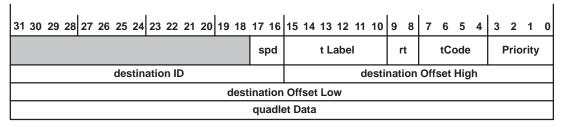

| 5–1 Quadlet Transmit Format (Write Request)                    | 5–2  |

| 5–2 Quadlet Transmit Format (Read Response)                    | 5–2  |

| 5–3 Block Transmit Format (Write Request)                      | 5–3  |

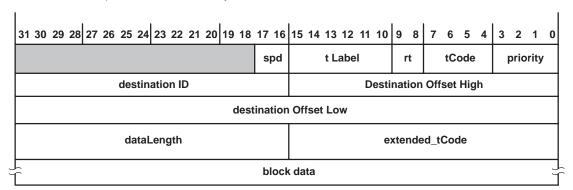

| 5–4 Block Transmit Format (Read Request)                       | 5–3  |

| 5–5 Packet Control Token Format for Asynchronous, Isochronous, |      |

| Self-ID, and PHY Packets                                       | 5–4  |

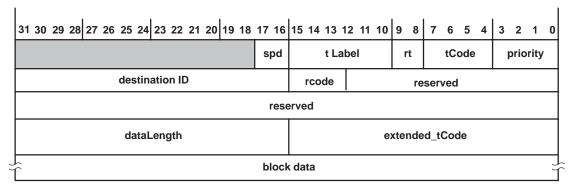

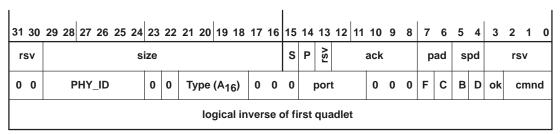

| 5–6 Quadlet – Receive Format                                   | 5–7  |

| 5–7 Block – Receive Format                                     |      |

| 5-8 Acknowledge Buffer Format                                  | 5–10 |

| 5–9 Asynchronous Stream Transmit Format                        | 5–11 |

| 5–10 Asynchronous Stream Receive Format                        | 5–11 |

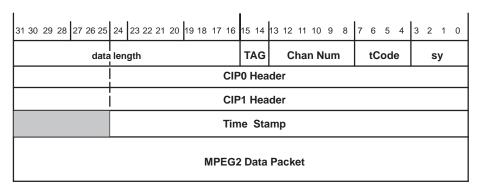

| 5–11 MPEG2 Transmit Format                                     | 5–12 |

| 5–12 MPEG2 Receive Format                                      | 5–13 |

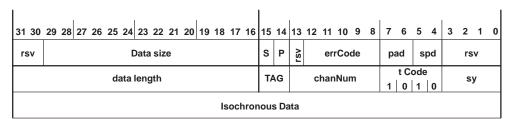

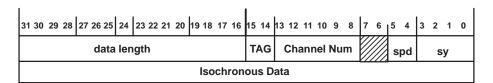

| 5–13 Isochronous CIP Headers – MPEG2 Data                      | 5–13 |

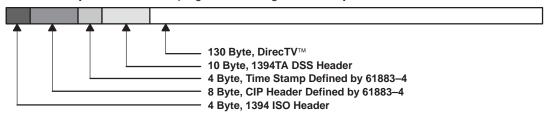

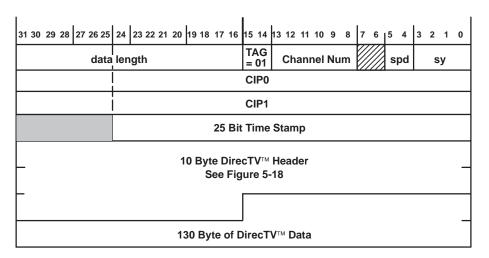

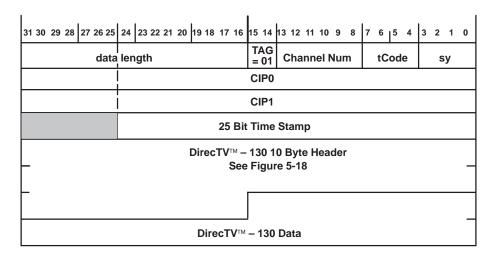

| 5–14 1394 DirecTV™ Packet                                      | 5–15 |

| 5–15 DirecTV™ Transmit Format                                  | 5–15 |

| 5–16 DirecTV™ Receive Format                                   | 5–16 |

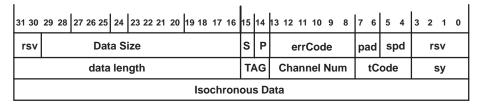

| 5–17 Isochronous CIP Headers – DSS Data                        | 5–16 |

| 5–18 DirecTV™ 130 10-Byte Header                               | 5–16 |

| 5–19 DV Transmit Format – DIF Sequence                         | 5–19 |

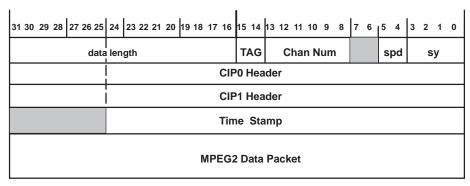

| 5–20 DV Transmit Data Packet                                   | 5–19 |

| 5–21 DV Receive Format                                         | 5–19 |

| 5–22 Isochronous CIP Headers – DV Data                         | 5–19 |

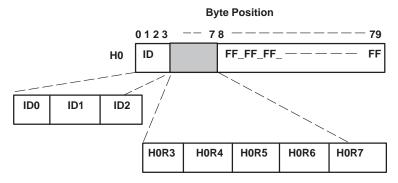

| 5–23 H0 DIF Block Header for DV Transmit                       | 5–20 |

| 5–24 DV Smoothing                                              | 5–21 |

| 5–25 ISO Transmit                                              | 5-25 |

| 5–26 | ISO Receive                                           | 5–25 |

|------|-------------------------------------------------------|------|

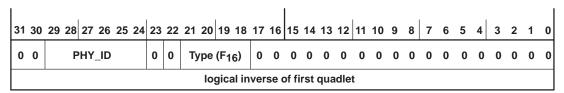

| 5–27 | PHY Configuration Packet Format                       | 5–26 |

| 5–28 | Remote Access Packet Format                           | 5–27 |

| 5–29 | Remote Reply Packet – Receive                         | 5–28 |

| 5–30 | Remote Command Packet                                 | 5–28 |

| 5–31 | Remote Confirmation Packet                            | 5–29 |

| 5–32 | Resume Packet                                         | 5–30 |

| 5–33 | Self-ID Packet Control Token Format                   | 5–31 |

| 5–34 | Receive Self-ID Packet Format (RCVSID=1, RXSIDFULL=1) | 5–32 |

| 5-35 | Receive Self-ID Packet Format (RCVSID=1, RXSIDFULL=0) | 5-32 |

## **List of Tables**

| Iabi | e litle                                                       | Page               |

|------|---------------------------------------------------------------|--------------------|

| 3–1  | Pin Name/Buffer Name Cross Reference, Sorted by Pin Number    | 2–12<br>3–7<br>3–8 |

|      | Multistrobe Mode - Write Critical Timing Numbers              | 3–9                |

|      | Multistrobe Mode - Read Critical Timing Numbers               |                    |

|      | HSDIx_A[2:0] Bus Encoding Values                              |                    |

|      | HSDI Synchronization Modes                                    |                    |

|      | HSDI Critical Timing Parameters                               |                    |

|      | Time Stamp and Aging Control Bits                             | 4–2                |

|      | Allowable Values for 1394 Time Stamps                         | 4–4                |

|      | Interrupt Enables and Descriptions                            | 4–7                |

|      | Configuration Registers for PID Filtering                     | 4–9                |

|      | Configuration Registers for Packet Insertion                  | 4-12               |

| 5–1  | Asynchronous Transmit Header Insert†                          | 5–1                |

| 5–2  | tCodes Supported for Asynchronous Automatic Header Insertion  | 5–1                |

| 5-3  | Quadlet Transmit Format Functions                             | 5–2                |

| 5–4  | Block – Transmit Format Functions                             | 5–4                |

| 5–5  | Bit Description for Packet Control Token                      | 5–5                |

| 5–6  | Asynchronous Receive Control                                  | 5–5                |

| 5–7  | Asynchronous Receive Header Strip                             | 5–6                |

|      | Quadlet – Receive Format Functions                            | 5–7                |

| 5–9  | Block – Receive Format Functions                              | 5–8                |

|      | O ACK Code Meanings                                           | 5–9                |

| 5–1  | Acknowledge Buffer Bit Descriptions for Asynchronous Packets  | 5–10               |

|      | 2 Asynchronous Stream Transmit Functions                      |                    |

|      | 3 Asynchronous Stream Receive Functions                       |                    |

|      | 4 Isochronous-Transmit Functions                              |                    |

|      | 5 MPEG2 DVB Transmit Bandwidth Classes                        |                    |

|      | 6 MPEG2 Receive Header Stripping                              |                    |

|      | 7 DirecTV™ Transmit Bandwidth Classes                         |                    |

|      | 3 DirecTV™ Receive Header Stripping                           |                    |

|      | 9 Automatic Empty Packets Relative to Frame Length, NTSC Only |                    |

|      | O Automatic Empty Packets Relative to Frame Length, PAL Only  |                    |

|      | 1 Receive Header Stripping                                    |                    |

|      | 2 DV TX Headers                                               |                    |

|      | 3 Isochronous Transmit Header Stripping                       |                    |

|      | 4 Isochronous Receive Header Stripping                        |                    |

| 5-2  | 5 Isochronous Receive Headers                                 | 5-26               |

| 5–26 PHY Configuration Packet Functions                                         | 5–27 |

|---------------------------------------------------------------------------------|------|

| 5–27 Remote Access Packet Functions                                             | 5–27 |

| 5–28 Remote Reply Packet Functions                                              | 5–28 |

| 5–29 Remote Command Packet Functions                                            | 5–29 |

| 5–30 Remote Confirmation Packet Functions                                       | 5–29 |

| 5–31 Remote Confirmation Packet Functions                                       | 5–30 |

| 5–32 Resume Packet Functions                                                    | 5–30 |

| 5–33 Bit Descriptions for Self-ID Packet Control Token                          | 5–31 |

| 5–34 Receive Self-ID Setup Using Control Register Bits (RCVSID and RXSIDFULL) . | 5–31 |

| 5–35 Receive Self-ID Function                                                   | 5–33 |

| 5–36 Data Buffer Contents (following a bus reset) With Three Nodes on the Bus   | 5–33 |

| 6–1 ceLynx Address Ranges                                                       | 6–1  |

## 1 Introduction

## 1.1 Device Package Information

| ORDERING NUMBER | NAME      | VOLTAGE | PACKAGE  |

|-----------------|-----------|---------|----------|

| TSB42AA4        | ceLynx    | 3.3 V   | PQFP 128 |

| TSB42AB4        | ceLynx-DV | 3.3 V   | PQFP 128 |

## 1.2 References

The following sources of information were used in the generation of this document:

- IEEE Standard for a High Performance Serial Bus, IEEE Standard 1394–1995

- IEEE 1394.a Serial Bus Supplement, IEEE P1394a Draft 3.0

- Digital Interface for Consumer Audio/Video Equipment, IEC Document 61883

- Open Cable<sup>®</sup>, Home Digital Network (HDND) 1394 Interface Specification, Version 2.0

- 1394 TA Document 1998017, ITU-R BO 1294 System B Signal Transmission 1.0

## 2 ceLynx Overview

#### 2.1 ceLynx Description

Consumer Electronics Link (ceLynx) is a high performance 1394 link layer device designed specifically to support advanced consumer electronics applications, particularly those applications which require the transmission of Moving Picture Expert Group 2 (MPEG2) transport streams and encryption/decryption of those streams across a 1394 network. The device supports both digital video broadcasting (DVB) and DirecTV™ type MPEG2 streams using the digital transmission content protection method (DTCP) method of encryption, as well as digital video (DV) encoded streams. The ceLynx supports both the IEC 61883 standard for DVB and DV streams over 1394 and the 1394 Trade Association standard for DirecTV™ over 1394.

The ceLynx is also versatile enough to handle regular 1394 isochronous (TAG=00), asynchronous data and asynchronous streams. A key feature of the ceLynx is its ability to handle multiple data type streams simultaneously; the user may transport DVB, DirecTV™, and DV data streams and normal isochronous and asynchronous data *simultaneously*. The ceLynx can also support multiple streams of the same data type simultaneously,(for example, transmit or receive two DVB transport streams or two DV streams).

The ceLynx is full duplex, allowing simultaneous playback and recording of audio/video data. Full duplex support also includes the capability of using the DTCP method simultaneously using the two embedded M6 cipher modules. The large internal 8-Kbyte FIFO is very flexible, allowing the user to partition it into eight independent first in first out (FIFOs) and allowing the user to determine the exact configuration of each of these FIFOs to fit their application. Advanced features have been added to support *time shifting* applications, Program ID (PID) filtering and packet insertions.

The ceLynx is also designed to interface seamlessly with popular MPEG2 decoder chipsets. This decreases the design-in effort of customers when using these popular chipsets.

## 2.2 Key Features

- DTCP content protection (TSB42AA4 only).

- Interfaces directly to industry standard 400, 200, and 100 Mbit physical layer devices, including Texas Instruments TSB41LV0X and TSB41AXX family of physical layer devices.

- Compliant with IEEE 1394-1995 and IEEE 1394.a.

- MPEG2 time stamp-based release, as described in IEC 61883-4.

- High-speed data interface (HSDI):

- Byte-wide or serial mode

- Two independent HSDI ports

- Bidirectional

- Several control modes for a variety of applications

- Connects seamlessly to common MPEG2 decoder chipsets

- 16-bit microprocessor interface supports Motorola 68000/68020 style bus

- Large 8K byte FIFO can be configured up to eight independent Tx or Rx FIFOs

- 8K byte FIFO supports the following data types:

- DVB MPEG2 transport streams (IEC 61883-4)

- DirecTV™ transport streams

DirecTV is a trademark of Hughes Communications, Inc.

- DV program streams (IEC 61883-2)

- Asynchronous streams

- Unformatted and packed asynchronous and isochronous streams

- Support for external processor DMA

- Programmable data/space available indications for flow control; almost full and almost empty indicators

- Hardware assist built in for time-shift application; allows reuse of old time stamps for AV-HDD applications

- Supports bus manager functions and automatic 1394 self-ID verification

- · Interrupt driven to minimize host polling

- Single 3.3-V supply

- Separate async acknowledge buffer decreases the ack-tracking burden on host

- JTAG interface to support post-assembly scan of device I/O

- Bus holder isolation

- Embedded support for DTCP content protection:

- Two M6 baseline ciphers (one per HSDI port)

- Random number generator in hardware

- SHA-1 secure hash algorithm in hardware

- Authentication key cipher in hardware

- Optional auto-configuration for MPEG2/DV transmit and receive functions

- PID filtering and packet insertion for MPEG2 transport stream

## 2.3 Application Information

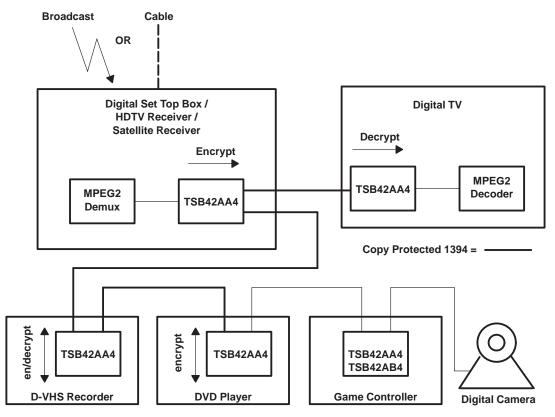

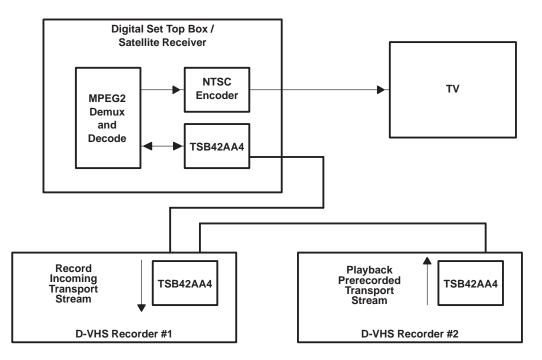

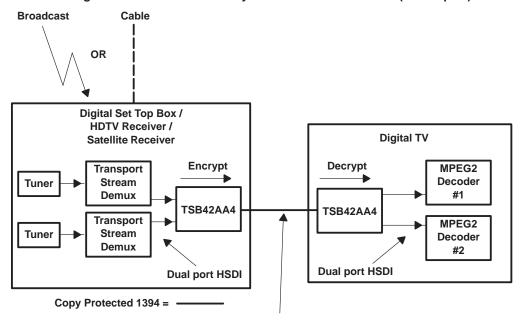

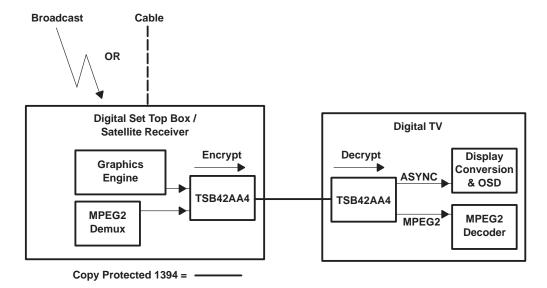

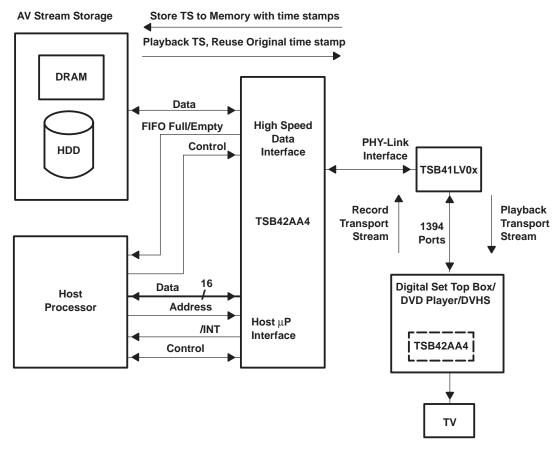

Figures 2–1 through 2–5 show several applications where the ceLynx fulfills various functional requirements for consumer electronic devices.

Figure 2–1. Home Entertainment System Interconnect With Content Protection

Figure 2-2. Simultaneous Playback and Record of Video (Full Duplex)

The set box sends multiple PES packets to the digital TV on either one transport stream on one Iso channel OR on two different transport streams on two different Iso channels.

Figure 2-3. Picture in Picture Capability Inside Digital TV

Figure 2-4. Graphics Overlay From Digital STB to DTV

Figure 2-5. Time-Shift Application

## 2.4 ceLynx Functional Block Diagram

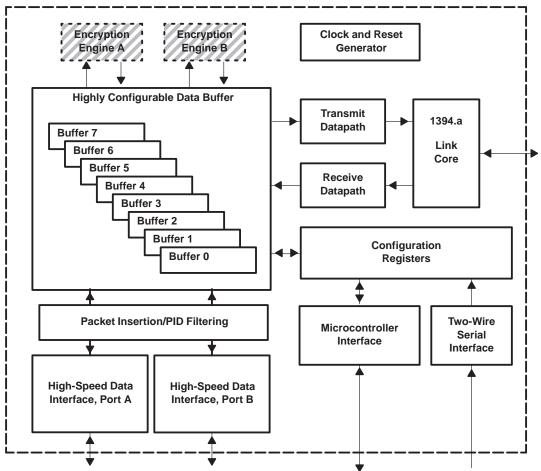

† Shaded region (encryption engines A and B) are only implemented in TSB42AA4.

Figure 2-6. ceLynx Functional Block Diagram

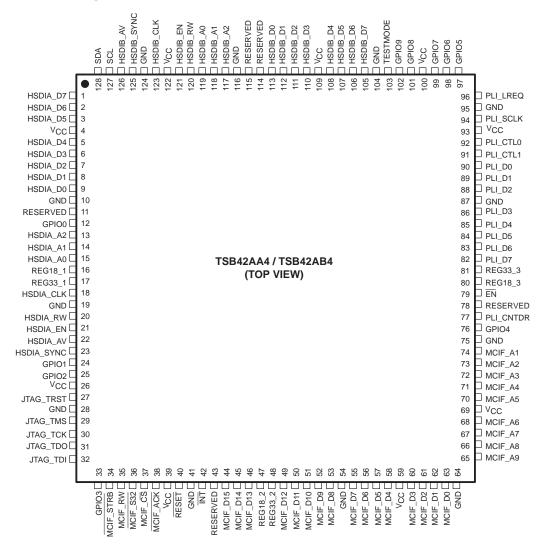

## 2.5 Pin Assignments

#### 2.5.1 Pin Descriptions

#### 2.5.1.1 Power

| NAME  | PIN NO.                                                    | I/O | DESCRIPTION                             |

|-------|------------------------------------------------------------|-----|-----------------------------------------|

| GND   | 10, 19, 28, 41,<br>54, 64, 75, 87,<br>95, 104, 116,<br>124 | _   | Device ground terminals                 |

| Vcc   | 4, 26, 39, 59,<br>69, 93, 100,<br>109, 122                 | -   | 3.3 V power supply terminals            |

| RESET | 40                                                         | I   | Reset input. This signal is active low. |

## 2.5.1.2 Voltage Regulators

| NAME                          | PIN NO.        | I/O | DESCRIPTION                                                                                                                                                                                      |

|-------------------------------|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REG18_1<br>REG18_2<br>REG18_3 | 16<br>47<br>80 | 0   | Internal 1.8-V voltage regulator outputs. These pins should be connected to ground through a 0.1 $\mu\text{F}$ decoupling capacitor. They provide decoupling for the internal voltage regulator. |

| REG33_1<br>REG33_2<br>REG33_3 | 17<br>48<br>81 | I   | Internal voltage regulator inputs. The regulator provides the 1.8 V needed for the ceLynx internal logic. These pins should be connected to 3.3 V (V $_{\rm CC}$ .)                              |

| EN                            | 79             | I   | Internal power supply enable. Active low. This pin must be tied low to enable the ceLynx internal 1.8-V power supply.                                                                            |

## 2.5.1.3 High-Speed Data Interface

| NAME         | PIN NO.                                      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|----------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HSDIA_D[7:0] | 1, 2, 3, 5,<br>6, 7, 8, 9                    | I/O | HSDI port A data bus. Bidirectional HSDIA_D[7] is the MSB and HSDIA_D[0] is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| HSDIB_D[7:0] | 105, 106, 107,<br>108, 110, 111,<br>112, 113 | I/O | HSDI port B data bus. Bidirectional HSDIB_D[7] is the MSB and HSDIB_D[0] is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| HSDIA_A[2:0] | 13, 14, 15                                   | I   | HSDI port A address bus. HSDIA_A[2] is the MSB and HSDIA_A[0] is the LSB. Selects the internal buffer used to store data prior to 1394 transmission or after 1394 reception. This bus is unused when HSDI port A is configured in single stream mode.                                                                                                                                                                                                                                                       |

| HSDIB_A[2:0] | 117, 118, 119                                | I   | HSDI port B address bus. HSDIB_A[2] is the MSB and HSDIB_A[0] is the LSB.  Selects the internal buffer used to store data prior to 1394 transmission or after 1394 reception.  This bus is unused when HSDI port B is configured in single stream mode.                                                                                                                                                                                                                                                     |

| HSDIA_CLK    | 18                                           | I   | HSDI port A clock. (Data is clocked on the rising clock edge.) Max throughput in byte mode is 27 Mbytes/sec.                                                                                                                                                                                                                                                                                                                                                                                                |

| HSDIB_CLK    | 123                                          | I   | HSDI port B clock. (Data is clocked on the rising clock edge.) Max throughput in byte mode is 27 Mbytes/sec.                                                                                                                                                                                                                                                                                                                                                                                                |

| HSDIA_Sync   | 23                                           | I/O | HSDI port A synchronization signal. Used to determine data packet boundaries. In 1394 transmit mode, the external host device drives the signal, marking the beginning or end of a data block. In 1394 receive mode, the ceLynx drives the pin, signaling the beginning or end of a data block The exact operation of the HSDIA_Sync depends on the synchronization mode. HSDIA_Sync polarity is programmable and defaults to <i>active high</i> . In default HSDIA configuration, this signal is not used. |

| HSDIB_Sync   | 125                                          | I/O | HSDI port B synchronization signal. Used to determine data packet boundaries. In 1394 transmit mode, the external host device drives the signal, marking the beginning or end of a data block. In 1394 receive mode, the ceLynx drives the pin, signaling the beginning or end of a data block The exact operation of the HSDIB_Sync depends on the synchronization mode. HSDIB_Sync polarity is programmable and defaults to <i>active high</i> . In default HSDIB configuration, this signal is not used. |

## 2.1.5.3 High-Speed Data Interface (continued)

| NAME      | PIN NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-----------|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| HSDIA_R/W | 20      | Ι   | HSDI port A read/write signal. Used to indicate either a host read or a how write transaction to the HSDIA port.  HSDIA_R/W polarity is programmable and defaults to active high during read operations and active low during write operations.                                                                                                                                                                            |  |  |  |

| HSDIB_R/W | 120     | _   | HSDI port B read/write signal. Used to indicate either a host read or a host write transaction to the HSDIB port.  HSDIB_R/W polarity is programmable and defaults to active high during read operations and active low during write operations.                                                                                                                                                                           |  |  |  |

| HSDIA_AV  | 22      | 0   | HSDI port A data available. Used during 1394 receive operations. Indicates when a packet of data is available in the selected receive buffer (as indicated by HSDIA_A[2:0].). HSDIA_AV polarity is programmable and defaults to <i>active high</i> .                                                                                                                                                                       |  |  |  |

| HSDIB_AV  | 126     | 0   | HSDI port B data available. Used during 1394 receive operations. Indicate when a packet of data is available in the selected receive buffer (sindicated by HSDIB_A[2:0].). HSDIB_AV polarity is programmable and defaults to active high.                                                                                                                                                                                  |  |  |  |

| HSDIA_EN  | 21      | I   | HSDIA port access enable. Used to indicate valid data for 1394 transmit (host write) or 1394 receive (host read) operations. Asserting HSDIA_EN during host writes latches the data on the next HSDIA_CLK rising edge. Asserting HSDIA_EN during host reads, presents received 1394 data from internal buffers on the next HSDIA_CLK rising edge. HSDIA_EN polarity is programmable and defaults to active high.           |  |  |  |

| HSDIB_EN  | 121     | _   | HSDIB port access enable. Used to indicate valid data for 1394 transmit (host write) operations or 1394 receive (host read) operations. Asserting HSDIB_EN during host writes latches the data on the next HSDIB_CLK rising edge. Asserting HSDIB_EN during host reads presents received 1394 data from internal buffers on the next HSDIB_CLK rising edge. HSDIB_EN polarity is programmable and defaults to active high. |  |  |  |

## 2.5.1.4 Microcontroller Interface (MCIF)†

| NAME      | PIN NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |

|-----------|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCIF_CS   | 37      | I   | ceLynx chip select. Enables the ceLynx to perform read or write transactions on the microcontroller interface. The MCIF_CS polarity is programmable and defaults to <i>active low</i> .                                                                                                                                                            |

| MCIF_ACK  | 38      | 0   | Acknowledge signal. Indicates to the host controller the completion of the current read or write access.                                                                                                                                                                                                                                           |

|           |         |     | When MCIF_ACK asserts (low) during host writes, data has been successfully written to the specified address. When MCIF_ACK asserts (low) during host reads, this indicates that data is valid and may be read by the host.  The MCIF_ACK polarity is programmable and defaults to active low.                                                      |

| MCIF_STRB | 34      | I   | Data strobe signal. During host write operations, this signal indicates that the data on MCIF_D[15:0] is valid and the ceLynx latches the data. During host read operations, this signal indicates to the ceLynx that the host is ready for data.  The MCIF_STRB polarity is programmable to active high or active low and defaults to active low. |

$<sup>\</sup>ensuremath{^{\dagger}}$  The microcontroller port does not support time stamping or encryption.

## 2.1.5.4 Microcontroller Interface† (continued)

| NAME         | PIN NO.                                                                 | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|--------------|-------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MCIF_RW      | 35                                                                      | _   | Read/write indicator. Indicates whether the current pending access is a rea or a write.  MCIF_RW polarity is programmable and defaults to <i>active high</i> during rea operations and <i>active low</i> during write operations.                                                                                                                  |  |  |  |  |

| MCIF_S32     | 36                                                                      | I   | Data transfer size indicator. Indicates whether the host controller desire 16-bit or 32-bit transactions. When set to 32-bit transactions, the post address auto-increments on the second consecutive access. The MCIF_32 polarity is programmable to active high or active low and defaults to active low. Active signal indicates 32-bit access. |  |  |  |  |

| ĪNT          | 42                                                                      | 0   | Interrupt. This is the ceLynx interrupt output to the host. The INT polarity is programmable and defaults to active low.                                                                                                                                                                                                                           |  |  |  |  |

| MCIF_A[9:1]  | 65, 66, 67, 68,<br>70, 71, 72, 73,<br>74                                | I   | Microcontroller interface address bus. MCIF_A[9] is the MSB and MCIF_A[1] is the LSB. Users should connect their LSB+1 address pin to MCIF_A[1] (byte access is not allowed).                                                                                                                                                                      |  |  |  |  |

| MCIF_D[15:0] | 44, 45, 46, 49,<br>50, 51, 52, 53,<br>55, 56, 57, 58,<br>60, 61, 62, 63 | I/O | Microcontroller interface bidirectional data bus. MCIF_D[15] is the MSB on this bus, and MCIF_D[0] is the LSB.                                                                                                                                                                                                                                     |  |  |  |  |

<sup>†</sup> The microcontroller port does not support time stamping or encryption.

## 2.5.1.5 JTAG

| NAME      | PIN NO. | I/O | DESCRIPTION                                                                               |

|-----------|---------|-----|-------------------------------------------------------------------------------------------|

| JTAG_TRST | 27      | I   | JTAG test reset. During normal device operation, this signal should be pulled high.       |

| JTAG_TMS  | 29      | I   | JTAG test mode select. During normal device operation, this signal should be pulled high. |

| JTAG_TCK  | 30      | ı   | JTAG clock. During normal device operation this signal should be pulled high.             |

| JTAG_TDO  | 31      | 0   | JTAG data output. During normal device operation, this signal should be left unconnected. |

| JTAG_TDI  | 32      | I   | JTAG data in. During normal device operation, this signal should be pulled high.          |

## 2.5.1.6 Two-Wire Serial Interface

| NAME | PIN NO. | I/O | DESCRIPTION                                                                                                                                                                                                                      |

|------|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA  | 127     | I   | Serial interface data input signal. Open collector input that typically interfaces to a serial EEPROM containing CFR data. Used during ceLynx power up and reset to auto configure CFRs.                                         |

| SCL  | 128     | 0   | Serial interface clock. Open collector. SCL is sampled at power up to determine if an EEPROM is present. Connect to ground if no ceLynx serial EEPROM configuration device is used. At maximum operations, frequency is 100 kHz. |

## 2.5.1.7 PHY-Link Interface

| NAME         | PIN NO.                                 | I/O | DESCRIPTION                                                                                                                                                                                                                                                |

|--------------|-----------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLI_D[0:7]   | 90, 89,<br>88, 86,<br>85, 84,<br>83, 82 | I/O | PHY-link data bus. PLI_D[0] is the MSB and PLI_D[7] is the LSB.                                                                                                                                                                                            |

| PLI_SCLK     | 94                                      | _   | Physical layer system clock. Supplied by the physical layer device and is 49.152 MHz. PLI_SCLK is required for link layer operation.                                                                                                                       |

| PLI_CNTDR    | 77                                      | I/O | Contender signal. When PLI_CNTDR is configured as an output in the SYSCFR.PINCFG register, the pin sets the IRM contender function in the PHY. When configured as an input, the pin reports the PHY contender status to the LCTRL (link control) register. |

| PLI_CTL[0:1] | 92, 91                                  | I/O | PHY-link interface control signals. These bidirectional control signals control the passage of information between the link and PHY. PLI_CTL[0] is the MSB and PLI_CTL[1] is the LSB.                                                                      |

| PLI_LPS      | NC                                      | NC  | PLI_LPS is not implemented in the current design.                                                                                                                                                                                                          |

| PLI_LREQ     | 96                                      | 0   | Link request. Requests the physical layer controller to perform some service.                                                                                                                                                                              |

## 2.5.1.8 Optional Signals

| NAME     | PIN NO. | I/O | DESCRIPTION                                                                |  |  |  |  |  |

|----------|---------|-----|----------------------------------------------------------------------------|--|--|--|--|--|

| GPIO0    | 12      | I/O |                                                                            |  |  |  |  |  |

| GPIO1    | 24      | I/O |                                                                            |  |  |  |  |  |

| GPIO2    | 25      | I/O |                                                                            |  |  |  |  |  |

| GPIO3    | 33      | I/O | General-Purpose I/O's.                                                     |  |  |  |  |  |

| GPIO4    | 76      | I/O | General-i dipose i/O s.                                                    |  |  |  |  |  |

| GPIO5    | 97      | I/O | GPIO functions are programmed via CFRs (reg 0×008 GPIOSEL). GPIOs are con- |  |  |  |  |  |

| GPIO6    | 98      | I/O | figured as ceLynx inputs after reset or power up.                          |  |  |  |  |  |

| GPIO7    | 99      | I/O |                                                                            |  |  |  |  |  |

| GPIO8    | 101     | I/O |                                                                            |  |  |  |  |  |

| GPIO9    | 102     | I/O |                                                                            |  |  |  |  |  |

| RESERVED | 11      | NC  | Reserved for future use. Leave unconnected.                                |  |  |  |  |  |

| RESERVED | 43      | NC  | Reserved for future use. Leave unconnected                                 |  |  |  |  |  |

| RESERVED | 78      | NC  | Reserved for future use. Leave unconnected.                                |  |  |  |  |  |

| RESERVED | 114     | NC  | Reserved for future use. Leave unconnected.                                |  |  |  |  |  |

| RESERVED | 115     | NC  | Reserved for future use. Leave unconnected.                                |  |  |  |  |  |

| TESTMODE | 103     | I   | Factory test pin. Connect to GND for normal device operation.              |  |  |  |  |  |

Table 2–1. Pin Name/Buffer Name Cross Reference, Sorted by Pin Number

| PIN# | PIN NAME               | I/O | PIN# | PIN NAME        | I/O | PIN# | PIN NAME              | I/O |

|------|------------------------|-----|------|-----------------|-----|------|-----------------------|-----|

| 1    | HSDIA_D7               | I/O | 44   | MCIF_D15        | I/O | 86   | PLI_D3                | I/O |

| 2    | HSDIA_D6               | I/O | 45   | MCIF_D14        | I/O | 87   | GND                   |     |

| 3    | HSDIA_D5               | I/O | 46   | MCIF_D13        | I/O | 88   | PLI_D2                | I/O |

| 4    | V <sub>CC</sub>        |     | 47   | REG18_2         | 0   | 89   | PLI_D1                | I/O |

| 5    | HSDIA_D4               | I/O | 48   | REG33_2         |     | 90   | PLI_D0                | I/O |

| 6    | HSDIA_D3               | I/O | 49   | MCIF_D12        | I/O | 91   | PLI_CTL1              | I/O |

| 7    | HSDIA_D2               | I/O | 50   | MCIF_D11        | I/O | 92   | PLI_CTL0              | I/O |

| 8    | HSDIA_D1               | I/O | 51   | MCIF_D10        | I/O | 93   | V <sub>CC</sub>       |     |

| 9    | HSDIA_D0               | I/O | 52   | MCIF_D9         | I/O | 94   | PLI_SCLK              | ı   |

| 10   | GND                    |     | 53   | MCIF_D8         | I/O | 95   | GND                   |     |

| 11   | RESERVED               | NC  | 54   | GND             |     | 96   | PLI_LREQ              | 0   |

| 12   | GPIO0                  | I/O | 55   | MCIF_D7         | I/O | 97   | GPIO5                 | I/O |

| 13   | HSDIA_A2               | Τ   | 56   | MCIF_D6         | I/O | 98   | GPIO6                 | I/O |

| 14   | HSDIA_A1               | ı   | 57   | MCIF_D5         | I/O | 99   | GPIO7                 | I/O |

| 15   | HSDIA_A0               | Τ   | 58   | MCIF_D4         | I/O | 100  | V <sub>CC</sub>       |     |

| 16   | REG18_1                | 0   | 59   | V <sub>CC</sub> |     | 101  | GPIO8                 | I/O |

| 17   | REG33_1                | Ι   | 60   | MCIF_D3         | I/O | 102  | GPIO9                 | I/O |

| 18   | HSDIA_CLK              | Ι   | 61   | MCIF_D2         | I/O | 103  | TESTMODE              | ı   |

| 19   | GND                    |     | 62   | MCIF_D1         | I/O | 104  | GND                   |     |

| 20   | HSDIA_RW <sup>†</sup>  | ı   | 63   | MCIF_D0         | I/O | 105  | HSDIB_D7              | I/O |

| 21   | HSDIA_EN <sup>†</sup>  | Τ   | 64   | GND             |     | 106  | HSDIB_D6              | I/O |

| 22   | HSDIA_AV <sup>†</sup>  | 0   | 65   | MCIF_A9         |     | 107  | HSDIB_D5              | I/O |

| 23   | HSDIA_SYNC†            | I/O | 66   | MCIF_A8         |     | 108  | HSDIB_D4              | I/O |

| 24   | GPIO1                  | I/O | 67   | MCIF_A7         | ı   | 109  | V <sub>CC</sub>       |     |

| 25   | GPIO2                  | I/O | 68   | MCIF_A6         | I   | 110  | HSDIB_D3              | I/O |

| 26   | V <sub>CC</sub>        |     | 69   | V <sub>CC</sub> |     | 111  | HSDIB_D2              | I/O |

| 27   | JTAG_TRST              | I   | 70   | MCIF_A5         | I   | 112  | HSDIB_D1              | I/O |

| 28   | GND                    |     | 71   | MCIF_A4         | I   | 113  | HSDIB_D0              | I/O |

| 29   | JTAG_TMS               | I   | 72   | MCIF_A3         | I   | 114  | RESERVED              | NC  |

| 30   | JTAG_TCK               | I   | 73   | MCIF_A2         | ı   | 115  | RESERVED              | NC  |

| 31   | JTAG_TDO               | 0   | 74   | MCIF_A1         | I   | 116  | GND                   |     |

| 32   | JTAG_TDI               | I   | 75   | GND             |     | 117  | HSDIB_A2              | I   |

| 33   | GPIO3                  | I/O | 76   | GPIO4           | I/O | 118  | HSDIB_A1              | I   |

| 34   | MCIF_STRB <sup>†</sup> | I   | 77   | PLI_CNTDR       | I/O | 119  | HSDIB_A0              | I   |

| 35   | MCIF_RW <sup>†</sup>   | I   | 78   | RESERVED        | NC  | 120  | HSDIB_RW <sup>†</sup> | I   |

| 36   | MCIF_S32 <sup>†</sup>  | I   | 79   | EN <sup>‡</sup> | I   | 121  | HSDIB_EN <sup>†</sup> | I   |

| 37   | MCIF_CS†               | I   | 80   | REG18_3         | 0   | 122  | V <sub>CC</sub>       |     |

| 38   | MCIF_ACK <sup>†</sup>  | 0   | 81   | REG33_3         | I   | 123  | HSDIB_CLK             | I   |

| 39   | V <sub>CC</sub>        |     | 82   | PLI_D7          | I/O | 124  | GND                   |     |

| 40   | RESET‡                 | I   | 83   | PLI_D6          | I/O | 125  | HSDIB_SYNC†           | I/O |

| 41   | GND                    |     | 84   | PLI_D5          | I/O | 126  | HSDIB_AV†             | 0   |

| 42   | ĪNT ‡                  | 0   | 85   | PLI_D4          | I/O | 127  | SCL                   | I/O |

| 43   | RESERVED               | NC  |      |                 |     | 128  | SDA                   | I/O |

<sup>†</sup> Denotes pin with programmable polarity. ‡ Denotes active low pin.

#### 3 External Interfaces

The ceLynx has four external interfaces; the HSDI, the microcontroller interface (MCIF), the physical layer interface, and a two-wire serial interface for an external EEPROM. The HSDI and MCIF each support multiple modes designed for maximum flexibility and ease of use. The physical layer interface conforms to IEEE 1394-1995 and 1394.a standards and allows the ceLynx to operate seamlessly with industry standard 100-, 200-, and 400-Mbit physical layer devices. This includes the Texas Instruments family of 400 Mbps PHYS (TSB41LV0X). The two-wire serial interface gives a connection to EEPROM for easy loading of CFR and CSR information

This section includes the interface, functional operation, and detailed timing information for all modes of each interface.

## 3.1 Microcontroller Interface (MCIF)

The ceLynx has a host controller interface that is designed to interface seamlessly with 68000/68020 style processors. This interface is completely asynchronous. The interface consists of 16 data lines, 9 address lines, and various control signals. All signals are resynchronized internally to a 50-MHz clock derived from the SCLK input from the physical layer device. The host controller interface operates seamlessly with various vendors MPEG2 transport chipsets for ease of use.

Both 32-bit and 16-bit transactions are supported on the microcontroller interface. When using 32-bit accesses the host supplies only one address, then follows with two data phases. The link microcontroller interface automatically increments the address for the second data phase. For 16-bit access, each transaction requires a separate address. Each 16-bit access is independent of any other transaction. The microcontroller interface uses the MCIF\_S32 signal to determine if the current access is 32- or 16-bit. The MCIF\_S32 signal state should not change in the middle of an access. It can change in between accesses.

The 16-bit transaction capability allows the host more efficient access since it eliminates the need for the host to disable interrupts between upper and lower doublet accesses. Disabling interrupts is required if only full quadlet (32-bit) access is supported for every CFR access.

For a 32-bit read, the upper and lower doublets are time independent. When the first doublet is accessed, a snapshot of the entire 32-bit register is captured. The second doublet access uses the snapshot value.

The snapshot is not used for 16-bit register access. Each 16-bit access results in the most up to date doublet value.

Note that nonquadlet aligned addressing is not supported. The host controller can only access the upper half or lower half of any 32-bit CFR. For example, the version ID CFR is located at addresses 000h and 002h. The host is not allowed to perform a 32-bit access starting at address 003h. This would, in effect, be an attempt to write to addresses 003h and 004h. The 004h is located within a separate CFR. However, using 16-bit transactions, the user can access either upper or lower half of all 32-bit CFRs independently.

#### NOTE:

The host interface does not support time stamping or encryption.

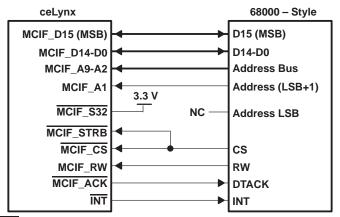

Figure 3–1 shows the typical connection between ceLynx and 68000-style processor.

NOTES: 1. MCIF\_S32 is used for controllers that can supply a single address for a 32-bit transaction.

MCIF\_STRB is provided for controllers that have separate strobe and chip select signals. The MCIF\_STRB

and MCIF\_CS signals can be tied together if the application processor does not have a separate strobe

signal.

Figure 3-1. Interface Between ceLynx and 68000-Style Processor

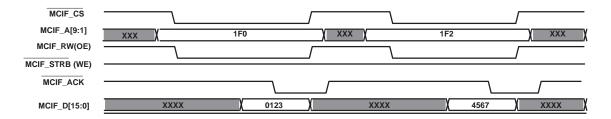

## 3.1.1 Read Operation

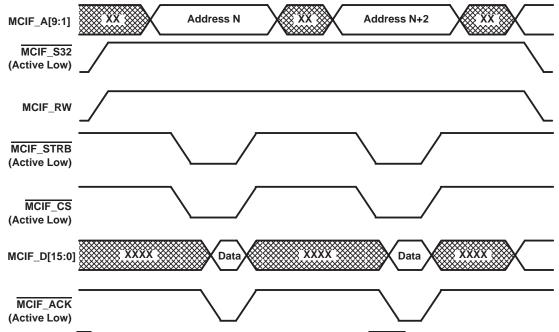

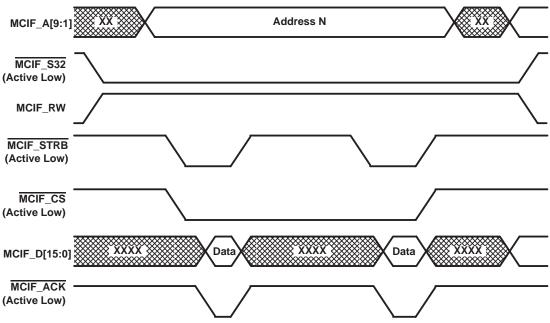

Figure 3–2 depicts a typical read operation using 16-bit transactions. The host begins the read access by driving the address to be read from onto MCIF\_A[9:1]. The host then drives MCIF\_RW high to indicate a read. The host drives MCIF\_STRB low to indicate that it is ready to receive the data. MCIF\_CS selects the link as the peripheral being accessed. Note the MCIF\_STRB signal acts as a master enable on the microcontroller interface. No transactions occur unless MCIF\_STRB is active. The address is sampled on the falling edge of MCIF\_CS and begins the internal read access to the specified CFR. After the 16-bit word is retrieved from the internal CFR, the link responds by driving the data onto the data bus and driving MCIF\_ACK low to indicate that data is available

The difference in functionality of a 32-bit read transaction is that the host indicates a 32-bit access by driving MCIF\_S32 active low. The host will only give one address for the entire transaction. In this mode, the MCIF address signals should be driven for the entire 32-bit access. All other events remain the same. See Figure 3–3.

NOTE: MCIF\_CS can be asserted during both 16-bit transactions. The MCIF\_STROB acts as the master enable for the MCIF.

Figure 3-2. 16-Bit Read

NOTE: MCIF\_CS can be deasserted between data phases of 32-bit read. The MCIF\_STRB acts as the master enable for the MCIF.

Figure 3-3. 32-Bit Read

## 3.1.2 Write Operation

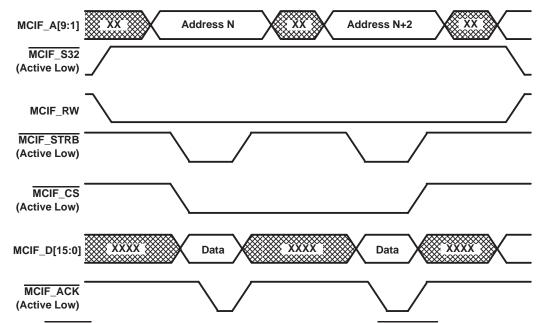

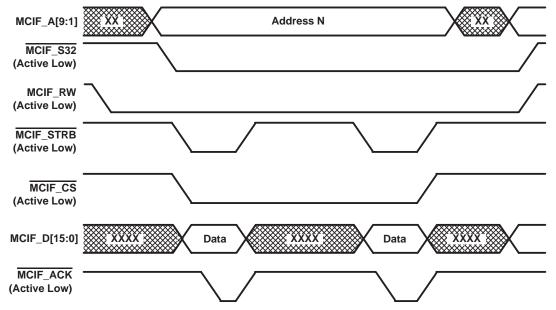

Figure 3–4 depicts a 16-bit write operation. The host begins the write access by driving the address to be written to MCIF\_A[9:1]. The host drives MCIF\_RW low to indicate a write, and MCIF\_CS low to select the link as the peripheral being accessed. The host drives the data out onto MCIF\_D[15:0] and MCIF\_STRB low to indicate that data present on the data bus is valid. The link responds by driving MCIF\_ACK low to indicate that this cycle is complete and data has been successfully written to the selected address.

NOTE: MCIF\_CS can be deasserted between the two 16-bit transactions. The MCIF\_STRB signal acts as the master enable for MCIF.

Figure 3-4. 16-Bit Write

Figure 3–5 depicts a 32-bit write operation. This works identically to the 16-bit write. However, the MCIF\_S32 signal is low for the entire access. This indicates a 32-bit access to ceLynx. ceLynx automatically increments the address for the second word access. Address N should be driven on the interface for the entire 32-bit access.

NOTE: MCIF\_CS can be deasserted between the data phases of a 32-bit access. The MCIF\_STRB signal acts as the master enable for MCIF.

Figure 3-5. 32-Bit Write

## 3.1.3 Critical Timing

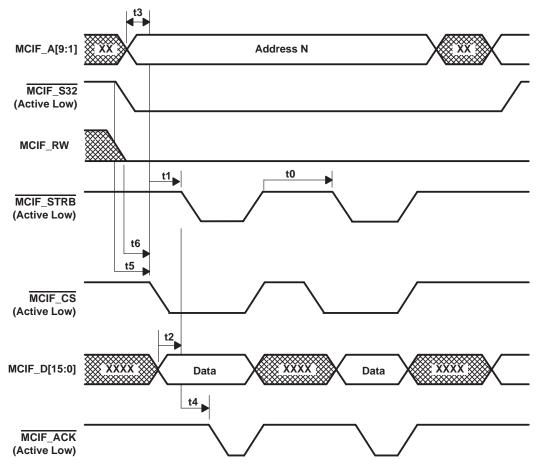

Figure 3–6 and Figure 3–7 show critical timing for read and write transactions. The critical timing numbers for 16-bit and 32-bit accesses are identical.

Figure 3-6. Microcontroller Interface Critical Write Timing

Figure 3-7. Microcontroller Interface Critical Read Timing

Table 3-1. MCIF Critical Timing Parameters

| PARAMETER | DESCRIPTION                               | MIN | MAX | UNITS |

|-----------|-------------------------------------------|-----|-----|-------|

| t0        | STR to STRB (rising edge to falling edge) | 9   |     | ns    |

| t1        | Setup time, CS to STRB                    | 0   |     | ns    |

| t2        | Setup time, DATA to STRB                  | 0   |     | ns    |

| t3        | Setup time, address to CS                 | 0   |     | ns    |

| t4        | Write access time, STRB to ACK            |     | 114 | ns    |

| t5        | Setup time, S32 to CS                     | 0   |     | ns    |

| t6        | Setup time, RW (write) to CS              | 0   |     | ns    |

| t7        | Read access time, STRB to ACK             |     | 114 | ns    |

| t8        | Data output delay, ACK to DATA out        | 0   |     | ns    |

| t9        | Setup time, RW (read) to CS               | 0   |     | ns    |

NOTES: 3. All signals have 0 ns hold time in relation to MCIF\_ACK.

4.  $\overline{STRB} = \overline{MCIF\_STRB}$ ,  $\overline{CS} = \overline{MCIF\_CS}$ , DATA =  $\overline{MCIF\_D[15:0]}$ , RW =  $\overline{MCIF\_RW}$

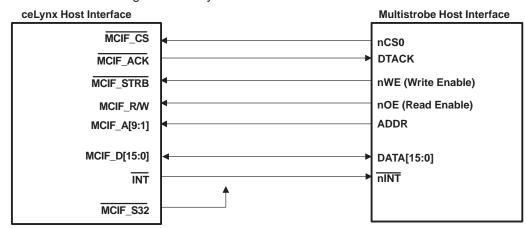

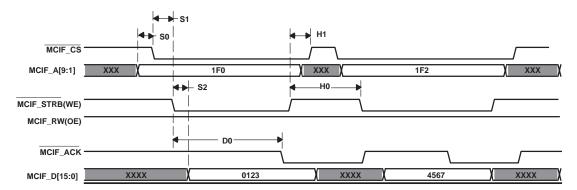

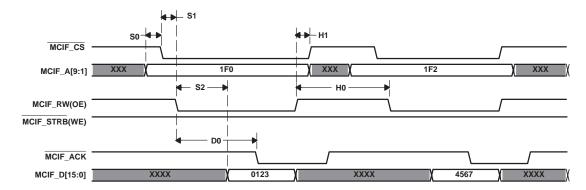

## 3.1.4 Host Interface – Multistrobe Mode

The ceLynx host port consists of separate 8-bit address and 16-bit data busses. In the default setting, reads and writes to the host port are controlled by one signal; MCIF\_RW. ceLynx has an additional mode, which can provide separate read and write strobes. ceLynx MCIF\_RW signal can be programmed to operate as a read strobe signal only. When in this mode, it is referred to as output enable. ceLynx MCIF\_STRB signal operates as the write strobe signal. In this mode, it is referred to as write enable.

## 3.1.4.1 Register Settings for Multistrobe Host Interface

The application should use the two-wire serial interface to external EEPROM to configure these registers on power up and reset.

Table 3-2. Multistrobe Mode Register Settings

| REGISTER AND BIT NAME | DESCRIPTION                                                                                                            |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| MCIFCFG.MCRWISOE      | The host interface MCIF_RW signal operates as read (output enable) (see Note 5)                                        |

| PINCFG.MCRWPOL        | Controls the active-level of MCIF_RW pin (see Note 6).                                                                 |

| PINCFG.MCCSZPOL       | Controls the active-level of MCIF_CS pin.                                                                              |

| PINCFG.MCSTRBZPOL     | Controls the active level of MCIF_STRB pin. In multistrobe mode this signal is default active low for a write request. |

- NOTES: 5. The MCIF\_STRB signal operates as write (input enable).

- 6. In multistrobe mode the default for a read request is active low.

## 3.1.4.2 Connection Diagram for ceLynx – Multistrobe Mode Host Interface

NOTE: 32-bit Accesses are also supported in (16-bit accesses) multistrobe mode.

Figure 3–8. Microcontroller Host Interface Connection Diagram

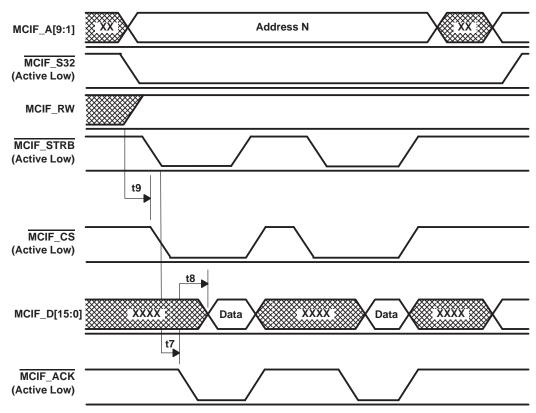

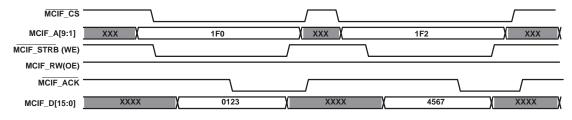

## 3.1.4.3 ceLynx – Host Port Multistrobe Functional Timing

Figure 3–9. Host Port Multistrobe Timing – Write Operation

Figure 3–10. Host Port Multistrobe Timing – Read Operation

Figure 3-11. Multistrobe Mode - Write Critical Timing

Table 3-3. Multistrobe Mode - Write Critical Timing Numbers

| VALUE                                                                                | MIN | MAX | UNIT |

|--------------------------------------------------------------------------------------|-----|-----|------|

| S0 Setup time for address valid to MCIF_CS low                                       | 0   |     |      |

| S1 Setup time for MCIF_CS low to MCIF_STRB (WE) asserted                             | 0   |     |      |

| S2 Setup time for MCIF_STRB (WE) asserted to beginning of data                       | 0   |     |      |

| D0 Delay time from MCIF_STRB (WE) asserted to write data operation complete MCIF_ACK |     | 114 | nS   |

| H0 Hold time between two MCIF_STRB (WE) cycles                                       | 9   |     | nS   |

| H1 Hold time between MCIF_STRB (WE) high and MCIF_CS high                            | 0   |     |      |

Figure 3-12. Multistrobe Mode - Read Critical Timing

Table 3-4. Multistrobe Mode - Read Critical Timing Numbers

| VALUE                                                                            | MIN | MAX | UNIT |

|----------------------------------------------------------------------------------|-----|-----|------|

| S0 Setup time for address valid to MCIF_CS low                                   | 0   |     |      |

| S1 Setup time for MCIF_CS low to MCIF_RW(OE) asserted                            | 0   |     |      |

| S2 Setup time for MCIF_RW(OE) asserted to beginning of data                      | 0   |     |      |

| D0 Delay time from MCIF_RW(OE) asserted to read data operation complete MCIF_ACK |     | 114 | nS   |

| H0 Hold time between two MCIF_RW(OE) cycles                                      | 9   |     | nS   |

| H1 Hold time between MCIF_RW(OE) high and MCIF_CS high                           | 0   |     |      |

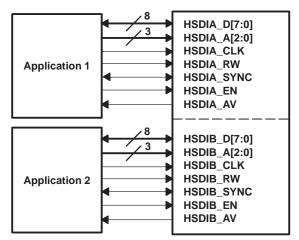

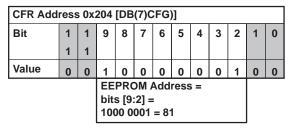

## 3.2 High-Speed Data Interface (HSDI)

The high-speed data interface is designed to support high bandwidth applications, where the access latency of the microcontroller interface is insufficient for the bandwidth of the streaming data. Examples include MPEG2 or DV streams where the upper limit of the incoming or outgoing data can be up to 60 Mbits/sec. The HSDI can support throughputs of up to 27 Mbytes/sec in byte-wide mode, and up to 100 MHz in serial mode. All supported data types can be transmitted and/or received at this interface including plain Isochronous, asynchronous streams, asynchronous, DVB, DirecTV™, and DV type data.

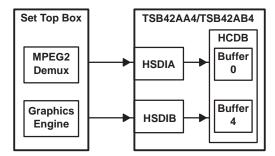

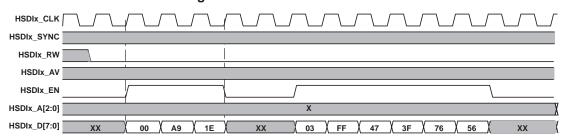

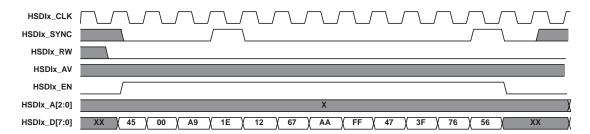

The high-speed data interface consists of two bidirectional, 8-bit data busses; HSDI ports A and B. Each bus has a corresponding 3-bit address bus used to select the internal FIFO that is to be written or read. The address bus is only used in multistream mode. HSDIA\_A[2:0] determine the FIFO accessed by HSDI port A, and HSDIB\_A[2:0] determine the FIFO accessed by HSDI port B. Each port has its own read and write control signals. Figure 3–7 shows the interface signals for each port. In general, the HSDI is a fully bidirectional interface.

The HSDI has two stream modes: single stream and multistream. In single stream mode, each HSDI port can only be connected to a maximum of one transmit buffer and one receive buffer. The HSDI accesses the buffers based on the HSDIx\_RW signal.

In multistream mode, each HSDI port can be connected to multiple transmit or receive buffers. The HSDI determines which buffer to access by decoding the HSDIx\_A[2:0] signals. The HSDIx\_RW must be used to determine the interface direction.

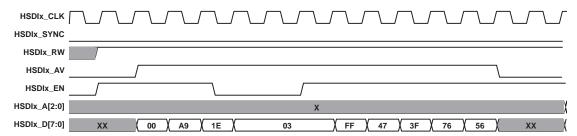

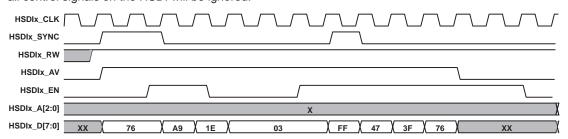

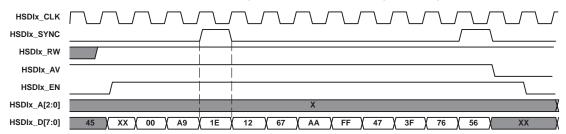

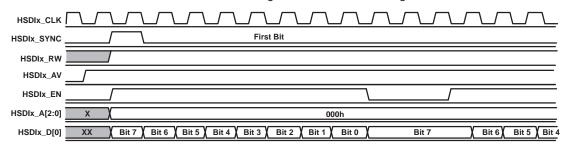

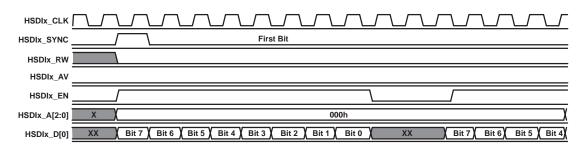

The HSDI supports three synchronization modes: Mode A, Mode B and Mode C. The sync mode defines how the HSDIx\_Sync signal will be used to determine packet boundaries on transmit and receive. The HSDIx\_Sync signal is input on transmit and output on receive.

The HSDIx\_EN signal is an input used on transmit to indicate valid data. Data is not written to transmit buffers unless the HSDIx\_EN signal is active. HSDIx\_EN is also an input on receive to indicate the application is ready to receive the data. No data is received to the application until the HSDIx\_EN signal is active.

The HSDIx\_AV signal is an output used to indicate when data is available for reading. This signal is active once one cell of data is available in the receive buffer. For data types that use time stamp based release, the HSDIx\_AV signal will be activated only after the timestamp matches the cycle timer. The signal is not used in transmit mode.

The HSDIx\_RW signal is used to indicate the direction of the HSDIx. In multistream mode, the HSDIx\_RW is used with the HSDIx\_A[2:0] signals to determine the buffer and the direction of the access. In single stream mode, the HSDIx\_RW signal is used to select the fixed transmit or receive buffer.

All control signals are programmable in their active level (active high or active low). The default is active high. The endianess of the byte stacking operation is programmable to either big (default) or little endian independently for transmit and receive mode.

Figure 3–13. High-Speed Data Interface Table 3–5. HSDIx\_A[2:0] Bus Encoding Values

| HSDx_A[2:0] | MEANING       |

|-------------|---------------|

| 000         | HSDI Buffer 0 |

| 001         | HSDI Buffer 1 |

| 010         | HSDI Buffer 2 |

| 011         | HSDI Buffer 3 |

| 100         | HSDI Buffer 4 |

| 101         | HSDI Buffer 5 |

| 110         | HSDI Buffer 6 |

| 111         | HSDI Buffer 7 |

#### 3.2.1 Data Bus Modes

The HSDI is designed to support the widest range of applications and available MPEG2 transport demux devices. The HSDI provides two separate databus modes to address this concern: the byte wide mode and the serial mode.

#### 3.2.1.1 Byte Wide Mode (default mode)

In byte wide mode, the full HSDIx\_D[7:0] bus is used to input or output data to the HSDI ports. HSDIx\_D[7] is the most significant bit. This is the default mode for each HSDI port.

#### 3.2.1.2 Serial Mode

In serial mode the HSDIx\_D[0] is used as a 1-bit wide mode input/output. This mode is selected using a control bit in the CFR.

The HSDIx\_SYNC signal marks the packet boundaries on a bit basis. The HSDIx\_EN signal should only be asserted on byte boundaries in either byte wide or serial mode.

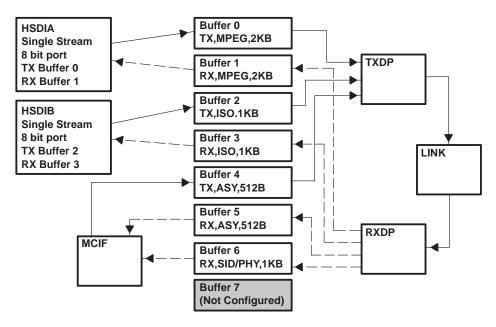

## 3.2.2 Stream Modes

The HSDI ports allow the user to either access multiple buffers from each HSDI port or to program the port to only support fixed buffers to simplify the control signals needed in the application. The two modes are multistream mode and single-stream mode (default).

## 3.2.2.1 Multistream Mode

Multistream mode supports all data types.

In *multistream* mode multiple data streams can be routed through a single *high-speed data interface* into different internal buffers. A three-bit buffer address is externally supplied on the *HSDIx\_A[2:0] pins*. For both transmit and receive operations, this address is synchronous to the eight-bit *HSDIx\_D[7:0]*. This address determines which buffer is accessed. The data must be written as complete packets. Different data types can not be mixed within packet boundaries.

The data streams on a single HSDI port can be of different nature. For example, an asynchronous data stream can be routed to buffer 0, and two isochronous streams can be routed to buffer 1 and 2 respectively. The stream type is indicated by the buffer that is being addressed and the associated configuration.

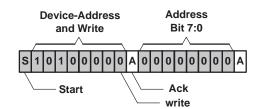

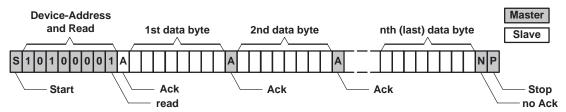

## 3.2.2.2 Single-Stream Mode (default mode)