64K ~ 8 ELECTRICALLY ERASABLE EPROM

### **GENERAL DESCRIPTION**

The W27LE520 is a high speed, low power Electrically Erasable and Programmable Read Only Memory organized as  $65,536 \times 8$  bits. It includes latches for the lower 8 address lines to multiplex with the 8 data lines. To cooperate with the MCU, this device could save the external TTL component, also cost and space. It requires only one supply in the range of 3.0V to 3.6V or 4.5V to 5.5V in normal read mode. The W27LE520 provides an electrical chip erase function. It will be a great convenient when you need to change/update the contents in the device.

### **FEATURES**

- High speed access time: 70/90 nS (max.)

- Read operating current: 8/20 mA (max.)

- Erase/Programming operating current 30 mA (max.)

- Standby current: 20/100 μA (max.)

- Unregulated battery power supply range, 3.0V to 3.6V and 4.5V to 5.5V

- +13V erase and programming voltage

### **PIN CONFIGURATIONS**

| A10 [    | 1 0        | 20   A8  |

|----------|------------|----------|

| A12 ]    | 2          | 19   AD1 |

| A14 [    | 3          | 18   AD3 |

| ALE ]    | 4          | 17   AD5 |

| VDD [    | 5 TSSOP    | 16   AD7 |

| OE/VPP ] | 6 Top View | 15   GND |

| A15 ]    | 7          | 14   AD6 |

| A13 ]    | 8          | 13   AD4 |

| A11 ]    | 9          | 12   AD2 |

| A9 ]     | 10         | 11   AD0 |

|          |            |          |

| OE/VPP   | 1 O        | 20   VDD |

| A15      | 2          | 19   ALE |

| A13      | 3          | 18   A14 |

| A11      | 4          | 17   A12 |

| A9       | 5 SOP      | 16   A10 |

| AD0      | 6 Top View | 15   A8  |

| AD2      | 7          | 14   AD1 |

| AD4      | 8          | 13   AD3 |

| AD6      | 9          | 12   AD5 |

| GND      | 10         | 11   AD7 |

- High Reliability CMOS Technology

- 2K V ESD Protection

- 200 mA Latchup Immunity

- Fully static operation

- All inputs and outputs directly LVTTL/CMOS compatible

- Three-state outputs

- Available packages: 20-pin TSSOP and 20-pin SOP

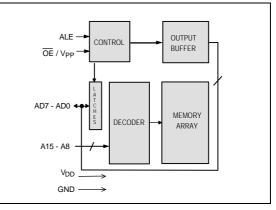

### **BLOCK DIAGRAM**

#### **PIN DESCRIPTION**

| SYMBOL  | DESCRIPTION                                    |

|---------|------------------------------------------------|

| AD0–AD7 | Address/Data Inputs/Outputs                    |

| A8–A15  | Address Inputs                                 |

| ALE     | Address Latch Enable                           |

| OE/Vpp  | Output Enable, Program/Erase<br>Supply Voltage |

| Vdd     | Power Supply                                   |

| GND     | Ground                                         |

## FUNCTIONAL DESCRIPTION

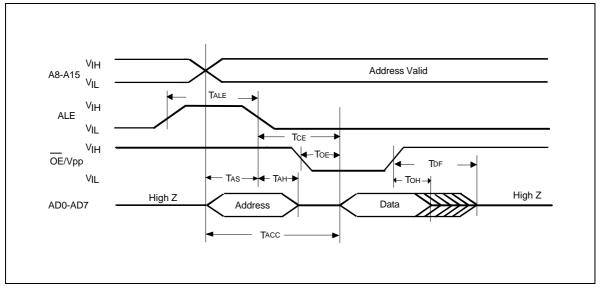

#### **Read Mode**

Unlike conventional UVEPROMs, which has  $\overline{CE}$  and  $\overline{OE}$  two control functions, the W27LE520 has one  $\overline{OE}/VPP$  and one ALE (address\_latch\_enable) control functions. The ALE makes lower address A[7:0] to be latched in the chip when it goes from high to low, so that the same bus can be used to output data during read mode. i.e. lower address A[7:0] and data bus DQ[7:0] are multiplexed.  $\overline{OE}/VPP$  controls the output buffer to gate data to the output pins. When addresses are stable, the address access time (TACC) is equal to the delay from ALE to output (TCE), and data are available at the outputs TOE after the falling edge of  $\overline{OE}/VPP$ , if TACC and TCE timings are met.

#### **Erase Mode**

The erase operation is the only way to change data from "0" to "1." Unlike conventional UVEPROMs, which use ultraviolet light to erase the contents of the entire chip (a procedure that requires up to half an hour), the W27LE520 uses electrical erasure. Generally, the chip can be erased within 100 mS by using an EPROM writer with a special erase algorithm.

There are two ways to enter Erase mode. One is to raise  $\overline{OE}/VPP$  to VPE (13V), VDD = VDE (6.5V), A9 = VHH (13V), A10 = high A8&A11 = low, and all other address pins include AD[7:0] keep at fixed low or high. Pulsing ALE high starts the erase operation. The other way is somewhat like flash, by programming two consecutive commands into the device and then enter Erase mode. The two commands are loading Data = AA(hex) to Addr. = 5555(hex) and Data = 10(hex) to Addr. = 2AAA(hex). Be careful to note that the ALE pulse widths of these two commands are different: One is 50 µS, while the other is 100 mS. Please refer to the Smart Erase Algorithm 1 & 2.

#### **Erase Verify Mode**

The device will enter the Erase Verify Mode automatically after Erase Mode. Only power down the device can force the device enter Normal Read Mode again.

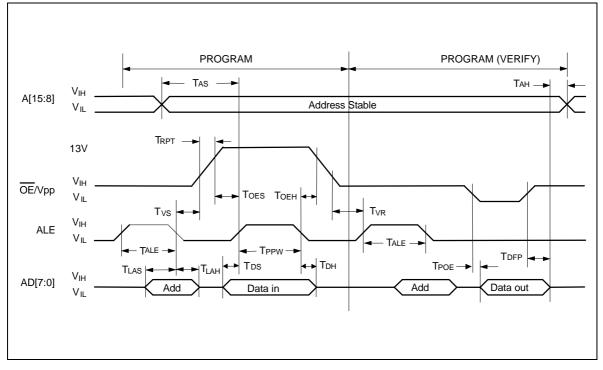

#### **Program Mode**

Programming is the only way to change cell data from "1" to "0." The program mode is entered when  $\overline{OE}/VPP$  is raised to VPP (13V), VDD = VDP (6.5V), the address pins equal the desired addresses, and the input pins equal the desired inputs. Pulsing ALE high starts the programming operation.

#### **Program Verify Mode**

The device will enter the Program Verify Mode automatically after Program Mode. Only power down the device can force the device enter Normal Read Mode again.

#### **Erase/Program Inhibit**

Erase or program inhibit mode allows parallel erasing or programming of multiple chips with different data. When ALE low, erasing or programming of non-target chips is inhibited, so that except for the ALE and  $\overline{OE}/VPP$  pins, the W27LE520 may have common inputs.

#### Standby Mode

The standby mode significantly reduces VDD current. This mode is entered when ALE and  $\overline{OE}/VPP$  keep high. In standby mode, all outputs are in a high impedance state.

#### System Considerations

An EPROM's power switching characteristics require careful device decoupling. System designers are interested in three supply current issues: standby current levels (ISB), active current levels (IDD), and transient current peaks produced by the falling and rising edges of ALE Transient current magnitudes depend on the device output's capacitive and inductive loading. Proper decoupling capacitor selection will suppress transient voltage peaks. Each device should have a

0.1  $\mu$ F ceramic capacitor connected between its VDD and GND. This high frequency, low inherentinductance capacitor should be placed as close as possible to the device. Additionally, for every eight devices, a 4.7  $\mu$ F electrolytic capacitor should be placed at the array's power supply connection between VDD and GND. The bulk capacitor will overcome voltage slumps caused by PC board trace inductances.

## TABLE OF OPERATING MODES

(VPP = 13V, VPE = 13V, VHH = 12V, VDP = 6.5V, VDE = 6.5V, VDD = 3.3V or 5.0V, VDI = 5.0V, X = VIH or VIL)

| MODE                                |             |        | PIN                                              |     |         |

|-------------------------------------|-------------|--------|--------------------------------------------------|-----|---------|

|                                     | ALE         | OE/Vpp | OTHER ADDRESS                                    | Vdd | AD[7:0] |

| Address Latch Enable                | VIH         | Vін    | AIN                                              | Vdd | A[7:0]  |

| Read                                | VIL         | VIL    | AIN                                              | Vdd | DOUT    |

| Output Disable                      | VIL/<br>VIH | Vih    | Х                                                | Vdd | High Z  |

| Standby                             | Vih         | Vін    | Х                                                | Vdd | A[7:0]  |

| Program                             | VIH         | VPP    | AIN                                              | Vdp | DIN     |

| Erase 1                             | Vih         | Vpe    | A8&A11 = VIL, A9 = VPE,<br>A10 = VIH, Others = X | Vde | Х       |

| Erase 2                             | Vін         | VPE    | First command:<br>Addr. = 5555 (hex)             | Vde | AA(hex) |

|                                     |             |        | Second command:<br>Addr. = 2AAA (hex)            | Vde | 10(hex) |

| Product Identifier-<br>manufacturer | VIL         | VIL    | A8 = VIL, A9 = VHH, Others = X                   | Vdi | DA(Hex) |

| Product Identifier-device           | VIL         | VIL    | A8 = VIH, A9 = VHH, Others = X                   | Vdi | 1F(Hex) |

## **DC CHARACTERISTICS**

#### **Absolute Maximum Ratings**

| PARAMETER                                                                    | RATING        | UNIT |

|------------------------------------------------------------------------------|---------------|------|

| Ambient Temperature with Power Applied                                       | -55 to +125   | °C   |

| Storage Temperature                                                          | -65 to +150   | °C   |

| Voltage on all Pins with Respect to Ground Except<br>OE/VPP, A9 and VDD Pins | -2.0 to +7.0  | V    |

| Voltage on OE/VPP Pin with Respect to Ground                                 | -2.0 to +7.0  | V    |

| Voltage on A9 Pin with Respect to Ground                                     | -2.0 to +7.0  | V    |

| Voltage VDD Pin with Respect to Ground                                       | -2.0 to +14.0 | V    |

Notes:

1. Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.

2. Minimum voltage is -0.6V DC which may undershoot to -2.0V for pulses of less than 20 nS. Maximum output pin voltage is VDD +0.75V DC which may overshoot to +7.0V for pulses of less than 20 nS.

## **DC Erase Characteristics**

(TA = 25° C  $\pm$ 5° C, VDD = 6.5V  $\pm$ 0.25V)

| PARAMETER                                    | SYM.        | CONDITIONS                           |       | LIMIT | S       | UNIT |

|----------------------------------------------|-------------|--------------------------------------|-------|-------|---------|------|

|                                              |             |                                      | MIN.  | TYP.  | MAX.    |      |

| Input Load Current                           | LI          | VIN = VIL or VIH                     | -10   | -     | 10      | μA   |

| VDD Erase Current                            | ICP         | ALE = VIH, $\overline{OE}/VPP = VPE$ | -     | -     | 30      | mA   |

|                                              |             | A8 & A11 = VIL, A9 = VPE,            |       |       |         |      |

|                                              |             | A10 = VIH, Others = X                |       |       |         |      |

| VPP Erase Current                            | <b>I</b> PP | ALE = VIH, $\overline{OE}/VPP = VPE$ | -     | -     | 30      | mA   |

|                                              |             | A8 & A11 = VIL, A9 = VPE,            |       |       |         |      |

|                                              |             | A10 = VIH, Others = X                |       |       |         |      |

| Input Low Voltage                            | VIL         | -                                    | -0.3  | -     | 0.8     | V    |

| Input High Voltage                           | Vін         | -                                    | 2.4   | -     | VDD+0.3 | V    |

| Output Low Voltage<br>(Verify)               | Vol         | IOL = 2.1 mA                         | -     | -     | 0.45    | V    |

| Output High Voltage<br>(Verify)              | Vон         | Юн = -0.4 mA                         | 2.4   | -     | -       | -    |

| A9 SID Voltage                               |             | VDD = 5V ±10%                        | 11.5  | 12    | 12.5    | V    |

|                                              | Vнн         |                                      |       |       |         |      |

| A9 Erase Voltage                             | VPE         | -                                    | 12.75 | 13    | 13.25   | V    |

| VPP Erase Voltage                            | VPE         | -                                    | 12.75 | 13    | 13.25   | V    |

| VDD Supply Voltage<br>(Erase & Erase Verify) | Vde         | -                                    | 6.25  | 6.5   | 6.75    | V    |

Note: VDD must be applied simultaneously or before VPP and removed simultaneously or after VPP.

## CAPACITANCE

(VDD = 3.0V to 3.6V or 4.5V to 5.5V, TA = 25° C, f = 1 MHz)

| PARAMETER          | SYMBOL |           | MAX. | UNIT |

|--------------------|--------|-----------|------|------|

| Input Capacitance  | CIN    | VIN = 0V  | 6    | pF   |

| Output Capacitance | Соит   | Vout = 0V | 12   | pF   |

# **AC CHARACTERISTICS**

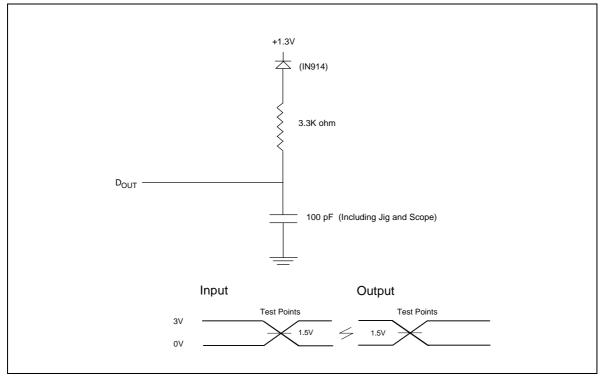

#### **AC Test Conditions**

| PARAMETER                               | CONDITIONS                                |

|-----------------------------------------|-------------------------------------------|

| Input Pulse Levels                      | 0V/3V                                     |

| Input Rise and Fall Times               | 10 nS                                     |

| Input and Output Timing Reference Level | 1.5V/1.5V                                 |

| Output Load                             | CL = 100  pF,  IOH/IOL = -0.4  mA/2.1  mA |

### AC Test Load and Waveforms

Publication Release Date: September 2000 Revision A2

- 5 -

# **READ OPERATION DC CHARACTERISTICS**

(VDD = 3.0V to 3.6V or 4.5V to 5.5V, TA = 0 to 70° C)

| PARAMETER                           | SYM.        | CO                    | NDITIONS                                       |      | LIMITS |             | UNIT |

|-------------------------------------|-------------|-----------------------|------------------------------------------------|------|--------|-------------|------|

|                                     |             |                       |                                                | MIN. | TYP.   | MAX.        |      |

| Input Load Current                  | <b> </b> LI | VIN = 0V to $VD$      | D                                              | -5   | -      | 5           | μA   |

| Output Leakage Current              | ILO         | VOUT = $0V$ to V      | VDD                                            | -5   | -      | 5           | μA   |

| Standby VDD Current<br>(CMOS input) | ISB         | VDD = 3.0V to<br>3.6V |                                                |      | -      | 20          | μA   |

|                                     |             | VDD = 4.5V to<br>5.5V | ±0.3V All others<br>inputs = GND/<br>VDD ±0.3V |      | -      | 100         |      |

| VDD Operating Current               | IDD         | VDD = 3.0V to<br>3.6V | ALE = VIL,<br>IOUT = 0 mA                      | -    | -      | 8           | mA   |

|                                     |             | VDD = 4.5V to<br>5.5V | f = 5 MHz                                      | -    | -      | 20          |      |

| Input Low Voltage                   | VIL         |                       | -                                              |      | -      | 0.8         | V    |

| Input High Voltage                  | Vih         |                       | -                                              | 2.0  | -      | Vdd<br>+0.3 | V    |

| Output Low Voltage                  | Vol         | IOL = 2.1 mA          |                                                | -    | -      | 0.4         | V    |

| Output High Voltage                 | Кон         | IOH = -0.4 mA         |                                                | 2.4  | -      | -           | V    |

# **READ OPERATION AC CHARACTERISTICS**

(VDD = 3.0V to 3.6V or 4.5V to 5.5V, TA = 0 to 70° C)

| PARAMETER                        | SYM. | W27LE520-70 |      | W27LE520-90 |      | UNIT |

|----------------------------------|------|-------------|------|-------------|------|------|

|                                  |      | MIN.        | MAX. | MIN.        | MAX. |      |

| Address Latch Enable Access Time | TCE  | -           | 70   | -           | 90   | nS   |

| Address Latch Enable Width       | TALE | 45          | -    | 45          | -    | nS   |

| Address Access Time              | TACC | -           | 70   | -           | 90   | nS   |

| Address Setup Time               | TAS  | 15          | -    | 15          | -    | nS   |

| Address Hold Time                | Тан  | 15          | -    | 15          | -    | nS   |

| Output Enable Access Time        | Τοε  | -           | 35   | -           | 35   | nS   |

| OE /VPP High to High-Z Output    | Tdf  | -           | 25   | -           | 25   | nS   |

| Output Hold from Address Change  | Тон  | 0           | -    | 0           | -    | nS   |

Note: VDD must be applied simultaneously or before VPP and removed simultaneously or after VPP.

## DC PROGRAMMING CHARACTERISTICS

(Vdd = 6.5V  $\pm 0.25$ V, Ta = 25° C  $\pm 5^{\circ}$  C)

| PARAMETER                    | SYM. | CONDITIONS       | LIMITS |      | UNIT     |    |

|------------------------------|------|------------------|--------|------|----------|----|

|                              |      |                  | MIN.   | TYP. | MAX.     |    |

| Input Load Current           | lu   | VIN = VIL or VIH | -10    | -    | 10       | μA |

| VDD Program Current          | ICP  | ALE = VIH,       | -      | -    | 30       | mA |

|                              |      | OE /VPP = VPP    |        |      |          |    |

| VPP Program Current          | IPP  | ALE = VIH,       | -      | -    | 30       | mA |

|                              |      | OE /VPP = VPP    |        |      |          |    |

| Input Low Voltage            | VIL  | -                | -0.3   | -    | 0.8      | V  |

| Input High Voltage           | Vін  | -                | 2.4    | -    | Vdd +0.5 | V  |

| Output Low Voltage (Verify)  | Vol  | IOL = 2.1 mA     | -      | -    | 0.45     | V  |

| Output High Voltage (Verify) | Vон  | Iон = -0.4 mA    | 2.4    | -    | -        | V  |

| A9 Silicon I.D. Voltage      | Vнн  | VDD = 5V ±10%    | 11.5   | 12.0 | 12.5     | V  |

| VPP Program Voltage          | Vpp  | -                | 12.75  | 13.0 | 13.25    | V  |

| VDD Supply Voltage (Program) | Vdp  | -                | 6.25   | 6.5  | 6.75     | V  |

# AC PROGRAMMING/ERASE CHARACTERISTICS

(VDD =  $6.5V \pm 0.25V$ , TA =  $25^{\circ} C \pm 5^{\circ} C$ )

| PARAMETER                                         | SYM.  |      | LIMITS |      | UNIT |

|---------------------------------------------------|-------|------|--------|------|------|

|                                                   |       | MIN. | TYP.   | MAX. |      |

| OE /VPP Pulse Rise Time                           | TPRT  | 50   | -      | -    | nS   |

| Address Latch Enable Width                        | TALE  | 500  | -      | -    | nS   |

| ALE Program Pulse Width                           | TPPW  | 47.5 | 50     | 52.5 | μS   |

| ALE Erase Pulse Width                             | Tepw  | 95   | 100    | 105  | mS   |

| ALE Erase Pulse Width 1                           | TEPW1 | 47.5 | 50     | 52.5 | μS   |

| ALE Erase Pulse Width 2                           | TEPW2 | 95   | 100    | 105  | mS   |

| Latched Address Setup Time                        | TLAS  | 100  | -      | -    | nS   |

| Latched Address Hold Time                         | TLAH  | 100  | -      | -    | nS   |

| Address Setup Time                                | TAS   | 2.0  | -      | -    | μS   |

| Address Hold Time                                 | Тан   | 0    | -      | -    | μS   |

| OE /VPP Setup Time                                | TOES  | 2.0  | -      | -    | μS   |

| OE /VPP Hold Time                                 | Тоен  | 2.0  | -      | -    | μS   |

| Data Setup Time                                   | TDS   | 2.0  | -      | -    | μS   |

| Data Hold Time                                    | Трн   | 2.0  | -      | -    | μS   |

| Data Valid from OE /VPP Low during Erase Verify   | TEOE  | -    | -      | 150  | nS   |

| Data Valid from OE /VPP Low during Program Verify | TPOE  | -    | -      | 150  | nS   |

| OE /VPP High to Output High Z                     | Tdfp  | 0    | -      | 130  | nS   |

| OE /VPP High Voltage Delay After ALE Low          | Tvs   | 2.0  | -      | -    | μS   |

| OE /VPP Recovery Time                             | TVR   | 2.0  | -      | -    | μS   |

Note: VDD must be applied simultaneously or before VPP and removed simultaneously or after VPP.

# TIMING WAVEFORMS

### AC Read Waveform

# **Programming Waveform**

#### Timing Waveforms, continued

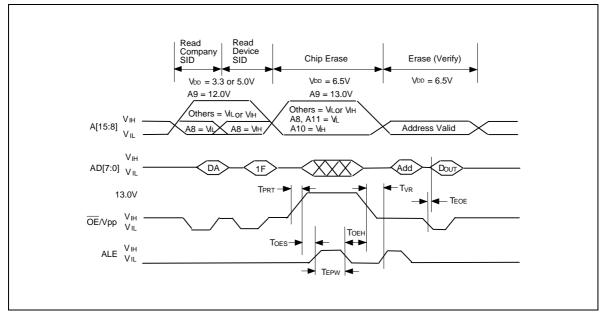

#### **Erase Waveform 1**

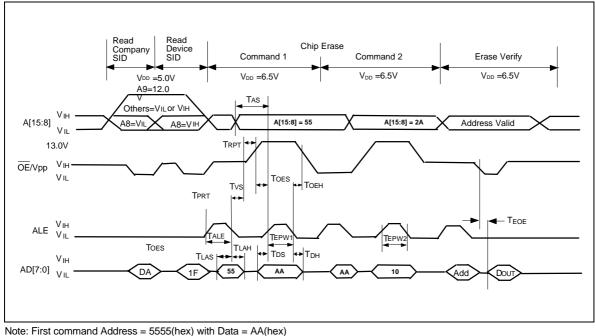

#### **Erase Waveform 2**

Second command Address = 5555(nex) with Data = AA(nex) Second command Address = 2AAA(hex) with Data = 10(hex)

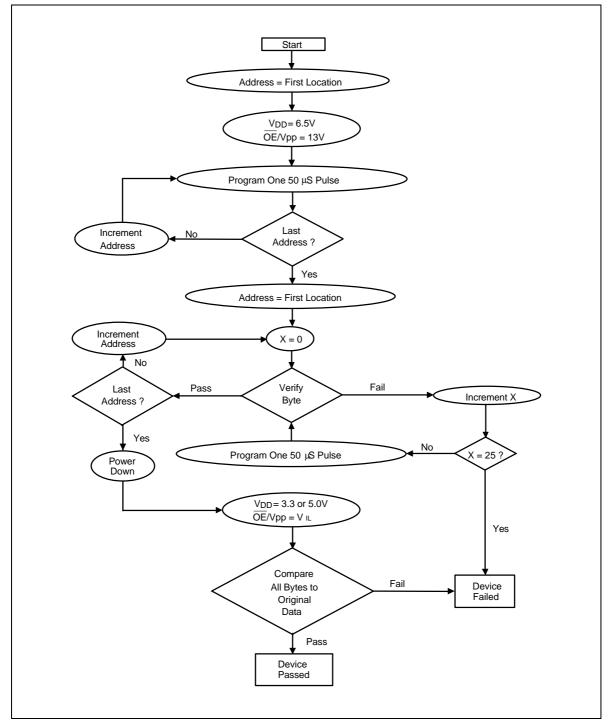

## **SMART PROGRAMMING ALGORITHM 1**

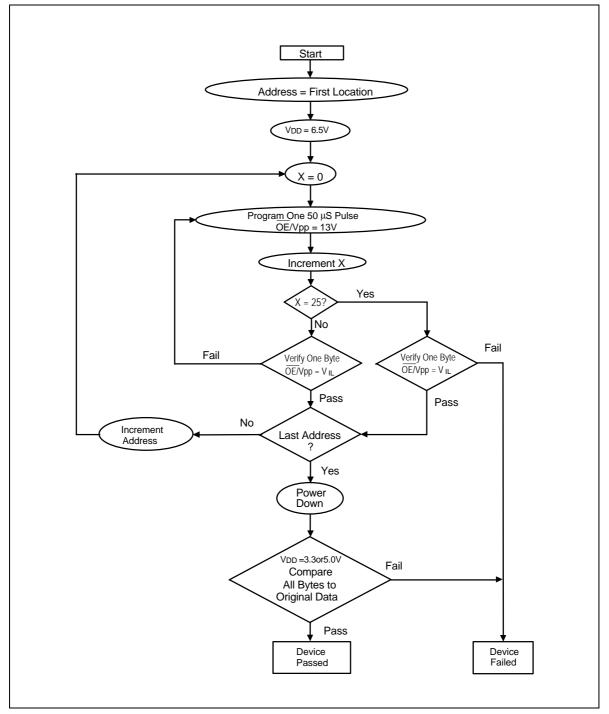

## **SMART PROGRAMMING ALGORITHM 2**

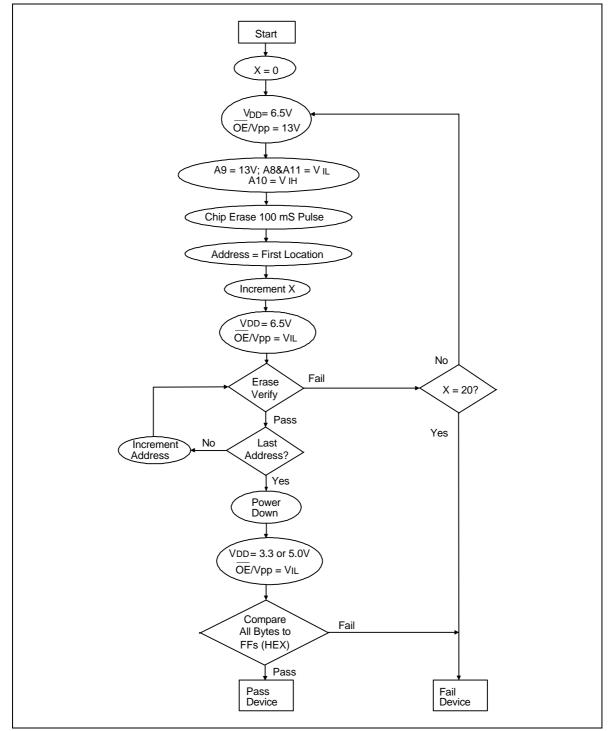

## **SMART ERASE ALGORITHM 1**

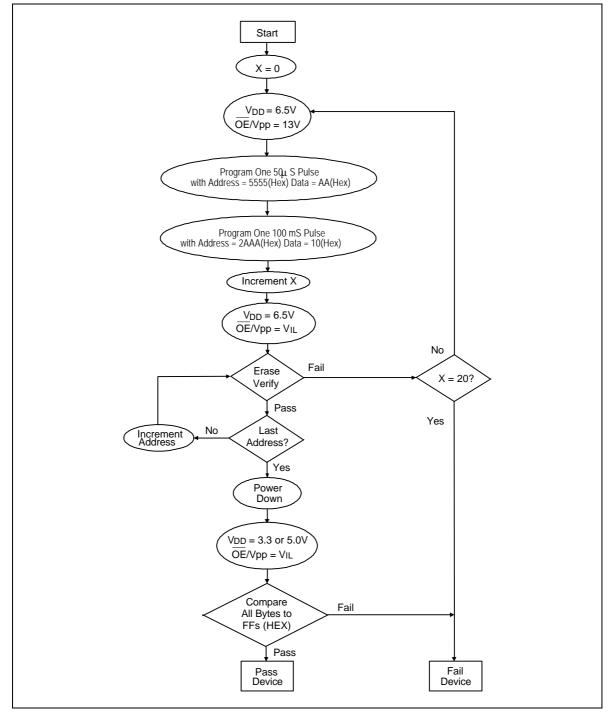

## **SMART ERASE ALGORITHM 2**

# **ORDERING INFORMATION**

| PART NO.      | ACCESS<br>TIME<br>(nS) | OPERATING<br>CURRENT<br>MAX. (mA) | STANDBY<br>CURRENT<br>MAX. (mA) | PACKAGE       |

|---------------|------------------------|-----------------------------------|---------------------------------|---------------|

| W27LE520W-70* | 70                     | 8/20                              | 20/100                          | 173 mil TSSOP |

| W27LE520W-90* | 90                     | 8/20                              | 20/100                          | 173 mil TSSOP |

| W27LE520S-70* | 70                     | 8/20                              | 20/100                          | 300 mil SOP   |

| W27LE520S-90* | 90                     | 8/20                              | 20/100                          | 300 mil SOP   |

Notes:

1. The Part No is preliminary and might be changed after project is consoled.

2. Winbond reserves the right to make changes to its products without prior notice.

3. Purchasers are responsible for performing appropriate quality assurance testing on products intended for use in applications where personal injury might occur as a consequence of product failure.

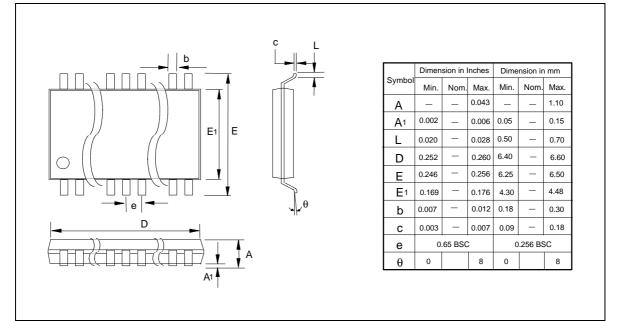

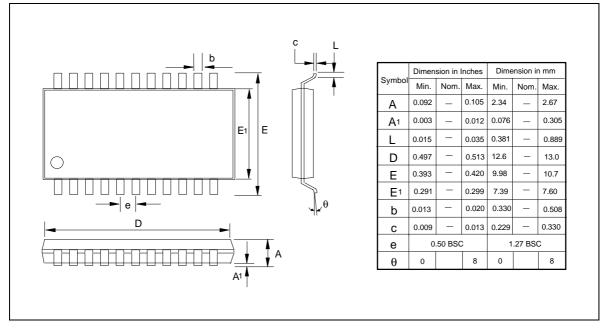

## PACKAGE DIMENSIONS

## 20-pin TSSOP

## 20-pin SOP

### **VERSION HISTORY**

| VERSION | DATE      | PAGE | DESCRIPTION                                 |

|---------|-----------|------|---------------------------------------------|

| A1      | Jun. 2000 | -    | Initial Issued                              |

| A2      | Sep. 2000 | 9    | Correct Erase Waveform                      |

|         |           | 3    | Modify Address Latch Enable Mode: X -> Ain; |

|         |           |      | Modify Output Disable Mode: VIL -> VIL/VIH; |

|         |           |      | Modify Standby Mode: Ain -> X;              |

|         |           |      | Typo Correction                             |

### Headquarters

No. 4, Creation Rd. III,UScience-Based Industrial Park,HHsinchu, TaiwanHTEL: 8863-577066HFAX: 886-3-5796096Hhttp://www.winbond.com.tw/Voice & Fax-on-demand: 8862-27197006

rk, No. 378 Kwun Tong Rd; Kowloon, Hong Kong TEL: 852-27513100 FAX: 852-27552064 / \$2-27197006 Winbond Electronics North America Corp. Winbond Memory Lab. Winbond Microelectronics Corp. Winbond Systems Lab. 2727 N. First Street, San Jose, CA 95134, U.S.A. TEL: 4089436666 FAX: 408-5441798

Taipei Office

11F, No. 115, Sec. 3, MinSheng East Rd.,

Taipei, Taiwan

TEL:

886-2-27190505

FAX:

886-2-27197502

Note: All data and specifications are subject to change withou t notice.

Winbond Electronics (H.K.) Ltd.

Unit 9-15, 22F, Millennium City,