# **WTS701**

# WINBOND SINGLE-CHIP TEXT-TO-SPEECH PROCESSOR

The information contained in this datasheet may be subject to change without notice. It is the responsibility of the customer to check the Winbond USA website (<a href="https://www.winbond-usa.com">www.winbond-usa.com</a>) periodically for the latest version of this document, and any Errata Sheets that may be generated between datasheet revisions.

## 1. GENERAL DESCRIPTION

The WTS701 is a high quality, fully integrated, single-chip Text-to-Speech solution that is ideal for use in applications such as automotive appliances, GPS/navigation systems, cellular phones and other portable products or accessories. The WTS701 product accepts ASCII (and Unicode for Mandarin) input via a SPI port and converts it to spoken audio via an analog output or digital CODEC output.

The WTS701 integrates a text processor, smoothing filter and multi-level memory storage array on a single-chip. Text-to-speech conversion is achieved by processing the incoming text into a phonetic representation that is then mapped to a corpus of naturally spoken word parts. The synthesis algorithm attempts to use the largest possible word unit in the appropriate context to maximize natural sounding speech quality. The speech units are stored uncompressed in a multi-level, non-volatile analog storage array to provide the highest sound quality to density trade-off. This unique, single-chip solution is made possible through Winbond's patented multilevel storage technology. Voice and audio signals are stored directly into solid-state memory in their natural, uncompressed form, providing superior quality voice reproduction.

The chip can be programmed through the SPI port, allowing downloading of different languages and speaker databases

#### 2. FEATURES

## Fully Integrated Solution

- Single-chip compact text-to-speech translation

- No algorithm development required

- Selectable digital and analog audio output

- Simple SPI interface

- Reprogrammable solution enables loading different voice or language

## Text-To-Speech Algorithm Characteristics

- High quality speech synthesis using speech element concatenation

- Winbond's standard 100-year speech retention

- Audio stored as uncompressed analog waveform industry's highest quality and most natural sounding

## Easy to Use and Control

- Real time conversion for streaming text

- General text preprocessing and normalization

- User customization for special characters such as SMS icons and chat emoticons

- User customization for application specific abbreviations

## Language Support

- Support U.S. English and Mandarin (Beijing dialect)

- Other languages in development or in planning

### Device Management

- Accepts ASCII or Unicode streaming text

- 256-byte text buffer

- Playback of Phonetic Alphabet

- Variable speed playback

- Control of pitch change

- Supports Power Down mode.

- Supports Pause and Resume, Stop and Finish text conversion commands

## Peripheral Control

- 16-bit linear PCM slave interface output support

- SPI serial port for control commands and status report to system's host controller

- Hardware handshake control signals

- Analog audio output with 8Ω speaker driver and digital volume control

- Analog audio input (AUXIN) for driving external audio to the speaker

## Low Power Consumption

- +2.7 to +3.3V (V<sub>CC</sub>) Supply Voltage

- Operating Current:

$I_{CC Convert} = 35 \text{ mA (typical)}$

Standby Current:

$I_{SB} < 1\mu A$  (typical)

# • Device Characteristics

- Available in 56-lead TSOP package

- Industrial temperature range (-40C to +85C)

- 3V/5V logic tolerance

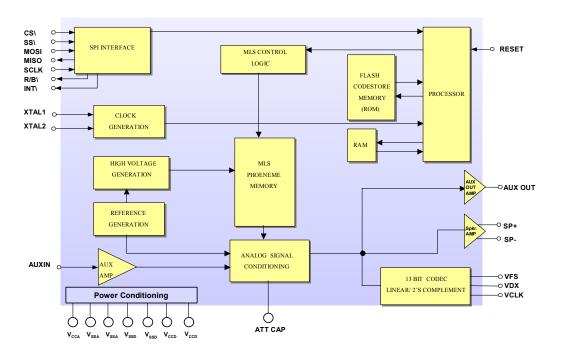

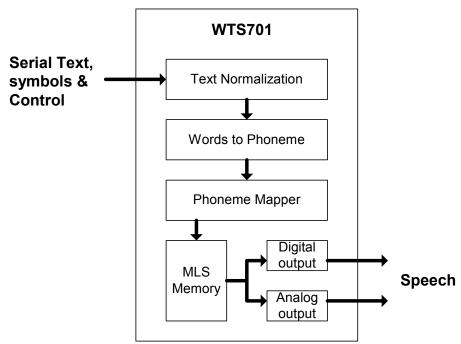

# 3. BLOCK DIAGRAM

## 3.1 WTS701 BLOCK DIAGRAM

Figure 1. WTS701 Block Diagram.

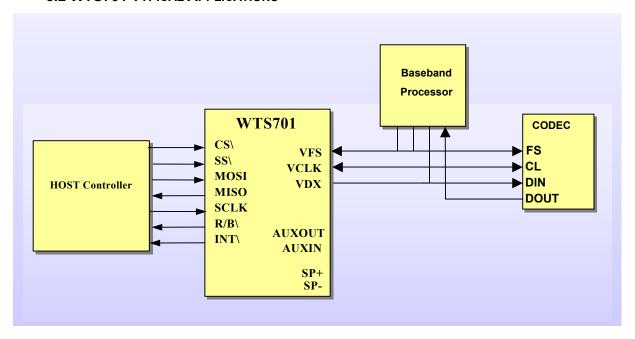

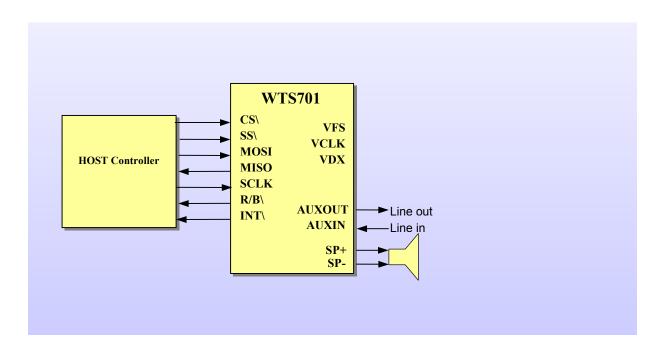

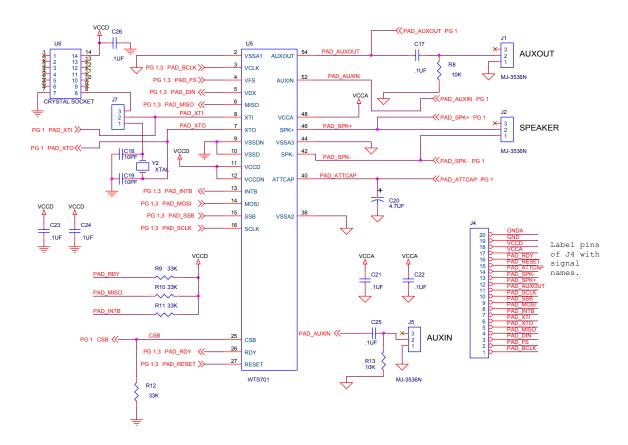

# 3.2 WTS701 TYPICAL APPLICATIONS

Figure 2. WTS701 Configuration for Digital (CODEC) Environment.

Figure 3. WTS701 Configuration for Analog Environment

# **WTS701**

| 4. TABLE OF CONTENTS                    |    |

|-----------------------------------------|----|

| 1. GENERAL DESCRIPTION                  | 2  |

| 2. FEATURES                             | 3  |

| 3. BLOCK DIAGRAM                        | 4  |

| 3.1. WTS701 Block Diagram               | 4  |

| 3.2. WTS701 Typical Applications        | 5  |

| 4. TABLE OF CONTENTS                    | 6  |

| 5. PIN CONFIGURATION                    | 8  |

| 6. PIN DESCRIPTION                      | 9  |

| 7. FUNCTIONAL DESCRIPTION               | 11 |

| 7.1. Text-to-Speech Mechanism           | 12 |

| 7.1.1. Text Normalization               | 12 |

| 7.1.2. Words-to-Phoneme conversation    | 12 |

| 7.1.3. Speech-element Mapping           | 12 |

| 7.2. Physical Interface                 | 13 |

| 7.2.1. Clocking                         | 13 |

| 7.2.2. Power Down Mode                  | 14 |

| 7.2.3. Power and Grounding              | 14 |

| 7.2.4. SPI Interface                    | 15 |

| 7.2.5. Flow Control Interface           | 16 |

| 7.2.6. The Codec Interface              | 16 |

| 7.2.7. The Analog Interface             | 17 |

| 7.2.8. Resetting                        | 18 |

| 7.3. Communication Protocol             | 19 |

| 7.3.1. Command Classes                  | 20 |

| 7.3.2. Status Register                  | 21 |

| 7.3.3. Interrupt Handler                | 22 |

| 7.3.4. BCNT – Byte Count Register       | 23 |

| 7.3.5. Command Acceptance               | 23 |

| 7.3.6. Data Acceptance                  | 23 |

| 7.4. Commands Overview                  | 23 |

| 7.4.1. Commands Description             | 26 |

| 7.4.2 Illegal Commands                  | 37 |

| 7.4.3. Configuration Registers          |    |

| 7.4.4. System Operation                 | 41 |

| 7.4.5. Initialization and Configuration | 43 |

# **WTS701**

| 7.4.6. Converting Text                                          | 43 |

|-----------------------------------------------------------------|----|

| 7.5. SPI Interface                                              | 45 |

| 7.5.1. SPI Transactions                                         | 45 |

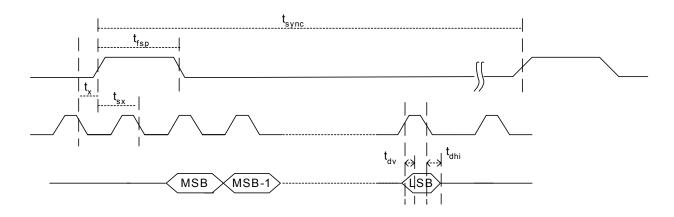

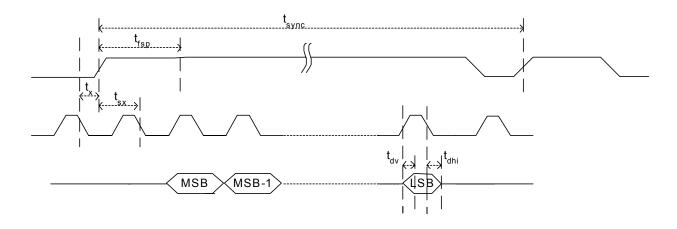

| 7.6. CODEC Interface                                            | 48 |

| 7.7. Phonetic Alphabet Playback                                 | 51 |

| 7.8. Customizing Abbreviations                                  | 53 |

| 7.8.1. Abbreviation Data Format                                 | 54 |

| 7.8.2. Abbreviation Table Format                                | 54 |

| 7.8.3. Command Execution                                        | 55 |

| 7.9. Device Programming                                         | 55 |

| 7.10. Text-to-Speech Processor Commands – Quick Reference Table | 56 |

| 7.10.1. Text Input Format                                       | 61 |

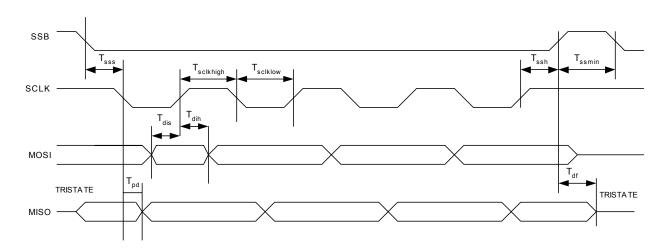

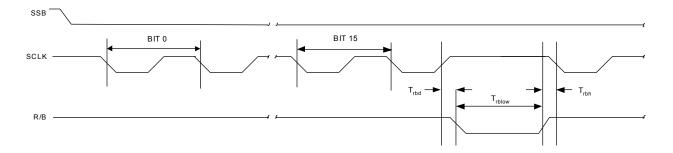

| 8. TIMING WAVEFORMS                                             | 63 |

| 8.1. SPI Timing Diagram                                         | 63 |

| 8.2. CODEC Timing Diagrams                                      | 65 |

| 9. ABSOLUTE MAXIMUM RATINGS                                     | 67 |

| 10. ELECTRICAL CHARACTERISTICS                                  | 68 |

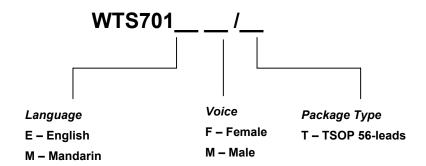

| 11. TYPICAL APPLICATION CIRCUIT                                 | 71 |

| 12. PACKAGE DIMENSIONS                                          | 72 |

| 13. ORDERING INFORMATION                                        | 73 |

| 14. VERSION HISTORY                                             | 73 |

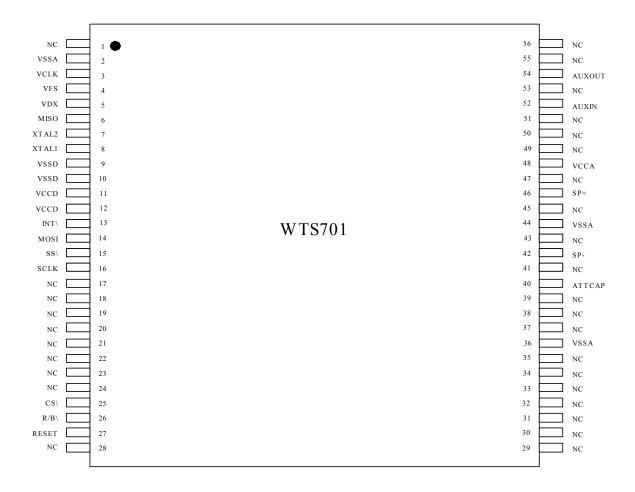

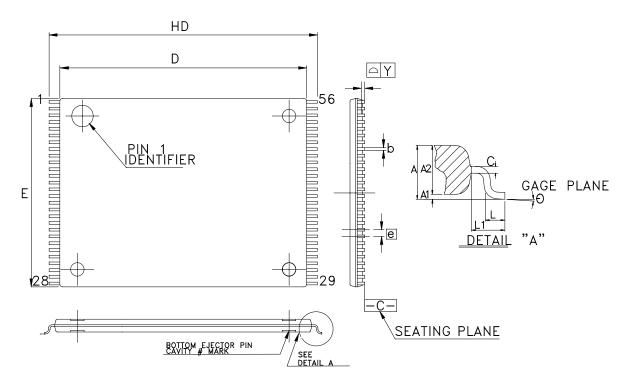

# 5. PIN CONFIGURATION

The following sections detail the pins of the WTS701 processor.

<u>Table 1</u> shows all the pins and the signals that use them in different configurations. It also shows the type and direction of each signal. <u>Figure 4</u> shows the physical pin out of the 56-pin TSOP package.

Figure 4. 56-pin TSOP Package Connection Diagram.

# 6. PIN DESCRIPTION

Table 1. WTS701 Pin Signal Assignment.

| PIN NO. | SYMBOL | I/O | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13      | INT\   | 0   | Interrupt Output; an open drain output that indicates that the device wishes an interrupt service. The device can request an interrupt when it finishes an operation or needs more data to process. Under what conditions the device generates an interrupt can be configured through the user configuration registers. This pin remains LOW until a Read Interrupt command is executed. |

| 26      | R/B\   | 0   | Ready/busy signal; This pin defaults HIGH indicating the device is ready for data transfer. The pin is driven LOW to handshake a pause in SPI data transfer.                                                                                                                                                                                                                             |

| 7       | XTAL2  | 0   | CRYSTAL 2: This is the crystal oscillator output. It is the inversion of XTAL1.                                                                                                                                                                                                                                                                                                          |

| 8       | XTAL1  | _   | CRYSTAL 1: This is the crystal oscillator input. This pin may be driven by an external clock. The clock to the WTS701 processor is configured by a clock configuration register, which is set by the host processor during the initialization phase.                                                                                                                                     |

| 15      | SS\    | 1   | SPI Slave Select input. This is an active LOW input used to select the device to respond to an SPI transaction.                                                                                                                                                                                                                                                                          |

| 16      | SCLK   | I   | SPI Serial clock input.                                                                                                                                                                                                                                                                                                                                                                  |

| 6       | MISO   | 0   | SPI Master In, Slave Out pin. Serial data line used to communicate with SPI master. Pin is tri-state when SS\=1.                                                                                                                                                                                                                                                                         |

| 14      | MOSI   | I   | SPI <b>M</b> aster <b>O</b> ut, <b>S</b> lave <b>I</b> n. Serial data input from Master                                                                                                                                                                                                                                                                                                  |

| 25      | CS\    |     | Chip Select (active LOW) Pin must be LOW to access WTS701 device.                                                                                                                                                                                                                                                                                                                        |

| 27      | RESET  | Ι   | Global reset signal.                                                                                                                                                                                                                                                                                                                                                                     |

| 3       | VCLK   |     | CODEC master clock                                                                                                                                                                                                                                                                                                                                                                       |

| 4       | VFS    | I   | CODEC frame synchronization signal                                                                                                                                                                                                                                                                                                                                                       |

| 5       | VDX    | 0   | CODEC data output. This pin puts data out in the linear PCM unsigned or 2's complement format. It is tri-stated until the user requests a CONVERT operation.                                                                                                                                                                                                                             |

| 52      | AUXIN  | I   | Analog input pin. This pin should be capacitively coupled.                                                                                                                                                                                                                                                                                                                               |

| 54      | AUXOUT | 0   | Analog Output for single ended output from the device.                                                                                                                                                                                                                                                                                                                                   |

| 46      | SP+    | 0   | Differential Positive Speaker Driver Output.                                                                                                                                                                                                                                                                                                                                             |

| 42      | SP-    | 0   | Differential Negative Speaker Driver Output.                                                                                                                                                                                                                                                                                                                                             |

# **WTS701**

| 40                                                                     | ATTCAP | I/O | AutoMute Capacitor Pin. Should have a 4.7uF capacitor to VSSA.                                                                                                                      |

|------------------------------------------------------------------------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11,12                                                                  | VCCD   | Р   | Positive Digital Supply pin. These pins carry noise generated by internal clocks in the chip. They must be carefully bypassed to Digital Ground to ensure correct device operation. |

| 9,10                                                                   | VSSD   | G   | Digital Ground pin.                                                                                                                                                                 |

| 2,36,44                                                                | VSSA   | G   | Analog Ground pins.                                                                                                                                                                 |

| 48                                                                     | VCCA   | Р   | Positive Analog Supply pin. This pin supplies the LOW level audio sections of the device. It should be carefully bypassed to Analog Ground to ensure correct device operation.      |

| 1,17-<br>24,28-<br>35,37-<br>39,41,43,<br>45,47,49-<br>51,53,55-<br>56 | NC     |     | Not Connected – must be floating.                                                                                                                                                   |

Note: TYPE I:Input, O:Output, I/O bi-directional, P:Power, G:Ground

#### 7. FUNCTIONAL DESCRIPTION

As a real System-On-Chip solution, the WTS701 performs the overall control functions for host controller and text-to-speech processing.

The WTS701 system architecture consists of the following functions:

- Serial interface to monitor the SPI port and interpret commands and data

- Text normalization module to pre-process incoming text into pronounceable words

- Words to phoneme translator, which converts incoming text to phoneme codes

- Phoneme mapping module that maps incoming phonemes to words, sub-words, syllables or phonemes present in the MLS memory

- Volume and speed adjustments

- Digital and analog output blocks for off-chip usage

The WTS701 system performs text-to-speech synthesis based on concatenative samples. The units for concatenation can vary from whole words down to phoneme units. The convention is that the larger the sub-word unit used for synthesis the higher the quality of the speech output. A corpus of pre-recorded words is stored in Winbond's patented multilevel storage (MLS) memory and a mapping of the various sub-word parts is held in a lookup table. The speech creation is achieved by concatenation of these speech elements to produce words. The system process flow is shown in Figure 5.

Figure 5. WTS701 System Process Flow.

#### 7.1 TEXT-TO-SPEECH MECHANISM

The text to speech component of the system consists of three principal blocks:

- Text normalization

- Word to phoneme conversion

- Phoneme mapping

#### 7.1.1 Text Normalization

Text normalization involves the translation of incoming text into pronounceable words. It includes such functions as expanding abbreviations and translating numeric strings to spoken words. It involves a certain amount of context processing to determine correct spoken form.

In addition, the WTS701 looks into abbreviation list stored in the device's internal memory and converts acronyms, abbreviations or special characters (such as Instant Messaging icons or emoticons) into the appropriate text representation.

The default abbreviation list supported by the WTS701 is a general one that can be modified by the user to match the domain that the text is being loaded from. This enables a flexibility of adding abbreviation specifically for the text either by the developer or even the end user to best customize the product for its preferences. Instant Messaging or Short Messages Service (SMS) unique characters are supported through this functionality as well, defining the icon ASCII/Unicode text and its replacement. The default abbreviation list supported is described in the specific language release letter.

#### 7.1.2 Words-to-Phoneme conversion

Once the data stream has been translated to pronounceable words, the system next determines how to pronounce them. This function is obviously highly language dependent. For a language such as English it is impossible to break this task down to a set of definitive rules. The task is achieved by a combination of rule based processing together with exception processing.

# 7.1.3 Phoneme Mapping

This algorithm maps phoneme strings into the MLS phonetic inventory. This task falls into two portions. First, the word must be split into sub-word portions. This splitting must be done at appropriate phonetic boundaries to achieve high quality concatenation. Once a sub-word unit is determined, the inventory is searched to determine if a match is present. A matching weight is assigned to each match depending on how closely the phonetic context matches. Each sub-word has a left and right side context to match as well as the phoneme string itself. If no suitable match is found

in the inventory, then the sub-word is further split in a tree like manner until a match is found. The splitting tree is processed from left to right and each time a successful match occurs the address and duration of the match in the corpus is placed in a queue of phonetic parts to be played out the audio interface.

### 7.2 PHYSICAL INTERFACE

The following sections describe the physical pin properties and the timing associated with the physical interface to the device. Note that all input pins are 3V and 5V tolerant, except for the CS\ signal which is only 3V tolerant.

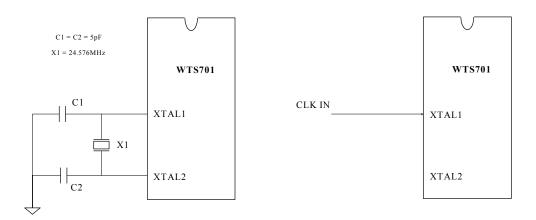

# 7.2.1 Clocking

The WTS701 processor can receive its clock from either external clock source or crystal oscillator

The XTAL1 and XTAL2 pins provide the crystal interface to the device. The clock to the WTS701 processor is configured by a clock configuration register, which must be set by the host processor during the initialization phase. Figure 6 below shows how to connect the WTS701 to a crystal oscillator. An external clock can be connected to the WTS701 providing the clock source for the system, as shown in Figure 6.

Figure 6. Clock Generation.

#### 7.2.2 Power Down Mode

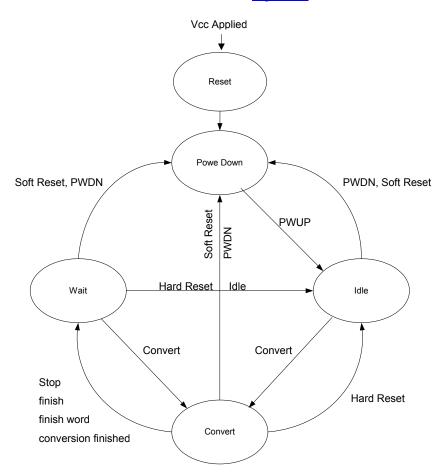

Upon application of power, the WTS701 will enter the RESET state and then be in a POWER DOWN state. In the POWER DOWN mode, only Class0 SPI commands are valid. (See subsection <u>7.3.1</u>). The Power Down status of the device can be determined with a RDST (Read Status) command, specified by the RDY bit in STATUS BYTE 0.

Issuing the PWDN (Power Down) command to the WTS701 processor will return the processor to the POWER DOWN mode. In POWER DOWN mode the external crystal oscillator is shut off and the processor is deactivated. POWER DOWN mode is exited by issuing a PWUP (Power Up) command to the WTS701. The PWUP command should be preceded by a SCLC (Set Clock) command to ensure correct clock configuration.

## 7.2.3 Power and Grounding

The WTS701 can operate over 2.7V to 3.3V supply voltage range. The power supply and ground pins ( $V_{CCA}$ ,  $V_{CCD}$ ,  $V_{SSA}$ ,  $V_{SSD}$ ) should be carefully bypassed as close to the chip as possible to ensure high quality audio. In addition, ATTCAP pin should have a 4.7  $\mu$ F capacitor connected to ground. This pin must not be left floating. The pins that are marked as NC (Not Connected), should be left floating.

## V<sub>CCA</sub>, V<sub>CCD</sub> (Voltage Inputs)

To minimize noise, the analog and digital circuits in the WTS701 device use separate power busses. These +3.0 V busses lead to separate pins. For optimal noise immunity, tie the  $V_{CCD}$  pins together as close as possible and decouple both supplies as near to the package as possible.

## V<sub>SSA</sub>, V<sub>SSD</sub> (Ground Inputs)

The WTS701 series utilizes separate analog and digital ground busses. The analog ground ( $V_{SSA}$ ) pins should be tied together as close to the package as possible and connected through a low-impedance path to power supply ground. The digital ground ( $V_{SSD}$ ) pin should be connected through a separate low-impedance path to power supply ground. These ground paths should be large enough to ensure that the impedance between the  $V_{SSA}$  pins and the  $V_{SSD}$  pin is less than  $3\Omega$ . The backside of the die is connected to  $V_{SSD}$  through the substrate resistance.

# NC (Not Connect)

These pins should not be connected to the board at any time. Connection of these pins to any signal, ground or  $V_{CC}$  may result in incorrect device behavior or cause damage to the device.

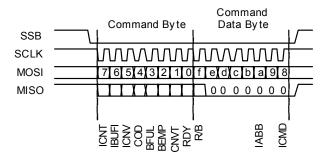

#### 7.2.4 SPI Interface

Communications with the WTS701 is conducted over the SPI serial communications port. The device responds to a command when the Chip Select signal (CS\) is LOW and addressed by an active LOW signal on the SS\(Slave Select) pin. Under this condition, it accepts data on the MOSI input, which is clocked in on rising edges of the serial clock (SCLK) signal. Concurrently, valid data from the WTS701 device to the bus master is available on MISO for the HIGH period of SCLK. The protocol implemented on the WTS701 defines that the first two bytes of data sent in an SPI transaction is a command word. A transaction is defined as the SPI transfers conducted while SS\ is LOW, the transaction ends when SS\ returns HIGH. List of available commands can be found in subsection 7.10 (Text-To-Speech Processor Commands Quick Reference Table).

All Input pins are 3V and 5V tolerant, except for the CS\ signal which is only 3V tolerant.

The following is a description of the WTS701 SPI interface signals:

## SCLK (Serial Clock)

The Serial Clock line is a digital input. It is driven by the SPI master and controls the timing of the data exchanged over the SPI data lines, MOSI and MISO. The maximum frequency of the clock rate for this pin is 5MHz.

#### SS\ (Slave Select)

The Slave Select line is an active LOW digital input. It is driven by the SPI master and acts as a chip select line. The device only responds to SPI transactions when this line is selected (LOW) and then raised HIGH after SPI communication ends.

#### CS\ (Chip Select)

The Chip Select line is an active LOW digital input. It can be driven by the host controller to enable SPI transactions to the device. Normally this pin is tied LOW unless more than one device is to share the same SS\ signal.

## MOSI (Master Out, Slave In)

The MOSI line is a digital input. MOSI is driven by the SPI master. It provides data transfer from the master to the slave.

#### MISO (Master In, Slave Out)

The MISO line is a digital output. When SS\ is HIGH, this pin is tri-state. When SS\ is LOW, MISO is driven by the device. It provides serial data transfer from the slave to the master.

#### 7.2.5 Flow Control Interface

In addition to the SPI interface, the WTS701 has two control lines to facilitate data transfer and host communications. The INT\ (interrupt) pin is used by the WTS701 to request an interrupt service from the host controller. The interrupt types that the device generates are controlled by the communications control register command (SCOM). The R/B\ (ready/busy) pin is used to control the flow of data across the SPI bus. When this signal is HIGH, the device can accept more data. When it is LOW, SPI transactions must be paused or terminated.

## INT\ (Interrupt)

INT\ is an open drain output pin. The WTS701 interrupt pin goes LOW and stays LOW when an interrupt event has occurred, as defined by the SCOM command. The interrupt is cleared when a RINT (read interrupt) command is executed. The status register defines what type of interrupt has occurred.

# R/B\ (Ready/Busy Signal)

The R/B\ line is an output pin used to control data transfer rate across the SPI port. The line is used as a handshake signal to the SPI Master to indicate when the device is ready for more data. When HIGH, the master is free to send more data. When LOW, the device is busy and cannot accept more data.

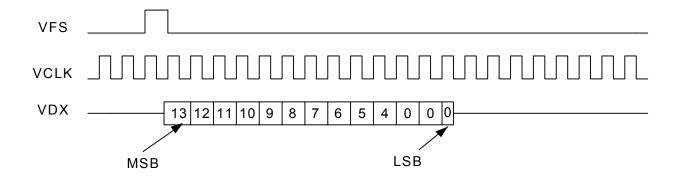

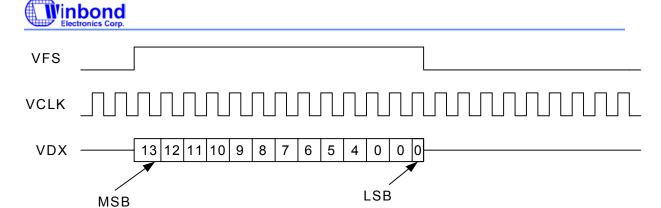

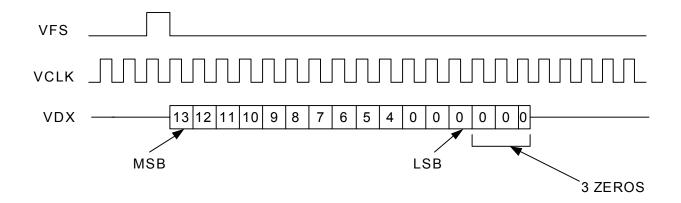

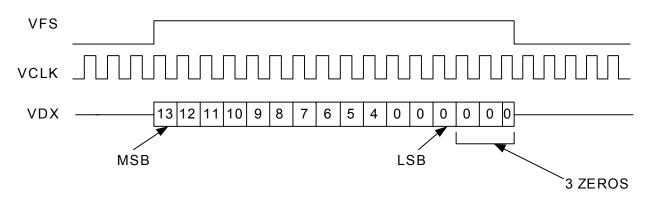

# 7.2.6 The CODEC Interface

The WTS701 provides an on chip interface for digital environment systems, supporting slave CODEC interface mode. The WTS701 CODEC interface is controlled by an external source hence the WTS701 only transmits data. Thus, it is effectively an analog-to-digital converter. Each analog sample is converted to 10 bit digital word. This digital word is transmitted with the MSB first. Since the host expects either 13 or 16 bit data in the short frame format, either three or six zeros are appended as the LSB. It interfaces to the baseband CODEC via the VCLK, VFS and VDX lines. Refer to Figure 2, for more information about the connection between the WTS701 and a CODEC.

All Input pins are 3V and 5V tolerant.

The following is a description of the WTS701 CODEC interface signals:

#### VCLK (CODEC Clock Line)

The CODEC clock line supplies the sampling clock to the internal CODEC. This is a digital input and expects a 512kHz—2.048MHz clock.

### **VFS (CODEC Synchronization Line)**

The CODEC synchronization line supplies a frame synchronization signal to the internal CODEC. This is a digital input. After receipt of a synchronization pulse, the CODEC will output data on the VDX line. The VFS line expects an 8kHz sample rate and supports both short frame and long frame synchronization signal.

### **VDX (CODEC Data Transmit Line)**

The CODEC data transmit line is a digital output that places digital audio data onto the CODEC bus. The line is in a tri-state condition until the device is due to transmit data. The data output from the VDX line is selected by the SCOD Command. When WTS701 places data on the VDX line, it is required that the VFS line should be in tri-state condition when another device is connected to the CODEC as well.

## 7.2.7 The Analog Interface

The WTS701 provides an on chip analog interface for audio output via an  $8\Omega$  speaker driver or an output buffer capable of driving a  $5k\Omega$  load. Additionally, an analog input (AUXIN) allows an audio signal to be fed through the WTS701 chip to either output device. The command SAUD configures the analog path. A digitally controlled attenuator provides volume control via the SVOL command.

The following is a description of the analog pins:

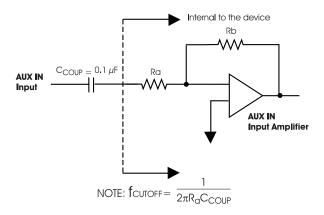

# **AUXIN (Analog Input)**

The AUXIN is an additional audio input to the WTS701. This input has a nominal 694 mV p-p level at its minimum gain setting (0 dB) (See <u>Table 2</u>). Additional gain is available in 3 dB steps (controlled by the SAUD Command) up to 9 dB. The use and equivalent circuit of the input amplifier is shown in <u>Figure 7</u>.

Figure 7. AUXIN Input Amplifier.

Table 2. AUXIN Gain Settings.

| 0TLP Input AUD Register |      |      |      | Gain <sup>2</sup> | Resistor                                | Speaker                           |

|-------------------------|------|------|------|-------------------|-----------------------------------------|-----------------------------------|

| V <sub>P-P</sub> '      | AIG1 | AIG0 |      | (dB)              | Ratio (R <sub>b</sub> /R <sub>a</sub> ) | Out V <sub>P-P</sub> <sup>3</sup> |

| 0.694                   | 0    | 0    | 1.00 | 0                 | 40.1 / 40.1                             | 0.694                             |

| 0.491                   | 0    | 1    | 1.41 | 3                 | 47.0 / 33.2                             | 0.694                             |

| 0.347                   | 1    | 0    | 2.00 | 6                 | 53.5 / 26.7                             | 0.694                             |

| 0.245                   | 1    | 1    | 2.82 | 9                 | 59.2 / 21                               | 0.694                             |

<sup>&</sup>lt;sup>1</sup>OTLP Input is the reference Transmission Level Point that is used for testing. This level is typically 3 dB below clipping.

## **AUXOUT (Analog Output)**

The AUXOUT is an audio output pin used to provide an analog output of the synthesized speech from the WTS701. It drives a minimum load of  $5 \text{ k}\Omega$  up to a maximum of 1 V p-p. The AC signal is superimposed on approximately 1.2 VDC bias and must be capacitively coupled to the load. This output stage may be powered down by clearing the AOPU bit via the SAUD command.

### **SP +, SP- (Speaker +/-)**

This is the speaker differential output circuit. It is designed to drive an  $8\Omega$  speaker connected across the speaker pins up to a maximum of 23.5 mW power. This stage has selectable gains of 1.32 and 1.6, which can be chosen through the SPGO bit via the SAUD command. These pins are biased to approximately 1.2 VDC and, if used single-ended, must be capacitively coupled to their load. Do **NOT** ground the unused pin. This output stage may be powered down by clearing the SPPU bit via the SAUD command.

#### **ATTCAP (AutoMute Attenuator Capacitor)**

This pin provides a capacitor connection for setting the AutoMute. It should have a 4.7  $\mu$ F capacitor connected to ground and it cannot be left floating. The AutoMute circuit reduces the amount of noise present in the output during quiet pauses.

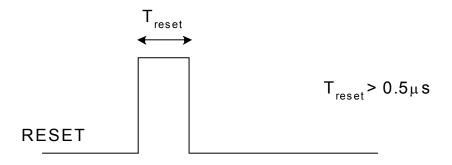

#### 7.2.8 Resetting

The chip has an internal power-on reset circuit that ensures correct initialization upon application of power. The reset pin signal must be held HIGH for  $0.5\mu s$  to achieve a reset (see Figure 8) and to put the WTS701 in the RESET state. Once the WTS701 completes the reset, it will enter the POWER DOWN mode. Before issuing active commands, a clock configuration and device power up command must be issue in the POWER DOWN mode.

Issuing a Reset command (RST) resets the WTS701 processor to the initial POWER DOWN state. Applying the reset pin, while the chip is active, allows the host processor to reset the WTS701 to its default values and the IDLE state.

<sup>&</sup>lt;sup>2</sup>From AUXIN to AUXOUT. <sup>3</sup>Measured differentially at SP+/SP.

Figure 8. Reset Condition Timing.

#### 7.3 COMMUNICATION PROTOCOL

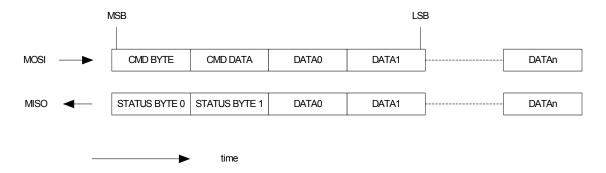

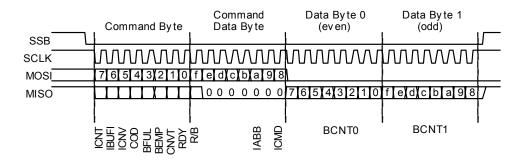

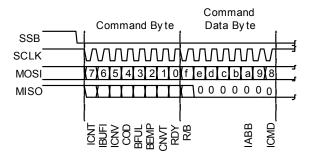

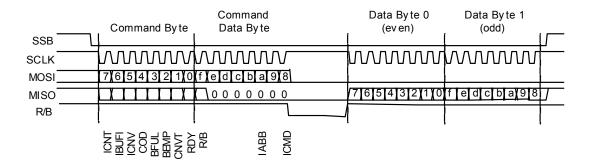

The WTS701 is controlled by a series of SPI transactions to send commands to the device. The general format of an SPI transaction is shown in <u>Figure 9.</u> A transaction is always started by sending a command word. The command word consists of a command byte followed by a command data byte. At the same time, the status register is shifted out on the MISO line. What follows depends on what command is sent. The general case is that following the command word, up to *n*-bytes of data can be sent to the device and *n*-bytes can be read from the device. An SPI transaction is finished when SS\ is returned to the HIGH condition.

Figure 9. SPI Transaction Format.

## 7.3.1 Command Classes

The SPI transactions to the WTS701 fall into four classes. The four classes represent variations in how the command, and any associated data, is handled. The class of a command is defined by the two most significant bits of the command byte. A summary of the command classes is given below

#### Class 0 Commands

These are commands that are executed irrespective of the state of the WTS701. That is, the command will execute even if the device is busy or powered down. These commands are executed internally by a hardware command interpreter. All commands not of class 0 require that the WTS701 be in a powered up state. Example of class 0 command is the Read Status (RDST) command.

## **Class 1 Commands**

Class 1 commands require interpretation by the internal firmware of the WTS701. Class 1 commands consist only of a command byte and command data byte. Any further data sent in a transaction is ignored. Class 1 commands are most often used for setting a configuration register in the device or sending commands that have no data such as the conversion pause (PAUS) command.

## **Class 2 Commands**

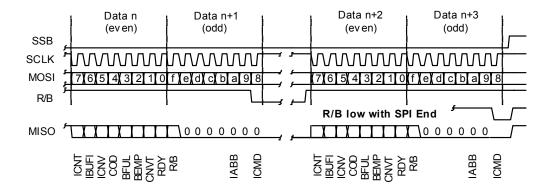

Class 2 commands have associated data. After the command word, any data bytes following are loaded into an internal FIFO buffer for processing. If this FIFO becomes full, the R/B\ signal is asserted (LOW) indicating that the host must pause data transfer. An alternative to monitoring the R/B\ line, the R/B\ bit of the status register can be monitored instead (see subsection 7.3.2) or via the RDST command.

#### **Class 3 Commands**

Class 3 commands have data to return to the host. The R/B\ line will go to busy immediately following the command word indicating that the WTS701 is fetching the requested data. Data is put into the BCNT0 and BCNT1 (see subsection 7.3.4) registers and is read out in the two subsequent bytes after R/B\ is released. If more than two bytes are returned from the command, R/B\ will again be asserted until data is ready to read. The primary Class 3 commands are to read the contents of internal configuration registers such as RREG command.

# 7.3.2 Status Register

The WTS701 has a sixteen-bit status register whose value is returned to the host controller during the command word. For class 2 commands, the status register is repeatedly returned every two bytes. This status register provides the host with information regarding the current status of the chip. The host can decide on required actions with this information. The Status Register is echoed back by all commands.

Table 3. Status Bytes.

|               | Bit 7 | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2 | Bit 1    | Bit 0 |

|---------------|-------|----------|----------|----------|----------|-------|----------|-------|

| Status Byte 0 | ICNT  | IBUF     | ICNV     | COD      | BFUL     | BEMP  | CNVT     | RDY   |

| Status Byte 1 | R/B\  | Reserved | Reserved | Reserved | Reserved | IABB  | Reserved | ICMD  |

The contents of the status bytes are described in Table 4.

Table 4. Status Bit Description.

| Byte                                                                                                                                                                                                      | Bit Name | Bit #                                                                                                                                                              |                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                           | RDY      | 0                                                                                                                                                                  | Ready to accept commands. After the device has been powered up, this bit is set after the Power Up latency delay.                                                                                                                                               |

| CNVT                                                                                                                                                                                                      |          | 1                                                                                                                                                                  | Converting. This bit is set anytime while the conversion process is running. If this bit is clear when a convert command is sent, the count in the Count register is set to 0.                                                                                  |

|                                                                                                                                                                                                           | BEMP     | 2                                                                                                                                                                  | The input buffer is empty. This bit is set anytime the input buffer is empty.                                                                                                                                                                                   |

| 0 0                                                                                                                                                                                                       | BFUL     | 3                                                                                                                                                                  | The input buffer is full. This bit is cleared after 128 bytes become available in the input buffer.                                                                                                                                                             |

| Status Byte 0                                                                                                                                                                                             | COD      | 4                                                                                                                                                                  | CODEC is enabled. This is set when the CODEC has been enabled by the SCOD command.                                                                                                                                                                              |

| Statu                                                                                                                                                                                                     | ICNV     | 5                                                                                                                                                                  | Conversion finished interrupt has occurred. To stop CODEC transmission or Power Down the analog outputs an IDLE command should be sent. This bit is cleared by RINT command.                                                                                    |

| gone below the defined threshold. The buffer the SCOM command. If set by the SCOM commands also go LOW. This bit is cleared by RINT commands.  ICNT  7 Count interrupt has occurred. This interrupt is go |          | 6                                                                                                                                                                  | The input text buffer been filled above the defined threshold and then gone below the defined threshold. The buffer threshold level is set by the SCOM command. If set by the SCOM command, the INT\ pin will also go LOW. This bit is cleared by RINT command. |

|                                                                                                                                                                                                           |          | Count interrupt has occurred. This interrupt is generated every time a word has been spoken if activated by the SCOM command. This bit is cleared by RINT command. |                                                                                                                                                                                                                                                                 |

| te 1                                                                                                                                                                                                      |          |                                                                                                                                                                    | Command was ignored. Anytime ICMD is set, the transaction must revert to a single word command and the command must be resent. Any data sent will be ignored.                                                                                                   |

| Status Byte 1                                                                                                                                                                                             | IABB     | 2                                                                                                                                                                  | Abbreviation interrupt has occurred, abbreviation add or abbreviation delete has been completed. Now the ENTER_RRSM command can be sent.                                                                                                                        |

| (0)                                                                                                                                                                                                       | R/B\     | 7                                                                                                                                                                  | Current state of the R/B\ pin. If this bit is 0, any data sent will be ignored.                                                                                                                                                                                 |

<sup>\*5</sup> bits are reserved.

# 7.3.3 Interrupt Handler

If an interrupt has occurred, no further interrupts will be registered until the first interrupt has been cleared. Only one interrupt can be active at any time.

The RINT command will read and clear pending interrupts while the RDST command will read interrupts without clearing them.

Make sure that all interrupts that are not being used are masked by clearing the corresponding bits in the COM register.

# 7.3.4 BCNT -- Byte Count Register

The byte count register (BCNT) is a tool for the host to keep track of where in a conversion the WTS701 is. When a new conversion is started, the byte count register is reset to zero. As each word (as defined by white-space separated characters) is spoken, the byte count register is updated to point to the first character of the next word to be spoken. In this way, the host can position a new conversion if the user wishes to repeat or skip text. The BCNT register is sent with BCNT1 (MSB) first and BCNT0 (LSB) second.

## 7.3.5 Command Acceptance

The WTS701 processes commands and data as they are sent to the device. Under certain conditions the device will not be ready to accept a new command or data. If the device has not finished processing the previous command, the ICMD bit of the status register will be set. If this bit is set, it implies that device is not in a position to accept the command being sent and that it will be ignored. The host should monitor this bit when a command is sent and, if it is detected, the SPI transaction should be terminated at the end of the command word. The host can then resend the command until the command is accepted.

# 7.3.6 Data Acceptance

The WTS701 has an eight byte FIFO to buffer data from the SPI port to the internal processor. During a conversion, data is read from this FIFO into an internal RAM data buffer. If SPI transmission is too fast for the WTS701 to keep up with the R/B\ line will be asserted (LOW) to pause data transfer. Alternatively, the STATUS register can be monitored for the state of the R/B\ signal.

## 7.4 COMMANDS OVERVIEW

Control of the WTS701 is implemented through a 16-bit command word. The command word is always the first word to follow the falling edge on the SS\ signal. The command word consists of the command byte followed by the command data byte. Many commands do not require a command data byte, although one must be sent. For commands that have no data, the command data byte is a 'don't care'.

Commands fall into five categories. Commands that control an operational synthesis function of the text-to-speech processing, commands that modify internal configuration registers, commands that change system state, commands that read internal status registers, and customization commands.

- 23 -

#### **Status Commands**

## Table 5. Status Opcodes.

The WTS701 has three read-only registers accessed by the opcodes, which are shown to the right.

The Read Status Register

returns the device's

operational status and the

numbers of bytes that have been converted.

| Opcode | Mnemonic | Function                |

|--------|----------|-------------------------|

| 0x04   | RDST     | Read Status Register    |

| 0x06   | RINT     | Read Interrupt Register |

| 0x12   | RVER     | Device Version          |

- The Read Interrupt Register returns the same status data and clears any of the interrupt status bits that are set.

- The version register returns the device and language version of the chip.

## **System Commands**

Table 6. System Opcodes.

The WTS701 responds to various system commands that change the state of the system, namely:

- The Power Up command wakes up the device from POWER DOWN mode.

- Opcode

Mnemonic

Function

0x02

PWUP

Power Up

0x40

PWDN

Power Down

0x10

RST

Reset

0x57

IDLE

Go Idle

- The Power Down

command requests that the device enter the POWER DOWN mode.

- The Reset command resets the device (see subsection 7.4.3).

- The Idle command puts WTS701 processor in IDLE mode

## **Synthesis Commands**

The synthesis commands affect the text-to-speech synthesis. They are detailed in the table to the right.

The basic commands are:

- Start a conversion

- Pause the conversion

- Resume the conversion

- Stop the conversion

- Finish conversion at the end of the next word.

- Finish the conversion at the end of the buffer

- Volume up/down

- Speed up/down the text-tospeech conversion

| Opcode | Mnemonic | Function             |

|--------|----------|----------------------|

| 0x81   | CONV     | Start Converting     |

| 0x49   | PAUS     | Pause Conversion     |

| 0x4A   | RES      | Resume Conversion    |

| 0x4B   | ST       | Stop Conversion      |

| 0x4D   | FINW     | Finish Word          |

| 0x4C   | FIN      | Finish Buffer        |

| 0x53   | VLUP     | Volume Up            |

| 0x54   | VLDN     | Volume Down          |

| 0x55   | SPUP     | Speed Up Conversion  |

| 0x56   | SPDN     | Slow Down Conversion |

Table 7. Synthesis Opcodes.

# **Configuration Commands**

The WTS701 has several configuration registers. The commands are:

- The COM configuration register governs the behavior of how the chip uses the INT\ and R/B\ hardware lines to communicate with the host

- The CODEC register configures the mode of the digital audio output

- The AUDIO register sets parameters of the analog audio path

|      | Table 8. Co | onfiguration Opcodes. |

|------|-------------|-----------------------|

| code | Mnemonic    | Function              |

| Opcode | Mnemonic | Function                           |

|--------|----------|------------------------------------|

| 0xC0   | RREG     | Read Configuration register        |

| 0x4E   | SCOM     | COM Configuration register         |

| 0x4F   | SCOD     | CODEC Configuration register       |

| 0x50   | SAUD     | AUDIO Configuration register       |

| 0x51   | SVOL     | VOL Configuration register         |

| 0x52   | SSPD     | SPEED Configuration register       |

| 0x14   | SCLC     | CLC (Clock) Configuration register |

| 0x77   | SPTC     | Set Speech Pitch                   |

- The VOLUME register sets the volume level of output

- The SPEED register sets the speed level of output speech

- The CLC register sets the master clock frequency of the device

- The SPTC command sets speech pitch

#### **Customization Commands**

The WTS701 has the ability for the user to customize the way in which it responds to certain text strings. This is done by way of an abbreviation table. The customization opcodes allow the user to interrogate and modify the abbreviation table.

| Opcode | Mnemonic   | Function                      |

|--------|------------|-------------------------------|

| 0xC8   | ABBR_NUM   | Get number of abbrev. entries |

| 0xC9   | ABBR_RD    | Read abbreviation table       |

| 0xC7   | ABBR_MEM   | Get number of free bytes.     |

| 0xAF   | ABBR_ADD   | Add abbrev. entry             |

| 0x83   | ABBR_DEL   | Delete abbrev. entry          |

| 0x0C   | ENTER RRSM | Swap memory                   |

Table 9. Customization Opcodes.

7.4.1 Command Description

The following section list all the standard commands that can be executed on the WTS701.

#### **PWDN Go to POWER DOWN Mode**

This command puts the WTS701 processor in power-down mode. This is a single word command therefore no data is required for this command. The Power Down command places the WTS701 device into its lowest power consumption mode. In POWER DOWN mode, the device will only respond to a Power Up command (PWUP) and Read Status (RDST) command. As soon as Power Down sequence has ended, the RDY flag in the status word is cleared.

| PWDN           | Class                                        | 1 | Туре      | I     |               |  |  |

|----------------|----------------------------------------------|---|-----------|-------|---------------|--|--|

| Byte Sequence: | Host controller                              |   | 0x        | 40    | 0x00          |  |  |

|                | WTS701                                       |   | Status By | rte 0 | Status Byte 1 |  |  |

| Description:   | Put the WTS701 processor in power-down mode. |   |           |       |               |  |  |

# **PWUP Power Up**

This command wakes up the WTS701 processor to IDLE state. The result of this command is that the WTS701 starts the power up sequence, which leads to bringing up internal supplies, resetting the processor, all configuration registers are initialized to their default values and entering IDLE state. As soon as power up sequence has ended, the RDY flag in the status word is asserted. The SCLC command must be sent BEFORE PWUP.

| PWUP           | Class                                       | 0 | Туре      | I    |               |  |  |

|----------------|---------------------------------------------|---|-----------|------|---------------|--|--|

| Byte Sequence: | Host controller                             |   | 0x        | 02   | 0x00          |  |  |

|                | WTS701                                      |   | Status By | te 0 | Status Byte 1 |  |  |

| Description:   | Wake up the WTS701 processor to IDLE state. |   |           |      |               |  |  |

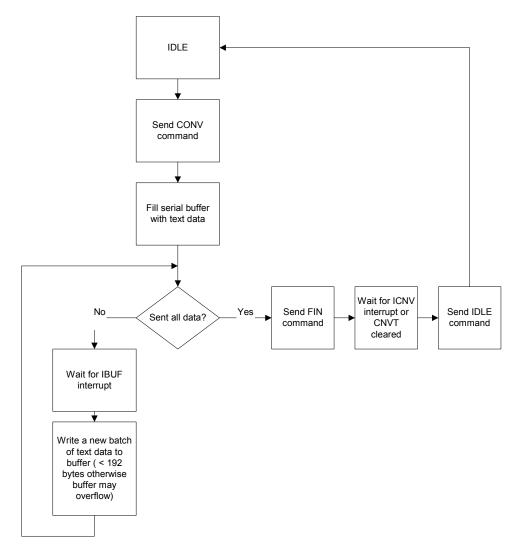

#### CONV Convert

The convert command starts the text to speech conversion process. The convert command is followed by ASCII text data. The device has a buffer of 256 bytes. When this buffer is full, the chip pulls the R/B\ line LOW and sets the BFUL bit in the status word indicating that the WTS701 buffer manager is in the buffer full condition. The WTS701 remains in the buffer full condition until the input buffer has been emptied of half the buffer space (128 bytes). When the buffer is full, the Host may do one of two things:

- 1. The Host may end the command at that point, then poll the BFUL bit of the SPI status register until it is clear, and then send new CONV commands with the additional ASCII text data.

- 2. The Host may also continue the command (keep SS\ LOW) and wait for the R/B\ pin to go HIGH. As each word is processed by the WTS701, space will become free in the buffer and the R/B\ pin will go HIGH until it is full again.

The device may also be configured such that it will generate an interrupt to the host when the buffer threshold (set by RCOM command) has been crossed. (See  $\underline{\text{Tables 3}}$  and  $\underline{\text{4}}$ ) This allows the host to fill the buffer then wait for the Interrupt to send the additional data.

During conversion, the Convert Count Register is updated as each word has been spoken. This register is cleared to zero at power up, and at the beginning of a new conversion process after one has been terminated.

A convert command is terminated in several ways:

- The first is to send a finish command (FIN) indicating that the host has finished sending data. In this case, the device finishes converting the text buffer, then stops and enters a wait state.

- The conversion process will also stop when the EOT (^D, ASCII 0x1A, UNICODE 0x00 0x1A) character is part of the input text. When the device detects the EOT character, it will continue the conversion process until the buffer is emptied and the final word spoken. Then it will stop and enter the wait state.

- The finish word command (FINW) will cause the WTS701 device to finish the word currently being spoken, then flush the buffers and enter the wait state.

- The stop command (ST) will cause the WTS701 to immediately stop converting, flush the buffer and enter the wait state.

Once the wait state has been entered the device will clear the convert (CONV) bit from the status register and, if enabled, generate an ICVT interrupt. At this stage the CODEC and analog path are still active. To release the CODEC bus or Power Down the analog path an IDLE command should be sent to the device.

| CONV          | Class           | 2                                                                              | Туре          | III             |       |                 |       |  |  |  |

|---------------|-----------------|--------------------------------------------------------------------------------|---------------|-----------------|-------|-----------------|-------|--|--|--|

| Byte          | Host controller |                                                                                | 0x81          | 0x00            | DATA0 |                 | DATAn |  |  |  |

| Sequence: WTS |                 | 1                                                                              | Stadus Byte 0 | 1 Status Byte 0 |       | Status Byte n%2 |       |  |  |  |

| Description:  | Start or        | Start or continue a conversion process. Data sent is text data for conversion. |               |                 |       |                 |       |  |  |  |

## PAUS Pause

This command causes a pause of the conversion process. There is no data associated with this command. The pause condition is terminated by the RES (Resume) command

| PAUS           | Class                                         | 1 | Туре      |      |               |  |  |

|----------------|-----------------------------------------------|---|-----------|------|---------------|--|--|

| Byte Sequence: | Host controller                               |   | 0x        | 49   | 0x00          |  |  |

|                | WTS701                                        |   | Status By | te 0 | Status Byte 1 |  |  |

| Description:   | This command pauses the conversation process. |   |           |      |               |  |  |

#### RES Resume

This command causes the conversion to resume if it was paused. There is no data associated with this command

| RES            | Class                                        | 1 | Туре      | I    |               |  |  |

|----------------|----------------------------------------------|---|-----------|------|---------------|--|--|

| Byte Sequence: | Host controller                              |   | 0x        | 4A   | 0x00          |  |  |

|                | WTS701                                       |   | Status By | te 0 | Status Byte 1 |  |  |

| Description:   | This command resumes conversion after pause. |   |           |      |               |  |  |

# ST Stop

This command immediately stops conversion without finishing buffer.

| ST             | Class           | 1       | Туре          | I |               |  |

|----------------|-----------------|---------|---------------|---|---------------|--|

| Byte Sequence: | Host controller |         | 0x4B          |   | 0x00          |  |

|                | WTS701          |         | Status Byte 0 |   | Status Byte 1 |  |

| Description:   | Stop conv       | ersion. |               |   |               |  |

# FINW Finish Word

This command directs the WTS701 to finish text conversion at the end of the current word.

| FINW           | Class           | 1                                                                                 | Туре      | I     |               |  |  |  |

|----------------|-----------------|-----------------------------------------------------------------------------------|-----------|-------|---------------|--|--|--|

| Byte Sequence: | Host controller |                                                                                   | 0x4D      |       | 0x00          |  |  |  |

|                | WTS701          |                                                                                   | Status By | rte 0 | Status Byte 1 |  |  |  |

| Description:   |                 | This indicates that conversion is to end with the processing of the current word. |           |       |               |  |  |  |

## FIN Finish

This command indicates that no further conversion data is to follow and to stop conversion after processing the current buffer contents.

| FIN            | Class                                                  | 1 | Туре      | I     |               |  |  |

|----------------|--------------------------------------------------------|---|-----------|-------|---------------|--|--|

| Byte Sequence: | Host controller                                        |   | 0x        | 4C    | 0x00          |  |  |

|                | WTS701                                                 |   | Status By | rte 0 | Status Byte 1 |  |  |

| Description:   | Finish conversion after processing the current buffer. |   |           |       |               |  |  |

## IDLE Idle

This command is executed after the receipt of an end-of-conversion interrupt (ICNV) has occurred. The IDLE command will deactivate all audio outputs and bring the device to the IDLE state.

| IDLE           | Class                     | 1      | Туре      | I     |               |  |  |

|----------------|---------------------------|--------|-----------|-------|---------------|--|--|

| Byte Sequence: | Host cont                 | roller | 0x        | 57    | 0x00          |  |  |

|                | WTS701                    |        | Status By | rte 0 | Status Byte 1 |  |  |

| Description:   | Put WTS701 in IDLE state. |        |           |       |               |  |  |

#### RDST Read Status

The Read Status command reads the status word of the device. If two dummy data bytes are also sent, the contents of the byte count register are also returned. Refer to subsections  $\frac{7.3.2}{1.00}$  and  $\frac{7.3.4}{1.00}$  for more information regarding the STATUS register and BCNT register.

| RDST           | Class     | 0                               | Туре          | II |          |        |           |       |

|----------------|-----------|---------------------------------|---------------|----|----------|--------|-----------|-------|

| Byte Sequence: | Host cont | roller                          | 0x04          |    | 0x00     |        | 0x00      | 0x00  |

|                | WTS701    |                                 | Status Byte 0 |    | Status I | Byte 1 | BCNT<br>1 | BCNT0 |

| Description:   | Read Sta  | Read Status word of the device. |               |    |          |        |           |       |

#### RVER Read Version

The Read version command reads the WTS701 version information. The software version information is only valid when the device is powered up.

| RVER           | Class   | 0                                                     | Туре          | П |          |       |        |        |

|----------------|---------|-------------------------------------------------------|---------------|---|----------|-------|--------|--------|

| Byte Sequence: | Host co | ntroller                                              | 0x12          |   | 0x00     |       | 0x00   | 0x00   |

|                | WTS70   | 1                                                     | Status Byte 0 |   | Status B | yte 1 | HW VER | SW VER |

| Description:   | Read W  | Read WTS701 processor Software and Hardware versions. |               |   |          |       |        |        |

# RINT Read Interrupt

The Read Interrupt command reads the status word of the device, it also clears the status interrupt request flags at the end of the transaction. As a result of this command, all interrupt bits are cleared and INT\ pin is released. Refer to subsections  $\frac{7.3.2}{1.00}$  and  $\frac{7.3.4}{1.00}$  for more information regarding the STATUS register and BCNT register.

| RINT           | Class              | 0                                                     | Туре | П        |       |       |       |      |

|----------------|--------------------|-------------------------------------------------------|------|----------|-------|-------|-------|------|

| Byte Sequence: | Host co            | ntroller                                              | 0x06 |          | 0x00  |       | 0x00  | 0x00 |

|                | WTS701 Status Byte |                                                       | e 0  | Status B | yte 1 | BCNT1 | BCNT0 |      |

| Description:   | Read st            | Read status word and clear the status interrupt bits. |      |          |       |       |       |      |

# RREG Read Configuration Register

The read configuration register command reads the configuration register specified in the command data byte. The code 0xNN is the register number and it is described in  $\frac{\text{Table 10}}{\text{Table 10}}$  – Configuration Registers, subsection  $\frac{7.4.2}{\text{Table 10}}$ .

| RREG           | Class   | 3                                 | Туре        | IV  |          |       |      |      |

|----------------|---------|-----------------------------------|-------------|-----|----------|-------|------|------|

| Byte Sequence: | Host co | ntroller                          | 0xC0        |     | 0xNN     |       | 0x00 | 0x00 |

|                | WTS70   | 1                                 | Status Byte | e 0 | Status B | yte 1 | XX   | REG  |

| Description:   | Read co | lead configuration register 0xNN. |             |     |          |       |      |      |

Note: XX = don't care.

## **SCOM Set COM Register**

Set the COM (interrupt communication) configuration register to value 0xNN. Refer to subsection 7.4.2 describing all configuration registers and the COM register in particular.

The Default value of this register after Power-Up or Reset is 0x00. Refer to subsection 7.4.2 - Configuration Registers, which describes all register bits.

| SCOM           | Class                      | 1               | Туре          | 1            |                        |

|----------------|----------------------------|-----------------|---------------|--------------|------------------------|

| Byte Sequence: | Host cont                  | Host controller |               | 4E           | 0xNN                   |

|                | WTS701                     |                 | Status Byte 0 |              | Status Byte 1          |

| Description:   | Set the Coto to value Coto | •               | upt commi     | unication) c | configuration register |

Publication Release Date: 6/25/2002 Revision 3.08

# SCOD Set COD Register

Set the COD (CODEC control) configuration register to value 0xNN.

The Default value of this register after Power-Up or Reset is 0x01. Refer to subsection 7.4.2 -Configuration Registers, which describes all register bits.

| SCOD           | Class                                                          | 1 | Туре          | 1 |               |  |

|----------------|----------------------------------------------------------------|---|---------------|---|---------------|--|

| Byte Sequence: | Host controller                                                |   | 0x4F          |   | 0xNN          |  |

|                | WTS701                                                         |   | Status Byte 0 |   | Status Byte 1 |  |

| Description:   | Set the COD (CODEC control) configuration register to va 0xNN. |   |               |   |               |  |

# SAUD Set AUD Register

Set the AUD (analog audio) configuration register to value 0xNN.

The Default value of this register after Power-Up or Reset is 0x43. Refer to subsection 7.4.2 - Configuration Registers, which describes all register bits.

| SAUD           | Class                                                           | 1      | Туре          | I |               |

|----------------|-----------------------------------------------------------------|--------|---------------|---|---------------|

| Byte Sequence: | Host cont                                                       | roller | 0x50          |   | 0xNN          |

|                | WTS701                                                          |        | Status Byte 0 |   | Status Byte 1 |

| Description:   | Set the AUD (analog audio) configuration register to valu 0xNN. |        |               |   |               |

# SVOL Set VOL Register

Set the VOL (volume) configuration register to value 0xNN.

The Default value of this register after Power-Up or Reset is 0x07. Refer to subsection 7.4.2 - Configuration Registers, which describes all register bits.

| SVOL           | Class                                                      | 1      | Туре          | I |               |  |

|----------------|------------------------------------------------------------|--------|---------------|---|---------------|--|

| Byte Sequence: | Host cont                                                  | roller | 0x51          |   | 0xNN          |  |

|                | WTS701                                                     |        | Status Byte 0 |   | Status Byte 1 |  |

| Description:   | Set the VOL (volume) configuration register to value 0xNN. |        |               |   |               |  |

# SSPD Set SPD Register

Set the SPD (speech rate/speed) configuration register to value 0xNN.

The Default value of this register after Power-Up or Reset is 0x02. Refer to subsection 7.4.2 - Configuration Registers, which describe all register bits.

| SSPD           | Class             | 1              | Туре        | I          |                       |

|----------------|-------------------|----------------|-------------|------------|-----------------------|

| Byte Sequence: | Host cont         | ost controller |             | 52         | 0xNN                  |

|                | WTS701            | NTS701         |             | te 0       | Status Byte 1         |

| Description:   | Set the value 0xN | ` .            | ech rate/sp | eed) confi | iguration register to |

# SCLC Set CLC Register

Set the Clock configuration register (CLC) to value 0xNN.

The value of this register **must** be set after Power-Up or Reset command to 0x00. Refer to subsection <u>7.4.2</u> - Configuration Registers, which describes all register bits.

| SCLC           | Class                                                     | 0      | Туре | I    |               |  |

|----------------|-----------------------------------------------------------|--------|------|------|---------------|--|

| Byte Sequence: | Host cont                                                 | roller | 0x14 |      | 0xNN          |  |

|                | WTS701                                                    | /TS701 |      | te 0 | Status Byte 1 |  |

| Description:   | Set the Clock configuration register (CLC) to value 0xNN. |        |      |      |               |  |

#### SPTC Set Speech Pitch

Set the speech pitch to value 0xNN. The valid pitch values are between 0x00 and 0x06 while the default pitch value is 0x01, and these values can be used to control the speech output pitch. The command can be executed only when the WTS701 is in IDLE state.

| SPTC           | Class                                         | 1      | Туре          | I |               |  |      |

|----------------|-----------------------------------------------|--------|---------------|---|---------------|--|------|

| Byte Sequence: | Host cont                                     | roller | 0x77          |   | 0x77 0xNN     |  | 0xNN |

|                | WTS701                                        |        | Status Byte 0 |   | Status Byte 1 |  |      |

| Description:   | Set the speech pitch parameter to value 0xNN. |        |               |   |               |  |      |

# VLUP Volume-Up Command

Increment the volume (VOL) register. Has no effect if already at maximum volume.

The Default value of this register after Power-Up or Reset is 0x07. Refer to subsection 7.4.2 - Configuration Registers, which describes all register bits.

| VLUP           | Class                                | 1                    | Туре | I     |               |  |

|----------------|--------------------------------------|----------------------|------|-------|---------------|--|

| Byte Sequence: | Host cont                            | roller               | 0x53 |       | 0x00          |  |

|                | WTS701                               | /TS701 Status Byte 0 |      | rte 0 | Status Byte 1 |  |

| Description:   | Increment the volume (VOL) register. |                      |      |       |               |  |

#### VLDN VOLUME DOWN COMMAND

Decrement the volume (VOL) register. This has no effect if already at minimum volume. The Default value of this register after Power-Up or Reset is 0x07. Refer to subsection 7.4.2 - Configuration Registers, which describes all register bits.

| VLDN           | Class                                | 1 | Туре          |  |               |  |

|----------------|--------------------------------------|---|---------------|--|---------------|--|

| Byte Sequence: | Host controller                      |   | 0x54          |  | 0x00          |  |

|                | WTS701                               |   | Status Byte 0 |  | Status Byte 1 |  |

| Description:   | Decrement the volume (VOL) register. |   |               |  |               |  |

# SPUP Speed Up Command

Increase speaking rate (SPD register). This has no effect if already at maximum speaking rate. The Default value of this register after Power-Up or Reset is 0x02. Refer to subsection 7.4.2 - Configuration Registers, which describes all register bits.

| SPUP           | Class                                  | 1           | Туре | 1     |               |  |

|----------------|----------------------------------------|-------------|------|-------|---------------|--|

| Byte Sequence: | Host cont                              | roller      | 0x55 |       | 0x00          |  |

|                | WTS701                                 | 01 Status E |      | rte 0 | Status Byte 1 |  |

| Description:   | Increase speaking rate (SPD register). |             |      |       |               |  |

# SPDN Speed Down Command

Decrease speaking rate (SPD register). Has no effect if already at minimum speaking rate. The Default value of this register after Power-Up or Reset is 0x02. Refer to subsection 7.4.2 - Configuration Registers, which describes all register bits.

| SPDN           | Class     | 1                                      | Туре          | I  |               |  |  |

|----------------|-----------|----------------------------------------|---------------|----|---------------|--|--|

| Byte Sequence: | Host cont | Host controller                        |               | 56 | 0x00          |  |  |

|                | WTS701    |                                        | Status Byte 0 |    | Status Byte 1 |  |  |

| Description:   | Decrease  | Decrease speaking rate (SPD register). |               |    |               |  |  |

## RST Reset Command

Sending this command has the same affect as a Power-On reset, the WTS701 enters the POWER DOWN state.

| RST            | Class                    | 0 | Туре          | I |               |  |  |