### 14-CHANNEL T1/E1/J1 LONG-HAUL/SHORT-HAUL LINE INTERFACE UNIT

**MARCH 2003** REV. P1.0.1

### GENERAL DESCRIPTION

The XRT83L314 is a fully integrated 14-channel longhaul and short-haul line interface unit (LIU) that operates from a single 3.3V power supply. Using internal termination, the LIU provides one bill of materials to operate in T1, E1, or J1 mode independently on a per channel basis with minimum external components. The LIU features are programmed through a standard microprocessor interface. EXAR's LIU has patented high impedance circuits that allow the transmitter outputs and receiver inputs to be high impedance when experiencing a power failure or when the LIU is powered off. Key design features within the LIU optimize 1:1 or 1+1 redundancy and non-intrusive monitoring applications to ensure reliability without using relays.

The on-chip clock synthesizer generates T1/E1/J1 clock rates from a selectable external clock frequency and has five output clock references that can be used for external timing (8kHz, 1.544Mhz, 2.048Mhz, nxT1/J1, nxE1).

Additional features include RLOS, a 16-bit LCV counter for each channel, AIS, QRSS generation/ detection, Network Loop Code generation/detection, TAOS, DMO, and diagnostic loopback modes.

#### **APPLICATIONS**

- T1 Digital Cross Connects (DSX-1)

- ISDN Primary Rate Interface

- CSU/DSU E1/T1/J1 Interface

- T1/E1/J1 LAN/WAN Routers

- Public Switching Systems and PBX Interfaces

- T1/E1/J1 Multiplexer and Channel Banks

- Integrated Multi-Service Access Platforms (IMAPs)

- Integrated Access Devices (IADs)

- Inverse Multiplexing for ATM (IMA)

- Wireless Base Stations

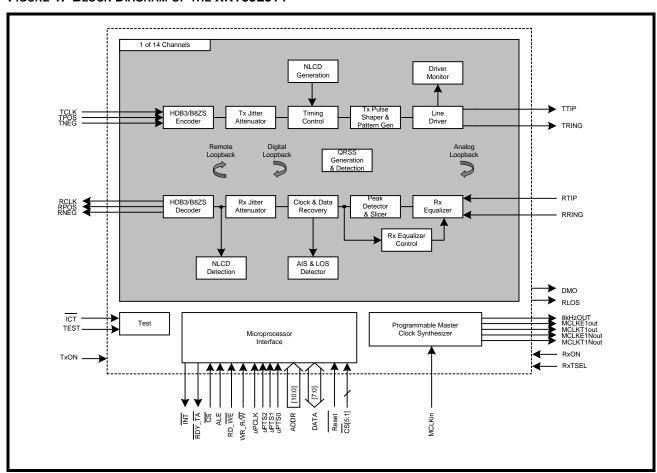

FIGURE 1. BLOCK DIAGRAM OF THE XRT83L314

### **FEATURES**

- Fully integrated 14-Channel short haul and long haul transceivers for T1/J1 (1.544MHz) and E1 (2.048MHz) applications.

- T1/E1/J1 short haul, long haul, and clock rate are per port selectable through software without changing components.

- Internal Impedance matching on both receive and transmit for  $75\Omega$  (E1),  $100\Omega$  (T1),  $110\Omega$  (J1), and  $120\Omega$  (E1) applications are per port selectable through software without changing components.

- Power down on a per channel basis with independent receive and transmit selection.

- Five pre-programmed transmit pulse settings for T1 short haul applications, as well as an arbitrary programmable waveform generator for custom transmit pulse shaping per channel.

- Arbitrary pulse generator for T1 short haul and T1 long haul modes per channel.

- Transmit line build outs (LBO) for T1 long haul applications from 0dB to -22.5dB in three -7.5dB steps on a per channel basis.

- On-Chip transmit short-circuit protection and limiting protects line drivers from damage on a per channel basis.

- Independent Crystal-Less digital jitter attenuators (JA) with 32-Bit or 64-Bit FIFO for the receive and transmit paths

- On-Chip frequency multiplier generates T1 or E1 master clocks from a variety of external clock sources (8, 16, 56, 64, 128, 256kHz and 1X, 2X, 4X, 8X T1 or E1)

- Driver failure monitor output (DMO) alerts of possible system or external component problems.

- Transmit outputs and receive inputs may be "High" impedance for protection or redundancy applications on a per channel basis.

- Support for automatic protection switching.

- 1:1 and 1+1 protection without relays.

- Selectable receiver sensitivity from 0 to 36dB cable loss in T1 @ 772kHz, and 0 to 43dB cable loss in E1 @ 1,024kHz.

- Receive monitor mode handles 0 to 29dB resistive attenuation (flat loss) along with 0 to 6dB cable loss for both T1 and E1.

- Receiver line attenuation indication output in 1dB steps.

- Loss of signal (RLOS) according to ITU-T G.775/ ETS300233 (E1) and ANSI T1.403 (T1/J1).

- Programmable receive slicer threshold (45%, 50%, 55%, or 68%) for improved receiver interference immunity.

- Programmable data stream muting upon RLOS detection.

- On-Chip HDB3/B8ZS encoder/decoder with an internal 16-bit LCV counter for each channel.

- On-Chip digital clock recovery circuit for high input jitter tolerance.

- QRSS pattern generator and detection for testing and monitoring.

- Error and bipolar violation insertion and detection.

- Transmit all ones (TAOS) and in-band network loop up and loop down code generation.

- Automatic loop code detection for remote loopback activation.

- Supports local analog, remote, digital, and dual loopback modes.

- Low Power dissipation: 170mW per channel (50% density).

- 250mW per channel maximum power dissipation (100% density).

- Single 3.3V supply operation (3V to 5V I/O tolerant).

- 304-Pin TBGA package

- -40°C to +85°C Temperature Range

- Supports gapped clocks for mapper/multiplexer applications.

### PRODUCT ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE TYPE  | OPERATING TEMPERATURE RANGE |  |  |  |  |  |

|----------------|---------------|-----------------------------|--|--|--|--|--|

| XRT83L314IB    | 304 Lead TBGA | -40°C to +85°C              |  |  |  |  |  |

# PIN OUT OF THE XRT83L314

|    | А             | В          | ၁         | D                                | Ш          | ш           | Ö      | I       | ſ          | ×            | _           | Σ         | z         | Д        | æ                     | T        | n                            | >        | 8        | <b>\</b>                                          | AA                       | AB                       | AC                              |

|----|---------------|------------|-----------|----------------------------------|------------|-------------|--------|---------|------------|--------------|-------------|-----------|-----------|----------|-----------------------|----------|------------------------------|----------|----------|---------------------------------------------------|--------------------------|--------------------------|---------------------------------|

| 1  | ınnamed.12    | ınnamed.17 | RGND_5    | RRING_5                          | RTIP_5     | RVDD_4      | RTIP_4 | RRING_4 | RGND_4     | unnamed.16   | ınnamed.10  | RGND_3    | RRING_3   | RTIP_3   | RVDD_3                | RTIP_2   | RRING_2                      | RGND_2   | RRING_1  | RTIP_1                                            | unnamed.9                | RLOS                     | unnamed.0                       |

| 2  | ICTB          | DGND_DRV   | TRING_5   | TVDD_5                           | RVDD_5     | RCLK_5      | RCLK_4 | TRING_4 | DVDD_3_4_5 | unnamed.14 u | DGND_3_4_5u | TRING_3   | TVDD_3    | RCLK_3   | RCLK_2                | RVDD_2   | TRING_2                      | DVDD_1_2 | RGND_1   | RVDD_1                                            | RCLK_1                   | UPCLK                    | DVDD_DRV                        |

| 3  | TCLK_5        | INTB       | DVDD_PRE  | unnamed.13                       | TTIP_5     | RNEG_5      | RNEG_4 | TTIP_4  | TVDD_4     | DVDD_DRV     | AGND_BIAS   | TTIP_3    | RNEG_3    | RNEG_2   | TTIP_2                | TVDD_2   | DGND_DRV                     | TRING_1  | TTIP_1   | RNEG_1                                            | RDY_DTACKB               | [9]0                     | D[5]                            |

| 4  | MCLKE1xN      | TPOS_4     | 4_SOGT    | TEST                             | unnamed.11 | TGND_5      | RPOS_5 | RPOS_4  | TGND_4     | AVDD_BIAS    | DGND_PRE    | TGND_3    | RPOS_3    | RPOS_2   | TGND_2                | DGND_1_2 | TVDD_1                       | TGND_1   | RPOS_1   | ОМО                                               | Шa                       | D[2]                     | D[1]                            |

| 2  | MCLKOUT_E1    | TCLK_4     | TNEG_4    | TNEG_5                           |            |             |        |         |            |              |             |           |           |          |                       |          |                              |          |          | DVDD_PRE                                          | D[4]                     | [0]a                     | TCLK_1                          |

| 9  | MCLKIN        | TCLK_3     | TNEG_3    | TPOS_3                           |            |             |        |         |            |              |             |           |           |          |                       |          |                              |          |          | D[3]                                              | TPOS_1                   | TPOS_2                   | TCLK_2                          |

| 7  | MCLKOUT_T1    | TPOS_6     | TNEG_6    | TCLK_6                           |            |             |        |         |            |              |             |           |           |          |                       |          |                              |          |          | TNEG_1                                            | TNEG_2                   | TNEG_0                   | TCLK_0                          |

| 8  | RVDD_6        | MCLKT1xN   | GNDPLL_21 | rGND_6 RPOS_6 DVDD_DRV EIGHT_KHZ |            |             |        |         |            |              |             |           |           |          |                       |          |                              |          |          | TPOS_0                                            | DGND_DRV                 | DGND_PRE                 | GNDPLL_11                       |

| 6  | RTIP_6        | RCLK_6     | GNDPLL_22 | DVDD_DRV                         |            |             |        |         |            |              |             |           |           |          |                       |          |                              |          |          | RPOS_13 TGND_13 DGND_13_0 TGND_0 RPOS_0 GNDPLL_12 | RCLK_0                   | RVDD_0                   | RTIP_0                          |

| 10 | RGND_6RRING_6 | TVDD_6     | RNEG_6    | RPOS_6                           |            |             |        |         |            |              |             |           |           |          |                       |          |                              |          |          | RPOS_0                                            | RNEG_0                   | 0_ddvT                   | RRING_0                         |

| 1  | RGND_(        | TRING_6    | TTIP_6    | _                                |            |             |        |         |            |              |             | View      |           |          |                       |          |                              |          |          | OTGND_C                                           | 0_TTIP_0                 | TRING_0                  | RGND_(                          |

| 12 | RGND_7        | TRING_7    | DGND_6_7  |                                  |            | Bottom View |        |         |            |              |             | DGND_13_( | DVDD_13_0 | TRING_13 | RGND_13 RGND_0RRING_0 |          |                              |          |          |                                                   |                          |                          |                                 |

| 13 | RRING_7       | TVDD_7     | TTIP_7    | TGND_7                           |            |             |        |         |            |              |             | ш         |           |          |                       |          |                              |          |          | TGND_13                                           | TTIP_13                  | RCLK_13 TVDD_13          | RRING_1                         |

| 14 | RTIP_7        | RCLK_7     | RNEG_7    | RPOS_7                           |            |             |        |         |            |              |             |           |           |          |                       |          |                              |          |          | RPOS_13                                           | RNEG_13                  | RCLK_13                  | RTIP_13                         |

| 15 | RVDD_7        | /DDPLL_21  | /DDPLL_22 | DGND_PRE RPOS_7                  |            |             |        |         |            |              |             |           |           |          |                       |          |                              |          |          | RXTSEL                                            | DVDD_UP                  | DGND_UP                  | RVDD_13 RTIP_13 RRING_13        |

| 16 | DGND_DRV      | TCLK_7     | TNEG_7    | TCLK_10                          |            |             |        |         |            |              |             |           |           |          |                       |          |                              |          |          | TCLK_13                                           | TPOS_12 TNEG_11 DVDD_DRV | TPOS_11 TPOS_13VDDPLL_12 | TNEG_12TCLK_11 TNEG_13VDDPLL_11 |

| 17 | TPOS_7        | TNEG_10    | TCLK_9    | FPOS_9                           |            |             |        |         |            |              |             |           |           |          |                       |          |                              |          |          | TCLK_12                                           | TNEG_11                  | POS_13                   | NEG_13                          |

| 18 | TPOS_10       | TNEG_9     | TNEG_8    | RDB_DSB                          |            |             |        |         |            |              |             |           |           |          |                       |          |                              |          |          | A[7]                                              | rpos_12                  | rPos_11                  | TCLK_11                         |

| 19 | TCLK_8 T      | TPOS_8     | . SW_ALE  | CSB2 R                           |            |             |        |         |            |              |             |           |           |          |                       |          |                              |          |          | A[1]                                              | A[6] T                   | RXOFF T                  | TNEG_12                         |

| 20 | WRB_RWB       | CSB5       | CSB3      | DVDD_PRE                         | A[9]       | TGND_8      | RPOS_8 | RPOS_9  | TGND_9     | unnamed.4    | DGND_PRE    | TGND_10   | RPOS_10   | RPOS_11  | TGND_11               | TRING_11 | JGND_11_12                   | TGND_12  | RPOS_12  | DVDD_PRE                                          | A[2]                     | A[5]                     | TXOFF                           |

| 21 | CSB4          | CSB1       | DVDD_DRV  | unnamed.7                        | 8_ddvT     | TTIP_8      | RNEG_8 | RNEG_9  | TTIP_9     | unnamed.3    | DGND_DRV    | TTIP_10   | RNEG_10   | RNEG_11  | TTIP_11               | TVDD_11  | DVDD_DRV DVDD_11_12DGND_11_1 | TVDD_12  | TTIP_12  | RNEG_12                                           | UPTS0                    | A[3]                     | A[4]                            |

| 22 | CSB           | RESETB     | A[8]      | TRING_8                          | RVDD_8     | RCLK_8      | RCLK_9 | TVDD_9  | TRING_9    | unnamed.1    | unnamed.6   | TRING_10  | TVDD_10   | RCLK_10  | RCLK_11               | RVDD_11  | DVDD_DRVI                    | TRING_12 | RGND_12  | RCLK_12                                           | unnamed.5                | UPTS1                    | A[0]                            |

| 23 | A[10]         | unnamed.2  | RGND_8    | RRING_8                          | RTIP_8     | RVDD_9      | RTIP_9 | RRING_9 | RGND_9     | DVDD_8_9_10  | DGND_8_9_10 | RGND_10   | RRING_10  | RTIP_10  | RVDD_10               | RTIP_11  | RRING_11                     | RGND_11  | RRING_12 | RTIP_12                                           | RVDD_12                  | DGND_DRV                 | UPTS2                           |

### ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE       | OPERATING TEMPERATURE RANGE              |  |  |  |  |

|----------------|---------------|------------------------------------------|--|--|--|--|

| XRT83L314IB    | 304 LEAD TBGA | -40 <sup>0</sup> C to +85 <sup>0</sup> C |  |  |  |  |

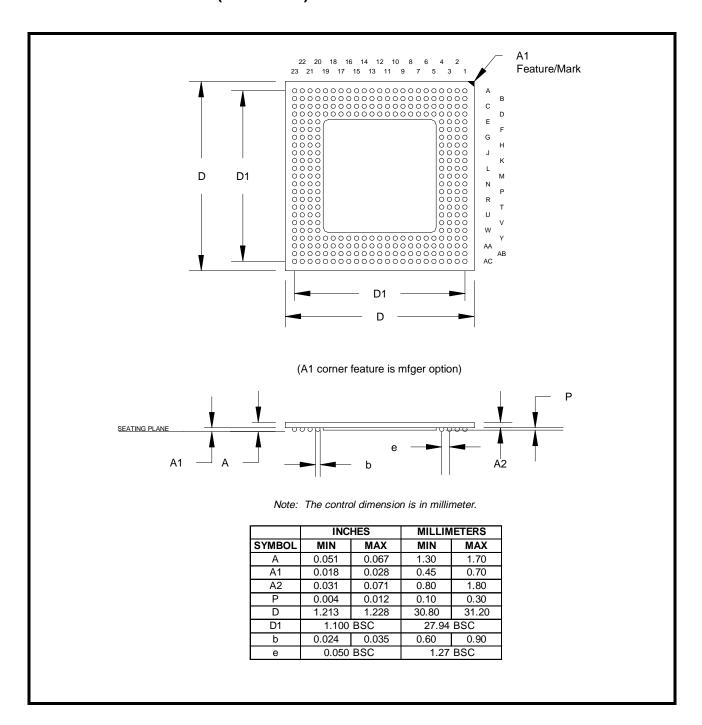

## **PACKAGE DIMENSIONS (DIE DOWN)**

### **REVISION HISTORY**

| REVISION # | DATE     | DESCRIPTION                                                 |

|------------|----------|-------------------------------------------------------------|

| P1.0.0     | 02/14/03 | First release of the 14-Channel LIU Preliminary Datasheet   |

| P1.0.1     | 03/27/03 | Added the 16-bit LCV Counter Details for Revision B Silicon |

### **NOTICE**

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 2003 EXAR Corporation

Datasheet March 2003.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.