# CXG1156K

# Power Amplifier Module for JCDMA

#### Description

The CXG1156K is the power amplifier module which operates at a single power supply. This IC is designed using the Sony's original p-Gate HFET process.

# Features

• Single power supply operation:

VDD1 = VDD2 = 3.5V (High power mode),

1.3V (Low power mode 1),

1.0V (Low power mode 2),

VGG = 2.7V

- Small package: 0.065cc (6.2mm × 6.2mm × 1.7mm)

- High efficiency:  $\eta add = 40\%$  Pout = 27.5dBm (High power mode),

- ηadd = 23%@Pout = 15dBm (Low power mode 1)

- Output power (high/low power mode switching supported):

POUT = 18 to 27.5dBm: High power mode,

POUT = 15 to 18dBm: Low power mode 1,

#### Pout $\leq$ 15dBm: Low power mode 2

• Gain: Gp = 29dB (@900MHz)

# Applications

Power amplifier for JCDMA system cellular phones

#### Structure

p-Gate HFET module

#### Absolute Maximum Ratings (Ta = 25°C)

| <ul> <li>Operating case temperature</li> </ul> | Tcase                 | -30 to +90  | °C  |

|------------------------------------------------|-----------------------|-------------|-----|

| <ul> <li>Storage temperature</li> </ul>        | Tstg                  | -30 to +125 | °C  |

| <ul> <li>Bias voltage</li> </ul>               | Vdd1, Vdd2            | 6           | V   |

| <ul> <li>Bias voltage</li> </ul>               | Vgg                   | 3.3         | V   |

|                                                | (@VDD1 = VDD2 = 3.5V) |             |     |

| <ul> <li>Input power</li> </ul>                | PIN                   | 8           | dBm |

# **Recommended Operating Conditions**\*

• VDD1 = VDD2 = 3.2 to 4.2V@Pout = 18 to 27.5dBm,

1.3 to 2.0V@Pout ≤ 18dBm,

• VGG = 2.7V ± 1%

<sup>\*</sup>This recommended operating voltage is the value that specified the supply voltage range where the functional operation was confirmed by the Sony's recommended evaluation board. GaAs module is ESD sensitive devices. Special handling precautions are required.

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

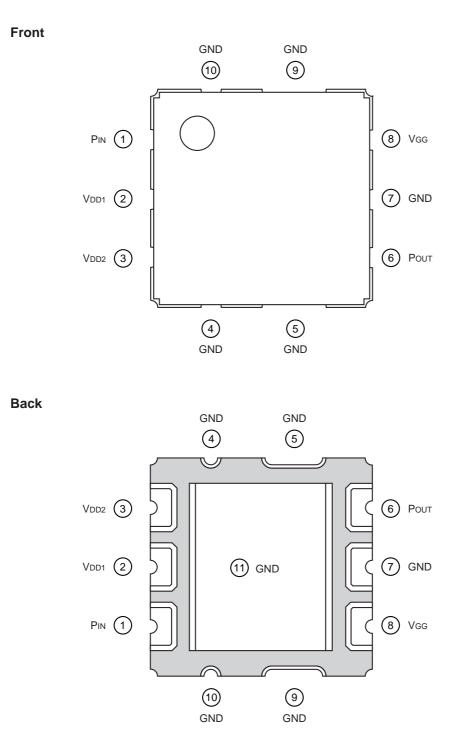

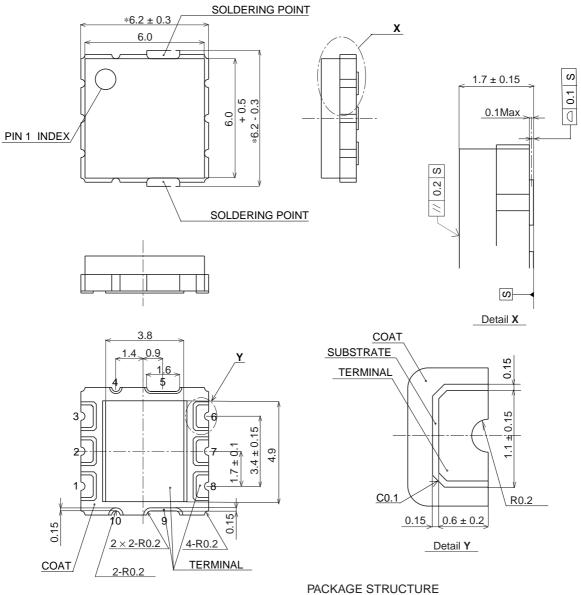

# Package Outline/Pin Configuration

Note) Be sure to solder the GND part (11) to the land.

For the land where the GND part (11) is connected, form the GND pattern by making the through holes in the land.

# **Electrical Characteristics**

# $(ZS = ZL = 50\Omega, IS-95 \text{ Modulation}, Tc = 25^{\circ}C)$

| Item                        | Conditions                                                                                   | Min. | Тур. | Max. | Unit |

|-----------------------------|----------------------------------------------------------------------------------------------|------|------|------|------|

| Frequency                   |                                                                                              | 887  |      | 925  | MHz  |

| Current consumption 1       | Pout = 27.5dBm, Vdd = 3.5V, Vgg = 2.7V                                                       |      | 405  | 420  | mA   |

| Current consumption 2       | Pout = 15dBm, Vdd = 1.3V, Vgg = 2.7V                                                         |      | 105  | 110  | mA   |

| Current consumption 3       | Pout = 12dBm, Vdd = 1.0V, Vgg = 2.7V                                                         |      | 79   | 90   | mA   |

| Gain 1                      | Pout = 27.5dBm, Vdd = 3.5V, Vgg = 2.7V                                                       | 25   | 29   |      | dB   |

| Gain 2                      | Pout = 18dBm, Vdd = 1.3V, Vgg = 2.7V                                                         | 22   | 24   |      | dB   |

| Gain 3                      | Pout = 15dBm, Vdd = 1.0V, Vgg = 2.7V                                                         | 20   | 22   |      | dB   |

| ACPR1<br>(High power mode)  | POUT = $27.5$ dBm, VDD = $3.5$ V, VGG = $2.7$ V,<br>±900kHz offset, 30kHz band width         |      | -54  | -47  | dBc  |

| ACPR2<br>(High power mode)  | POUT = $27.5$ dBm, VDD = $3.5$ V, VGG = $2.7$ V,<br>± $1.98$ MHz offset, $30$ kHz band width |      | -64  | -58  | dBc  |

| ACPR1<br>(Low power mode 1) | POUT = 18dBm, VDD = 1.3V, VGG = 2.7V,<br>±900kHz offset, 30kHz band width                    |      | -56  | -50  | dBc  |

| ACPR2<br>(Low power mode 1) | POUT = $18$ dBm, VDD = $1.3$ V, VGG = $2.7$ V,<br>$\pm 1.98$ MHz offset, 30kHz band width    |      | -63  | -58  | dBc  |

| ACPR1<br>(Low power mode 2) | POUT = 15dBm, VDD = 1.0V, VGG = 2.7V,<br>±900kHz offset, 30kHz band width                    |      | -56  | -50  | dBc  |

| ACPR2<br>(Low power mode 2) | POUT = $15$ dBm, VDD = $1.0$ V, VGG = $2.7$ V,<br>$\pm 1.98$ MHz offset, 30kHz band width    |      | -63  | -58  | dBc  |

| 2nd, 3rd harmonics          | POUT = 27.5dBm, VDD = 3.5V, VGG = 2.7V                                                       |      | -27  | -23  | dBc  |

| Input VSWR                  | VDD = 3.5V, VGG = 2.7V                                                                       |      | 1.3  | 2    |      |

| Gate current                | Vgg = 2.7V, Pout ≤ 27.5dBm                                                                   |      | 1.7  | 2.5  | mA   |

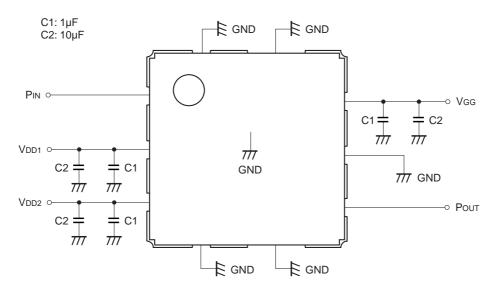

## **Recommended External Circuit**

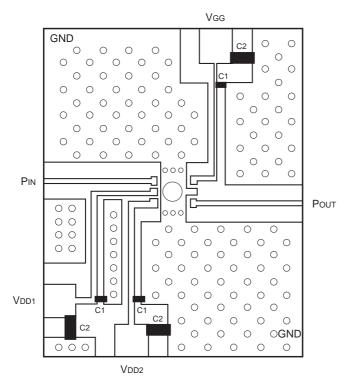

## **Recommended Evaluation Board**

| Board material:               | Glass fabric-base epoxy         |

|-------------------------------|---------------------------------|

| Size:                         | $40mm \times 50mm \times 0.6mm$ |

| Relative dielectric constant: | 4.6                             |

#### Front

#### Back

| O O GND | 000                                   | 0 0   |

|---------|---------------------------------------|-------|

|         |                                       | 0 0 0 |

|         |                                       |       |

| 0 0 0   |                                       |       |

|         |                                       | 00    |

|         | O O O O O O O O O O O O O O O O O O O |       |

| 0 0 0 0 | 0                                     | 000   |

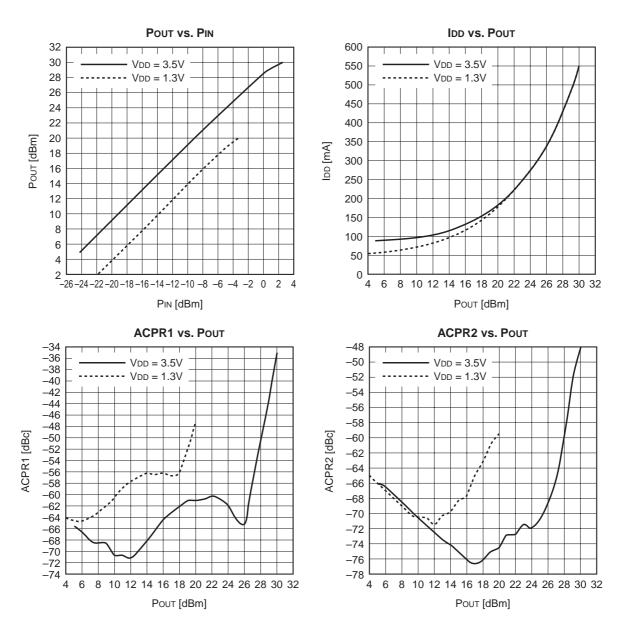

#### **Example of Representative Characteristics**

#### Conditions: f = 900MHz

$\label{eq:VDD1} VDD1 = VDD2 = 3.5V, VGG = 2.7V \mbox{ (High power mode)} \\ VDD1 = VDD2 = 1.3V, VGG = 2.7V \mbox{ (Low power mode 1)} \\ Ta = 25^{\circ}C$

Package Outline

Unit: mm

**10PIN LCC**

| NOTE: Dimension "*" | does not | include | cutting | burr. |

|---------------------|----------|---------|---------|-------|

|---------------------|----------|---------|---------|-------|

| SONY CODE  | LCC-10C-03 |

|------------|------------|

| JEITA CODE |            |

| JEDEC CODE |            |

| PACKAGE MATERIAL   | CERAMIC SUBSTRATE |

|--------------------|-------------------|

| TERMINAL TREATMENT | GOLD PLATING      |

| TERMINAL MATERIAL  | NICKEL PLATING    |

| PACKAGE MASS       | 0.8g              |