#### DECEMBER

#### Features

- ■Single power can operate at 2.4 V through 6V.

- Current output could drive 8 ohm speaker with a transistor, Vout could drive buzzer directly.

- The voice content is stored up to 15 seconds and can be separated to 64 sections.

- Duration of each section can be different.

- ■Mute is available for each section up to 48 seconds totally.

- A Forever Play function is available.

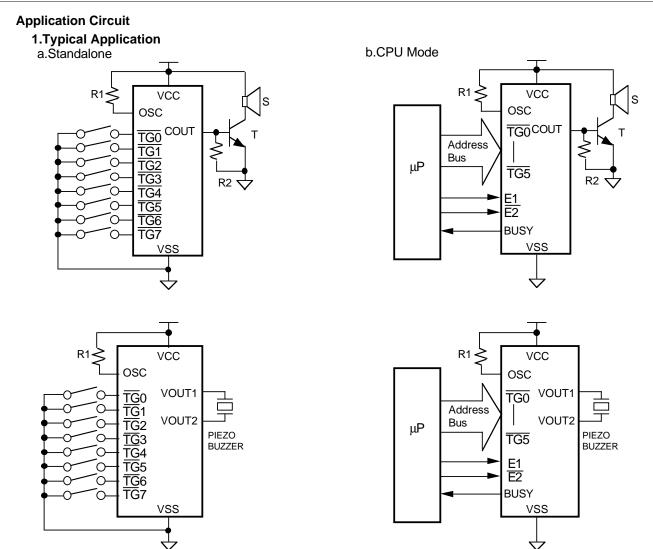

- ■Four addressing interface modes are provided for ■CPU addressing mode: versatile applications: CPU, Stand alone, Ring Trigger and Table Trigger.

- ■Stand alone mode:

- 8 sections can be accessed by 8 trigger input pins individually.

- Table trigger mode:

- a. A phrase is accessed by TGO, low active.

- b. This phrase is composed of 16 elements contiguously as the table content.

- These 16 elements are chosen from 8 sections. C.

- d. Section is located and numbered by 0 through 7.

- ■Ring trigger mode:

- a. A section-by-section phrase is accessed by  $\overline{TGO}$ , low active.

- b. This phrase is composed of 16 element (section)s contiguously as the table content.

- Each single trigger plays next one element (section) c. following above sequence.

- d. These 16 elements are chosen from 8 sections.

- e. Section is located and numbered by 0 through 7.

- a. 64 sections can be accessed by 6 address bits with enable strobe trigger.

- b. Section is located and numbered by 0 through 63. c. The address bit is high true.

- Mask option for either retriggerable output or not.

- Mask option for either Level or Edge trigger type.

- For all four modes, retrigger action restarts playing from the beginning.

- One BUSY output signal is available.

- Automatic power down function(selected by external input, pwr).

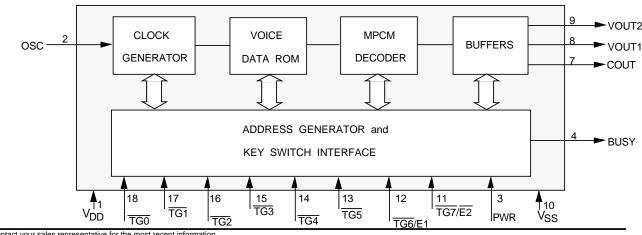

#### **General Description**

The MSS1506 is a single-chip CMOS LSI ROM that can memorize voice up to 15 seconds using MOSEL qualified coding method (MPCM).

Four addressing interfaces are provided: CPU mode, Stand Alone mode, Ring Trigger mode and Table Trigger mode for versatile applications. The voice content can be stored separatly into 64 or 8 or 16 sections or 1 phrase with arbitary length. With minimum external components, this chip can be applied to various application. Customer voice is edited and programmed into ROM by changing one mask during fabrication.

Contact your sales representative for the most recent information

## **MSS1506** VOICE ROM

## MSS1506

### Absolute Maximum Rating

| Symbol                                    | Rating                                                 | Unit |  |  |

|-------------------------------------------|--------------------------------------------------------|------|--|--|

| V <sub>DD</sub> ~ V <sub>SS</sub>         | -0.5 ~ +7.0                                            | V    |  |  |

| V <sub>IN</sub> (TG)<br>all input pins    | $V_{SS}$ -0.3 < $V_{IN}$ < $V_{DD}$ +0.3               | V    |  |  |

| V <sub>OUT</sub> (STS)<br>all output pins | V <sub>SS</sub> <v<sub>OUT &lt; V<sub>DD</sub></v<sub> | V    |  |  |

| T (Operating)                             | -10 ~ +60                                              | °C   |  |  |

| T (Storage)                               | -55 ~ +125                                             | °C   |  |  |

## Pad Description

| Pad No. | Signal Name       | I/O   | Function                                                                                  |  |  |  |  |  |

|---------|-------------------|-------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1       | V <sub>DD</sub>   | Power | Positive power supply                                                                     |  |  |  |  |  |

| 2       | OSC               | I     | Oscillator input                                                                          |  |  |  |  |  |

| 3       | PWR               | I     | Active high for non-power down, Internal pull low                                         |  |  |  |  |  |

| 4       | BUSY              | 0     | Busy signal output, active high                                                           |  |  |  |  |  |

| 5       | NC                |       |                                                                                           |  |  |  |  |  |

| 6       | NC                |       |                                                                                           |  |  |  |  |  |

| 7       | Cout              | 0     | Audio signal current output (for speaker)                                                 |  |  |  |  |  |

| 8       | V <sub>OUT1</sub> | 0     | Audio signal voltage output (for buzzer)                                                  |  |  |  |  |  |

| 9       | V <sub>OUT2</sub> | 0     | Audio signal voltage output (for buzzer)                                                  |  |  |  |  |  |

| 10      | V <sub>SS</sub>   | Power | Negative power supply                                                                     |  |  |  |  |  |

| 11      | E2, TG7           | NC/I  | No connection (RT,TT);Trigger 7, active low( SA);<br>Enable 2, active low (CPU)           |  |  |  |  |  |

| 12      | E1, TG6           | NC/I  | No connection (RT,TT);Trigger 6, active low (SA);<br>Enable 1, active high (CPU)          |  |  |  |  |  |

| 13      | TG5               | NC/I  |                                                                                           |  |  |  |  |  |

| 14      | TG4               | NC/I  |                                                                                           |  |  |  |  |  |

| 15      | TG3               | NC/I  | No connection (RT, TT); Trigger 1 ~ 5, active low<br>(SA); address 1 ~ 5, high true (CPU) |  |  |  |  |  |

| 16      | TG2               | NC/I  |                                                                                           |  |  |  |  |  |

| 17      | TG1               | NC/I  |                                                                                           |  |  |  |  |  |

| 18      | TGO               | 1     | Trigger 0, active low (RT TT, SA);<br>address 0 high true (CPU)                           |  |  |  |  |  |

### **AC** Characteristics

| Timing         | Parameter                 | Min. | Тур. | Max. | Unit. |

|----------------|---------------------------|------|------|------|-------|

| Τ <sub>T</sub> | Trigger pulse width       | 10   | —    |      | ms    |

| Tw             | Write Enable pulse width  | 300  | —    | -    | ns    |

| T <sub>H</sub> | Trigger address hold time | 80   | _    | _    | ns    |

| Τ <sub>Ρ</sub> | Power rise up time        | _    | _    | 1    | ms    |

| T <sub>R</sub> | Power Ripple width        | _    | _    | 1    | ms    |

## **MSS1506**

#### **DC** Characteristics

| Symbol          | Parameter                                                    |      |       | Min. | Тур. | Max. | Unit                               | Condition                                     |  |

|-----------------|--------------------------------------------------------------|------|-------|------|------|------|------------------------------------|-----------------------------------------------|--|

| I <sub>SB</sub> | Supply Stand by                                              |      | —     | 1    | -    |      |                                    |                                               |  |

| IOP             | Current                                                      |      |       | —    | —    | 200  | μA                                 | V <sub>DD</sub> = 4.5V, I/O Open              |  |

| V <sub>IH</sub> | Input Vol                                                    | tage |       | 4    | 4.5  | 5    |                                    | V <sub>DD</sub> = 4.5V                        |  |

| V⊫              | $(\overline{T0} \sim \overline{T7}, E1, \overline{E2}, PWR)$ |      |       | -0.3 | 0    | 0.3  | V                                  | VDD - 4.0 V                                   |  |

| IH              | Input Current                                                |      |       | —    | 0    |      |                                    | V <sub>DD</sub> = 4.5V                        |  |

| ۱ <sub>L</sub>  | ( <del>T</del> 0~T7)                                         |      |       | —    | —    | -15  | μA                                 |                                               |  |

| <b>I</b> н      | Input Current<br>for PWR                                     |      |       | —    | —    | 20   | μA                                 | $V_{DD} = 4.5V$                               |  |

| ۱ <sub>L</sub>  |                                                              |      |       | —    | 0    |      | μΑ                                 |                                               |  |

| I <sub>ОН</sub> | O/P Current Drive                                            |      | Drive | -8   | -13  | -18  | <b>س</b> ۸                         | V <sub>DD</sub> = 4.5V, V <sub>O/P</sub> = 0V |  |

| loL             | V <sub>OUT1</sub> ,V <sub>OU</sub>                           | JT2  | Sink  | 8    | 13   | 18   | mA                                 | $V_{DD} = 4.5V, V_{O/P} = 4.5V$               |  |

| Iон             | Output Current                                               |      | —     | 2    | _    |      | $V_{DD} = 4.5V, V_{O/P} = 0V$      |                                               |  |

| l <sub>OL</sub> | (BUSY)                                                       |      |       | —    | 4    | —    | mA                                 | $V_{DD} = 4.5V, V_{O/P} = 4.5V$               |  |

| lω              | Output Current (C OUT )                                      |      |       | 2.4  | 3    | 3.6  | mA                                 | $V_{DD} = 4.5V$                               |  |

| ΔF/F            | Frequency Stability                                          |      |       | _    | 5    | %    | [Fosc(4.5V) - Fosc(4V)]/Fosc(4.5V) |                                               |  |

| ΔF/F            | Frequency Variation                                          |      |       | _    | _    | 10   | %                                  | $V_{DD} = 4.5V, Rosc = 1.2M\Omega$            |  |

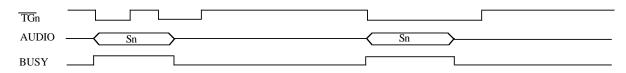

#### **Timing Diagram**

#### I.1. Acceptable Power On Signal & Ripple

#### II.1. Stand Alone mode, No Retrigger function, Edge Trigger Mask, low active, single trigger input

#### II.2. Stand Alone mode, No Retrigger function, Level Trigger Mask, low active, single trigger input

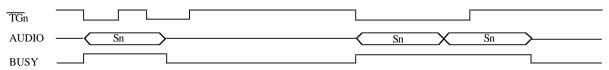

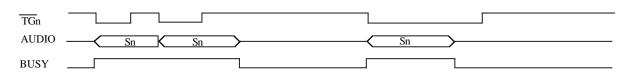

#### III.1. Stand Alone mode, Retrigger function, Edge Trigger Mask, low active, single trigger input

# **MSS1506**

| TGn                                                                                                              |

|------------------------------------------------------------------------------------------------------------------|

| AUDIO <u>Sn</u> <u>Sn</u> <u>Sn</u> <u>Sn</u>                                                                    |

| BUSY                                                                                                             |

|                                                                                                                  |

| IV. 1. Stand Alone mode, No Retrigger function, Edge Trigger Mask, low active, two non - overlap trigger inputs  |

| TGI<br>TG2                                                                                                       |

| AUDIO <u>S2</u> <u>S1</u>                                                                                        |

| BUSY                                                                                                             |

|                                                                                                                  |

| IV. 2. Stand Alone mode, No Retrigger function, Level Trigger Mask, low active, two non - overlap trigger inputs |

| TGI                                                                                                              |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                            |

| BUSY                                                                                                             |

|                                                                                                                  |

| IV. 3. Stand Alone mode, Retrigger function, low active, two non - overlap trigger inputs                        |

| TGI                                                                                                              |

|                                                                                                                  |

| AUDIO $\sim$ S2 K S1 $\rightarrow$ BUSY $\sim$                                                                   |

|                                                                                                                  |

| V. 4. Retrigger function, Trigger Mask = Edge or Level, Overlap trigger inputs                                   |

| TGI                                                                                                              |

| TG2                                                                                                              |

| AUDIO <u>S2</u> <u>S1</u>                                                                                        |

| BUSY                                                                                                             |

|                                                                                                                  |

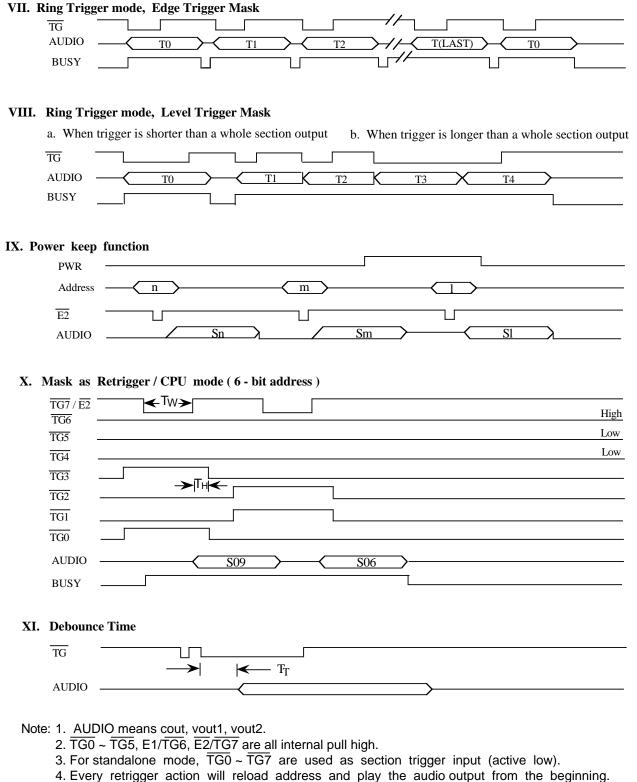

| V. Table Trigger Mask                                                                                            |

| TG                                                                                                               |

| AUDIO $\underline{T0}$ $\underline{T1}$ $\underline{T2}$ $\underline{T(LAST)}$                                   |

| BUSY                                                                                                             |

| NOTE: Tn = nth element of Table content.                                                                         |

III.1. Stand Alone mode, Retrigger function, Level Trigger Mask, low active, single trigger input

5. In CPU mode to avoid unwanted noise caused by abrupt change between different sections of messages, it is recommended to program PWR pin to high (V<sub>DD</sub>) during voice processing.

# **MSS1506**

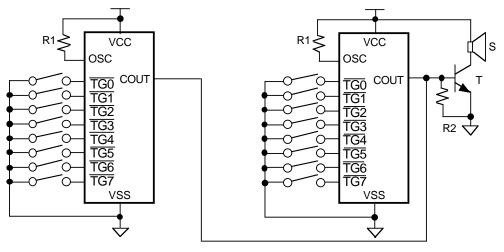

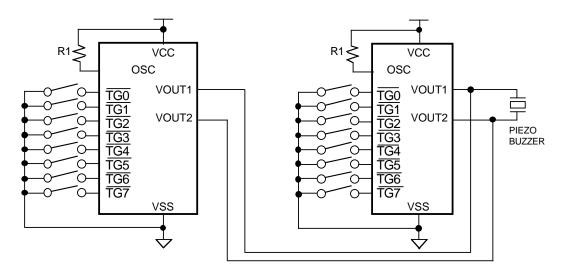

#### **2.Parallel Application**

(Could extend depth to desired section number in parallel arrangement)

## **MSS1506**

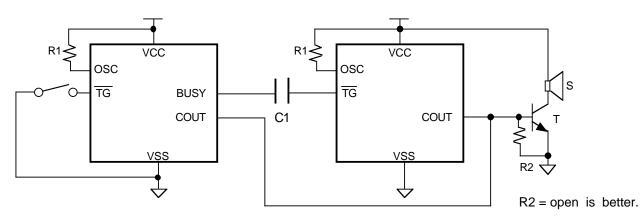

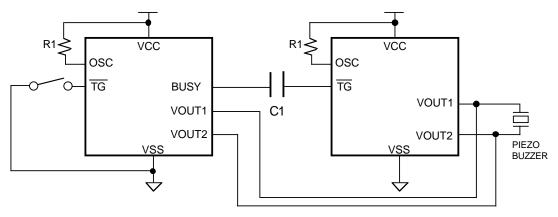

#### **3.Cascade Application**

(Could extend length to desired length in serial arrangement)

- Note: 1.  $R1 = 1.2 M \Omega$ ,  $C1 = 0.1 \mu f$ , T(transistor) =  $\beta > 150$ , R2 = open, S(speaker) = 1/4 w, 8  $\Omega$ ; all typical. Piezo buzzer resonant frequency being around 1K Hz in recommended.

Input switch could be replaced by CDS.

- 4. Cout, Vout1, Vout2 are tristate during stand by state.

- 5. Both cascade and parallel application are applied in CPU mode.

### **Bonding Diagram**

| Pad No. | Designation       |

|---------|-------------------|

| 1       | V <sub>DD</sub>   |

| 2       | OSC               |

| 3       | PWR               |

| 4       | BUSY              |

| 5       | NC                |

| 6       | NC                |

| 7       | C <sub>OUT</sub>  |

| 8       | V <sub>OUT1</sub> |

| 9       | V <sub>OUT2</sub> |

| 10      | Vss               |

| 11      | TG7               |

| 12      | TG <sub>6</sub>   |

| 13      | TG <sub>5</sub>   |

| 14      | TG4               |

| 15      | TG <sub>3</sub>   |

| 16      | TG <sub>2</sub>   |

| 17      | TG <sub>1</sub>   |

| 18      | TG <sub>0</sub>   |

| 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 |

|----|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |    |

|    |    |    |    |    |    |    |    |    |

| 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  |

Note: Substrate is  $\mathsf{V}_{\mbox{DD}}$