| application | UCC1806 |

|-------------|---------|

| INFO        | UCC2806 |

| available   | UCC3806 |

|             |         |

# Low Power, Dual Output, Current Mode PWM Controller

## FEATURES

- BiCMOS Version of UC1846 Families

- 1.4mA Maximum Operating Current

- 100µA Maximum Startup Current

- 1.0A Peak Output Current

- 125nsec Circuit Delay

- Easier Parallelability

- Improved Benefits of Current Mode Control

## DESCRIPTION

The UCC1806 family of BiCMOS PWM controllers offers exceptionally improved performance with a familiar architecture. With the same block diagram and pinout of the popular UC1846 series, the UCC1806 line features increased switching frequency capability while greatly reducing the bias current used within the device. With a typical startup current of 50µA and a well defined voltage threshold for turn-on, these devices are favored for applications ranging from off-line power supplies to battery operated portable equipment. Dual high current, FET driving outputs and a fast current sense loop further enhance device versatility.

All the benefits of current mode control including simpler loop closing, voltage feed-forward, parallelability with current sharing, pulse-by-pulse current limiting, and push-pull symmetry correction are readily achievable with the UCC1806 series.

#### (continued)

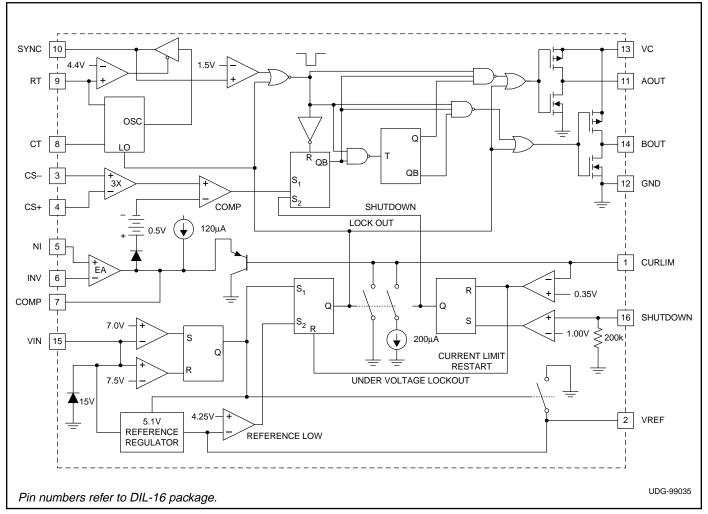

**BLOCK DIAGRAM**

SLUS272A - FEBRUARY 2000

## ABSOLUTE MAXIMUM RATINGS

| Supply Voltage, Low Impedance (Pin 15)+15V                       |

|------------------------------------------------------------------|

| Supply Current, High Impedance (Pin 15)+25mA                     |

| Output Supply Voltage (Pin 13)+18V                               |

| Output Current, Continuous Source or Sink ±200mA                 |

| Output Current, Gate Drive                                       |

| Analog Input Voltage (Pin 3, 4, 5, 6, 16)0.3V to +VIN +0.3V      |

| Sync Output Current (Pin 10) ±30mA                               |

| Error Amplifier Output Current (Pin 7) . +10mA/– (Self Limiting) |

| Power Dissipation at $T_A = 25^{\circ}C$ (Note 3) 1000mW         |

| Power Dissipation at $T_C = 25^{\circ}C$ (Note 3)                |

| Storage Temperature Range                                        |

| Lead Temperature (soldering, 10 seconds)+300°C                   |

Note 1. All voltages are with respect to Ground, Pin 12.

Note 2. Currents are positive into, negative out of the specified terminal.

Note 3. Consult packaging section of databook for thermal limitations and considerations of package.

Note 4. Pin numbers refer to DIL-16 package.

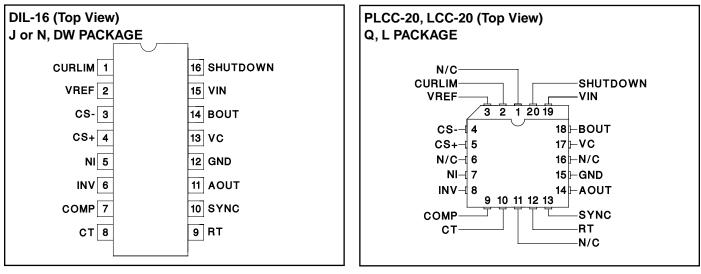

#### **CONNECTION DIAGRAMS**

### **DESCRIPTION (continued)**

These devices are available with multiple package options for both through-hole and surface mount applications; and in commercial, industrial, and military temperature ranges. Contact factory for availability.

The UCC1806 is specified for operation from  $-55^{\circ}$ C to +125°C, the UCC2806 is specified for operation from -40°C to +85°C, and the UCC3806 is specified for operation from 0°C to +70°C. The part is available in DIP and SOIC packages.

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications hold for  $T_A = -55^{\circ}C$  to +125°C for the UCC1806, -40°C to +85°C for the UCC2806, and 0°C to +70°C for the UCC3806;  $V_{IN} = 12V$ ,  $R_T = 33k$ , CT = 330pF,  $C_{BYPASS}$  on  $V_{REF} = 0.01\mu$ F,  $T_A = T_J$ .

| PARAMETER              | TEST CONDITION                                                     | UCC18 | UCC1806 / UCC2806 |      |      | UCC3806 |      |    |

|------------------------|--------------------------------------------------------------------|-------|-------------------|------|------|---------|------|----|

|                        |                                                                    | MIN   | TYP               | MAX  | MIN  | TYP     | MAX  |    |

| Reference Section      |                                                                    | •     |                   |      |      |         |      |    |

| Output Voltage         | $T_{\rm J} = 25^{\circ} {\rm C}, \ {\rm I}_{\rm O} = 0.2 {\rm mA}$ | 5.02  | 5.10              | 5.17 | 5.00 | 5.10    | 5.20 | V  |

| Load Regulation        | 0.2mA < I <sub>O</sub> < 5mA                                       |       | 3                 | 25   |      | 3       | 25   | mV |

| Total Output Variation | Line, Load, Temperature (Note 7)                                   | -150  |                   | 150  | -150 |         | 150  | mV |

| Output Noise Voltage   | $10Hz \le f \le 10kHz$ , T <sub>J</sub> = 25°C (Note 5)            |       | 70                |      |      | 70      |      | μV |

| Long Term Stability    | T <sub>A</sub> = 125°C, 1000 Hours (Note 5)                        |       | 5                 | 25   |      | 5       | 25   | mV |

| Output Short Circuit   |                                                                    | -10   |                   | -30  | -10  |         | -30  | mA |

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications hold for  $T_A = -55^{\circ}C$  to +125°C for the UCC1806, -40°C to +85°C for the UCC2806, and 0°C to +70°C for the UCC3806;  $V_{IN} = 12V$ ,  $R_T = 33k$ , CT = 330pF,  $C_{BYPASS}$  on  $V_{REF} = 0.01\mu$ F,  $T_A = T_J$ .

| PARAMETER                                              | TEST CONDITION UCC1806 / UCC2806                                                             |      | C2806 | l                  |      |      |       |     |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------|------|-------|--------------------|------|------|-------|-----|

|                                                        |                                                                                              | MIN  | TYP   | MAX                | MIN  | TYP  | MAX   |     |

| Oscillator Section                                     |                                                                                              |      |       |                    |      |      |       |     |

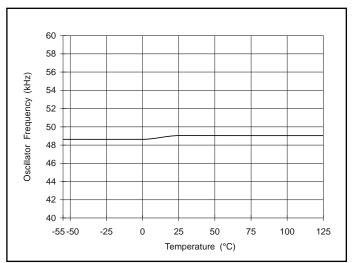

| Initial Accuracy                                       | $T_J = 25^{\circ}C$                                                                          | 42   | 47    | 52                 | 42   | 47   | 52    | kHz |

| Temperature Stability                                  | $T_{MIN} < T_A < T_{MAX}$ (Note 5)                                                           |      | 2     |                    |      | 2    |       | %   |

| Amplitude                                              |                                                                                              |      | 2.35  |                    |      | 2.35 |       | V   |

| SYNC Delay to Outputs                                  | Pin 8 = 0V, Pin 9 = $V_{REF}$ ,<br>$V_{SYNC}$ = 0.8V to 2.0V                                 |      | 50    | 125                |      | 50   | 100   | ns  |

| Discharge Current                                      | T <sub>J</sub> = 25°C, V <sub>PIN</sub> 8 = 2.0V                                             |      | 2     |                    |      | 2    |       | mA  |

| SYNC, VOL                                              | $I_{OUT} = +1mA$                                                                             |      |       | 0.4                |      |      | 0.4   | V   |

| SYNC, VOH                                              | $I_{OUT} = -4mA$                                                                             | 2.4  |       |                    | 2.4  |      |       | V   |

| SYNC, VIL                                              | Pin 8 = 0V, Pin 9 = V <sub>REF</sub>                                                         |      |       | 0.8                |      |      | 0.8   | V   |

| SYNC, VIH                                              | Pin 8 = 0V, Pin 9 = V <sub>REF</sub>                                                         | 2.0  |       |                    | 2.0  |      |       | V   |

| SYNC Input Current                                     |                                                                                              | -1   |       | +1                 | -1   |      | +1    | μA  |

| Error Amplifier Section                                |                                                                                              |      |       |                    |      |      |       |     |

| Input Offset Voltage                                   |                                                                                              |      |       | 5                  |      |      | 10    | mV  |

| Input Bias Current                                     |                                                                                              |      |       | -1                 |      |      | -1    | μA  |

| Input Offset Current                                   |                                                                                              |      |       | 500                |      |      | 500   | nA  |

| Common Mode Range                                      |                                                                                              | 0    |       | V <sub>IN</sub> -2 | 0    |      | VIN-2 | V   |

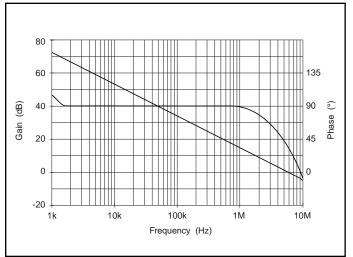

| Open Loop Gain                                         | V <sub>O</sub> = 1.0 to 4.0                                                                  | 80   | 100   |                    | 80   | 100  |       | dB  |

| Unity Gain Bandwidth                                   |                                                                                              | 1    |       |                    | 1    |      |       | MHz |

| Output Sink Current                                    | V <sub>ID</sub> < -20mV, V <sub>PIN 7</sub> = 1.0V                                           | 1    |       |                    | 1    |      |       | mA  |

| Output Source Current                                  | V <sub>ID</sub> < 20mV, V <sub>PIN 7</sub> = 3.0V                                            | -80  | -120  |                    | -80  | -120 |       | μA  |

| Output High Level                                      | $V_{ID} = -50 \text{mV}$                                                                     | 4.5  |       |                    | 4.5  |      |       | V   |

| Output Low Level                                       | $V_{ID} = -50 \text{mV}$                                                                     |      |       | 0.5                |      |      | 0.5   | V   |

| Current Sense Amplifier Sec                            | tion                                                                                         |      |       |                    |      |      |       |     |

| Amplifier Gain                                         | $V_{PIN 3} = 0V, V_{PIN 1} = V_{REF}$ (Notes 3,4)                                            | 2.75 | 3     | 3.35               | 2.75 | 3    | 3.35  | V/V |

| Maximum Differential Input<br>Signal (VPIN 4 - VPIN 3) | $V_{PIN 1} = V_{REF}, V_{PIN 5} = V_{REF}, V_{PIN 6} = 0V$                                   | 1.1  |       |                    | 1.1  |      |       | V   |

| Input Offset Voltage                                   | V <sub>PIN 1</sub> = 0.5V, V <sub>PIN 7</sub> = OPEN                                         |      | 10    | 30                 |      | 10   | 50    | mV  |

| CMRR                                                   | $V_{CM} = 0$ to $V_{IN} - 3.5$                                                               | 60   |       |                    | 60   |      |       | dB  |

| PSRR                                                   |                                                                                              | 56   |       |                    | 56   |      |       | dB  |

| Input Bias Current                                     | V <sub>PIN 1</sub> = 0.5V, PIN 7 OPEN (Note 3)                                               |      |       | -1                 |      |      | -1    | μA  |

| Input Offset Current                                   | VPIN 1 = 0.5V, PIN 7 OPEN (Note 3)                                                           |      |       | 1                  |      |      | 1     | μA  |

| Delay to Outputs                                       | $V_{PIN 5} = V_{REF}$ , PIN 6 = 0, PIN 1 = 2.75V,<br>PIN 4 - PIN 3 = 0 to 1.5V step (Note 6) |      | 125   | 175                |      | 125  | 175   | ns  |

| Current Limit Adjust Section                           |                                                                                              |      |       |                    |      |      |       |     |

| Current Limit Offset                                   | V <sub>PIN 3</sub> = 0, V <sub>PIN 4</sub> = 0, PIN 7 = open                                 | 0.40 | 0.50  | 0.60               | 0.40 | 0.50 | 0.60  | V   |

| Input Bias Current                                     |                                                                                              |      |       | 1                  |      |      | 1     | μA  |

| Minimum Latching Current                               |                                                                                              | 300  | 200   |                    | 300  | 200  |       | μA  |

| Maximum Non-Latching<br>Current                        |                                                                                              |      | 200   | 80                 |      | 200  | 80    | μA  |

| Shutdown Terminal Section                              |                                                                                              |      |       |                    |      |      |       |     |

| Threshold Voltage                                      |                                                                                              | 0.94 | 1.00  | 1.06               | 0.9  | 1.0  | 1.1   | V   |

| Input Voltage Range                                    |                                                                                              | 0    |       | Vin                | 0    |      | Vin   | V   |

| Delay to Outputs                                       | V <sub>PIN 16</sub> = 0 to 1.3V                                                              |      | 75    | 150                |      | 75   | 150   | ns  |

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications hold for  $T_A = -55^{\circ}C$  to +125°C for the UCC1806, -40°C to +85°C for the UCC2806, and 0°C to +70°C for the UCC3806;  $V_{IN} = 12V$ ,  $R_T = 33k$ , CT = 330pF,  $C_{RVPASS}$  on  $V_{REF} = 0.01\mu$ F.  $T_A = T_{I_A}$ .

| PARAMETER                  | TEST CONDITION                                    | UCC1 | UCC1806 / UCC2806 |      |      | UCC3806 |      |    |

|----------------------------|---------------------------------------------------|------|-------------------|------|------|---------|------|----|

|                            |                                                   | MIN  | TYP               | MAX  | MIN  | TYP     | MAX  |    |

| Output Section             |                                                   |      |                   |      |      |         |      |    |

| Output Supply Voltage      |                                                   | 2.5  |                   | 15   | 2.5  |         | 15   | V  |

| Output Low Level           | I <sub>SINK</sub> = 20mA                          |      | 100               | 300  |      | 100     | 200  | mV |

|                            | I <sub>SINK</sub> = 100mA                         |      | 0.40              | 1.1  |      | 0.40    | 1.1  | V  |

| Output High Level          | $I_{SOURCE} = -20 \text{mA}$                      | 11.6 | 11.9              |      | 11.6 | 11.9    |      | V  |

|                            | I <sub>SOURCE</sub> = -100mA                      | 11   | 11.6              |      | 11   | 11.6    |      | V  |

| Rise Time                  | T <sub>J</sub> = 25°C, C <sub>LOAD</sub> = 1000pF |      | 35                | 65   |      | 35      | 65   | ns |

| Fall Time                  | T <sub>J</sub> = 25°C, C <sub>LOAD</sub> = 1000pF |      | 35                | 65   |      | 35      | 65   | ns |

| Under Voltage Lockout Sect | ion                                               |      |                   |      |      |         |      |    |

| Startup Current            | V <sub>IN</sub> < Start Threshold                 |      | 50                | 100  |      | 50      | 100  | μA |

| Operating Supply Current   |                                                   |      | 1                 | 1.4  |      | 1       | 1.4  | mA |

| VIN Shunt Voltage          | I <sub>VIN</sub> = 10mA                           | 15   |                   | 17.5 | 15   |         | 17.5 | V  |

| Startup Threshold          |                                                   | 6.5  | 7.5               | 8    | 6.5  | 7.5     | 8    | V  |

| Threshold Hysteresis       |                                                   |      | 0.75              |      |      | 0.75    |      | V  |

Note 1: All voltages are with respect to Ground, Pin 12.

Note 2: Currents are positive into, negative out of the specified terminal.

Note 3: Parameters measured at trip point of latch with  $V_{PIN 5} = V_{REF}$ ,  $V_{PIN 6} = 0V$ .

Note 4: Amplifier gain defined as: G = delta change at Pin 7/delta change forced at Pin 4 delta voltage at Pin 4 = 0 to 1V.

Note 5: Guaranteed by design. Not 100% tested in production.

Note 6: Current Sense Amp output is slew rate limited to provide noise immunity.

Note 7: Line Range = 10V to 15V, Load Range = 0.2mA to 5mA.

#### **PIN DESCRIPTIONS**

**AOUT and BOUT:** AOUT and BOUT provide alternating high current gate drive for the external MOSFETs. Duty cycle can be varied from 0 to 50% where minimum dead time is a function of CT. Both outputs use MOS transistor switches with inherent anti-parallel body diodes to clamp voltage swings to the supply rails, allowing operation without the use of clamp diodes.

**COMP:** COMP is the output of the error amplifier and the input of the PWM comparator. The error amplifier is a low output impedance, 2MHz operational amplifier which allows sinking or sourcing of current at the COMP pin. The error amplifier is internally current limited, so that zero duty cycle can be commanded by externally forcing COMP to GND.

**CS**–: CS- is the inverting input of the 3X, differential current sense amplifier.

**CS+:** CS+ is the non-inverting input of the 3X, differential current sense amplifier.

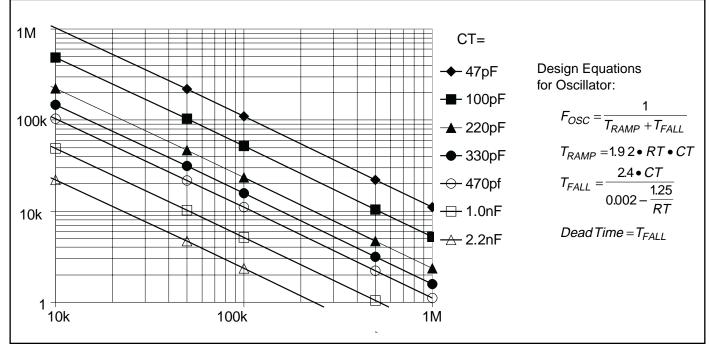

**CT**: CT is the oscillator timing capacitor connection point, which is charged by the current set by RT. CT is discharged to GND through a 2.6mA current sink. This causes a linear discharge of CT to zero volts which then initiates the next switching cycle. Dead time occurs during the discharge of CT, forcing AOUT and BOUT low. Switching frequency (fs) and dead time (td) are approximated by:

$$fs = \frac{1}{2 \bullet RT \bullet CT + td}$$

and  $td = 961 \bullet CT$

**CURLIM:** CURLIM programs the primary current limit threshold and determines whether the device will latch off or retry after an overcurrent condition. When a shutdown signal is generated, a 200µA current source to ground pulls down on CURLIM. If the voltage on the pin remains above 350mV the device remains latched and the power must be cycled to restart. If the voltage on the pin falls below 350mV, the device attempts a restart. The voltage threshold is typically set by a resistor divider from

## **PIN DESCRIPTIONS (continued)**

$V_{\mathsf{REF}}$  to ground. To calculate the current limit adjust voltage threshold the following equations can be used;

Current Limit Adjust Latching Mode Voltage:

$$V = \frac{V_{REF} - (R1 \bullet 300 \,\mu A)}{1 + \frac{R1}{R2}} > 350 \,mV$$

Current Limit Adjust Non-Latching Mode Voltage:

$$V = \frac{V_{REF} - (R1 \cdot 80 \,\mu A)}{1 + \frac{R1}{R2}} > 350 \,mV$$

where R1 is the resistance from the  $V_{\text{REF}}$  to CURLIM and R2 is the resistance from CURLIM to GND.

**GND:** GND is the reference ground and power ground for all functions of this part. Bypass and timing capacitors should be connected as close as possible to GND.

**INV:** INV is the inverting input of the error amplifier and has a common mode range from 0V to  $V_{IN}$  –2V.

**NI:** NI is the non-inverting input of the error amplifier and has a common mode range from 0V to  $V_{IN}$  –2V.

**RT:** RT is the connection point for the oscillator timing resistor. It has a low impedance input and is nominally at 1.25V. The current through RT is mirrored to the timing capacitor pin, CT. This causes a linear charging of CT from 0V to 2.35V. Note that the current mirror is limited to a maximum of  $100\mu$ A so RT must be greater than 12.5k.

**SHUTDOWN:** The SHUTDOWN pin is provided for enhanced protection. When SHUTDOWN is driven above 1V, AOUT and BOUT are forced low.

**SYNC:** SYNC is a bi-directional pin, allowing or providing external synchronization with TTL compatible thresholds. In a typical application RT is connected through a timing resistor to GND which allows the internal oscillator to free run. In this mode SYNC outputs a TTL compatible pulse during the oscillator dead time (when CT is being discharged). If RT is forced above 4.4V, SYNC acts as an input with TTL compatible thresholds and the internal oscillator is disabled. When SYNC is high, greater than 2V the outputs are held active low. When SYNC returns low, the outputs may be high until the on-time is terminated by the normal peak current signal, a fault seen at SHUT-DOWN or the next high assertion of SYNC. Multiple UCC3806s can be synchronized by a single master UCC3806 or external clock.

**VC:** VC is the input supply connection for the FET drive outputs and has an input range of 2.5V to 15V. VC should be capacitively bypassed for proper operation.

$V_{IN}$ :  $V_{IN}$  is the input supply connection for this device. The UCC1806 has a maximum startup threshold of 8V and internally limited by means of a 15V shunt regulator. The shunted supply current must be limited to 2.5mA. For proper operation, VIN must be bypassed to GND with at least a 0.01µF ceramic capacitor.

$V_{REF}$ :  $V_{REF}$  is a 5.1V  $\pm 1\%$  trimmed reference output with a 5mA maximum available current.  $V_{REF}$  must be bypassed to GND with at least a 0.1µF ceramic capacitor for proper operation.

**TYPICAL CHARACTERISTICS**

Figure 1. Error amplifier gain and phase response.

Figure 2. Oscillator frequency vs. temperature.

## UCC1806 UCC2806 UCC3806

## **TYPICAL CHARACTERISTICS (continued)**

Figure 3. Oscillator frequency vs. RT and CT.

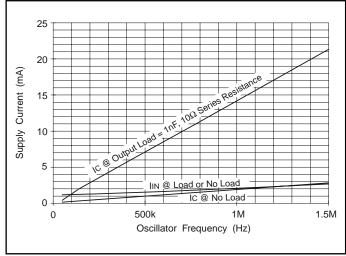

Figure 4. Supply current vs. oscillator frequency.

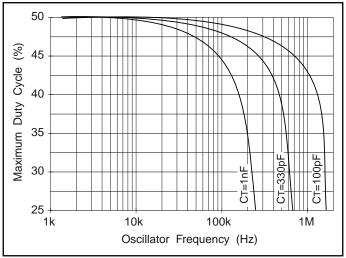

Figure 5. Maximum duty cycle vs. frequency.

## UCC1806 UCC2806 UCC3806

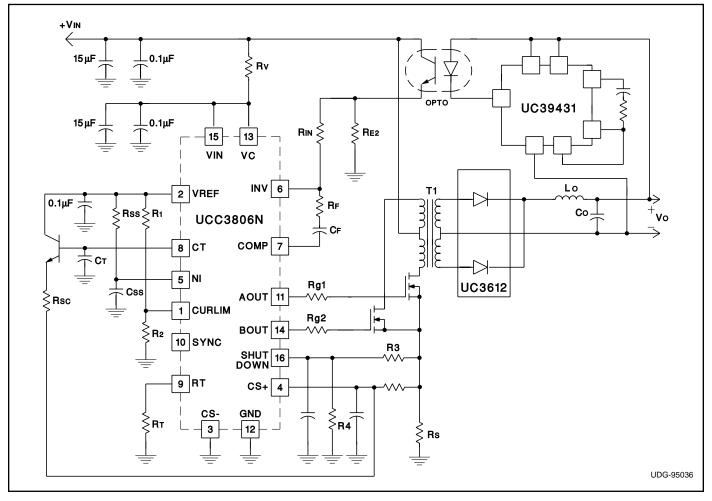

## **TYPICAL APPLICATION**

UNITRODE CORPORATION 7 CONTINENTAL BLVD. • MERRIMACK, NH 03054 TEL. (603) 424-2410 • FAX (603) 424-3460

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated