SLLS151D - DECEMBER 1988 - REVISED APRIL 2003

| <ul> <li>Meet or Exceed the Requirements of</li></ul>                                         | SN65C1154 N PACKAGE                                          |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|

| TIA/EIA-232-F and ITU Recommendation                                                          | SN75C1154 DW, N, OR NS PACKAGE                               |  |  |  |  |  |

| V.28                                                                                          | (TOP VIEW)                                                   |  |  |  |  |  |

| <ul> <li>Very Low Power Consumption</li> <li>5 mW Typ</li> </ul>                              | V <sub>DD</sub> [ 1 20 ] V <sub>CC</sub><br>1RA [ 2 19 ] 1RY |  |  |  |  |  |

| <ul> <li>Wide Driver Supply Voltage</li></ul>                                                 | 1DY [] 3 18 [] 1DA                                           |  |  |  |  |  |

| ±4.5 V to ±15 V                                                                               | 2RA [] 4 17 ] 2RY                                            |  |  |  |  |  |

| <ul> <li>Driver Output Slew Rate Limited to</li></ul>                                         | 2DY [] 5 16 [] 2DA                                           |  |  |  |  |  |

| 30 V/µs Max                                                                                   | 3RA [] 6 15 [] 3RY                                           |  |  |  |  |  |

| <ul> <li>Receiver Input Hysteresis 1000 mV Typ</li> <li>Push-Pull Receiver Outputs</li> </ul> | 3DY [] 7 14 [] 3DA<br>4RA [] 8 13 [] 4RY                     |  |  |  |  |  |

| <ul> <li>Push-Pull Receiver Outputs</li> <li>On-Chip Receiver 1-µs Noise Filter</li> </ul>    | 4DY [] 9 12 [] 4DA<br>V <sub>SS</sub> [] 10 11 [] GND        |  |  |  |  |  |

#### description/ordering information

The SN65C1164 and SN75C1154 are low-power BiMOS devices containing four independent drivers and receivers that are used to interface data terminal equipment (DTE) with data circuit-terminating equipment (DCE). These devices are designed to conform to TIA/EIA-232-F. The drivers and receivers of the SN65C1154 and SN75C1154 are similar to those of the SN75C188 quadruple driver and SN75C189A quadruple receiver, respectively. The drivers have a controlled output slew rate that is limited to a maximum of 30 V/ $\mu$ s and the receivers have filters that reject input noise pulses of shorter than 1  $\mu$ s. Both these features eliminate the need for external components.

The SN65C1154 and SN75C1154 have been designed using low-power techniques in a BiMOS technology. In most applications, the receivers contained in these devices interface to single inputs of peripheral devices such as ACEs, UARTs, or microprocessors. By using sampling, such peripheral devices usually are insensitive to the transition times of the input signals. If this is not the case, or for other uses, it is recommended that the SN65C1154 and SN75C1154 receiver outputs be buffered by single Schmitt input gates or single gates of the HCMOS, ALS, or 74F logic families.

| TA            | PACKAGE   |              | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|---------------|-----------|--------------|--------------------------|---------------------|

| –40°C to 85°C | PDIP (N)  | Tube of 20   | SN65C1154N               | SN65C1154N          |

| 0°C to 70°C   | PDIP (N)  | Tube of 20   | SN75C1154N               | SN75C1154N          |

|               | SOIC (DW) | Tube of 25   | SN75C1154DW              | SN75C1154           |

|               |           | Reel of 2500 | SN75C1154DWR             | 311/301134          |

|               | SOP (NS)  | Reel of 2000 | SN75C1154NSR             | SN75C1154           |

#### **ORDERING INFORMATION**

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2003, Texas Instruments Incorporated

SLLS151D - DECEMBER 1988 - REVISED APRIL 2003

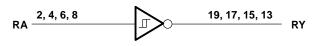

### logic diagram (positive logic)

Typical of Each Receiver

Typical of Each Driver

SLLS151D - DECEMBER 1988 - REVISED APRIL 2003

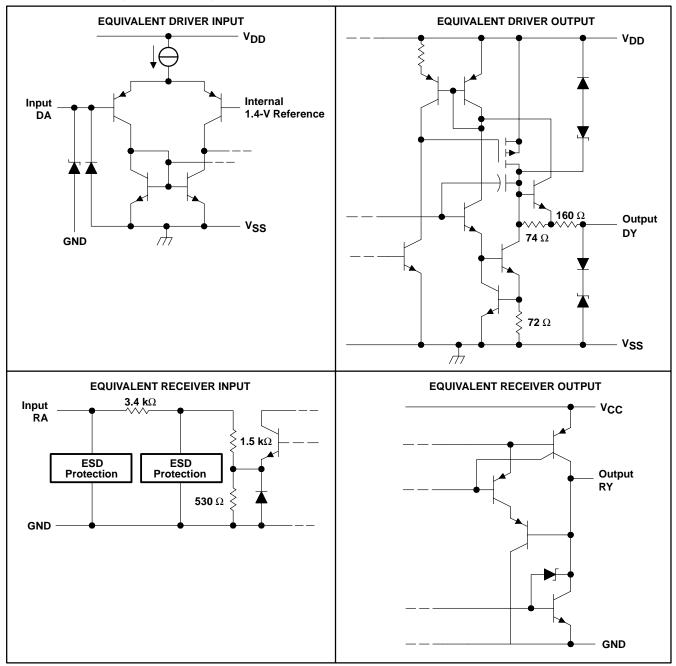

# schematics of inputs and outputs

Resistor values shown are nominal.

#### SLLS151D - DECEMBER 1988 - REVISED APRIL 2003

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage: V <sub>DD</sub> (see Note 1)                     | 15 V                                        |

|------------------------------------------------------------------|---------------------------------------------|

|                                                                  |                                             |

| V <sub>SS</sub>                                                  |                                             |

| V <sub>CC</sub>                                                  |                                             |

| Input voltage range, V <sub>I</sub> : Driver                     | $\ldots$ V <sub>SS</sub> to V <sub>DD</sub> |

| Receiver                                                         |                                             |

| Output voltage range, V <sub>O</sub> :Driver                     | $(V_{SS} - 6 V)$ to $(V_{DD} + 6 V)$        |

| Receiver                                                         |                                             |

| Package thermal impedance, $\theta_{JA}$ (see Notes 2 and 3): DV | / package 58°C/W                            |

| Ng                                                               | backage 69°C/W                              |

| NŠ                                                               | package 60°C/W                              |

| Operating virtual junction temperature, T <sub>J</sub>           | 150°C                                       |

| Storage temperature range, T <sub>stg</sub>                      |                                             |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 sec         |                                             |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage s are with respect to the network GND terminal.

- 2. Maximum power dissipation is a function of  $T_J(max)$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any allowable ambient temperature is  $P_D = (T_J(max) T_A)/\theta_{JA}$ . Operating at the absolute maximum  $T_J$  of 150°C can affect reliability.

- 3. The package thermal impedance is calculated in accordance with JESD 51-7.

#### recommended operating conditions

|                 |                                          |           | MIN                 | NOM | MAX             | UNIT |

|-----------------|------------------------------------------|-----------|---------------------|-----|-----------------|------|

| V <sub>DD</sub> | Supply voltage                           |           | 4.5                 | 12  | 15              | V    |

| VSS             | Supply voltage                           |           | -4.5                | -12 | -15             | V    |

| VCC             | Supply voltage                           |           | 4.5                 | 5   | 6               | V    |

| . v.            | Input voltage Driver Received            | Driver    | V <sub>SS</sub> + 2 |     | V <sub>DD</sub> | V    |

| ٧I              |                                          | Receiver  |                     |     | ±25             |      |

| VIH             | High-level input voltage                 | Driver    | 2                   |     |                 | V    |

| VIL             | Low-level input voltage                  | Driver    |                     |     | 0.8             | V    |

| ЮН              | High-level output current                | Receiver  |                     |     | -1              | mA   |

| IOL             | High-level output current                | Receiver  |                     |     | 3.2             | mA   |

| ТА              | Operating free air temperature           | SN65C1154 | -40                 |     | 85              | °C   |

|                 | Operating free-air temperature SN75C1154 |           | 0                   |     | 70              | 5    |

SLLS151D - DECEMBER 1988 - REVISED APRIL 2003

#### DRIVER SECTION

# electrical characteristics over operating free-air temperature range, $V_{DD}$ = 12 V, $V_{SS}$ = –12 V, $V_{CC}$ = 5 V $\pm 10\%$ (unless otherwise noted)

| PARAMETER TEST CONDITIONS |                                                         |                                       |                                        |                         | MIN              | түр† | MAX   | UNIT  |    |

|---------------------------|---------------------------------------------------------|---------------------------------------|----------------------------------------|-------------------------|------------------|------|-------|-------|----|

| Vou                       | High-level output voltage                               | V <sub>IL</sub> = 0.8 V,              | RL = 3 kΩ,                             | V <sub>DD</sub> = 5 V,  | $V_{SS} = -5 V$  | 4    | 4.5   |       | V  |

| Vон                       | High-level output voltage                               | See Figure 1                          | _                                      | V <sub>DD</sub> = 12 V, | $V_{SS} = -12 V$ | 10   | 10.8  |       | v  |

| Vei                       | Low-level output voltage                                | V <sub>IH</sub> = 2 V,                | RL = 3 kΩ,                             | V <sub>DD</sub> = 5 V,  | $V_{SS} = -5 V$  |      | -4.4  | -4    | V  |

| VOL                       | (see Note 4)                                            | See Figure 1                          |                                        | V <sub>DD</sub> = 12 V, | $V_{SS} = -12 V$ |      | -10.7 | -10   | v  |

| IН                        | High-level input current                                | V <sub>I</sub> = 5 V,                 | See Figure 2                           |                         |                  |      |       | 1     | μA |

| ۱ <sub>IL</sub>           | Low-level input current                                 | $V_{I} = 0,$                          | See Figure 2                           |                         |                  |      |       | -1    | μA |

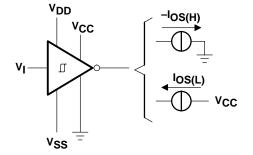

| IOS(H)                    | High-level short-circuit<br>output current <sup>‡</sup> | V <sub>I</sub> = 0.8 V,               | $V_{O} = 0 \text{ or } V_{SS},$        | See Figure 1            |                  | -7.5 | -12   | -19.5 | mA |

| IOS(L)                    | Low-level short-circuit output current <sup>‡</sup>     | V <sub>I</sub> = 2 V,                 | $V_O = 0 \text{ or } V_{DD},$          | See Figure 1            |                  | 7.5  | 12    | 19.5  | mA |

|                           | Supply ourrept from Van                                 | No load,                              |                                        | V <sub>DD</sub> = 5 V,  | $V_{SS} = -5 V$  |      | 115   | 250   |    |

| ססו                       | Supply current from VDD                                 | All inputs at 2 V                     | All inputs at 2 V or 0.8 V             |                         | $V_{SS} = -12 V$ |      | 115   | 250   | μA |

|                           | Supply ourropt from Vee                                 | No load,                              | No load,<br>All inputs at 2 V or 0.8 V |                         | $V_{SS} = -5 V$  |      | -115  | -250  |    |

| ISS                       | Supply current from $V_{SS}$                            | All inputs at 2 V                     |                                        |                         | $V_{SS} = -12 V$ |      | -115  | -250  | μA |

| r <sub>o</sub>            | Output resistance                                       | V <sub>DD</sub> = V <sub>SS</sub> = V | $V_{\rm CC} = 0$ , $V_{\rm O} = -2$    | 2 V to 2 V,             | See Note 5       | 300  | 400   |       | Ω  |

<sup>†</sup> All typical values are at  $T_A = 25^{\circ}C$ .

<sup>‡</sup> Not more than one output should be shorted at one time.

NOTES: 4. The algebraic convention, where the more positive (less negative) limit is designated as maximum, is used in this data sheet for logic levels only.

5. Test conditions are those specified by TIA/EIA-232-F.

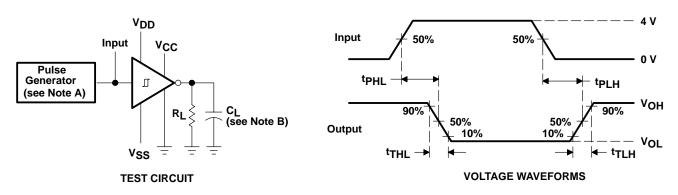

### switching characteristics, V<sub>DD</sub> = 12 V, V<sub>SS</sub> = –12 V, V<sub>CC</sub> = 5 V $\pm$ 10%, T<sub>A</sub> = 25°C (see Figure 3)

|                  |                                                                |                                           |              |      | •   | -   | •    |

|------------------|----------------------------------------------------------------|-------------------------------------------|--------------|------|-----|-----|------|

|                  | PARAMETER                                                      | TEST CO                                   | NDITIONS     | MIN  | TYP | MAX | UNIT |

| <sup>t</sup> PLH | Propagation delay time, low- to high-level output§             | $R_L = 3 \text{ to } 7 \text{ k}\Omega,$  | CL = 15 pF   |      | 1.2 | 3   | μs   |

| <sup>t</sup> PHL | Propagation delay time, high- to low-level output§             | $R_L = 3 \text{ to } 7 \text{ k}\Omega$ , | CL = 15 pF   |      | 2.5 | 3.5 | μs   |

| <sup>t</sup> TLH | Transition time, low- to high-level $\operatorname{output} \P$ | $R_L = 3 \text{ to } 7 \text{ k}\Omega,$  | CL = 15 pF   | 0.53 | 2   | 3.2 | μs   |

| <sup>t</sup> THL | Transition time, high- to low-level $\operatorname{output} \P$ | $R_L = 3 \text{ to } 7 \text{ k}\Omega,$  | CL = 15 pF   | 0.53 | 2   | 3.2 | μs   |

| <sup>t</sup> TLH | Transition time, low- to high-level output <sup>#</sup>        | $R_L = 3 \text{ to } 7 \text{ k}\Omega$ , | CL = 2500 pF |      | 1   | 2   | μs   |

| <sup>t</sup> THL | Transition time, high- to low-level output <sup>#</sup>        | $R_L = 3 \text{ to } 7 \text{ k}\Omega$ , | CL = 2500 pF |      | 1   | 2   | μs   |

| SR               | Output slew rate                                               | $R_L = 3 \text{ to } 7 \text{ k}\Omega$ , | CL = 15 pF   | 4    | 10  | 30  | V/µs |

§ tPHL and tPLH include the additional time due to on-chip slew rate control and are measured at the 50% points.

¶ Measured between 10% and 90% points of output waveform

<sup>#</sup> Measured between 3 V and –3 V points of output waveform (TIA/EIA-232-F conditions) with all unused inputs tied either high or low

SLLS151D - DECEMBER 1988 - REVISED APRIL 2003

### **RECEIVER SECTION**

#### electrical characteristics over operating free-air temperature range, $V_{DD} = 12 V$ , $V_{SS} = -12 V$ , $V_{CC}$ = 5 V $\pm$ 10% (unless otherwise noted)

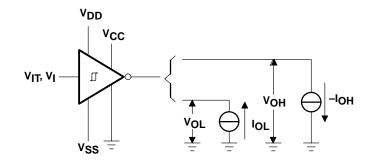

| PARAMETER                     |                                                                    | TEST CONDITIONS                                                   |                                                  |       | TYP†  | MAX  | UNIT |

|-------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------|-------|-------|------|------|

| V <sub>IT+</sub>              | Positive-going input threshold voltage                             | See Figure 5                                                      | See Figure 5                                     |       |       | 2.55 | V    |

| V <sub>IT</sub> _             | Negative-going input threshold voltage                             | See Figure 5                                                      |                                                  |       | 1     | 1.25 | V    |

| V <sub>hys</sub>              | Input hysteresis voltage<br>(V <sub>IT+</sub> – V <sub>IT–</sub> ) |                                                                   |                                                  |       | 1000  |      | mV   |

|                               |                                                                    | $V_{I} = 0.75 V$ , $I_{OH} = -20 \mu A$ ,                         | See Figure 5 and Note 6                          | 3.5   |       |      |      |

| Vari                          |                                                                    |                                                                   | V <sub>CC</sub> = 4.5 V                          | 2.8   | 4.4   |      | v    |

| VOH High-level output voltage | High-level output voltage                                          | V <sub>I</sub> = 0.75 V, I <sub>OH</sub> = −1 mA,<br>See Figure 5 | V <sub>CC</sub> = 5 V                            | 3.8   | 4.9   |      | v    |

|                               |                                                                    |                                                                   | V <sub>CC</sub> = 5.5 V                          | 4.3   | 5.4   |      |      |

| VOL                           | Low-level output voltage                                           | VI = 3 V, IOL = 3.2 mA,                                           | See Figure 5                                     |       | 0.17  | 0.4  | V    |

|                               | Lich lovel input ourrest                                           | Vj = 25 V                                                         |                                                  | 3.6   | 4.6   | 8.3  | mA   |

| ін                            | High-level input current                                           | V <sub>I</sub> = 3 V                                              |                                                  | 0.43  | 0.55  | 1    | ША   |

| L.                            |                                                                    | V <sub>I</sub> = -25 V                                            |                                                  | -3.6  | -5    | -8.3 | mA   |

| ۱L                            | Low-level input current                                            | V <sub>I</sub> = -3 V                                             |                                                  | -0.43 | -0.55 | -1   | mA   |

| IOS(H)                        | Short-circuit output<br>at high level                              | $V_{I} = 0.75 V, V_{O} = 0,$                                      | See Figure 4                                     |       | -8    | -15  | mA   |

| IOS(L)                        | Short-circuit output<br>at low level                               | $V_I=V_{CC},\qquad V_O=V_{CC},$                                   | See Figure 4                                     |       | 13    | 25   | mA   |

| laa                           | Supply current from V = =                                          | No load,                                                          | $V_{DD} = 5 V$ , $V_{SS} = -5 V$                 |       | 400   | 600  |      |

| lcc                           | Supply current from $V_{CC}$                                       | All inputs at 0 or 5 V                                            | $V_{DD} = 12 \text{ V},  V_{SS} = -12 \text{ V}$ |       | 400   | 600  | μA   |

<sup>†</sup> All typical values are at  $T_A = 25^{\circ}C$ . NOTE 6: If the inputs are left unconnected, the receiver interprets this as an input low and the receiver outputs will remain in the high state.

### switching characteristics, V\_{DD} = 12 V, V\_{SS} = –12 V, V\_{CC} = 5 V $\pm$ 10%, T\_A = 25°C

|                   | PARAMETER                                            |                         | TEST CONDITIONS     |              |   | TYP | MAX | UNIT |

|-------------------|------------------------------------------------------|-------------------------|---------------------|--------------|---|-----|-----|------|

| <sup>t</sup> PLH  | Propagation delay time,<br>low- to high-level output | C <sub>L</sub> = 50 pF, | $R_L = 5 k\Omega$ , | See Figure 6 |   | 3   | 4   | μs   |

| <sup>t</sup> PHL  | Propagation delay time,<br>high- to low-level output | C <sub>L</sub> = 50 pF, | $R_L = 5 k\Omega$ , | See Figure 6 |   | 3   | 4   | μs   |

| <sup>t</sup> TLH  | Transition time, low- to high-level output           | C <sub>L</sub> = 50 pF, | $R_L = 5 k\Omega$ , | See Figure 6 |   | 300 | 450 | ns   |

| t⊤HL              | Transition time, high- to low-level output           | C <sub>L</sub> = 50 pF, | $R_L = 5 k\Omega$ , | See Figure 6 |   | 100 | 300 | ns   |

| <sup>t</sup> w(N) | Duration of longest pulse<br>rejected as noise‡      | C <sub>L</sub> = 50 pF, | $R_L = 5 k\Omega$   |              | 1 |     | 4   | μs   |

<sup>‡</sup> The receiver ignores any positive- or negative-going pulse that is less than the minimum value of t<sub>w(N)</sub> and accepts any positive- or negative-going pulse greater than the maximum of  $t_{W(N)}$ .

SLLS151D - DECEMBER 1988 - REVISED APRIL 2003

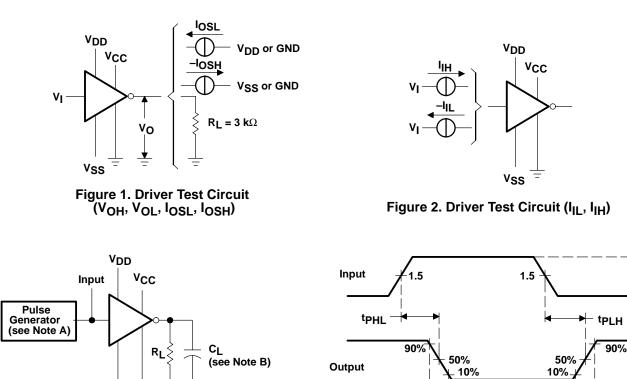

### PARAMETER MEASUREMENT INFORMATION

TEST CIRCUIT

Vss =

-

**VOLTAGE WAVEFORMS**

#### Figure 3. Driver Test Circuit and Voltage Waveforms

tTHL →

Figure 4. Receiver Test Circuit (IOSH, IOSL)

3 V

0 V

VOH

VOL

– <sup>t</sup>TLH

SLLS151D - DECEMBER 1988 - REVISED APRIL 2003

#### Figure 6. Receiver Test Circuit and Voltage Waveforms

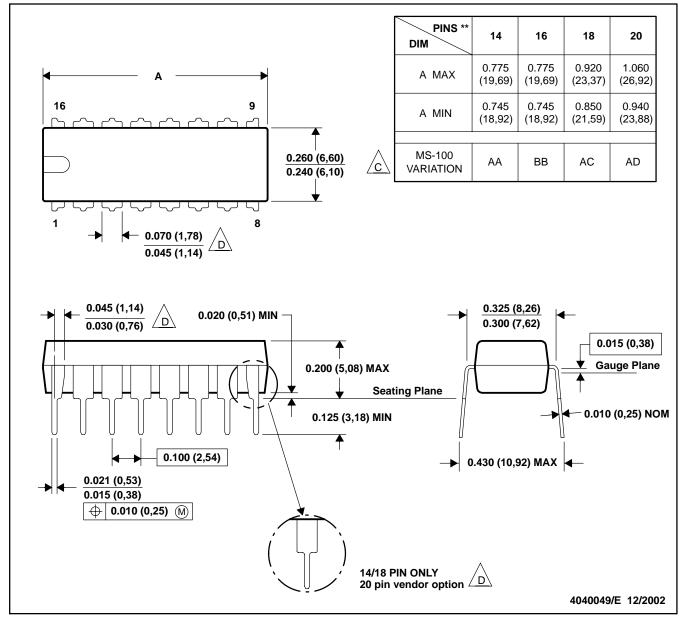

MPDI002C - JANUARY 1995 - REVISED DECEMBER 20002

#### N (R-PDIP-T\*\*)

PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

#### NOTES: A. All linear dimensions are in inches (millimeters).

/д.

B. This drawing is subject to change without notice.

/C Falls within JEDEC MS-001, except 18 and 20 pin minimum body Irngth (Dim A).

The 20 pin end lead shoulder width is a vendor option, either half or full width.

# **MECHANICAL DATA**

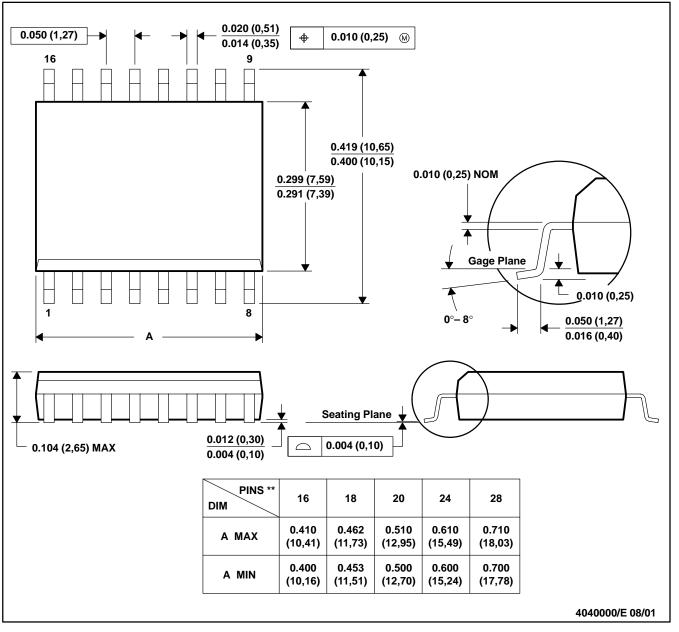

MSOI003E - JANUARY 1995 - REVISED SEPTEMBER 2001

#### PLASTIC SMALL-OUTLINE PACKAGE

DW (R-PDSO-G\*\*) 16 PINS SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013

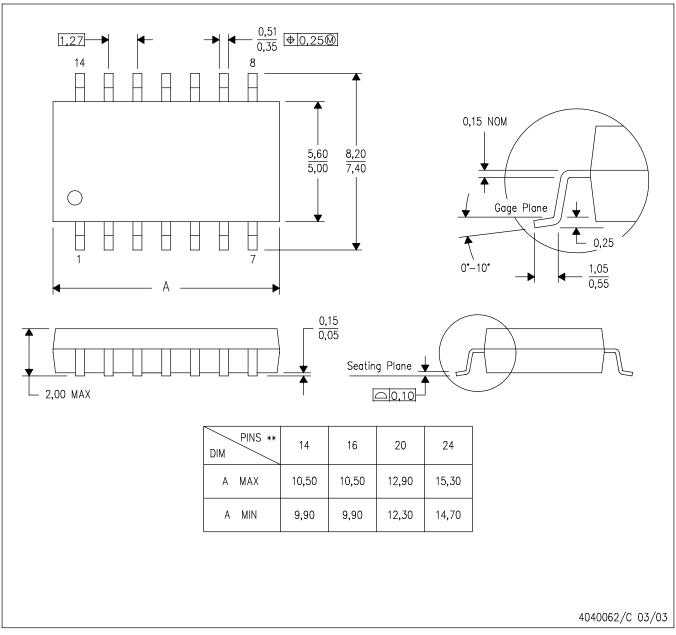

NS (R-PDSO-G\*\*) 14-PIN SHOWN

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion, not to exceed 0,15.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated