# ERRATA TO THE MSP50C6xx USER'S GUIDE

## (TEXAS INSTRUMENTS LITERATURE NO. SPSU014, JANUARY 2000)

This document contains corrections and additions to information in the MSP50C6xx User's Guide (TI Literature Number SPSU014, January 2000).

#### MSP50C6xx User's Guide Text Errors:

- 1. Page 2–39 of the user's guide, the 5th sentence is: **Not** that the reduced power mode... This should be: **Note** that the reduced power mode... (i.e., Not becomes Note)

- 2. Page 4–24, Table 4.11, Class 4, Subclass C, instruction description should be *Memory references with long constant fields operating on Rx*

- 3. Page 4–24, Table 4.11, Class 4, Subclass D, instruction description should be *Memory references with R5 operating on Rx*

- 4. On page 5–27, Section 5.6.5, know should be known

### MSP50C6xx User's Guide Table and Figure Errors:

| Errors        | Page(s) | Table(s) or Figure(s) | Correction                                          |  |  |  |  |  |  |  |

|---------------|---------|-----------------------|-----------------------------------------------------|--|--|--|--|--|--|--|

| INITZ         | A-7     | Table A-1             | RESET                                               |  |  |  |  |  |  |  |

| X1            | 1–11    | Table 1–2             | OSCIN                                               |  |  |  |  |  |  |  |

|               | 1–12    | Figure 1–4            | 7                                                   |  |  |  |  |  |  |  |

|               | 7–3     | Table 7–1             | 7                                                   |  |  |  |  |  |  |  |

|               | A-7     | Table A-1             | $\neg$                                              |  |  |  |  |  |  |  |

|               | B-8     | Table B-1             | 7                                                   |  |  |  |  |  |  |  |

|               | C-6     | Table 1               | 7                                                   |  |  |  |  |  |  |  |

| X2            | 1–11    | Table 1–2             | OSCOUT                                              |  |  |  |  |  |  |  |

|               | 1–12    | Figure 1–4            | 7                                                   |  |  |  |  |  |  |  |

|               | 7–3     | Table 7–1             | 7                                                   |  |  |  |  |  |  |  |

|               | A-7     | Table A-1             | 7                                                   |  |  |  |  |  |  |  |

|               | C-6     | Table 1               | 7                                                   |  |  |  |  |  |  |  |

| X2 (Pin#13)   | B-8     | Table B-1             | PLL                                                 |  |  |  |  |  |  |  |

| PLL (Pin#15)  | B-8     | Table B-1             | OSCOUT                                              |  |  |  |  |  |  |  |

| NC (Pin#31)   | B-8     | Table B-1             | VCC                                                 |  |  |  |  |  |  |  |

| GND1 (Pin#48) | B-8     | Table B-1             | GND2                                                |  |  |  |  |  |  |  |

| SCAN_OUT      | A-7     | Table A-1             | SCANOUT                                             |  |  |  |  |  |  |  |

|               | B-8     | Table B-1             | 7                                                   |  |  |  |  |  |  |  |

| SCAN_IN       | B-8     | Table B-1             | SCANIN                                              |  |  |  |  |  |  |  |

| SCAN_CLK      | B-8     | Table B-1             | SCANCLK                                             |  |  |  |  |  |  |  |

| PG0           | B-4     | Figure B–1            | Replace Figure B–1 with Figure 1 in this document   |  |  |  |  |  |  |  |

| OSCIN, OSCOUT | 1–10    | Table 1–1             | Exchange pad numbers (See Table 1 in this document) |  |  |  |  |  |  |  |

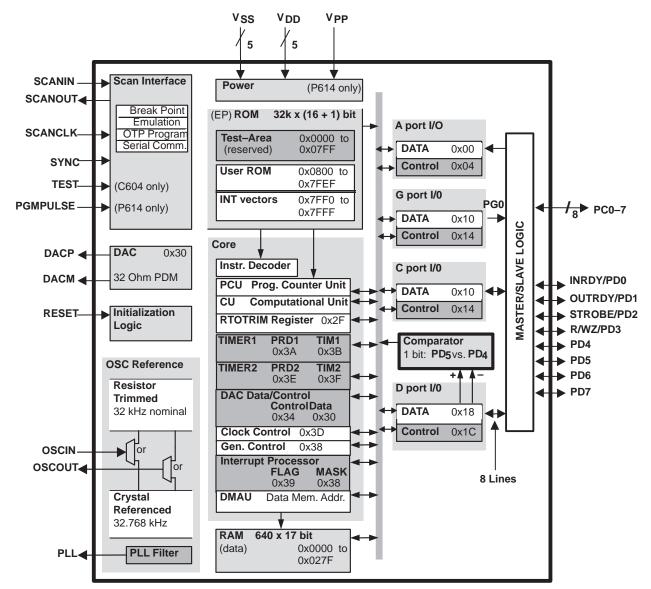

FIGURE 1. Revised MSP50C604 Block Diagram

TABLE 1. Revised MSP50C6xx Pad Numbers

| SIGNAL                       | PAD NUMBER | I/O | DESCRIPTION                    |  |  |  |  |  |

|------------------------------|------------|-----|--------------------------------|--|--|--|--|--|

| Oscillator Reference Signals |            |     |                                |  |  |  |  |  |

| OSCOUT                       | 65         | 0   | Resistor/crystal reference out |  |  |  |  |  |

| OSCIN                        | 66         | 1   | Resistor/crystal reference in  |  |  |  |  |  |

#### **Missing Instruction**

Add this instruction between pages 4–132 and 4–133.

## MULR Multiply (Rounded) With No Data Transfer

## **Syntax**

| [label] | name | src    | Clock, clk | Word, w | With RPT, clk | Class |

|---------|------|--------|------------|---------|---------------|-------|

|         | MULR | {adrs} | Table 4    | -0-46   | Table 4-0-46  | 5     |

**Execution**  $PH,PL \Leftarrow MR * src$

$PC \Leftarrow PC + 1$

Flags Affected TAG bit is set accordingly

Opcode

| Instructions | 16 | 15                                                                | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------|----|-------------------------------------------------------------------|----|----|----|----|----|---|---|------|---|---|---|---|---|---|---|

| MULR [adrs]  | 1  | 1                                                                 | 0  | 1  | 1  | 1  | 0  | 1 | 0 | adrs |   |   |   |   |   |   |   |

|              | х  | dma16 (for direct) or offset16 (long relative) (see Section 4.13) |    |    |    |    |    |   |   |      |   |   |   |   |   |   |   |

**Description** Perform multiplication of multiply register (MR) and effective data memory value, add

08x00 to the product. The 16 MSBs of the 32-bit product are stored in the product high

(PH) register. No status change. Round upper 16 bits.

See Also MULS, MUL, MULAPL, MULSPLS, MULTPL, MULTPLS, MULAPL

Example MULR \*R0++

Multiply **MR** with the content of data memory location pointed by **R0** and store the rounded upper 16 bits of the result in **PH**. Increment **R0** by 2.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated