#### VOICE SYNTHESIS LSI T6803

#### 1. General Description

The T6083 is a single chip PARCOR voice synthesis LSI with a built-in voice data ROM (64K bits) and low-pass filter circuit.

#### 2. Featrures

- o PARCOR system 10 kHz sampling voice output.

- o Built-in 64K bits ROM for voice data.

- o The dedicated ROM can be externally connected. (Max. 2M bits)

- o Max. 63 speech phrases are selectable.

(64 or more phrases can be specified when a microcomputer is connected.)

- o Various bit rates are selectable according to quality of sound (9.8, 5.6 and 2.5 Kbps).

- o 3 steps of speech speed can be changed over.

- o Built-in butterworth three stage low-pass filter.

- o 5V single power supply.

- Low current consumption by C-MOS process (2mA when a low-pass filter is used.)

- o Power standby mode available (3 µA).

- \* PARCOR is the voice analysing and synthesizing method depend by Nippon Telegram and Telephone Public Corporation (NTT). Toshiba's voice synthesizing LSI has been developed under the direction of NTT. Patent Nos. are No.754418, 876024 and 1045100.

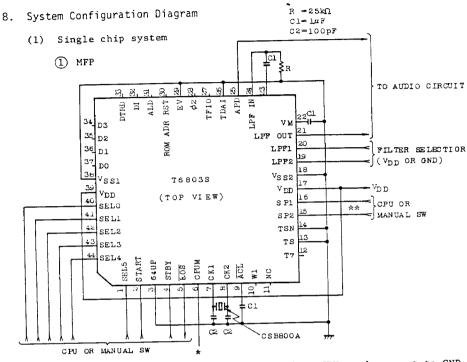

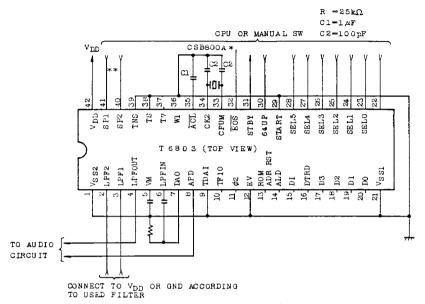

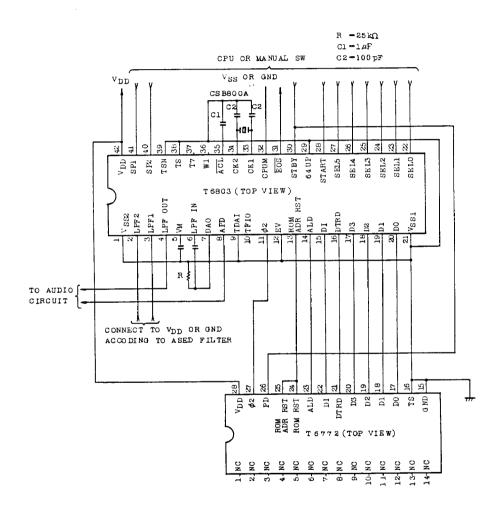

3. Examples of Voice Synthesizing System Configuration

When a voice synthesizing system is composed using the T6803, there are two types of configuration; CPU control type using a microcomputer, etc. and manual control type using SW, etc. In both types, connection of dedicated mask ROM is possible. Refer to (3).

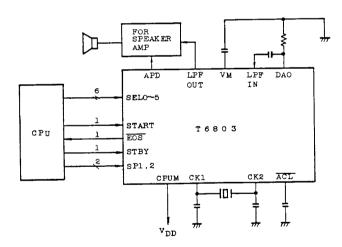

### (1) CPU control type

The basic configuration is the 2 chips configuration of CPU + T6803.

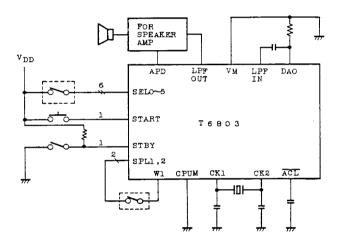

## (2) Manual control type

The configuration is a minimum system and the 1 chip configuration of T6803.

### 4. LSI's Specifications

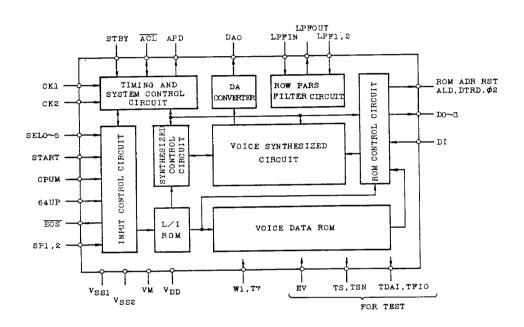

(1) Block Diagram

(2) Specifications for voice synthesizer

System PARCOR

Number of arithmetic bits 15 bits

Sampling frequency 10 kHz

Interpalating calculation Available

Frame length 10 mS/20 mS

(Selectable for every phrase .... L/I ROM)

Since the T6803 has the built-in filter circuit, voice can be output only when a speaker and speaker driving amplyfier are externally mounted to the voice output system.

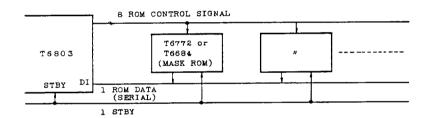

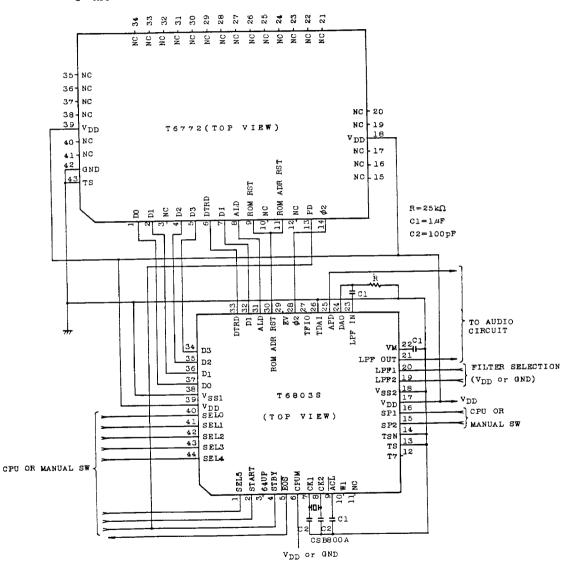

When the capacity (64K bits) of built-in ROM of the T6803 is insufficient in (1) and (2), it is possible to expand the capacity by externally mounted ROM.

## (3) Expansion of capacity by dedicated MASK ROM

T6772: 64K bit dedicated mask ROM for voice

(connectable up to max. 8 pieces)

T6684 : 128K bit dedicated mask ROM for voice

(connectable up to max. 16 pieces)

Circuit system

|     | Bit/frame                 |         | 50 bit/56  | bit/98   | bit  |      |      |      |

|-----|---------------------------|---------|------------|----------|------|------|------|------|

|     |                           | (sele   | ctable for | every p  | hras | se   | L/I  | ROM) |

|     | Sound source              |         | 2 kinds    | ( "      | rt   | )    |      |      |

|     | Number of filter stages   |         | 8 stages/  | 10 stage | s (  | **   | ")   |      |

|     | Synthesized sound         |         | Melody/vo  | ice      | (    | "    | ")   |      |

|     | DA converter              |         | 9 bits vo  | ltage ty | pe   |      |      |      |

|     |                           |         |            |          |      |      |      |      |

|     |                           |         |            |          |      |      |      |      |

| (3) | Specifications for low-pa | ss filt | er         |          |      |      |      |      |

|     | Туре                      | Butter  | worth      |          |      |      |      |      |

|     | No. of filter orders      | 3 stag  | e of LPF   |          |      |      |      |      |

|     | Filter characteristic     | 2 kind  | s (set up  | through  | the  | exte | rnal |      |

|     |                           |         | terminal   | .)       |      |      |      |      |

|     | Cut off frequency         | 2 kind  | s (        | 11       | )    |      |      |      |

Switched capacitor

#### (4) L/I (LABEL/INDEX) ROM

L/I ROM is a ROM used to set up actual start address of DATA ROM, synthesizing conditions, and internal/external ROM designation, corresponding to phrase code (LABEL) selected by SELO to 5 terminals, and the following data are internally set up automatically in the indirect designation mode (64UP = "L"):

Address 20 bits

Synthesizing conditions Following 5 data can be set up:

① Frame length (10ms or 20ms)

② Bits/frame (98 or 56 or 50)

③ Voice source (A or B)

④ Filter stage (10 or 8)

⑤ Melody (Melody or voice)

ROM designation Built-in/externally mounted ROM

The above-mentioned INDEX data can be designated to all combinations of SELO to 5 terminals (max. 63 ... 1 to 63 except 0).

## (5) Vioce data ROM

PARCOR analyzed voice data (64K bits) have been set.

[Note] L/I ROM and voice data ROM are MASK ROMs and contents desired by user will be incorporated at time of development.

### 5. Operational Description

- (1) Speaking phrase setting and speaking start instruction There are two methods available for setting speaking phrases and directing start of speaking.

- 1 Indirect setting (64UP = "L" level)

- o This is a method to use L/I ROM which is provide in the T6803. speaking phrases are set by combinatin of SELO to 5 (1-63) terminals and when the speaking start instruction START is input, the speaking of set phrases is started.

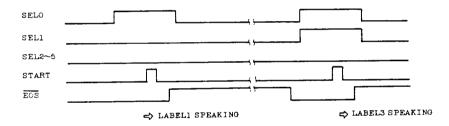

[Example 1] The speakings of LABEL 1 and LABEL 3

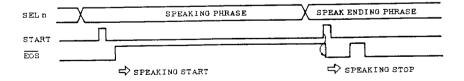

- o There is the  $\overline{\text{EOS}}$  terminal for an output signal to monitor whether this LSI is speaking or the speaking ended. This  $\overline{\text{EOS}}$  terminal becomes "H" level when the speaking START signal is input and becomes "L" level when the speaking ends.

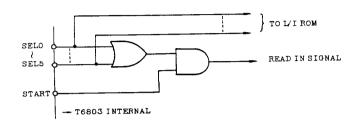

- o SELO to 5 and START input of T6803 are as illustrated below. It is possible to make the speaking using only one of the SELO to 5 with the START terminal set at "H" level.

[Input]

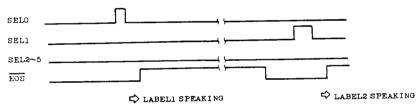

### [Example 2]

Pharase setting by SELO to 5 and speaking start (START input

= "H" level)

- o Example 1 is valid when SELO to 5 data lines are used commonly together with other peripheral devices, while in Example 2, SELO to 5 become the exclusive use data lines but it is possible to reduce number of lines to be connected by one line if the START terminal is set at "H" level when connecting to CPU.

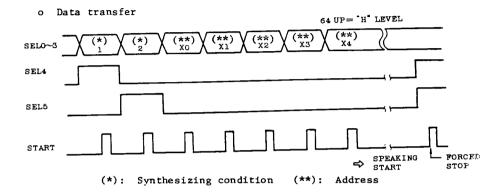

- 2 Direct setting (64UP = "H" level)

- o If number of phrases is over 63 phrases, it becomes possible to directly set synthesizing conditions and start address when the 64 UP terminal is set at "H" level.

- o In case of the direct setting, data are set at the SELO to 3 terminals and written T6803 by the START signal, and types of data to be transferred (synthesizing conditions, start address, forced stop) are designated by the SEL4 and SEL5 terminals.

- o Combinations are as shown in the following tables:

| SEL4 | SEL5 | Kinds of Data             | SEL3              | SEL2                 | SEL1   | SEL0             |

|------|------|---------------------------|-------------------|----------------------|--------|------------------|

| 0    | 0    | Start address             | MSB               |                      |        | LSB              |

| 1    | 0    | Synthesizing conditions 1 | Voice<br>source   | ROM De-<br>signation | Melody | Bit/<br>Frame(1) |

| 0    | 1    | Synthesizing conditions 2 | Bit/<br>Frame (2) | Frame<br>length      | 0      | Filter<br>stages |

| 1    | 1    | Forced<br>stop            | *                 | *                    | *      | *                |

1 : "H" Level

\* : Don't care

0 : "L" Level

| Data<br>Input Pin | 0                 | 1                 |

|-------------------|-------------------|-------------------|

| SEL0              | 98 bit            | 98 bit            |

| SEL1              | Voice source      | Melody            |

| SEL2              | Built-in<br>ROM   | External<br>ROM   |

| SEL3              | Voice<br>source A | Voice<br>source B |

Synthesizing condition 1

| Data<br>Input Pin | 0         | 1        |

|-------------------|-----------|----------|

| SEL0              | 10 stages | 8 stages |

| SEL1              | ><        | $\times$ |

| SEL2              | 20 ms     | 10 ms    |

| SEL3              | 56 bit    | 50 bit   |

Synthesizing condition 2

\* When 98 bit is designated in Bit/Frame (1), Bit/Frame (2) (50/56) becomes invalid.

- o Either synthesizing condition 1 or 2 can be first set. addition, when synthesizing conditions were set several times, the conditions that have been finally set become valid.

- o When transferring address data, divide 4-bit data into 5 times and transfer them from XO to X4 successively. If synthesizing condition have been set during transfer of address data, after the forced stop, transfer address data again from the first.

- o The synthesizing conditions are initialized (the state where synthesizing condition data become zero) at time of ACL or STBY. Except ACL and STBY, they are held until they are written again (including the indirect setting).

- o Speaking is automatically made after 5 times of address transfer.

- o The forced stop can be input in any state.

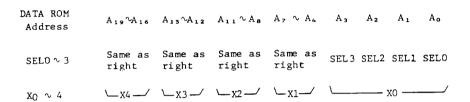

- o Addresses X<sub>0</sub> to X<sub>4</sub> correspond to DATA ROM addresses as follows:

(2) Forced stop of speaking

There are 3 methods to stop voice speaking by force.

- 1 Forced stop at time of indirect setting (64 UP = "L" level)

- o It is possible to switch speaking phrases by force.

Therefore, when the speaking end phrase is set at one of 63 LABELS, it is possible to effect the forced stop by inputting this LABEL.

INTEGRATED CIRCUIT

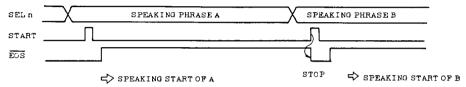

Further, the forced change of a speaking phrase is possible by starting a desired phrase.

Change speaking prase A with B

- Forced stop at time of direct setting (64 UP = "H" level)

- o As described in the above (2)-2, the forced stop of speaking at time of the direct setting is possible when SEL4 and SEL5 are set at "H" level and the START signal is input.

- o As the forced change of a speaking phrase in the direct setting mode is impossible, to make the speaking phrase change, once perform the forced stop and then, start the speaking.

- Speaking stop by ACL input

The ACL terminal is a terminal used to initialize the T6803 system at time of POWER ON by a capacitor connected to this terminal and an internally provided resistor. The T6803 is also initialized when a "L" level signal is input to this terminal from the outside. It is therefore possible to stop the speaking by inputting a "L" level signal to this terminal during the speaking.

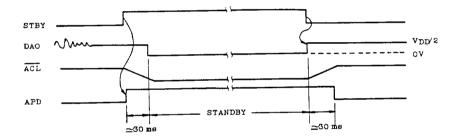

## (3) Standby operation

- o The T6803 has the standby function. When a "H" level signal is input to the STBY terminal, the T6803 is put in the standby mode, which can be released by inputting a "L" level signal.

- o The T6803 outputs APD (Audio Power Down) signal to control POWER ON/OFF of an external audio circuit, interlocking with the standby mode. This signal is set at "H" level in the standby mode and at "L" level when the standby mode is released.

o APD output becomes "H" level at the same time when STBY input becomes "H" level, but DAO output becomes "L" level  $\simeq$  30ms later.

Further, DAO output becomes  $V_{DD/2}$  level at the same time when STBY input becomes "L" level, but APD output becomes "L" level  $\simeq 30$  ms later.

o ACL input becomes "L" level in the standby mode.

o As the T6803 is initialized for 30ms after the standby mode is released, no external control is accepted during this period.

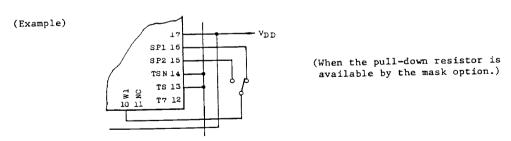

Note: When a pul-down resistor is provided in SELO to 5 and START input terminals by mask option, SELO to 5 and START input terminals should be set at OPEN or GND level in the standby mode.

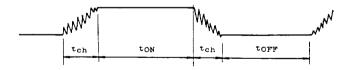

## (4) Chattering preventing circuit

o In the manual control mode (CPUM = "L" level), the chattering preventing circuit is actuated to prevent malfunction of the switches connected to the START input and SELO to 5 terminals.

The chattering preventing time is about 20ms and when the switches are stably kept at "H" level for about 60ms after they are depressed, the speaking is started.

If the switches are onced released and depressed again, they should be kept at "L" level stably for about 60ms.

Switch input

o In the CPU control mode (CPUM= "H" level), the chattering preventing circuit is not actuated, enabling the pulse operation.

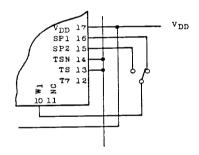

## (5) Speech speed

Speech speed is changable by setting SP1 or SP2.

Slow speed = 1.24 × normal speed.

Fast speed =  $0.76 \times normal$  speed.

## a) manual control

|     | slow | normal | fast |

|-----|------|--------|------|

| SP1 | Wl   | open   | open |

| SP2 | open | open   | Wl   |

Note: SP1 and SP2 is built-in pull down register by

mask option.

#### b) CPU control

|     | slow              | normal | fast              |

|-----|-------------------|--------|-------------------|

| SP1 | $v_{\mathrm{DD}}$ | GND    | GND               |

| SP2 | GND               | GND    | $v_{\mathrm{DD}}$ |

Note: SP1 and SP2 is not

built-in pull down

registor by mask option.

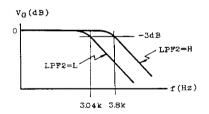

#### 6. Low-pass Filter

The T6803 has built-in butterworth three stage low- pass filters used by the latest switched capacitor technology and it is possible to output synthesized sound by connecting a speaker amplifier circuit externally.

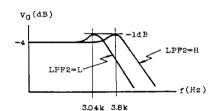

### (1) Filter characteristic selecting function

The filter built in the T6803 have four kinds of characteristics. Any one of the characteristics can be selected by setting LPF1 and LPF2 terminals.

LPF1: Filter shape change-over terminal

LPF2: Cut-off frequency change-over terminal

Filter type-1 (LPF1="L" level) Filter type-2 (LPF1="H" level)

(The cut-off frequency shown is a value when oscillation frequency of T6803 is 800 kHz.)

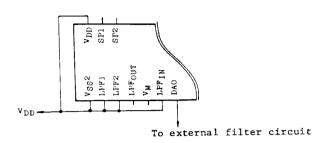

#### (2) When no built-in filter is used

Since the power supply ( $V_{SS}^2$ ) for the low-pass filters built-in the T6803 separated from the power supply ( $V_{SS}^2$ ) for the digital synthesizer, when a filter circuit is connected extermely as illustrated below, it becomes possible to save power of the built-in low-pass filters.

With LPF1  $\,$  LPF1N and  $\rm V_{SS}2$  connected to  $\rm V_{DD},$  open  $\rm LPF_{OUT}$  and  $\rm V_{M}.$

(It is not feasible to save power of the digital synthesizer and use the low-pass filters only.)

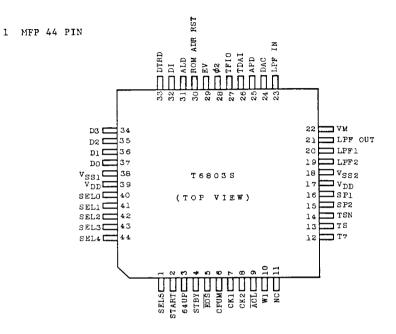

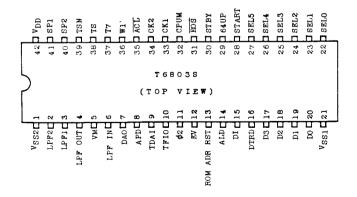

## 7. Pin Description & Pin Connection

### (1) Pin Description

|                  | PIN NO.       |               | CONFIGURATION |                               |                                              |  |  |

|------------------|---------------|---------------|---------------|-------------------------------|----------------------------------------------|--|--|

| PIN NAME         | DIP<br>42 PIN | MFP<br>44 PIN | 1/0           | PULL-UP/<br>-DOWN<br>RESISTOR | DESCRIPTION                                  |  |  |

| V <sub>SS2</sub> | 1             | 18            | (*)           | -                             | 0V                                           |  |  |

| LPF2             | 2             | 19            |               |                               | Change-over input of low-pass filter         |  |  |

| LPF1             | 3             | 20            | Input         | without                       | characteristic                               |  |  |

| LPF OUT          | 4             | 21            | Output        | -                             | Low-pass filter output                       |  |  |

| VΜ               | 5             | 22            | Output        |                               | Reference voltage output for low-pass filter |  |  |

| LPF IN           | 6             | 23            | Input         | without                       | Low-pass filter input                        |  |  |

| DA0              | 7             | 24            | DAC<br>Output | -                             | D/A converter output                         |  |  |

| APD              | 8             | 25            | Output        | -                             | Power down output for external audio circuit |  |  |

| TDAI             | 9             | 26            | Input         | without                       | Test input                                   |  |  |

| TFIO             | 10            | 27            | Output        | -                             | Test output                                  |  |  |

| ø2               | 11            | 28            | Output        | -                             | Clock pulse to external ROM                  |  |  |

| EV               | 12            | 29            | Input         | Pull-down                     | Input terminal for test                      |  |  |

| ROM ADR RST      | 13            | 30            |               |                               | Address reset output to external ROM         |  |  |

| ALD              | 14            | 31            | Output        | _                             | Start address set pulse to "                 |  |  |

| DI               | 15            | 32            | Input         | Pull-up                       | Data input from external ROM                 |  |  |

| DTRD             | 16            | 33            |               |                               | Data read pulse from external ROM            |  |  |

| D3               | 17            | 34            |               |                               |                                              |  |  |

| D2               | 18            | 35            | Output        | _                             | Address data output from external ROM        |  |  |

| Dl               | 19            | 36            |               |                               |                                              |  |  |

| DO               | 20            | 37            | ]             |                               |                                              |  |  |

| VSS1             | 21            | 38            | (*)           | -                             | ov                                           |  |  |

| SELO             | 22            | 40            |               |                               |                                              |  |  |

| SELL             | 23            | 41            |               |                               |                                              |  |  |

| SEL2             | 24            | 42            |               |                               |                                              |  |  |

| SEL3             | 25            | 43            | Input         |                               | Phrase selection input                       |  |  |

| SEL4             | 26            | 44            |               |                               |                                              |  |  |

| SEL5             | 27            | 1             |               |                               |                                              |  |  |

(\*): Power Supply

|          | PIN NO.       |               | CONFI        | GIRATION                      | DESCRIPTION                                        |  |

|----------|---------------|---------------|--------------|-------------------------------|----------------------------------------------------|--|

| PIN NAME | DIP<br>42 PIN | MFP<br>44 PIN | 1/0          | PULL-UP/<br>-DOWN<br>RESISTOR |                                                    |  |

| START    | 28            | 2             |              | *                             | Speaking start instruction input                   |  |

| 64 UP    | 29            | 3             | T            | without                       | Direct/indirect designation mode change-over input |  |

| STBY     | 30            | 4             | Input        | WILHOUL                       | Power down input                                   |  |

| EOS      | 31            | 5             | Output       | -                             | END OF SPEECH Output                               |  |

| CPUM     | 32            | 6             | Input        | without                       | Chattering prevention YES/NO change-over input     |  |

| CK1      | 33            | 7             | Input        | without                       | Ceramic vibrator connecting pin                    |  |

| CK2      | 34            | 8             | Output       | -                             |                                                    |  |

| ACL      | 35            | 9             | 1/0          | -                             | Power ON auto clear, Schmitt input                 |  |

| Wl       | 36            | 10            |              |                               | Timing signal output                               |  |

| т7       | 37            | 12            | Output       | _                             | Test output                                        |  |

| TS       | 38            | 13            |              | Pull-down                     | Test input                                         |  |

| TSN      | 39            | 14            | Input        | rull-down                     | 1656 Imput                                         |  |

| SP2      | 40            | 15            | Input        | *                             | Speaking speed change-over input                   |  |

| SPl      | 41            | 16            | '            |                               |                                                    |  |

| VDD      | 42            | 17, 39        | Power supply | -                             | +5V                                                |  |

\* Pull-down resistor Yes/No can be designated by the mask option.

| Option Designation | START, SELO ∿ 5 | SP1, 2    |

|--------------------|-----------------|-----------|

| No designation     | No              | No        |

| Option 1           | No              | Pull-down |

| Option 2           | Pull-down       | No        |

| Option 3           | Pull-down       | Pull-down |

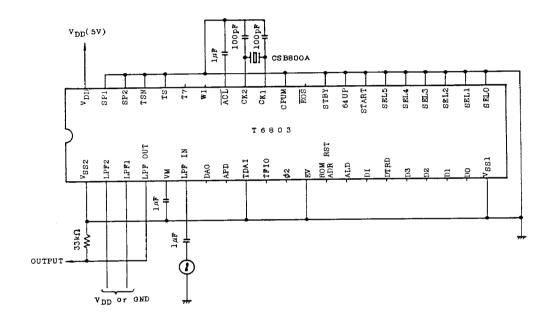

#### (2) PIN CONNECTION

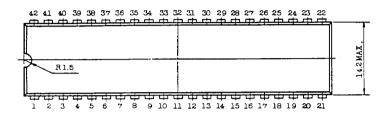

2 DIP 42 PIN

- $\star$  Connect to  $\textsc{V}_{\mbox{\scriptsize DD}}$  when the system is connected to CPU, and connect to GND when connected to MANUAL SW.

- \*\* Speed change-over can be also set externally.

- Note 1. Position the ceramic vibrator and capacitor, which are to be connected to CK1 and CK2 terminals of T6803 at locations very close to CK1 and CK2.

- 2. Do not use terminals as a reley terminal except NC terminal.

2 DIP

- $\dot{\mathtt{x}}$  Connect to  $\mathtt{V}_{\mathrm{DD}}$  when the system is connected to CPU, and connect to GND when connected to MANUAL SW.

- \*\* Speed change-over can be also set externally.

(Example)

(When the pull-down resistor is available by the mask option.)

- Note 1. Position the ceramic vibrator and capacitor, which are to be connected to CK1 and CK2 terminals of T6803 at locations very close to CK1 and CK2.

- 2. Do not use terminals as a reley terminal except NC terminal.

#### (2) ROM Expansion System

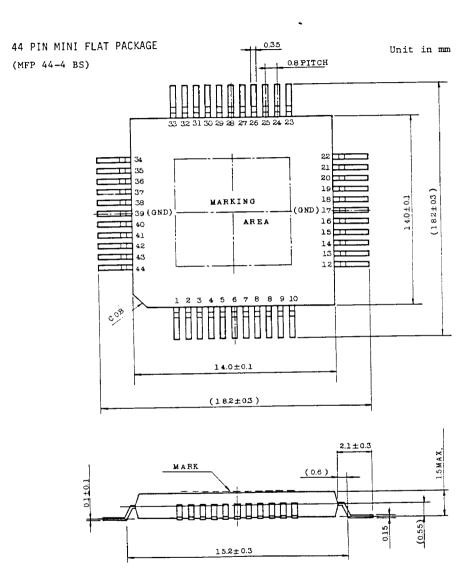

1 MFP

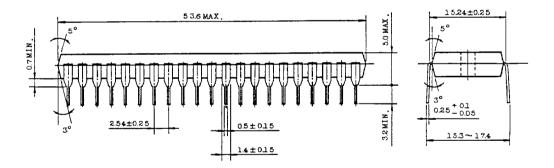

(2) DIP

Unit in mm

(Note) Lead pitch is 2.54 and tolerance is  $\pm 0.25$  against theoretical center of each lead that is obtained on the basis of No.1 and No.42 leads.

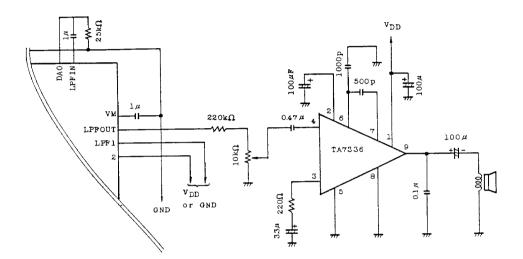

9. APPLICATION OF AUDIO CIRCUIT

## 10. ELECTRICAL CHARACTERISTICS

(1) ABSOLUTE MAXIMUM RATINGS (VSS1=VSS2=OV)

| ITEM                    | RATING                                                                                | UNIT                                                                                                                                                                                                                  |

|-------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supply Voltage          | $V_{SS}-0.3 \sim V_{SS}+6.0$                                                          | V                                                                                                                                                                                                                     |

| Input Voltage           | $V_{SS}-0.3 \sim V_{DD}+0.3$                                                          | V                                                                                                                                                                                                                     |

| Ouptut Voltage          | $V_{SS}-0.3 \sim V_{DD}+0.3$                                                          | V                                                                                                                                                                                                                     |

| Storage Temperature     | -55 ∿ 125                                                                             | °C                                                                                                                                                                                                                    |

| Operating Temperature   | -10 ∿ 55                                                                              | °C                                                                                                                                                                                                                    |

| Lead Temperature 10 sec | 260                                                                                   | °C                                                                                                                                                                                                                    |

|                         | Supply Voltage Input Voltage Ouptut Voltage Storage Temperature Operating Temperature | Supply Voltage $V_{SS}$ -0.3 $\sim V_{SS}$ +6.0 Input Voltage $V_{SS}$ -0.3 $\sim V_{DD}$ +0.3 Ouptut Voltage $V_{SS}$ -0.3 $\sim V_{DD}$ +0.3 Storage Temperature $-55 \sim 125$ Operating Temperature $-10 \sim 55$ |

(2) DC CHARACTERISTICS ( $V_{SS1}=V_{SS2}=0V$ ,  $V_{DD}=5V$ , Ta=25°C Unless otherwise specified limit value MIN. and MAX. values are defined by their absolute values.)

|                     |                                  |                             |                                         | LI                   | MITS |                 | UNIT     |

|---------------------|----------------------------------|-----------------------------|-----------------------------------------|----------------------|------|-----------------|----------|

| SYMBOL              | PARAMETER                        | APPLIED TERMINAL            | CONDITIONS                              | MIN.                 | TYP. | MAX.            | UNIT     |

| $V_{\mathrm{DD}}$   | Supply Voltage                   | $v_{ m DD}$                 | -                                       | 3.9                  | 5    | 5.7             | v        |

| I <sub>DDO(1)</sub> | Supply Current (1)               | $v_{\mathrm{DD}}$           | V <sub>DD=5</sub> V                     |                      | 1.2  | 2.7             | mA       |

| I <sub>DDO(2)</sub> | Supply Current (2)               | V <sub>DD</sub>             | V <sub>DD</sub> =5V                     |                      | 0.7  | 1.5             | mA       |

| I <sub>DDS</sub>    | Supply Current during power down | V <sub>DD</sub>             | V <sub>DD</sub> =5V                     | -                    | -    | 3               | μА       |

| fosc                | Frequency range                  | CK1                         | $V_{DD}=3.9 \sim 5.7V$                  | 760                  | 800  | 840             | kHz      |

| VIH                 | High level input voltage         | Except ACL, LPFIN           | $V_{DD}=3.9 \sim 5.7V$                  | V <sub>DD</sub> -0.8 |      | v               | V        |

| V <sub>IL</sub>     | Low level input voltage          | Except ACL, LPFIN           | V <sub>DD</sub> =3.9 ∿ 5.7V             | 0                    | -    | 0.8             | <u> </u> |

| R <sub>PD(1)</sub>  | Pull down registor(1)            | SP1, SP2 *2                 | -                                       |                      | 500  | -               | kΩ       |

| R <sub>PD</sub> (2) | Pull down registor(2)            | SEL0 ~ 5, START *2          |                                         | -                    | 30   |                 | kΩ       |

| R <sub>PU</sub>     | Pull up registor                 | DI                          | -                                       | -                    | 500  |                 | kΩ       |

| I <sub>IH</sub>     | High level input current         | Except TS, TSN,<br>EV *3    | V <sub>IN</sub> =V <sub>DD</sub>        | -                    | _    | 5               | μA       |

| I <sub>IL</sub>     | Low level input current          | -                           | V <sub>IN</sub> =OV                     | -                    | -    | -5              | μА       |

| I <sub>OH</sub>     | High level output current        | Except DAO, ACL, LPFOUT CK2 | V <sub>OUT</sub> =V <sub>DD</sub> -0.4V | -0.4                 | _    | -               | mA       |

| I <sub>OL</sub>     | Low level output current         | n                           | V <sub>OUT</sub> =0.4V                  | 0.4                  | -    | -               | m.A      |

| V <sub>OUT</sub>    | D/A converter output voltage     | DAO                         | No load                                 | 0                    |      | v <sub>DD</sub> | v        |

| R <sub>OUT</sub>    | D/A converter impedance          | DAO                         |                                         | 35                   | 50   | 65              | kΩ       |

<sup>\*1</sup> Condition of low pass filter is not active. ( $V_{\rm SS2}=V_{\rm DD}$ )

<sup>\*2</sup> Apply only pull down registor is built-in.

<sup>\*3</sup> Apply only pull down registor is not built-in.

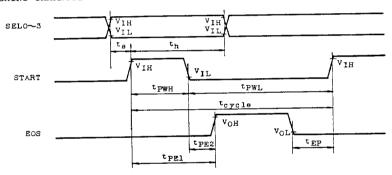

(3) AC CHARACTERISTICS (VSS1=VSS2=0V, VDD=5V, CL=15pF, Ta=-10  $\sim$  55°C) Unless otherwise CPUM=High level, 64UP=Low level)

|                 |                              | O CANTO TIME CALL                     | MIN. | TYP. | MAX. | UNIT |

|-----------------|------------------------------|---------------------------------------|------|------|------|------|

| SYMBOL          | PARAMETER                    | CONDITION                             | MIN. | 111. | III. |      |

| tPWH            | High level START pulse width |                                       | 4    |      |      | μs   |

| tPWL            | Low level START pulse width  | 64UP="H"                              | 24   |      |      | μs   |

| tcycle          | START cycle time             | 64UP="H"                              | 32   |      |      | μs   |

| ts              | Data set up time             | _                                     | 2    |      |      | μs   |

|                 |                              | _                                     | 2    |      |      | μs   |

| th              | Data hold time               | 64UP="H"                              | 18   |      |      | μs   |

| tPEl            | EOS Delay time (1)           | · · · · · · · · · · · · · · · · · · · | -    | _    | 2    | ms   |

| tPE2            | EOS Delay time (2)           |                                       | -    | -    | 2    | ms   |

| t <sub>EP</sub> | START set up time            |                                       | 0    | -    |      | ms   |

SWITCHING CHARACTERISTICS TEST WAVEFORM (CPUM="H")

(4) ANALOG CHARACTERISTICS (Unless otherwise VSS1=VSS2=OV, VDD=5V, Ta=25°C)

| SYMBOL                              | PARAMETER                 | Applied<br>Terminal | CONDITION                              | MIN.     | TYP. | MAX.                   | UNIT |

|-------------------------------------|---------------------------|---------------------|----------------------------------------|----------|------|------------------------|------|

| VIN                                 | Range of input voltage    | LPF IN              | V <sub>DD</sub> =3.9 <sub>√</sub> 5.7V | 1.2      | •    | V <sub>DD</sub> -1.2   | V    |

| VOUT                                | Output voltage            | LPF OUT             | 11                                     | 1.2      | -    | $v_{\mathrm{DD}}$ -1.2 | V    |

| V <sub>G</sub>                      | Voltage gain              | _                   | LPF1="L", 1Hz ~ 1kHz                   | -0.5     | 0    | +0.5                   | dB   |

|                                     |                           |                     | LPF1="H", 1Hz ~ 1kHz                   | -4.5     | -4   | -3.5                   | dB   |

| fc                                  | Cutoff frequency          |                     | LPF2="L"                               | 2.88     | 3.04 | 3.20                   | kH   |

|                                     |                           | _                   | LPF2="H"                               | 3.6      | 3.8  | 4.0                    | kH   |

| THD                                 | Total harmonic distortion |                     | V <sub>IN</sub> =1 V <sub>P</sub> -p   | -        | -    | 1.0                    | %    |

|                                     | Input registance          | LPF IN              |                                        | 1.0      | 4.0  | _                      | MΩ   |

| R <sub>IN</sub><br>R <sub>OUT</sub> | Output registance         | LPF OUT             |                                        | <u> </u> | 1.0  | 1.5                    | kΩ   |

MEASUREMENT CIRCUIT

V<sub>IN</sub>, V<sub>OUT</sub>, fc, THD