SLLS568A - JUNE 2003

- Fully Supports Provisions of IEEE Std 1394b-2002 at S100B Signaling Rates

- Provides One Transceiver to Drive IEEE Std 1394b Signaling Across Unshielded Twisted Pair Category 5 (UTP5 or CAT5) Cable or Better at 100 Megabits per Second (Mbits/s)

- Power-Down Features to Conserve Energy in Battery Powered Applications

- Single 3.3-V Supply Operation or Optional Dual 3.3-V/1.8-V Supply Operation

- Low-Cost High-Performance 24-Terminal TSSOP Package

- Low-Power Modes to Put Device Into Low Power States When Data Is Not Being Driven

#### description

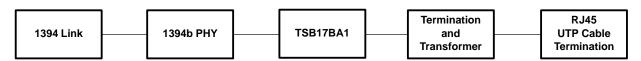

The TSB17BA1 is a single-port 100-Mbps transceiver used in transporting IEEE Std 1394b (1394b) or other coded data across CAT5 or better cabling. It is attached to a 1394b-capable port on a 1394b physical layer (PHY) to enable 1394b 100-Mbps signals to be transmitted and received across up to 100 meters of unshielded twisted-pair category 5 (UTP5) cable. Equalization is applied to the signal received from the UTP5 cable to boost signal-to-noise ratio (SNR) to allow sensing of the data. A 1394b PHY device capable of transmitting at only 100 Mbits/s in 1394b-only mode is required for correct functionality. This PHY must be connected to the TSB17BA1 at one of the twisted-pair (TP) ports, with the 110- $\Omega$  1394b transmission line properly terminated. The TSB17BA1 must then be connected to a 100- $\Omega$  transmission line properly terminated and connected to an isolating transformer. This transformer is then connected to an RJ45 connector. All of the parameters on the UTP5 side of the TSB17BA1 are set the same as 100baseT Ethernet. This allows the mechanical and magnetic infrastructure, which is used to design a 100baseT connection, to be used when designing a 100-Mbits/s UTP5 1394b connection. This device does not implement the autocrossover functionality described in chapter 12 of IEEE Std 1394b-2002. This means the required crossover of TPA to TPB and TPB to TPA must be done in the cable or connector or PWB; in other words, a mechanical crossover must be implemented (see the Application Information section).

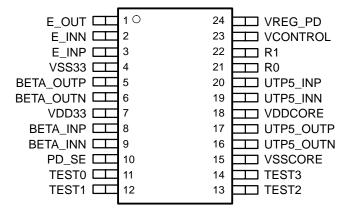

#### terminal assignments

#### PW PACKAGE (TOP VIEW)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Implements technology covered by one or more patents of Apple Computer, Inc. and SGS Thompson, Limited.

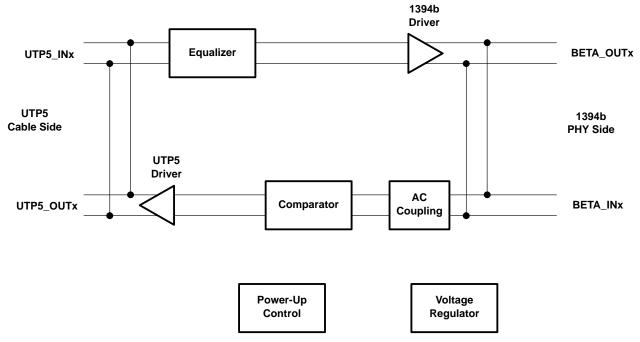

# functional block diagram

#### equalizer

The equalizer applies equalization to the signal received from the UTP5 cable to boost SNR to allow sensing of the data.

#### 1394b driver

This block drives the signal detected and enhanced by the equalizer from the UTP cable to a 1394b PHY port.

#### ac coupling

This block blocks direct current signals to the comparator. Only ac signals are propagated through this block.

#### comparator

This block converts 1394b signals from the 1394b PHY into levels capable of driving the UTP5 driver.

#### **UTP5** driver

This block drives signals onto the UTP5 cable.

#### power-up control

This block provides a signal for the control of the device relative to the state of the supply voltage.

#### voltage regulator

This block regulates an externally provided 3-3.6 V down to an internally used 1.8 V.

## **Terminal Functions**

| TE                               | RMINAL                      |                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|----------------------------------|-----------------------------|----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                             | TYPE                        | NO.                  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Test Terminals                   | <br>S                       |                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| E_INN                            | Test                        | 2                    | I   | Input reserved for future enhancement. Must be grounded for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| E_INP                            | Test                        | 3                    | ı   | Input reserved for future enhancement. Must be grounded for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| E_OUT                            | Test                        | 1                    | 0   | Output reserved for future enhancement. May be left unconnected for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| TEST0<br>TEST1<br>TEST2<br>TEST3 | CMOS                        | 11<br>12<br>13<br>14 | ı   | Test control. These inputs are used in the manufacturing test of the TSB17BA1. For normal use, these terminals must be pulled low to GND.                                                                                                                                                                                                                                                                                                                                                     |  |

| IEEE Std 1394                    | b PHY Termi                 | nals                 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| BETA_INP<br>BETA_INN             | Input from<br>1394b<br>PHY  | 8<br>9               | I   | Input of ac-coupling block. These twisted-pair differential-signal terminals connect the TSB17BA1 BETA_INP to the 1394b PHY TPB+ and BETA_INN to the 1394b PHY TPB- terminals of the port on the 1394b PHY. Board traces from each pair of positive and negative differential signal terminals must be kept matched and as short as possible to the external load resistors and to the 1394b PHY. The transmission lines between the 1394b PHY and TSB17BA1 must be terminated properly.      |  |

| BETA_OUTP<br>BETA_OUTN           | Output to<br>1394b<br>PHY   | 5<br>6               | 0   | Output of 1394b driver block. These twisted-pair differential-signal terminals, connect the TSB17BA1 BETA_OUTP to the 1394b PHY TPA+ and BETA_OUTN to the 1394b PHY TPA- terminals of the port on the 1394b PHY. Board traces from each pair of positive and negative differential signal terminals must be kept matched and as short as possible to the external load resistors and to the 1394b PHY. The transmission lines between the 1394b PHY and TSB17BA1 must be terminated properly. |  |

| RJ45 Termina                     | s                           |                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| UTP5_INN                         | Input from<br>UTP5<br>Cable | 19                   | 1   | Negative differential side of input from the UTP5 cable to the TSB17BA1 termination network. Connect to network corresponding to RJ45 pin number 6 or RJ45 pin number 8.                                                                                                                                                                                                                                                                                                                      |  |

| UTP5_INP                         | Input from<br>UTP5<br>Cable | 20                   | ı   | Positive differential side of input from the UTP5 cable to the TSB17BA1 termination network. Connect to network corresponding to RJ45 pin number 3 or RJ45 pin number 7.                                                                                                                                                                                                                                                                                                                      |  |

| UTP5_OUTN                        | Output to<br>UTP5<br>Cable  | 16                   | 0   | Negative differential side of output from TSB17BA1 to the UTP5 cable termination network. Connect to network corresponding to RJ45 pin number 2.                                                                                                                                                                                                                                                                                                                                              |  |

| UTP5_OUTP                        | Output to<br>UTP5<br>Cable  | 17                   | 0   | Positive differential side of output from TSB17BA1 to the UTP5 cable termination network.  Connect to network corresponding to RJ45 pin number 1.                                                                                                                                                                                                                                                                                                                                             |  |

| Power and Gr                     | ound Termina                | als                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| PD_SE                            | CMOS                        | 10                   | I/O | Global power down. A high on this terminal turns off all internal circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| R0                               | Bias                        | 21                   | -   | Current setting resistor. This terminal is connected to a precision external resistance to set the internal operating currents and the cable-driver output currents. This terminal has a very low impedance to ground.                                                                                                                                                                                                                                                                        |  |

| R1                               | Bias                        | 22                   | I   | Current setting resistor (band-gap sense voltage). This terminal is connected to a precision external resistance to set the internal operating currents and the cable-driver output currents. A resistance of 6.04 k $\Omega$ , 1% between R0 and R1, is required to meet the 1394b output-voltage limits.                                                                                                                                                                                    |  |

| VCONTROL                         |                             | 23                   | I/O | Voltage control (reserved). Nominally not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| VREG_PD                          | CMOS                        | 24                   | ı   | Power down for voltage regulator. When driven low, the device uses an internal regulator to generate the required 1.8 V. When driven high, the internal regulator is powered down and the 1.8 V must be supplied externally to power the 1.8-V circuitry of the device. Nominally tied low to enable the internal regulator.                                                                                                                                                                  |  |

# TSB17BA1 IEEE STD 1394b SINGLE-PORT CABLE TRANSCEIVER SLLS568A – JUNE 2003

# **Terminal Functions (Continued)**

| TE                                     | RMINAL |     |       | DECORIDATION                                                                                                                                                                                                                                                     |

|----------------------------------------|--------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                   | TYPE   | NO. | 1/0   | DESCRIPTION                                                                                                                                                                                                                                                      |

| Power and Ground Terminals (Continued) |        |     | nued) |                                                                                                                                                                                                                                                                  |

| VDDCORE                                | Supply | 18  | _     | Core power. Internal core circuit power terminal. Must be decoupled with a 1- $\mu$ F capacitor in parallel with other smaller capacitors, such as 0.001- $\mu$ F capacitors.                                                                                    |

| VDD33                                  | Supply | 7   | _     | 3.3-V power. I/O 3.3-V circuit power terminals. A combination of high-frequency decoupling capacitors near each terminal are suggested, such as paralleled 0.1 $\mu$ F and 0.001 $\mu$ F. Lower frequency 10- $\mu$ F filtering capacitors are also recommended. |

| VSSCORE                                | Supply | 15  | _     | Core ground. Tie to the ground plane of the PWB as close as possible to the terminal.                                                                                                                                                                            |

| VSS33                                  | Supply | 4   | _     | 3.3-V ground. Tie to the ground plane of the printed wiring board (PWB) as close as possible to the terminal.                                                                                                                                                    |

# TSB17BA1 IEEE STD 1394b SINGLE-PORT CABLE TRANSCEIVER

SLLS568A - JUNE 2003

# absolute maximum ratings over operating free-air temperature (unless otherwise noted)†

| Supply voltage range, V <sub>DD</sub> (see Note 1)           | -0.3 V to 4 V                |

|--------------------------------------------------------------|------------------------------|

| Input voltage range, V <sub>I</sub> (see Note 1)             |                              |

| Output voltage range at any output, VO                       |                              |

| Continuous total power dissipation                           | See Dissipation Rating Table |

| Operating free air temperature range, T <sub>A</sub>         | 0°C to 70°C                  |

| Storage temperature range, T <sub>stq</sub>                  |                              |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds |                              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values, except differential I/O bus voltages, are with respect to network ground.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{\scriptsize A}} \leq 25^{\circ}\mbox{\scriptsize C}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C <sup>‡</sup> | T <sub>A</sub> = 70°C<br>POWER RATING |

|---------|-----------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------|

| PW\$    | 0.93 W                                                                      | 10.9 mW/°C                                                  | 0.44 W                                |

$<sup>\</sup>overline{^{\dagger}}$  This is the inverse of the traditional junction-to-ambient thermal resistance (R $_{\theta}$ JA).

<sup>§ 2-</sup>oz trace and copper pad with solder.

# TSB17BA1 IEEE STD 1394b SINGLE-PORT CABLE TRANSCEIVER SLLS568A – JUNE 2003

# recommended operating conditions

|                                                                       |                                                                                            | MIN                 | TYP <sup>†</sup> | MAX                 | UNIT |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------|------------------|---------------------|------|

| Supply voltage, V <sub>DD33</sub>                                     |                                                                                            | 3                   | 3.3              | 3.6                 | V    |

| Supply voltage, VDDCORE                                               |                                                                                            | 1.65                | 1.8              | 1.95                | ٧    |

| High-level input voltage, VIH                                         | TEST[0:3], PD_SE, VREG_PD                                                                  | 0.7×V <sub>DD</sub> |                  |                     | ٧    |

| Low-level input voltage, V <sub>IL</sub>                              | TEST[0:3], PD_SE, VREG_PD                                                                  |                     |                  | 0.3×V <sub>DD</sub> | ٧    |

| Maximum junction temperature, TJ                                      | $R_{\theta JA} = 91.47^{\circ}C/W$ , $T_A = 70^{\circ}C$ , high-K board                    |                     |                  | 86.5                | °C   |

| (see R <sub>0JA</sub> values listed in thermal characteristics table) | $R_{\theta JA} = 150.70^{\circ} \text{C/W}, T_A = 70^{\circ} \text{C}, \text{low-K board}$ |                     |                  | 97.1                | °C   |

| 1394b Differential input voltage, V <sub>ID</sub>                     | BETA_INP-BETA_INN                                                                          | 200                 |                  | 800                 | mV   |

| 1394b Common-mode input voltage, V <sub>IC</sub>                      | BETA_IN cable inputs, nonsource power node                                                 | 0.4706              |                  | 2.015               | V    |

| Receive input jitter                                                  | BETA_INP, BETA_INN cable inputs, S100 operation                                            |                     |                  | ±1.08               | ns   |

| Receive input skew                                                    | Between BETA_OUT and BETA_IN cable inputs, S100 operation                                  |                     |                  | ±0.8                | ns   |

<sup>†</sup> All typical values are at  $V_{DD} = 3.3 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

SLLS568A – JUNE 2003

# electrical characteristics over recommended ranges of operating conditions (unless otherwise noted)

#### driver

|                   | PARAMETER                                | TEST CONDITIONS | TYP  | UNIT |

|-------------------|------------------------------------------|-----------------|------|------|

| VOD               | Differential output voltage (BETA)       |                 | 705  | mV   |

| VOD               | Differential output voltage (UTP5)       |                 | 500  | mV   |

| IBETA             | Beta drive current, BETA_OUTP, BETA_OUTN | Drivers enabled | 12.5 | mA   |

| I <sub>UTP5</sub> | UTP5 drive current, UTP5_OUTP, UTP5_OUTN | Drivers enabled | 10   | mA   |

#### receiver

|                    | PARAMETER                        | TEST CONDITIONS  | MIN | TYP | MAX | UNIT |

|--------------------|----------------------------------|------------------|-----|-----|-----|------|

| _                  | Difference (full form and a new  | Drivers Parkland | 4   | 7   |     | kΩ   |

| $Z_{\text{ID}}$    | Differential impedance           | Drivers disabled |     |     | 4   | pF   |

| 7                  | Common modelimendones            | Drivers disabled | 20  |     |     | kΩ   |

| Z <sub>IC</sub>    | Common-mode impedance            | Drivers disabled |     |     | 24  | pF   |

| V <sub>TH</sub> -R | Receiver input threshold voltage | Drivers disabled | -30 |     | 30  | mV   |

#### device

|           | PARAMETER                                       | TEST CONDITIONS             |     | UNIT |

|-----------|-------------------------------------------------|-----------------------------|-----|------|

|           | 3.3-V supply current <sup>†</sup>               |                             | 4   |      |

| IDDSTATIC | V <sub>DDCORE</sub> supply current <sup>†</sup> | No signals to driver inputs | 4   | mA   |

|           | 3.3-V supply current <sup>‡</sup>               |                             | 7.5 |      |

|           | 3.3-V supply current <sup>†</sup>               |                             | 6   |      |

| IDDDYN    | VDDCORE supply current <sup>†</sup>             | Normal operation            | 30  | mA   |

|           | 3.3-V supply current <sup>‡</sup>               | •                           |     |      |

<sup>†</sup> Measured with internal regulator off, 1.8-V supply current from external source

#### thermal characteristics

| PARAMETER       |                                         | TEST CONDITIONS                                                                                                                                                                                                                                  |  | UNIT |

|-----------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------|

| $R_{\thetaJA}$  | Junction-to-free-air thermal resistance | Board mounted, no air flow, high conductivity TI-recommended test board, chip soldered or greased to thermal land with 2-oz copper (high-K board)  Board mounted, no air flow, high conductivity JEDEC test board with 1-oz copper (low-K board) |  | °C/W |

| $R_{\theta JC}$ | Junction-to-case-thermal resistance     |                                                                                                                                                                                                                                                  |  | °C/W |

| $R_{\theta JA}$ | Junction-to-free-air thermal resistance |                                                                                                                                                                                                                                                  |  | °C/W |

| $R_{\theta JC}$ | Junction-to-case-thermal resistance     |                                                                                                                                                                                                                                                  |  | °C/W |

<sup>‡</sup> Measured with internal regulator on

SLLS568A – JUNE 2003

electrical characteristics over recommended ranges of operating conditions (unless otherwise noted) (continued)

# switching characteristics

|                | PARAMETER                            | TEST CONDITIONS               | MIN | TYP  | MAX  | UNIT |

|----------------|--------------------------------------|-------------------------------|-----|------|------|------|

|                | Jitter, transmit                     | Between BETA_OUT and BETA_IN  |     | 2    |      | ns   |

|                | Observative and "                    | Between BETA_OUT and BETA_IN  |     |      | 0.10 |      |

|                | Skew, transmit                       | Between UTP5_OUT and UTP5_IN  |     |      | 0.20 | ns   |

| t <sub>r</sub> | TP differential rise time, transmit  | 10% to 90%                    |     | 0.65 |      | ns   |

| t <sub>f</sub> | TP differential fall time, transmit  | 90% to 10%                    |     | 0.65 |      | ns   |

| tr             | UTP differential rise time, transmit | 10% to 90%, at RJ45 connector |     | 3.5  |      | ns   |

| t <sub>f</sub> | UTP differential fall time, transmit | 90% to 10%, at RJ45 connector |     | 3.5  |      | ns   |

#### PARAMETER MEASUREMENT INFORMATION

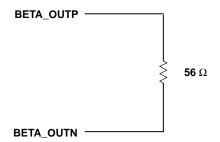

Figure 1. Test Load for Beta Connection

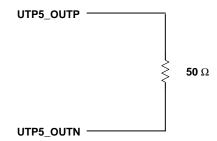

Figure 2. Test Load for UTP5 Connection

SLLS568A - JUNE 2003

#### **APPLICATION INFORMATION**

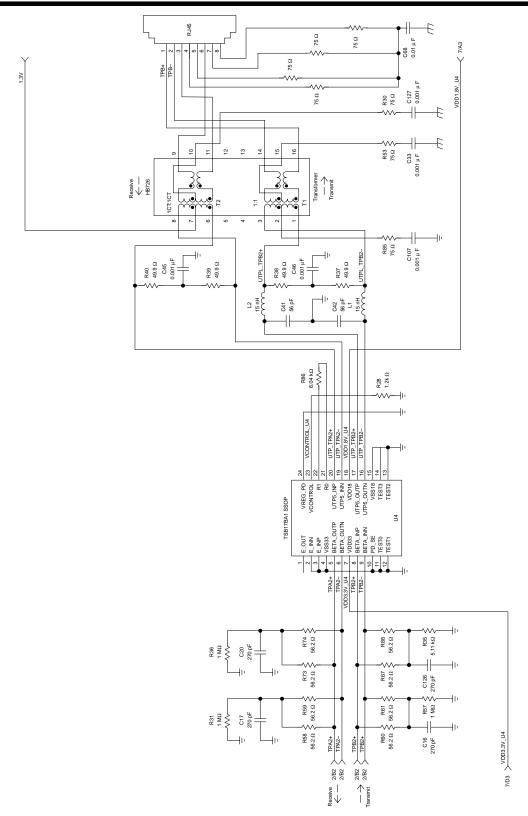

Figure 3. 1394b Cable Termination

#### signal coding

The signaling generated from a 1394b PHY is 8B/10B encoded. This means to send 8 bits of data requires the transmission of 10 bits across the cable. The maximum frequency that is required to send 100 Mbits/s is a fundamental frequency of 62.5 MHz (see the IEEE Std 1394b-2002 for more explanation).

#### connector pins

The current IEEE Std 1394b-2002 requires that the connection from 1394b PHY signal to the RJ45 connector pin be:

- TPB+ to RJ45 pin 1

- TPB- to RJ45 pin 2

- TPA+ to RJ45 pin 7

- TPA— to RJ45 pin 8

There is a proposal to change the IEEE Std 1394b-2002 connection from 1394b PHY signal to the RJ45 connector pin to be the same as the 100baseT Ethernet. This allows use of more 100baseT Ethernet components for 1394b connections. This changes the connections to:

- TPB+ to RJ45 pin 1

- TPB- to RJ45 pin 2

- TPA+ to RJ45 pin 3

- TPA— to RJ45 pin 6

It is anticipated that the change will be implemented into IEEE Std 1394b-2002, though it has not been ratified. Therefore, it is recommended that all implementations utilize the new pinout running TPA+ to pin 3 and TPA- to pin 6. If a closed system is created, meaning the designer controls the electronics at both ends of the UTP5 cable, then using pins 7 and 8 can give as much as a 12-dB reduction in crosstalk rather than using pins 3 and 6. Please contact Texas Instruments for further details.

#### cable connection

The IEEE Std 1394b-2002 requires the output of a TPB port to be connected to the input of a TPA port when connecting one device to a second device. In other words, it requires a crossover somewhere between the two PHY ports. The 1394b standard further states that a UTP5 device incorporates logic that can automatically implement this crossover in the logic. The TSB17BA1 does not contain this logic, therefore, the crossover must be implemented external to the TSB17BA1.

It is recommended for users of the TSB17BA1 to:

- Design the UTP5 connection to pins 1, 2 and 3, 6 as previously detailed.

- Ship an Ethernet crossover cable with their devices.

The crossover cable connects:

- Pin 1 on the near end of the cable to pin 3 on the far end of the cable

- Pin 2 on the near end of the cable to pin 6 on the far end of the cable

- Pin 3 on the near end of the cable to pin 1 on the far end of the cable

- Pin 6 on the near end of the cable to pin 2 on the far end of the cable, thereby implementing the crossover.

#### SLLS568A - JUNE 2003

#### APPLICATION INFORMATION

#### cable connection (continued)

This also works for CAT5-structured wiring cable that is typically installed in a home or office. The CAT5 cables in these structured wiring installations are wired straight through and do not crossover. It is recommended that the structured wiring hub at the center of the star-type installation contain only straight-through wiring. If the RJ45 connector is brought outside the wall, then it also is connected straight through. If all networkable devices are also created as straight-through connections, then the required crossover is implemented when the networkable device is connected to the RJ45 wall-plate connection using a crossover cable.

There is a special case for the structured wiring if the wall plate enables a 4-pin, 6-pin, or 9-pin 1394b connector. In this case, one port of the 1394b PHY is connected to the 1394b connector in the typical manner. However, the connection between the 1394b PHY and the UTP5 connection inside the wall must implement a crossover. This is true if the 1394b-structured wiring hub is wired straight through and the cable pulled is straight through. In this case, since all the electrical connections between the two 1394b ports are straight through, the crossover must be implemented on the wall-plate UTP5 connection. It is required that this crossover be completed between the RJ45 connector on the wall plate and the isolating transformer of the termination network.

Please contact Texas Instruments for further detail.

#### **PCB** layout considerations

There are certain signals that require special care in the layout of the TSB17BA1. The UTP5\_INP and UTP5\_INN signals are the inputs from what might be a 100-m cable. After propagating through a cable this long the signal amplitudes could be small and more easily affected by board noise. The routing for these signals from the RJ45 connector through the termination network to the PHY must be short and, if possible, a ground guard etch must be implemented to protect them from board noise. This etch must extend the length of the traces, be far enough away from the signal traces not to significantly affect the trace impedance, and be connected to the ground plane every 2 cm or less.

The precision resistor between the R1 and R0 terminals sets the internal currents and voltages of the TSB17BA1. Any noise that couples onto the R1 terminal can affect the entire device. Therefore, this connection must be kept short and as close to the TSB17BA1 as possible. This connection can also benefit from a ground guard etch around the R1 and R0 terminal connections.

To keep the noise introduced to these signals to a minimum it is recommended that no digital signals or large amplitude analog signals (like switching regulators) be routed in the vicinity of terminals 19–22 on the TSB17BA1. The output signals of the TSB17BA1 (UTP5\_OUTP, UTP5\_OUTN, BETA\_OUTP, and BETA\_OUTN) must also be routed away from these sensitive input pins.

Figure 4. Example Schematic Implementation

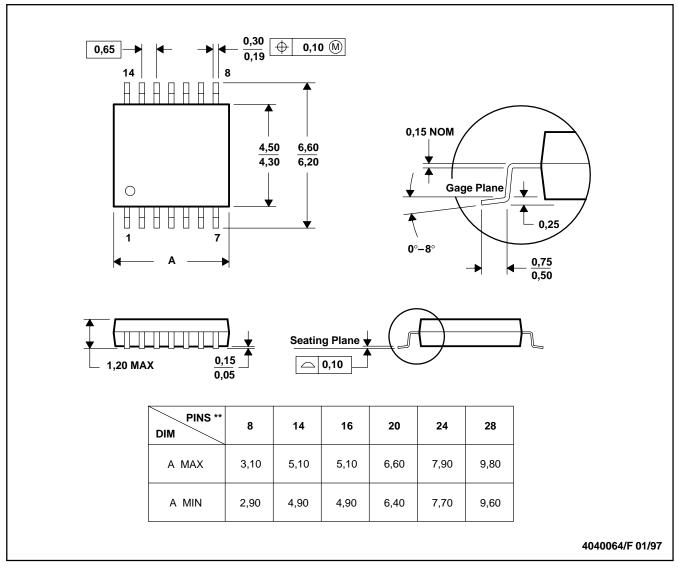

## **MECHANICAL DATA**

## PW (R-PDSO-G\*\*)

#### 14 PINS SHOWN

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

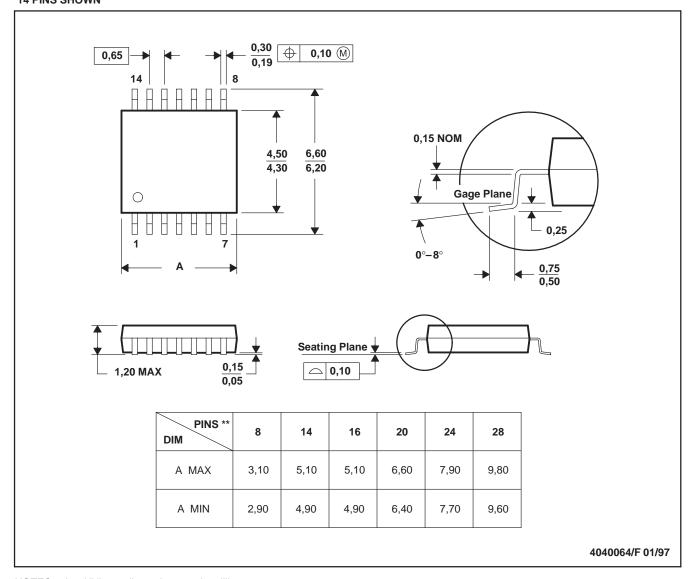

## PW (R-PDSO-G\*\*)

#### 14 PINS SHOWN

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third—party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products & application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265