# Special Fail-Safe IC

### **Description**

The U6808B is designed to support the fail-safe function of a safety critical system e.g. ABS. It includes a relay driver, a watchdog controlled by an external R/C-network

and a reset circuit initiated by an over- and undervoltage condition of the 5-V supply providing a positive and a negative reset signal.

#### **Features**

- Digital self-supervising watchdog with hysteresis

- One 250-mA output driver for relay

- Enable output open collector 10 mA

- Over-/undervoltage detection

- ENABLE- and RELAY outputs protected against standard transients and 40 V load dump

- ESD protection according to MIL-STD-883 D test method 3015.7

- Human body model:  $\pm~2~kV~(100~pF,~1.5~k\Omega)$

- Machine model:  $\pm 200 \text{ V} (200 \text{ pF}, 0 \Omega)$

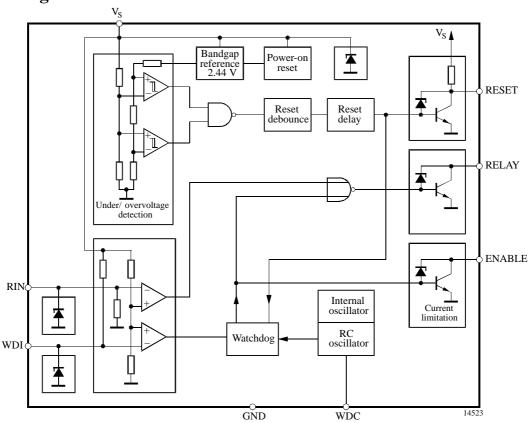

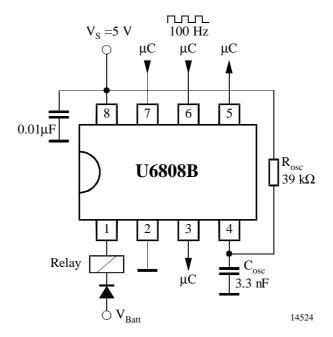

### **Block Diagram**

Figure 1. Block diagram

### **Ordering Information**

| <b>Extended Type Number</b> | Package | Remarks |

|-----------------------------|---------|---------|

| U6808B                      | SO8     |         |

Rev. A2, 18-Jan-01

# **Pin Description**

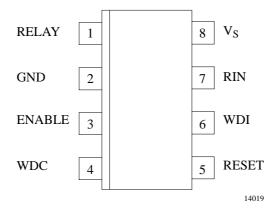

Figure 2. Pinning U6808B

Table 1 Pin description

| Pin | Name    | Type           | Function                       | Logic          |

|-----|---------|----------------|--------------------------------|----------------|

| 1   | RELAY   | Open collector | Fail-safe relay driver         | Driver off:—   |

|     |         | driver output  |                                | driver on: L   |

| 2   | GND     | Supply         | Standard ground                |                |

| 3   | ENABLE  | Digital output | Negative reset signal          | Reset: L       |

| 4   | WDC     | Analog input   | External RC for watchdog timer |                |

| 5   | RESET   | Digital output | Negative reset signal          | Reset: L       |

| 6   | WDI     | Digital input  | Watchdog trigger signal        | Pulse sequence |

| 7   | RIN     | Digital input  | Activation of relay driver     | H: driver on   |

|     |         |                |                                | L: driver off  |

| 8   | $V_{S}$ | Supply         | 5-V supply                     |                |

### **Fail-Safe Functions**

A fail-safe IC has to maintain its monitoring function even if there is a fault condition at one of the pins (e.g. short circuit). This ensures that a microcontroller system would not be brought into a critical status. A critical status is reached if the system is not able to switch off the relay and to give a signal to the  $\mu C$  via ENABLE- and RESET outputs. The following table shows the fault conditions for the pins.

Table 2 Table of fault conditions

| Pin   | Function                                      | Short to Vs    | Short to VBat  | Short to GND   | Open Circuit   |

|-------|-----------------------------------------------|----------------|----------------|----------------|----------------|

| RIN   | Digital input to activate the fail-safe relay | Relay on       | Relay on       | Relay off      | Relay off      |

| WDI   | Watchdog trigger input                        | Watchdog reset | Watchdog reset | Watchdog reset | Watchdog reset |

| OSC   | Capacitor and resistor of watch-dog           | Watchdog reset | Watchdog reset | Watchdog reset | Watchdog reset |

| RELAY | Driver of the fail-<br>safe relay             |                |                | Relay on       | Relay off      |

### **Truth Tables**

Table 3 Truth table the over- and under voltage conditions

| In                               | puts | Outputs                          |         |                 |  |  |

|----------------------------------|------|----------------------------------|---------|-----------------|--|--|

| Supply Voltage Relay Input (RIN) |      | Relay Output Driver RESET Output |         | Enable Output   |  |  |

| $(V_S)$                          |      | (RELAY)                          | (RESET) | Driver (ENABLE) |  |  |

| Normal                           | Low  | Off                              | High    | Off             |  |  |

|                                  | High | On                               | High    | Off             |  |  |

| Too low                          | Low  | Off                              | Low     | On              |  |  |

|                                  | High | Off                              | Low     | On              |  |  |

| Too high                         | Low  | Off                              | Low     | On              |  |  |

|                                  | High | Off                              | Low     | On              |  |  |

Table 4 Truth table for watchdog failures (RESET output don't care)

| Inj                     | puts                 | Outputs                        |                               |  |  |

|-------------------------|----------------------|--------------------------------|-------------------------------|--|--|

| Watchdog Input<br>(WDI) | Relay Input<br>(RIN) | Relay Output Driver<br>(RELAY) | Enable Output Driver (ENABLE) |  |  |

| Normal                  | Low                  | Off                            | Off                           |  |  |

|                         | High                 | On                             | Off                           |  |  |

| Too slow                | Low                  | Off                            | On                            |  |  |

|                         | High                 | Off                            | On                            |  |  |

| Too fast                | Low                  | Off                            | On                            |  |  |

|                         | High                 | Off                            | On                            |  |  |

# **Description of the Watchdog**

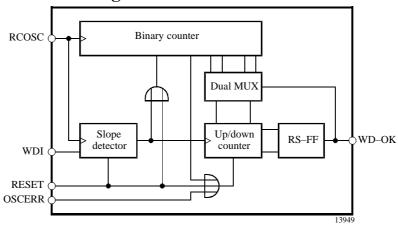

Figure 3. Watchdog block diagram

#### **Abstract**

The microcontroller is monitored by a digital window watchdog which accepts an incomming trigger signal of a constant frequency for correct operation. The frequency of the trigger signal can be varied in a broad range as the watchdog's time window is determined by external R/C components. The following description refers to the block diagram (Fig. 3)

Rev. A2, 18-Jan-01 3 (12)

#### WDI Input (Pin 6)

The microcontroller has to provide a trigger signal with the frequency  $f_{WDI}$  which is fed to the WDI input. A positive edge of  $f_{WDI}$  detected by a slope detector resets the binary counter and clocks the up/down counter additionally. The latter one counts only from 0 to 3 or reverse. Each correct trigger increments the up/down counter by 1, each wrong trigger decrements it by 1. As soon as the counter reaches status 3 the RS flip-flop is set; see Fig. 4 (WD state diagram). A missing incoming trigger signal is detected after 250 clocks of the internal watchdog frequency  $f_{RC}$  (see WD OK output) and resets the up/down counter directly.

#### **RCOSC Input**

With an external R/C circuitry the IC generates a time base (frequency  $f_{WDC}$ ) independent from the microcontroller. The watchdog's time window refers to a frequency of

$f_{WDC} = 100 \times f_{WDI}$

### **OSCERR** Input

A smart watchdog has to ensure that internal problems with its own time base are detected and do not lead to an undesired status of the complete system. If the RC oscillator stops oscillating a signal is fed to the OSCERR input after a timeout delay. It resets the up/down counter and disables the WD-OK output.

Without this reset function the watchdog would freeze its current status when  $f_{RC}$  stops.

#### **RESET Input**

During power-on and under-/ overvoltage detection a reset signal is fed to this pin. It resets the watchdog timer and sets the initial state.

#### **WD-OK Output**

After the up/down counter is incremented to status 3 (see Fig. 4, WD state diagram) the RS flip-flop is set and the WD-OK output becomes logic "1". This information is available for the microcontroller at the open-collector output ENABLE. If on the other hand the up/down counter is decremented to 0 the RS flip-flop is reset, the WD-OK output and the ENABLE output are disabled. The WD-OK output also controls a dual MUX stage which shifts the time window by one clock after a successful trigger thus forming a hysteresis to provide stable conditions for the evaluation of the trigger signal 'good' or 'false'. The WD-OK signal is also reset in the case the watchdog counter is not reset after 250 clocks (missing trigger signal).

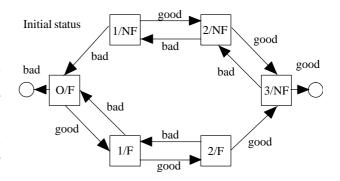

#### Watchdog State Diagram

Figure 4. Watchdog state diagram

#### **Explanation**

In each block, the first character represents the state of the counter. The second notation indicates the fault status of the counter. A fault status is indicated by an "F" and a no fault status is indicated by an "NF". When the watchdog is powered up initially, the counter starts out at the 0/F block (initial state). "Good" indicates that a pulse has been received whose width resides within the timing window. "Bad" indicates that a pulse has been received whose width is either too short or too long.

#### **Watchdog-Window Calculation**

#### Example with recommended values

$C_{osc} = 3.3 \text{ nF}$  (should be preferably 10%, NPO)

$R_{osc}{=}~39~k\Omega \quad (may~be~5\%,~R_{osc}{<}100~k\Omega~due~to~leakage$  current and humidity)

#### **RC** Oscillator

$$t_{WDC}\left(s\right) = 10^{-3} \times \left[C_{osc}\left(nF\right) \times \left[\left(0.00078 \times R_{osc}\left(k\Omega\right)\right) + 0.0005\right]\right]$$

$f_{WDC}$  (Hz) = 1 / ( $t_{WDC}$ )

#### Watchdog WDI

$f_{WDI}$  (Hz) =0.01 ×  $f_{WDC}$

$t_{WDC} = 100 \mu s$   $\rightarrow$   $f_{WDC} = 10 \text{ kHz}$

$f_{WDI} = 100 \text{ Hz}$  ->  $t_{WDI} = 10 \text{ ms}$

#### WDI pulse width for fault detection after 3 pulses:

Upper watchdog window

Minimum:  $169/f_{WDC} = 16.9 \text{ ms} \rightarrow f_{WDC} / 169 = 59.1 \text{ Hz}$

Maximum: 170/  $f_{WDC}\!=17.0$  ms  $-\!\!> f_{WDC}$  / 170 =58.8~Hz

Lower watchdog window

Minimum:  $79/f_{WDC} = 7.9 \text{ ms} -> f_{WDC} / 79 = 126.6 \text{ Hz}$ Maximum:  $80/f_{WDC} = 8.0 \text{ ms} -> f_{WDC} / 80 = 125.0 \text{ Hz}$

#### WDI dropouts for immediate fault detection:

Minimum:  $250/ f_{WDC} = 25 \text{ ms}$ Maximum:  $251/ f_{WDC} = 25.1 \text{ ms}$

| Time/s      | 9/ f <sub>WDC</sub> 80/ | f <sub>WDC</sub> 169/               | f <sub>WDC</sub> 170/ f <sub>W</sub> | DC 250/ i   | $f_{ m WDC}$   | $251/f_{WDC}$ |

|-------------|-------------------------|-------------------------------------|--------------------------------------|-------------|----------------|---------------|

|             |                         | Watchdog window update rate is good |                                      |             |                |               |

| -           |                         | update fate is good                 |                                      | T           | T              | T             |

| Update rate | Update rate is          |                                     | Update rate is ei-                   | Update rate | Update rate is | Pulse has     |

| is too fast | either too fast         |                                     | ther too slow or                     | is too slow | either too     | dropped out   |

|             | or good                 |                                     | good                                 |             | slow or pulse  |               |

|             |                         |                                     |                                      |             | has dropped    |               |

|             |                         |                                     |                                      |             | out            |               |

Figure 5. Watchdog timing diagram with tolerances

#### Remark to Reset Delay

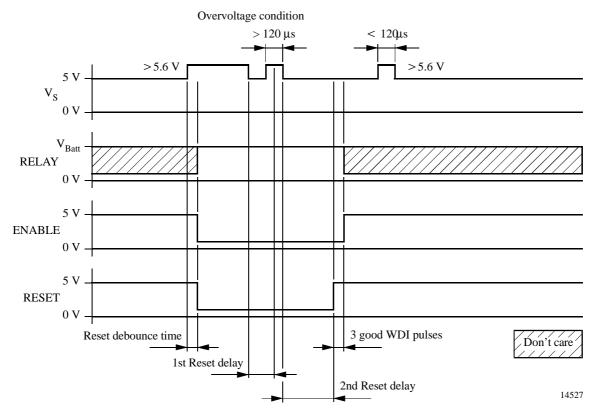

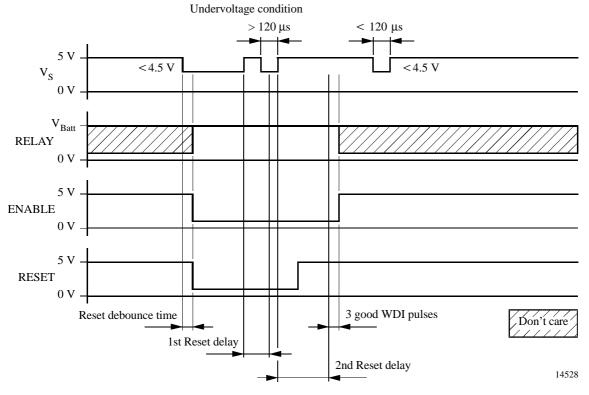

The duration of the over- or undervoltage pulses determines the enable- and reset output. A pulse duration shorter than the debounce time has no effect on the outputs. A pulse longer than the debounce time results in the first reset delay. If a pulse appears during this delay, a 2nd delay time is triggered. Therefore, the total reset delay time can be longer than specified in the data sheet.

### **Absolute Maximum Ratings**

| Parameters                                                                                                                 | Symbol                               | Value       | Unit     |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------|----------|

| Supply-voltage range                                                                                                       | V <sub>S</sub>                       | - 0.2 to 16 | V        |

| Power dissipation $V_S = 5 \text{ V}; T_{amb} = -40^{\circ}\text{C}$<br>$V_S = 5 \text{ V}; T_{amb} = 125^{\circ}\text{C}$ | P <sub>tot</sub><br>P <sub>tot</sub> | 250<br>150  | mW<br>mW |

| Thermal resistance                                                                                                         | R <sub>thja</sub>                    | 160         | K/W      |

| Junction temperature                                                                                                       | Tj                                   | 150         | °C       |

| Ambient temperature range                                                                                                  | T <sub>amb</sub>                     | -40 to 125  | °C       |

| Storage temperature range                                                                                                  | T <sub>stg</sub>                     | –55 to 155  | °C       |

Rev. A2, 18-Jan-01 5 (12)

# **Electrical Characteristics**

$V_S=5$  V,  $T_{amb}=-40$  to + 125°C; reference pin is GND;  $f_{intern}=100$  kHz + 50% - 45%,  $f_{WDC}=10$  kHz  $\pm$  10%;  $f_{WDI}=100$  Hz

| Parameter                    | Test Conditions / Pins                                | Symbol             | Min.                   | Typ. | Max.                     | Unit     |

|------------------------------|-------------------------------------------------------|--------------------|------------------------|------|--------------------------|----------|

| Supply voltage               |                                                       |                    |                        |      |                          |          |

| Operation range general      |                                                       | V <sub>S</sub>     | 4.5                    |      | 5.5                      | V        |

| Operation range reset        |                                                       | V <sub>S</sub>     | 1.2                    |      | 16.0                     |          |

| Supply current               |                                                       | <b>V</b> S         | 1.2                    |      | 10.0                     | v        |

| Relay off                    | $T_{amb} = -40$ °C                                    |                    |                        |      |                          | mA       |

| Kelay on                     | $T_{amb} = 40 \text{ C}$ $T_{amb} = 125 \text{ °C}$   |                    |                        |      | 6                        | mA       |

| Relay on                     | $T_{amb} = -40^{\circ}C$<br>$T_{amb} = 125^{\circ}C$  |                    |                        |      | 15                       | mA<br>mA |

| Digital input WDI            |                                                       |                    |                        |      |                          |          |

| Detection low                |                                                       |                    | -0.2                   |      | $0.2 \times V_S$         | V        |

| Detection high               |                                                       |                    | $0.7 \times V_S$       |      | V <sub>S</sub> +0.5<br>V | V        |

| Resistance to V <sub>S</sub> |                                                       |                    | 10                     |      | 40                       | kΩ       |

| Input current low            | Input voltage = 0 V                                   |                    | 100                    |      | 550                      | μΑ       |

| Input current high           | Input voltage = V <sub>S</sub>                        |                    | -5                     |      | 5                        | μΑ       |

| Zener clamping voltage       |                                                       | V <sub>ZWDI</sub>  | 20                     |      | 24                       | V        |

| Digital input RIN            |                                                       |                    |                        |      |                          |          |

| Detection low                |                                                       |                    | -0.2                   |      | $0.2 \times V_S$         | V        |

| Detection high               |                                                       |                    | $0.7 \times V_S$       |      | V <sub>S</sub> +0.5<br>V | V        |

| Resistance to GND            |                                                       |                    | 10                     |      | 40                       | kΩ       |

| Input current low            | Input voltage = 0 V                                   |                    | -5                     |      | +5                       | μΑ       |

| Input current high           | Input voltage = V <sub>S</sub>                        |                    | 100                    |      | 550                      | μΑ       |

| Zener clamping voltage       |                                                       | V <sub>ZRIN</sub>  | 20                     |      | 24                       | V        |

| Digital output RESET wit     | h internal pull-up                                    |                    |                        |      |                          |          |

| Voltage high                 | Pull-up = $6 \text{ k}\Omega$                         |                    | $0.7 \times V_{S}+0.1$ |      | V <sub>S</sub>           | V        |

| Voltage low                  | $I \le 1 \text{ mA}$<br>1.2 V < V <sub>S</sub> < 16 V |                    | 0                      |      | 0.3                      | V        |

| Zener clamping voltage       |                                                       | V <sub>ZRESE</sub> | 26                     |      | 30                       | V        |

| Reset debounce time          | Switch to 'low'                                       | t <sub>deb</sub>   | 120                    | 320  | 500                      | μs       |

| Reset delay time             | Switch back to 'high'                                 | t <sub>del</sub>   |                        | 50   |                          | ms       |

| Digital output ENABLE w      | vith open collector                                   |                    |                        |      |                          |          |

| Saturation voltage low       | I ≤ 10 mA                                             |                    | 0.01                   |      | 0.5                      | V        |

| Zener clamping voltage       |                                                       | V <sub>ZEN</sub>   | 26                     |      | 30                       | V        |

## **Electrical Characteristics (continued)**

$V_S=5$  V,  $T_{amb}=-40$  to + 125°C; reference pin is GND;  $f_{intern}=100$  kHz + 50% - 45%,  $f_{WDC}=10$  kHz  $\pm$  10%;  $f_{WDI}=100$  Hz

| Parameter                                                             | Test Conditions / Pins                                                             | Symbol                                               | Min.       | Тур. | Max.             | Unit           |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------|------------|------|------------------|----------------|

| Current limitation                                                    |                                                                                    | I <sub>lim</sub>                                     | 10         |      |                  | mA             |

| Leakage current                                                       | $V_{\rm EN} = 5 \text{ V} \ V_{\rm EN} = 16 \text{ V} \ V_{\rm EN} = 26 \text{ V}$ | I <sub>EN5</sub> I <sub>EN16</sub> I <sub>EN26</sub> |            |      | 20<br>100<br>200 | μΑ<br>μΑ<br>μΑ |

| Reset debounce time                                                   | Switch to 'low'                                                                    | t <sub>deb</sub>                                     | 120        | 320  | 500              | μs             |

| Reset delay time                                                      | Switch back to 'high'                                                              | t <sub>del</sub>                                     |            | 85   |                  | ms             |

| Relay driver output RELAY                                             |                                                                                    |                                                      |            |      |                  |                |

| Saturation voltage                                                    | I ≤ 250 mA<br>I ≤ 130 mA                                                           | V <sub>Rsat</sub><br>V <sub>Rsat</sub>               |            |      | 0.5<br>0.3       | V<br>V         |

| Maximum load current                                                  | $T_{amb}$ –40 to 90°C<br>$T_{amb} > 90$ °C                                         | I <sub>R</sub><br>I <sub>R</sub>                     | 250<br>200 |      |                  | mA<br>mA       |

| Zener clamping voltage                                                |                                                                                    | V <sub>ZR</sub>                                      | 26         |      | 30               | V              |

| Turn-off enegy                                                        |                                                                                    |                                                      | 30         |      |                  | mJ             |

| Leakage current                                                       | $V_R = 16 \text{ V}$ $V_R = 26 \text{ V}$                                          | I <sub>R16</sub><br>I <sub>R26</sub>                 |            |      | 20<br>200        | μΑ<br>μΑ       |

| Reset and V <sub>S</sub> control                                      |                                                                                    |                                                      |            |      |                  |                |

| Lower reset level                                                     |                                                                                    | Vs                                                   | 4.5        |      | 4.7              | V              |

| Upper reset level                                                     |                                                                                    | V <sub>S</sub>                                       | 5.35       |      | 5.6              | V              |

| Hysteresis                                                            |                                                                                    |                                                      | 25         |      | 100              | mV             |

| Reset debounce time                                                   |                                                                                    |                                                      | 120        | 320  | 500              | μs             |

| Reset delay                                                           |                                                                                    |                                                      | 20         | 50   | 80               | ms             |

| RC oscillator WDC                                                     |                                                                                    |                                                      |            |      |                  |                |

| Oscillator frequency                                                  | $R_{OSC} = 39 \text{ k}\Omega,$<br>$C_{OSC} = 3.3 \text{ nF}$                      | f <sub>WDC</sub>                                     | 9          | 10   | 11               | kHz            |

| Watchdog timing                                                       |                                                                                    |                                                      |            |      |                  |                |

| Power-on-reset prolongation time                                      |                                                                                    | t <sub>POR</sub>                                     | 34 .3      |      | 103.1            | ms             |

| Detection time for RC-oscillator fault                                | $V_{RC} = const.$                                                                  | t <sub>RCerror</sub>                                 | 81.9       |      | 246              | ms             |

| Time interval for over-/<br>under voltage detection                   |                                                                                    | t <sub>D,OUV</sub>                                   | 0.16       |      | 0.64             | ms             |

| Reaction time of RESET output over/ under voltage                     |                                                                                    | t <sub>R,OUV</sub>                                   | .187       |      | 0.72             | ms             |

| Nominal frequency for WDI                                             | $f_{RC} = 100 \times f_{WDI}$                                                      | f <sub>WDI</sub>                                     | 10         |      | 130              | Hz             |

| Nominal frequency for WDC                                             | $f_{WDI} = 1/100 \times f_{WDC}$                                                   | f <sub>WDC</sub>                                     | 1          |      | 13               | kHz            |

| Minimum pulse duration for<br>a securely WDI input pulse<br>detection |                                                                                    | t <sub>P,WDI</sub>                                   | 182        |      |                  | μs             |

Rev. A2, 18-Jan-01 7 (12)

## **Electrical Characteristics (continued)**

$V_S=5$  V,  $T_{amb}=-40$  to + 125°C; reference pin is GND;  $f_{intern}=100$  kHz  $\pm$  50% - 45%,  $f_{WDC}=10$  kHz  $\pm$  10%;  $f_{WDI}=100$  Hz

| Parameter                                                       | Test Conditions / Pins    | Symbol                | Min. | Тур. | Max.  | Unit   |

|-----------------------------------------------------------------|---------------------------|-----------------------|------|------|-------|--------|

| Frequency range for a correct WDI signal                        |                           | f <sub>WDI</sub>      | 64.7 |      | 112.5 | Hz     |

| Number of incorrect WDI trigger counts for locking the outputs  |                           | n <sub>lock</sub>     |      | 3    |       |        |

| Number of correct WDI trigger counts for releasing the outputs  |                           | n <sub>release</sub>  |      | 3    |       |        |

| Detection time for a stucked WDI signal                         | V <sub>WDI</sub> = const. | t <sub>WDIerror</sub> | 24.5 |      | 25.5  | ms     |

| Watchdog timing relative to                                     | $f_{ m WDC}$              |                       |      |      |       |        |

| Minimum pulse duration for a securely WDI input pulse detection |                           |                       |      | 2    |       | cycles |

| Frequency range for a correct WDI signal                        |                           |                       | 80   |      | 169   | cycles |

| Hysteresis range at the WDI ok margins                          |                           |                       |      | 1    |       | cycle  |

| Detection time for a dropped out WDI signal                     | V <sub>WDI</sub> = const. |                       | 250  |      | 251   | cycles |

### Protection against transient voltages according to ISO TR 7637–3 level 4 (except pulse 5)

| Pulse | Voltage | Source<br>Resistance * | Rise Time | Duration | Amount |

|-------|---------|------------------------|-----------|----------|--------|

| 1     | – 110 V | 10                     | 100 V/s   | 2 ms     | 15.000 |

| 2     | + 110 V | 10                     | 100 V/s   | 0.05 ms  | 15.000 |

| 3a    | – 160 V | 50                     | 30 V/ns   | 0.1 s    | 1 h    |

| 3b    | + 150 V | 50                     | 20 V/ns   | 0.1 s    | 1 h    |

| 5     | 40 V    | 2                      | 10 V/ms   | 250 ms   | 20     |

<sup>\*</sup> Relay driver: relay coil with  $R_{min} = 70~\Omega$  to be added to the source resistance.

# **Timing Diagrams**

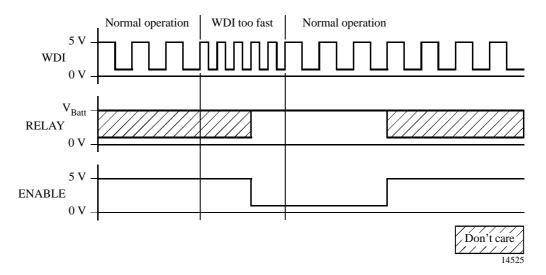

Figure 6. Watchdog in too-fast condition

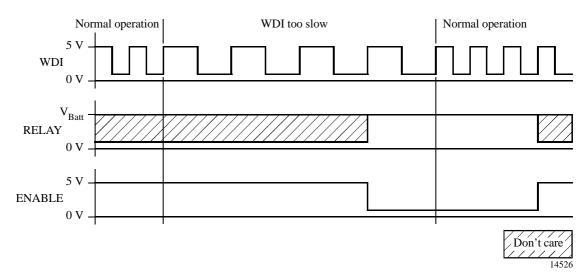

Figure 7. Watchdog in too-slow condition

Rev. A2, 18-Jan-01 9 (12)

Figure 8. Overvoltage condition

Figure 9. Undervoltage condition

Application Circuit

Figure 10. Application circuit

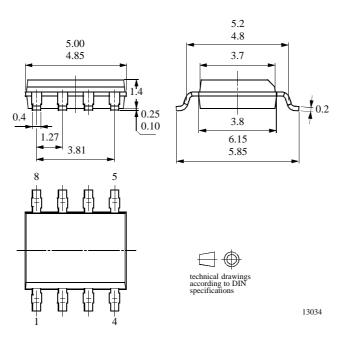

# **Package Information**

Package SO8

Dimensions in mm

Rev. A2, 18-Jan-01

### **Ozone Depleting Substances Policy Statement**

It is the policy of Atmel Germany GmbH to

- 1. Meet all present and future national and international statutory requirements.

- Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**Atmel Germany GmbH** has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**Atmel Germany GmbH** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice.

Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use Atmel Wireless & Microcontrollers products for any unintended or unauthorized application, the buyer shall indemnify Atmel Wireless & Microcontrollers against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

Data sheets can also be retrieved from the Internet: http://www.atmel-wm.com

11.

Atmel Germany GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2594, Fax number: 49 (0)7131 67 2423