19-3530; Rev 0; 1/05

EVALUATION KIT AVAILABLE

# Low-Jitter, 8kHz Reference Clock Synthesizer Outputs 35.328MHz

# **General Description**

The MAX9476 low-cost, high-performance clock synthesizer with an 8kHz input reference clock provides six buffered LVTTL clock outputs at 35.328MHz. The clock synthesizer can be used to generate the clocks for systems using T1, E1, T3, E3, and xDSL.

The MAX9476 features a phase-lock loop (PLL) that uses a voltage-controlled crystal oscillator (VCXO). The internal PLL phase locks the external crystal (35.328MHz) to the 8kHz input reference clock. In addition, this device generates a jitter-suppressed output that provides a better source for the reference clock relay.

The MAX9476 is available in a 24-pin TSSOP package and operates over the extended operating temperature range of -40°C to +85°C and a single +3V to +3.6V power-supply range. For using lower value external crystals, refer to the MAX9486 data sheet.

## Applications

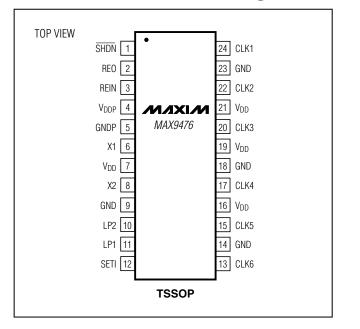

**Pin Configuration**

Telecom Equipment Using T1, E1, T3, E3, and ISDN Protocols

xDSL Equipment in CO with Interface to the Telecom Protocols

### \_Features

- ♦ 8kHz Input-Reference CLK

- 4ps<sub>RMS</sub> (typ) Output Jitter

- High-Jitter Rejection on the Reference CLK

- Synthesizer Locks to the 8kHz Reference with a ±100ppm Range

- Output Frequency: 35.328MHz

- Six Buffered LVTTL Low-Jitter Outputs

- ♦ One 8kHz Reference CLK Relay Output

- ♦ +3.3V Supply Operation

- ♦ 24-Pin TSSOP Package

# **Ordering Information**

| PART       | PIN-<br>TEMP RANGE PACKA |          | PKG<br>CODE |  |

|------------|--------------------------|----------|-------------|--|

| MAX9476EUG | -40°C to +85°C           | 24 TSSOP | U24-1       |  |

### ///XI//

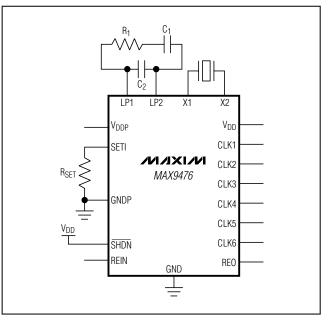

# Typical Application Circuit

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| 24-Pin TSSOP (derate 12.2mW/°C above                  | +70°C)976mW    |

| Operating Temperature Range                           | 40°C to +85°C  |

| Maximum Junction Temperature                          | +150°C         |

| Storage Temperature Range                             | 60°C to +150°C |

| ESD Rating (Human Body Model)                         | ±2kV           |

| Lead Temperature (soldering, 10s)                     | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# DC ELECTRICAL CHARACTERISTICS

$(V_{DD} = V_{DDP} = +3.0V$  to +3.6V,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{DD} = V_{DDP} = +3.3V$ ,  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                   | SYMBOL           | CONDITIONS             | MIN                       | ТҮР | MAX | UNITS |

|-----------------------------|------------------|------------------------|---------------------------|-----|-----|-------|

| DIGITAL INPUTS (REIN, SHDN) |                  | -                      |                           |     |     |       |

| Input-High Logic Level      | VIH              |                        | 2.0                       |     |     | V     |

| Input-Low Logic Level       | VIL              |                        |                           |     | 0.8 | V     |

| Input-Current High Level    | Ιн               | $V_{IN} = V_{DD}$      |                           |     | 20  | μA    |

| Input-Current Low Level     | ١ <sub>١</sub> ٢ | $V_{IN} = 0$           | -20                       |     |     | μΑ    |

| DIGITAL OUTPUT CLOCKS (CLK  | 1-CLK6, REG      | 0)                     |                           |     |     |       |

| Output-High Logic Level     | VOH              | I <sub>OH</sub> = -4mA | V <sub>DD</sub> -<br>0.6V |     |     | V     |

| Output-Low Logic Level      | V <sub>OL</sub>  | $I_{OL} = 4mA$         |                           |     | 0.4 | V     |

| POWER SUPPLY (VDD, VDDP)    |                  |                        |                           |     |     |       |

| Power-Supply Range          | V <sub>DD</sub>  |                        | 3.0                       |     | 3.6 | V     |

| PLL Power-Supply Range      | VDDP             |                        | 3.0                       |     | 3.6 | V     |

| Power-Supply Current        | IDD + IDDP       | (Note 2)               |                           | 9   | 16  | mA    |

| Shutdown Supply Current     | ISHDN            |                        |                           | 7.5 | 30  | μΑ    |

# AC ELECTRICAL CHARACTERISTICS

$(V_{DD} = V_{DDP} = +3.0V \text{ to } +3.6V, C_L = 20\text{pF}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted}. Typical values are at V_{DD} = V_{DDP} = +3.3V, T_A = +25^{\circ}\text{C}.)$  (Note 3)

| PARAMETER                       | SYMBOL          | CONDITIONS                                         | MIN  | ТҮР    | МАХ  | UNITS |

|---------------------------------|-----------------|----------------------------------------------------|------|--------|------|-------|

| DIGITAL OUTPUT CLOCKS (CLK      | (1-CLK6)        |                                                    |      |        |      |       |

| Frequency Range                 | fout            |                                                    |      | 35.328 |      | MHz   |

| Clock Rise Time                 | t <sub>R1</sub> | 20% to 80% V <sub>DD</sub>                         |      | 1.8    |      | ns    |

| Clock Fall Time                 | t <sub>F1</sub> | 80% to 20% V <sub>DD</sub>                         |      | 1.8    |      | ns    |

| Duty Cycle                      |                 |                                                    | 40   | 50     | 60   | %     |

| Dariad littar                   | JP1             | Peak-to-peak                                       |      | 83     |      | ps    |

| Period Jitter                   | JP2             | RMS                                                |      | 4      |      | psRMS |

| Output Skew                     | ts              | Peak-to-peak                                       |      | 185    |      | ps    |

| REFERENCE CLOCK OUTPUT (F       | REO)            |                                                    |      |        |      |       |

| Frequency                       | fREF            |                                                    |      | 8      |      | kHz   |

| Clock Rise Time                 | t <sub>R2</sub> |                                                    |      | 1.8    |      | ns    |

| Clock Fall Time                 | t <sub>F2</sub> |                                                    |      | 1.8    |      | ns    |

| Duty Cycle                      |                 |                                                    | 40   | 50     | 60   | %     |

| VCXO                            |                 |                                                    |      |        |      |       |

| Crystal Frequency               | fxtl            |                                                    |      | 35.328 |      | MHz   |

| Crystal Accuracy                |                 | Including frequency accuracy and temperature range |      | ±25    |      | ppm   |

| VCXO Pulling Range              |                 | (Note 4)                                           | -100 |        | +100 | ppm   |

| Input Reference CLK Pulse Width | tw              | Measured at high or low states                     | 10   |        |      | ns    |

**Note 1:** Specifications are 100% tested at  $T_A = +25^{\circ}C$ . Specifications over temperature are guaranteed by design and characterization. **Note 2:** No load on clock outputs.

Note 3: Guaranteed by design.

Note 4: Crystal loading capacitance is 14pF.

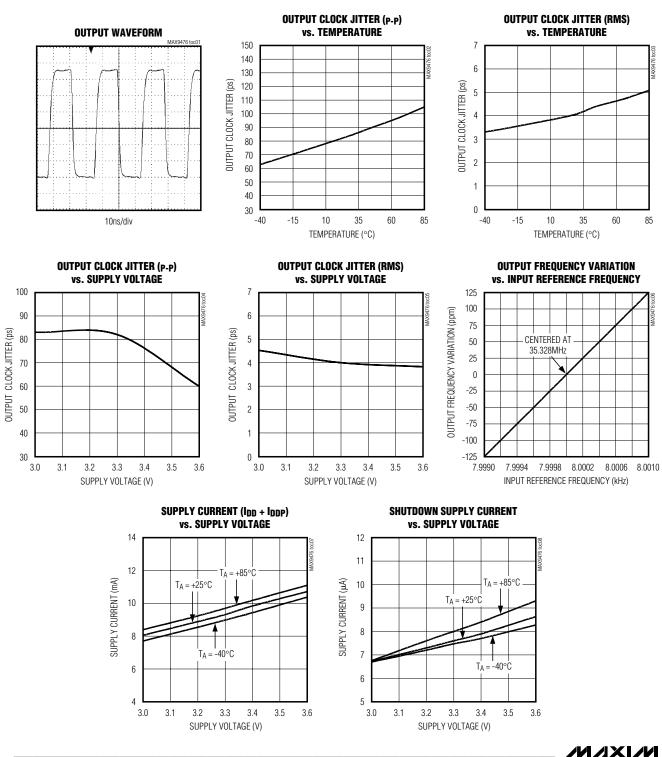

$(V_{DD} = V_{DDP} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Typical Operating Characteristics**

4

# Pin Description

| PIN              | NAME            | FUNCTION                                                                                                                                                                     |  |  |  |  |

|------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                | SHDN            | Active-Low Shutdown Input                                                                                                                                                    |  |  |  |  |

| 2                | REO             | Reference Clock Output. REO is an 8kHz reference clock output with jitter suppression.                                                                                       |  |  |  |  |

| 3                | REIN            | eference Input                                                                                                                                                               |  |  |  |  |

| 4                | VDDP            | Phase-Lock Loop (PLL) Power Supply. Bypass VDDP with 0.1µF and 0.001µF capacitors to GNDP.                                                                                   |  |  |  |  |

| 5                | GNDP            | PLL Ground                                                                                                                                                                   |  |  |  |  |

| 6                | X1              | Crystal Input 1. Connect X1 to a fundamental mode crystal for the VCXO.                                                                                                      |  |  |  |  |

| 7, 16, 19,<br>21 | V <sub>DD</sub> | Digital Power Supply. Bypass V <sub>DD</sub> with 0.1 $\mu$ F and 0.001 $\mu$ F capacitors to GND.                                                                           |  |  |  |  |

| 8                | X2              | Crystal Input 2. Connect X2 to a fundamental mode crystal for the VCXO.                                                                                                      |  |  |  |  |

| 9, 14, 18,<br>23 | GND             | Ground                                                                                                                                                                       |  |  |  |  |

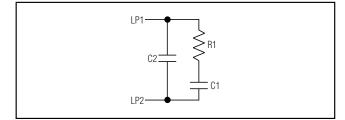

| 10               | LP2             | External Filter 2. Connect the loop filter capacitors and a resistor between LP1 and LP2 (see the <i>Typical Application Circuit</i> ). LP2 is internally connected to GNDP. |  |  |  |  |

| 11               | LP1             | External Filter 1. Connect the loop filter capacitors and a resistor between LP1 and LP2 (see the <i>Typical Application Circuit</i> ).                                      |  |  |  |  |

| 12               | SETI            | Charge-Pump Current-Setting Input. Connect a resistor from SETI to GNDP to set PLL charge-pump current (see the <i>Detailed Description</i> section).                        |  |  |  |  |

| 13               | CLK6            | Clock Output 6 at 35.328MHz                                                                                                                                                  |  |  |  |  |

| 15               | CLK5            | Clock Output 5 at 35.328MHz                                                                                                                                                  |  |  |  |  |

| 17               | CLK4            | Clock Output 4 at 35.328MHz                                                                                                                                                  |  |  |  |  |

| 20               | CLK3            | Clock Output 3 at 35.328MHz                                                                                                                                                  |  |  |  |  |

| 22               | CLK2            | Clock Output 2 at 35.328MHz                                                                                                                                                  |  |  |  |  |

| 24               | CLK1            | Clock Output 1 at 35.328MHz                                                                                                                                                  |  |  |  |  |

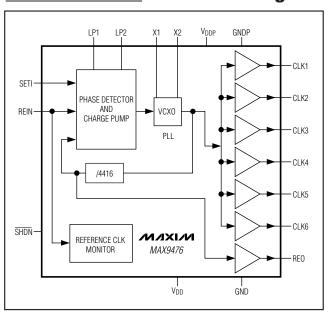

### Functional Diagram

of the reference CLK. However, if in a three-cycle time window the monitor counts two or three transitions, it considers the input reference clock as present. When the monitor detects the absence of the 8kHz reference clock, the outputs are operating at the center frequency of the crystal oscillator. However, when the monitor detects the return of the reference clock, the PLL locks to the reference clock. The ratio between the external crystal and the input reference clock is 4416.

**Clock Outputs (CLK1 to CLK6) and REO** The MAX9476 uses a 35.328MHz crystal and a reference clock (REIN) to generate six identical outputs, CLK1 to CLK6, at 35.328MHz. All CLK\_ outputs are LVTTL with a typical skew of 185ps. The MAX9476 also regenerates the 8kHz reference CLK at REO output.

#### Voltage-Controlled Crystal Oscillator (VCXO)

The MAX9476's internal VCXO takes an external 35.328MHz crystal as the base frequency and has a pulling range of approximately ±100ppm. This configuration also makes the VCXO PLL become a narrowband filter to reject high-frequency jitter on the input reference and eliminate it from the REO and CLK\_ outputs.

#### **SHDN** Mode

The MAX9476 features a shutdown mode with a supply current of  $7.5\mu A$  (typ). Drive SHDN low to get the device into shutdown mode. In this mode, all the outputs go low and the PLL is powered down. After SHDN goes high, the outputs still stay low for an additional 256ms to allow the PLL to be stabilized before the outputs are enabled again.

### **Applications Information**

#### **Crystal Selection**

The MAX9476 uses a 35.328MHz crystal as the base frequency for the VCXO. It is important to use a correct type of quartz crystal to avoid reducing frequency pulling range, or excessive output phase jitter.

Choose an AT-cut crystal that oscillates at 35.328MHz on its fundamental mode with a variation of ±25ppm including frequency accuracy and operating temperature range. The crystal's load capacitance should be 14pF. Pulling range may vary depending on the crystal used. Refer to the MAX9476 evaluation kit for details.

# **Detailed Description**

The MAX9476 is a high-performance clock synthesizer with an 8kHz input reference clock. This device generates six identical buffered LVTTL clock outputs at 35.328MHz. The internal PLL phase locks the external crystal (35.328MHz) to the 8kHz input reference clock. This device features a low-jitter output that provides a better source for the reference clock relay (see the *Functional Diagram*).

**Power-Up** At power-up, all the outputs are disabled and pulled low (to GND) for at least 256ms. After 256ms, the crystal oscillator starts oscillation. If the reference clock is not present at power-up, the outputs are forced to the center frequency of the crystal oscillator.

#### **Reference CLK Monitor**

The MAX9476 features internal clock (CLK) monitor circuitry to detect the presence of the external 8kHz reference clock. The internal CLK monitor continuously monitors the number of low-to-high transitions within a three-cycle (at 8kHz) time window. If the transition number is less than two, the internal CLK monitor states loss

#### PLL Loop Filter

The PLL contains an integrated VCXO that uses an external crystal to track the input reference signal and attenuate input jitter. Figure 1 shows the external loop filter of the PLL containing resistor R1 and two capacitors, C1 and C2. This loop filter is connected between LP1 and LP2 as shown in the *Typical Operating Circuit*. The loop-filter bandwidth is determined by C1, C2, R1, and RSET where RSET is used to set the value of the charge-pump current. The typical values of C1, C2, R1, and RSET are 22nF, 560pF, 1000k $\Omega$ , and 13k $\Omega$ , respectively.

Use the following equation to calculate a PLL loop bandwidth in Hz:

where R1 ( $\Omega$ ) is the resistor in the PLL loop filter (Figure 1), I<sub>SETI</sub> (A) is the charge-pump current calculated from the equation in the *Charge-Pump Current Setting* section, and N is the crystal PLL frequency divider equal to 4416.

The loop-damping factor is calculated by:

DampingFactor =

$$\frac{R_1}{2} \times \sqrt{\frac{8832 \times I_{SETI} \times C_1}{N}}$$

where C1 (F) and R1 ( $\Omega$ ) are the values of the capacitor and the resistor in the PLL loop filter shown in Figure 1; ISETI is calculated as shown in the *Charge-Pump Current Setting* section and N = 4416.

The following equation shows the relationship between components C1 and C2 in the loop filter:

#### $C2 \leq C1/20$

#### **Charge-Pump Current Setting**

The MAX9476 also allows external setting of the chargepump current in the PLL. Connect a resistor from SETI to GNDP to set the PLL charge-pump current:

Charge-Pump Current =  $2.4 \times 1000 / (R_{SET}(k\Omega) + 1)$

Figure 1. Typical Loop Filter

where  $R_{SET}$  is in  $k\Omega$  and the value of the charge-pump current is in  $\mu A.$

The loop response can be adjusted to meet individual application requirements since the charge-pump current and all the filter components for the VCXO loop can be set externally.

#### **Board Layout and Bypassing**

The MAX9476's high oscillator frequency makes proper layout important to ensure stability. For best performance, place components as close as possible to the device.

Digital or AC transient signals on GND can create noise at the clock outputs. Return GND to the highest quality ground available. Bypass  $V_{DD}$  and  $V_{DDP}$  with  $0.1\mu$ F and  $0.001\mu$ F capacitors, placed as close to the device as possible. Careful PC board ground layout minimizes crosstalk between the outputs and digital inputs.

Traces must be as short as possible on LP1 and LP2 and connect the capacitors and the resistor as close as possible to the device.

## **Chip Information**

TRANSISTOR COUNT: 7512 PROCESS: CMOS

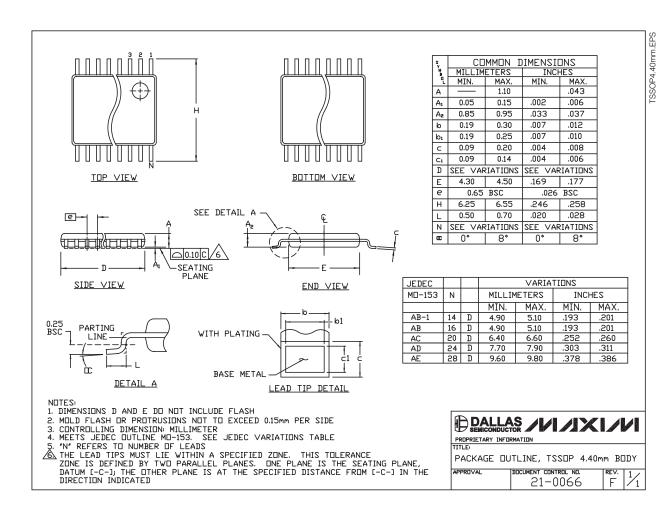

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### \_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2005 Maxim Integrated Products

8

Printed USA *maxim* is a registered trademark of Maxim Integrated Products, Inc.