S3160 Data Sheet

# 2.5 Gbps Wide Bandwidth Transimpedance Amplifier

# **FEATURES**

- · Greater than 2 GHz Bandwidth

- 3 kΩ differential transimpedance

- Single 3.3 V supply

- 6.5 pA/√(Hz) typical noise current density

- 2.2 mA peak to peak max input current

- Voltage limited outputs

- Maximum Die size: 1.27 mm by 1.27 mm

### **APPLICATIONS**

- SONET OC-48

- Fiber optic data links

# **GENERAL DESCRIPTION**

The S3160 is a high-speed transimpedance amplifier (TIA) for 2.5 Gbps applications. Input currents as high as 2.2 mA can be amplified with low duty cycle distortion. The low input noise allows signals down to 4  $\mu$ A (peak to peak) to be detected with a signal to noise ratio of 22 dB (allows for BER< 1E-10).

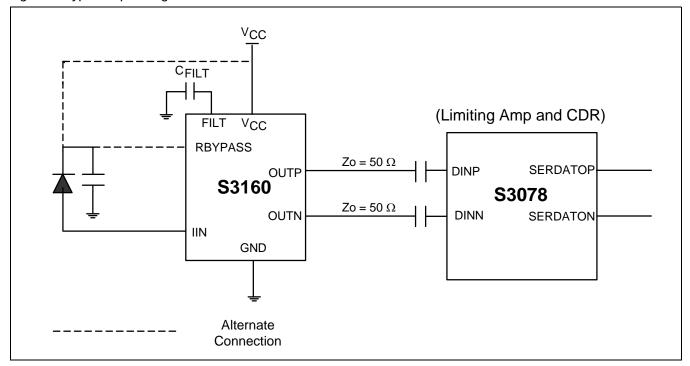

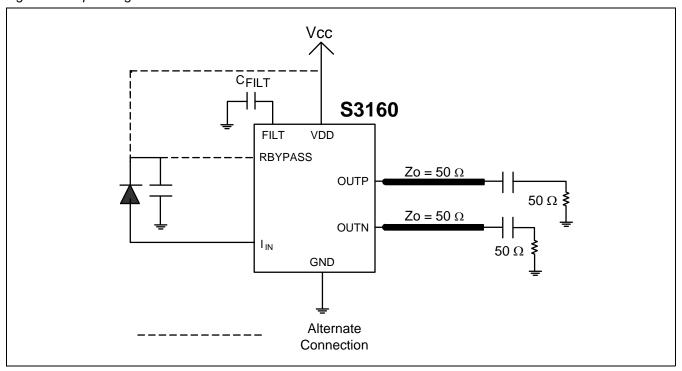

The outputs are voltage limited to 1000 mV, differential, in order to allow a wide input dynamic range without exceeding the input voltage range of the post (limiting) amplifier. Figure 1 shows a typical application.

Figure 1. Typical Operating Circuit

### **DETAILED DESCRIPTION**

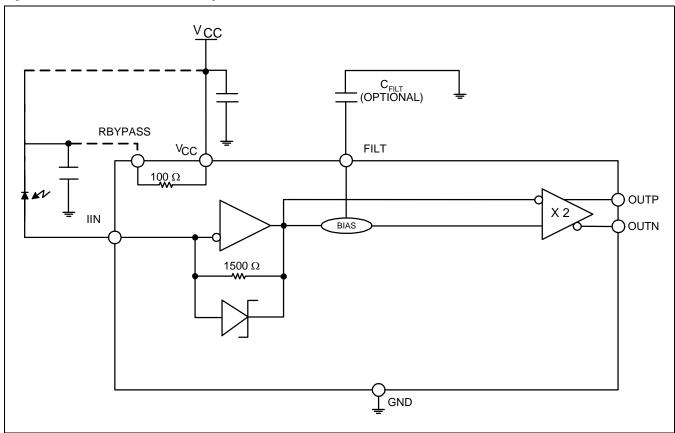

Figure 2 depicts the overall block diagram of the S3160 transimpedance amplifier. The amplifier circuitry consists of a transimpedance stage and an output driver stage with a 6 dB gain. The transimpedance amplifier converts the photodiode photocurrent to a voltage. The photodiode can be biased by connecting it to the RBYPASS pin or it can be connected directly to  $V_{\rm CC}$ .

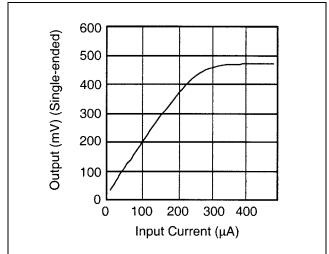

The amplifier gain is linear for an input of up to 300  $\mu$ A. Above that the transimpedance of the input stage is reduced by the action of the schottky diode, to prevent overdrive of the output stage. The output of the output stage begins to fully limit when the input current reaches 700  $\mu$ A. The output voltage is limited at 1000 mV, differential, peak to peak.

The output of the transimpedance stage is converted to a differential signal by the combination of the output stage and a bias block. This bias block averages the output of the transimpedance stage and establishes the DC input reference for the output stage. The bandwidth of this circuit is set by an on-chip capacitor, but can be reduced by adding an off-chip capacitor,  $C_{FILT}$ . This bandwidth corresponds to the low frequency -3 dB cutoff of the TIA. Increasing the value of  $C_{FILT}$  will reduce the low frequency -3 dB cutoff. With no  $C_{FILT}$  capacitor added it will be at 45 kHz.

Figure 2. S3160 Detailed Block Diagram

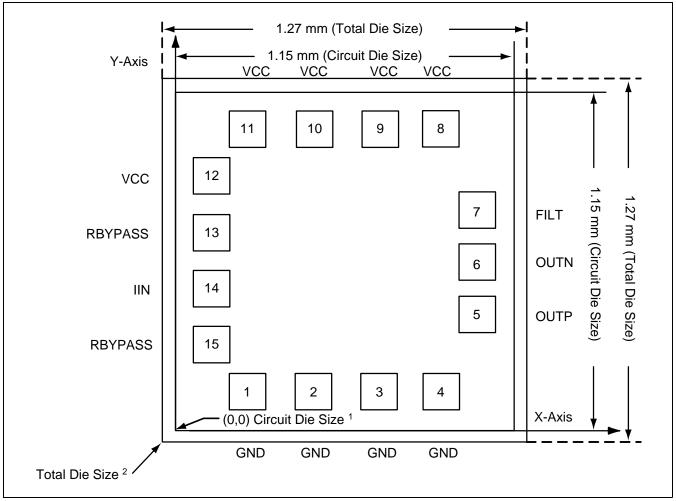

Table 1. S3160 Pad Assignment and Description

| Pin Name | I/O | Pad #                    | Coordinates [X,Y] <sup>(1)</sup>                                                          | Description                                                                                                                               |

|----------|-----|--------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| vcc      | S   | 8<br>9<br>10<br>11<br>12 | [868.9, 1051.4]<br>[669.6, 1051.4]<br>[470.8, 1051.4]<br>[271.8, 1051.4]<br>[90.8, 892.5] | +3.3 V Power supply.                                                                                                                      |

| GND      | S   | 1<br>2<br>3<br>4         | [273, 91.4]<br>[472, 91.4]<br>[670.8, 91.4]<br>[870.1, 91.4]                              | Ground.                                                                                                                                   |

| RBYPASS  | I   | 13<br>15                 | [100.925, 702.425]<br>[90.9, 293.3]                                                       | Bypass connection for cathode of photodiode.                                                                                              |

| IIN      | 1   | 14                       | [97.575, 473.975]                                                                         | PIN diode input.                                                                                                                          |

| FILT     | I   | 7                        | [1052.3. 777]                                                                             | Filter capacitor input. A capacitor to ground can be added at this pad to reduce the low frequency -3 dB cutoff. (See Design Procedures). |

| OUTN     | 0   | 6                        | [1049.275, 567.475]                                                                       | Negative transimpedance amplifier output.                                                                                                 |

| OUTP     | 0   | 5                        | [1049.275, 375.225]                                                                       | Positive transimpedance amplifier output.                                                                                                 |

<sup>1.</sup> The coordinates represent the position of the center of the pad in  $\mu m$ , with respect to the lower left corner of the circuit die.

<sup>2.</sup> Note: I = Input pin, O = Output pin, S = Supply pin.

Figure 3. S3160 Bonding Pad Location

Note: Pad Size is 94  $\mu$ m X 94  $\mu$ m. The exposed area of the pad is 80  $\mu$ m X 80  $\mu$ m. Die thickness is 254  $\mu$ m (10 mils).

- The circuit die size is the smallest possible size of the die. The lower left-hand corner of the circuit die is the

origin of the xy-coordinate system. Pad coordinates indicated in Table 1 are measured from this origin to the

pad's center.

- 2. The total die size is the largest possible size of the die. It includes a splicing area around the circuit die. The actual size of any given die may vary in size from the minimum (circuit die) size to the maximum (total die) size.

Table 2. Recommended Operating Conditions

| Parameter                                      | Min   | Тур | Max   | Units |

|------------------------------------------------|-------|-----|-------|-------|

| Ambient Temperature, T <sub>A</sub>            | -40   |     | +85   | °C    |

| Junction Operating Temperature, T <sub>J</sub> | -20   |     | +105  | °C    |

| Voltage on V <sub>CC</sub> with respect to GND | 3.135 | 3.3 | 3.465 | V     |

#### Table 3. Absolute Maximum Ratings

The following are the absolute maximum stress ratings for the S3160. Stresses beyond those listed may cause permanent damage to the device. Absolute maximum ratings are stress ratings only and operation of the device at the maximums stated or any other conditions beyond those indicated in the "Recommended Operating Conditions" of this document are not inferred. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                                      | Min  | Тур | Max                  | Units |

|------------------------------------------------|------|-----|----------------------|-------|

| Voltage on V <sub>CC</sub> with respect to GND | -0.5 |     | 4                    | V     |

| Voltage on all Other Pads                      | -0.5 |     | V <sub>CC</sub> +0.3 | V     |

| Storage Temperature Range                      | -55  |     | 150                  | °C    |

#### Electrostatic Discharge (ESD) Sensitivity Rating - Human Body Model (HBM):

The S3160 is rated to the following ESD voltages based upon JEDEC standard: JESD22-A114-B

CLASS 0 - All pins are rated at or above 1000 volts except pins I<sub>IN</sub>, OUTP and OUTN. OUTP and OUTN are rated at 500 V and I<sub>IN</sub> is rated to 100 volts

Adherence to standards for ESD protection should be taken during the handling of the devices to ensure that the devices are not damaged. The standards to be used are defined in ANSI standard ANSI/ESD S20.20-1999, "Protection of Electrical and Electronic Parts, Assemblies and Equipment." Contact your local FAE or sales representative for applicable ESD application notes.

Table 4. AC Electrical Characteristics (Vcc = 3.3 V  $\pm$  5%,  $T_{\rm A}$  = -40°C to +85°C)

| Parameter           | Description                               | Min  | Тур  | Max  | Units    | Conditions                                                                |

|---------------------|-------------------------------------------|------|------|------|----------|---------------------------------------------------------------------------|

| R <sub>T</sub>      | AC Transimpedance                         | 2.56 | 2.95 | 3.34 | kV/A     | 50 Ohm load                                                               |

| BW                  | -3 dB Bandwidth                           | 2.7  | 3.2  | 3.6  | GHz      | 0.5 pF photodiode capacitance,<br>1.5 nH input bond wire<br>inductance.   |

| BW <sub>LF</sub>    | Low Frequency -3 dB Cutoff                |      | 45   | 57   | kHz      | No C <sub>FILT</sub> connected                                            |

| I <sub>PK</sub>     | Maximum Input Current                     | 2.2  |      |      | mA       | Peak-to-peak                                                              |

| V <sub>OD</sub>     | Maximum Differential output voltage       |      | 1000 | 1200 | mV       | Peak-to-peak, differential                                                |

| I <sub>IN, CL</sub> | Input Current before clipping             | 250  | 300  |      | μА       | 1 dB compression point                                                    |

| I <sub>ND</sub>     | Input Noise Current Density               |      | 6.5  | 9.3  | pA/√(Hz) | 0 - 2.5 GHz                                                               |

| I <sub>N</sub>      | Input Noise Current                       |      | 325  | 465  | nA       | (Output rms noise)/RT, 2.5 GHz bandwidth                                  |

| J <sub>T</sub>      | Total Jitter (Pk to Pk)<br>(At 1E-12 BER) |      |      | 0.12 | UI       | Input is 2.488 Gbps,<br>2 <sup>23</sup> -1 PRBS. I <sub>IN</sub> = 2.2 mA |

| RIPPLE              | Output Ripple                             | -0.5 |      | +0.5 | dB       | 1 - 2000 MHz                                                              |

| Group Delay         | Group Delay Variation                     | -25  |      | +25  | pS       | 100 - 2500 MHz                                                            |

| S22                 | Output Reflection Coefficient             |      |      | -18  | dB       | 1 - 3500 MHz                                                              |

| R <sub>OUT</sub>    | Output Impedance                          | 45   | 50   | 58   | Ω        |                                                                           |

Table 5. DC Electrical Characteristics (Vcc = 3.3 V  $\pm$  5%,  $T_{\rm A}$  = -40°C to +85°C)

| Parameter         | Description                | Min                     | Тур                      | Max                      | Units | Conditions                                                                                |

|-------------------|----------------------------|-------------------------|--------------------------|--------------------------|-------|-------------------------------------------------------------------------------------------|

| lcc               | Supply Current             |                         | 40                       | 57                       | mA    |                                                                                           |

| V <sub>BIAS</sub> | Input Bias Voltage         | 0.79                    | 0.92                     | 1.0                      | V     |                                                                                           |

| V <sub>CM</sub>   | Common Mode Output Voltage | V <sub>CC</sub><br>-0.9 | V <sub>CC</sub><br>-0.65 | V <sub>CC</sub><br>-0.25 | V     | $50\Omega$ line termination to GND (AC Coupled) or 100 $\Omega$ line-to-line termination. |

Note: AC Electrical Characteristics are guaranteed by characterization.

# **DESIGN PROCEDURES**

# **Determining Capacitor Values**

$C_{FILT}$  can be selected using the formula: Low frequency –3 dB cutoff = 1 / [ $2\pi^*400$ k $\Omega^*(10$ pF +  $C_{FILT})$ ]

### APPLICATION INFORMATION

### Filtering Through RBYPASS

To reduce the effect of supply voltage noise at the cathode of the photodiode, the cathode connection to  $V_{CC}$  should be made through the RBYPASS resistor. The RBYPASS resistor and an external capacitor to ground at the cathode of the photodiode will act as a filter to reduce this noise and dampen any resonance at the cathode of the photodiode.

## Wire Bonding and Layout Information

For best performance all GND pads should be connected and the bond wire inductance between the photodiode and the IIN pin should be kept to below 1.5 nH - 2 nH. The back of the die is not metallized and should be connected to ground or left electrically unconnected.

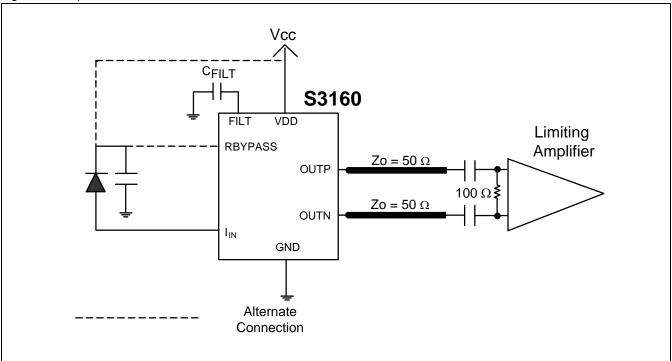

The outputs OUTP and OUTN should be terminated equally to prevent instabilities. Figures 4 and 5 show the differential and single-ended terminations.

Figure 4. Output Differential Termination

Figure 5. Output Single-Ended Termination

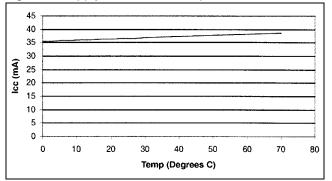

# **Typical Operating Characteristics**

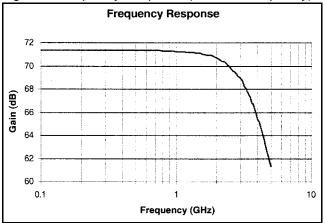

Figure 6. Frequency Response (Gain vs. Frequency)

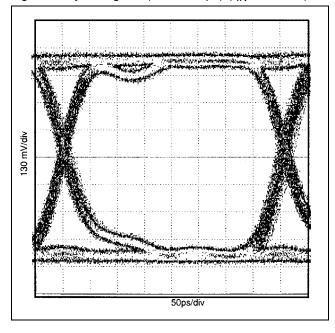

Figure 7. Eye Diagram (at 2.5 Gbps) ( $I_{IN} = 2.2 \text{ mA}$ )

Figure 8. Output Voltage vs. Input Current

Figure 9. Supply Current vs. Temperature

# Data Sheet

# **DOCUMENT REVISION HISTORY**

| Revision | Date     | Description                                                                                                          |

|----------|----------|----------------------------------------------------------------------------------------------------------------------|

| А        | 08/12/04 | • Pg. 6, Table 4, changed S22 Max from -22 dB to -18 dB; changed R $_{ m out}$ Max from 55 $\Omega$ to 58 $\Omega$ . |

| NC       | 2/28/01  | Production release version.                                                                                          |

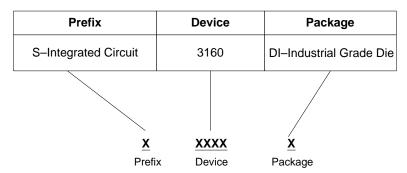

# **Ordering Information**

Applied Micro Circuits Corporation 6290 Sequence Dr., San Diego, CA 92121

Phone: (858) 450-9333 — (800) 755-2622 — Fax: (858) 450-9885 http://www.amcc.com

AMCC reserves the right to make changes to its products, its datasheets, or related documentation, without notice and warrants its products solely pursuant to its terms and conditions of sale, only to substantially comply with the latest available datasheet. Please consult AMCC's Term and Conditions of Sale for its warranties and other terms, conditions and limitations. AMCC may discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information is current. AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others. AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC is a registered Trademark of Applied Micro Circuits Corporation. Copyright © 2005 Applied Micro Circuits Corporation.