# 3.3 V, Wide Bandwidth, 2- to -1-Port (DPDT) Switch with Enable

ON Semiconductor's NLAS7222A series of analog switch circuits are produced using the company's advanced sub-micron CMOS technology, achieving industry-leading performance.

The NLAS7222A is a 2– to 1–port analog switch. Its wide bandwidth and low bit–to–bit skew allow it to pass high–speed differential signals with good signal integrity. The switch is bidirectional and offers little or no attenuation of the high–speed signals at the outputs. Industry–leading advantages include a propagation delay of less than 250 ps, resulting from its low channel resistance and low I/O capacitance. Its high channel–to–channel crosstalk rejection results in minimal noise interference. Its bandwidth is wide enough to pass High–Speed USB 2.0 differential signals (480 Mb/s).

#### **Features**

- $R_{ON}$  is Typically 6.5  $\Omega$  at  $V_{CC} = 3 \text{ V}$

- Low Bit-to-Bit Skew: Typically 50 ps

- OVT on D+ and D- up to 3.6 V

- Power OFF Protection:

When  $V_{CC} = 0$  V, D+ and D- Can Tolerate up to 3.6 V

- Low Crosstalk: -45 dB @ 250 MHz

- Low Current Consumption: 1 μA

- Near-Zero Propagation Delay: 250 ps

- Channel On–Capacitance: 6.5 pF (Typical)

- V<sub>CC</sub> Operating Range: +3.0 V to +3.6 V

- > 720 MHz Bandwidth (or Data Frequency)

- This is a Pb-Free Device

# **Typical Applications**

- Differential Signal Data Routing

- USB 2.0 Signal Routing

### **Important Information**

• Continuous Current Rating Through Each Switch ±50 mA

# ON Semiconductor®

http://onsemi.com

### MARKING DIAGRAM

WQFN-10 CASE 488AQ

XX = S

= Specific Device Code

M = Date Code

= Pb-Free Device

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 9 of this data sheet.

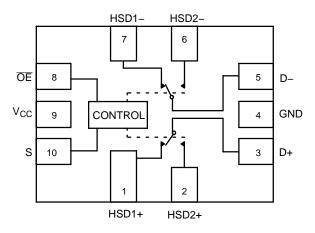

Figure 1. Pin Connections and Logic Diagram (Top View)

## **Table 1. PIN DESCRIPTION**

| Pin                                   | Function      |

|---------------------------------------|---------------|

| S                                     | Select Input  |

| ŌĒ                                    | Output Enable |

| HSD1+, HSD1-, HSD2+,<br>HSD2-, D+, D- | Data Ports    |

### **Table 2. TRUTH TABLE**

| ŌĒ | s | HSD1+,<br>HSD1– | HSD2+,<br>HSD2- |

|----|---|-----------------|-----------------|

| 1  | Χ | OFF             | OFF             |

| 0  | 0 | ON              | OFF             |

| 0  | 1 | OFF             | ON              |

### **MAXIMUM RATINGS**

| Symbol          | Parameter                                                           | Value                                         | Unit |

|-----------------|---------------------------------------------------------------------|-----------------------------------------------|------|

| V <sub>CC</sub> | Positive DC Supply Voltage                                          | -0.5 to +4.6                                  | V    |

| V <sub>IS</sub> | Analog Switch Input Voltage<br>HSD1+, HSD1-, HSD2+, HSD2-<br>D+, D- | -0.5 to V <sub>CC</sub> + 0.3<br>-0.5 to +4.6 | V    |

| V <sub>IN</sub> | Digital Select Input Voltage                                        | -0.5 to +4.6                                  | V    |

| I <sub>D</sub>  | Continuous DC Current (Through Analog Switch)                       | 50                                            | mA   |

| P <sub>D</sub>  | Power Dissipation                                                   | 0.5                                           | W    |

| T <sub>S</sub>  | Storage Temperature                                                 | -65 to +150                                   | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# **RECOMMENDED OPERATING CONDITIONS**

| Symbol                          | Parameter                               | Parameter                                  |                 |    | Unit |

|---------------------------------|-----------------------------------------|--------------------------------------------|-----------------|----|------|

| V <sub>CC</sub>                 | Positive DC Supply Voltage              | 3.0                                        | 3.6             | V  |      |

| V <sub>IS</sub>                 | Analog I/O Voltage (HSD1+, HSD1-, HSD2- | GND                                        | V <sub>CC</sub> | V  |      |

| Vos                             | Analog Common Output Voltage (D+, D-)   | GND                                        | 3.6             | V  |      |

| V <sub>IN</sub>                 | Digital Select Input Voltage            | GND                                        | V <sub>CC</sub> | V  |      |

| T <sub>A</sub>                  | Operating Temperature Range             | -40                                        | +85             | °C |      |

| t <sub>r</sub> , t <sub>f</sub> | Input Rise or Fall Time                 | $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ | 0               | 15 | ns   |

# DC ELECTRICAL CHARACTERISTICS FOR USB 2.0 SWITCHING OVER OPERATIONAL RANGE

|                       |                                                          |                                                            |                     | -4  | 10°C to +85°    | C    |      |

|-----------------------|----------------------------------------------------------|------------------------------------------------------------|---------------------|-----|-----------------|------|------|

| Symbol                | Parameter                                                | Test Conditions                                            | V <sub>CC</sub> (V) | Min | Typ<br>(Note 1) | Max  | Unit |

| V <sub>IH</sub>       | Input HIGH Voltage (V <sub>IN</sub> )                    |                                                            | 3.0 to 3.6          | 1.3 | -               | -    | V    |

| V <sub>IL</sub>       | Input LOW Voltage (V <sub>IN</sub> )                     |                                                            | 3.0 to 3.6          | -   | -               | 0.5  | V    |

| V <sub>IK</sub>       | Clamp Diode Voltage                                      | I <sub>IS</sub> = -18 mA                                   | 3.0                 | -   | -               | -1.2 | V    |

| I <sub>CC</sub>       | Quiescent Supply Current                                 | $V_{IS} = V_{CC}$ or GND; $I_D = 0$ A                      | 3.6                 | -   | -               | 1.0  | μΑ   |

| ГССТ                  | Increase in I <sub>CC</sub> per<br>Control Voltage       | V <sub>IN</sub> = 2.6 V                                    | 3.6                 | -   | -               | 10.0 | μΑ   |

| I <sub>I</sub>        | Input Leakage Current                                    | $0 \le V_{IS} \le V_{CC}$                                  | 3.6                 | _   | -               | ±1.0 | μΑ   |

| I <sub>OZ</sub>       | OFF State Leakage                                        | $0 \le V_{IS}$ ; $V_{OS} \le V_{CC}$                       | 3.6                 | _   | -               | ±1.0 | μΑ   |

| l <sub>OFF</sub>      | Power OFF Leakage Current (D+, D-)                       | $0 \le V_{IS}$ ; $V_{OS} \le V_{CC}$                       | 0                   | -   | -               | ±1.0 | μΑ   |

| R <sub>ON</sub>       | Switch On–Resistance                                     | $V_{IS} = 0 \text{ to } 0.4 \text{ V}; I_D = 8 \text{ mA}$ | 3.0                 | _   | 6.5             | 9.0  | Ω    |

| R <sub>FLAT(ON)</sub> | On–Resistance Flatness                                   | $V_{IS} = 0$ to 1.0 V; $I_D = 8$ mA                        | 3.0                 | _   | 2.0             | _    | Ω    |

| ΔR <sub>ON</sub>      | On–Resistance match from center ports to any other ports | $V_{IS} = 0 \text{ to } 0.4 \text{ V}; I_D = 8 \text{ mA}$ | 3.0                 | -   | 0.35            | -    | Ω    |

<sup>1.</sup> Typical values are at  $V_{CC}$  = 3.3 V and  $T_A$  = +25  $^{\circ}C$

### **AC ELECTRICAL CHARACTERISTICS**

| Symbol            | Parameter Test Conditions      |                                     | V <sub>CC</sub> (V) | -4  | °C              | Unit |     |

|-------------------|--------------------------------|-------------------------------------|---------------------|-----|-----------------|------|-----|

|                   |                                |                                     |                     | Min | Typ<br>(Note 2) | Max  |     |

| t <sub>ON</sub>   | Turn-ON Time                   | V <sub>IS</sub> = 0.8 V             | 3.0 to 3.6          | -   | 13.0            | 30.0 | ns  |

| t <sub>OFF</sub>  | Turn-OFF Time                  | V <sub>IS</sub> = 0.8 V             | 3.0 to 3.6          | _   | 12.0            | 25.0 | ns  |

| t <sub>BBM</sub>  | Break-Before-Make Delay        | V <sub>IS</sub> = 0.8 V             | 3.0 to 3.6          | 2.0 | 4.7             | 6.5  | ns  |

| t <sub>PD</sub>   | Propagation Delay              | C <sub>L</sub> = 10 pF              | 3.0 to 3.6          | -   | 0.25            | -    | ns  |

| O <sub>IRR</sub>  | OFF-Isolation                  | $f$ = 250 MHz; $R_L$ = 50 $Ω$       | 3.0 to 3.6          | -   | -28             | -    | dB  |

| X <sub>TALK</sub> | Non-Adjacent Channel Crosstalk | $f$ = 250 MHz; $R_L$ = 50 $Ω$       | 3.0 to 3.6          | -   | -45             | -    | dB  |

| BW                | -3 dB Bandwidth                | $R_L = 50 \ \Omega; \ C_L = 0 \ pF$ | 0.04-0.0            | -   | 720             | -    | MHz |

|                   |                                | $R_L = 50 \Omega; C_L = 5 pF$       | 3.0 to 3.6          | _   | 500             | -    |     |

# AC ELECTRICAL CHARACTERISTICS FOR USB 2.0 SWITCHING OVER OPERATIONAL RANGE

| t <sub>SK(O)</sub>  | Channel-to-Channel Skew | C <sub>L</sub> = 10 pF                            | 3.0 to 3.6 | - | 0.05 | - | ns |

|---------------------|-------------------------|---------------------------------------------------|------------|---|------|---|----|

| T <sub>JITTER</sub> | Total Jitter            | $R_L = 50 \Omega$ ; $C_L = 10 pF$                 | 3.0 to 3.6 | - | 0.2  | _ | ns |

|                     |                         | $t_r = t_f = 500 \text{ ps at } 480 \text{ Mbps}$ |            |   |      |   |    |

<sup>2.</sup> Typical values are at  $V_{CC}$  = 3.3 V and  $T_A$  = +25°C

# CAPACITANCE

| Symbol           | Parameter                     | Parameter Test Conditions                                        |     | -40°C to +85°C  |     |    |

|------------------|-------------------------------|------------------------------------------------------------------|-----|-----------------|-----|----|

|                  |                               |                                                                  | Min | Typ<br>(Note 3) | Max |    |

| C <sub>IN</sub>  | Control Pin Input Capacitance | V <sub>CC</sub> = 0 V                                            | -   | 4.5             | _   | pF |

| C <sub>ON</sub>  | HSD+, HSD- ON Capacitance     | V <sub>CC</sub> = 3.3 V; <del>OE</del> = 0 V                     | -   | 14              | _   | pF |

| C <sub>OFF</sub> | HSD+, HSD- OFF Capacitance    | $V_{CC} = V_{IS} = 3.3 \text{ V}; \overline{OE} = 3.3 \text{ V}$ | _   | 12              | _   | pF |

<sup>3.</sup> Typical values are at  $V_{CC}$  = 3.3 V and  $T_A$  = +25°C

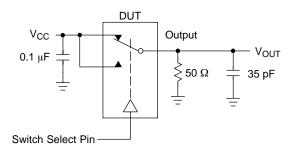

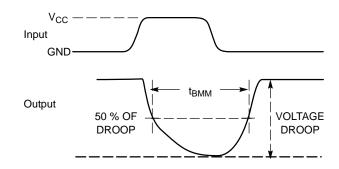

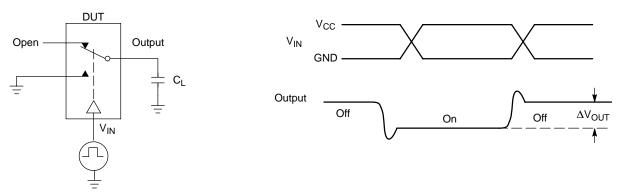

Figure 2. t<sub>BBM</sub> (Time Break-Before-Make)

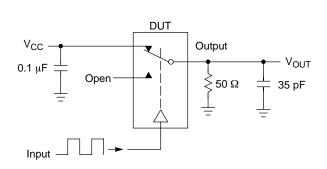

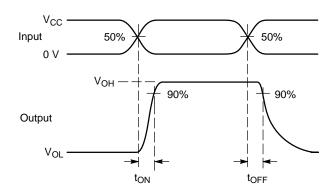

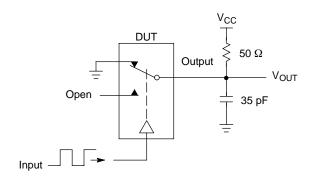

Figure 3. t<sub>ON</sub>/t<sub>OFF</sub>

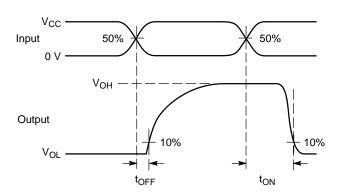

Figure 4. t<sub>ON</sub>/t<sub>OFF</sub>

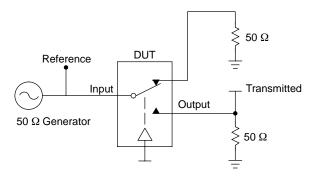

Channel switch control/s test socket is normalized. Off isolation is measured across an off channel. On loss is the bandwidth of an On switch.  $V_{\text{ISO}}$ , Bandwidth and  $V_{\text{ONL}}$  are independent of the input signal direction.

$$\begin{split} &V_{ISO} = \text{Off Channel Isolation} = 20 \text{ Log}\bigg(\frac{V_{OUT}}{V_{IN}}\bigg) \text{ for } V_{IN} \text{ at } 100 \text{ kHz} \\ &V_{ONL} = \text{On Channel Loss} = 20 \text{ Log}\bigg(\frac{V_{OUT}}{V_{IN}}\bigg) \text{ for } V_{IN} \text{ at } 100 \text{ kHz to } 50 \text{ MHz} \end{split}$$

Bandwidth (BW) = the frequency 3 dB below  $V_{ONL}$

$V_{CT}$  = Use  $V_{ISO}$  setup and test to all other switch analog input/outputs terminated with 50  $\Omega$

Figure 5. Off Channel Isolation/On Channel Loss (BW)/Crosstalk (On Channel to Off Channel)/V<sub>ONL</sub>

Figure 6. Charge Injection: (Q)

### **APPLICATIONS INFORMATION**

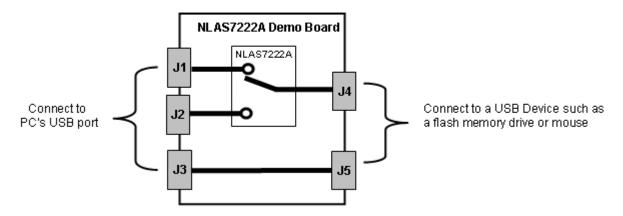

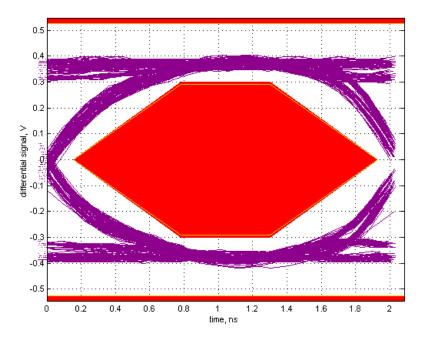

The low on resistance and capacitance of the NLAS7222A provides for a high bandwidth analog switch suitable for applications such as USB data switching. Results for the USB 2.0 signal quality tests will be shown in this section, along with a description of the evaluation test board. The data for the eye diagram signal quality and jitter tests verifies that the NLAS7222A can be used as a data switch in low, full and high speed USB 2.0 systems.

Figures 7, 8 and 9 provide a description of the test evaluation board. The USB tests were conducted per the procedures provided by the USB Implementers Forum

(www.usb.org), the industry group responsible for defining the USB certification requirements. The test patterns were generated by a PC and MATLAB software, and were inputted to the analog switch through USB connectors J1 (HSD1) or J2 (HSD2). A USB certified device was plugged into connector J4 to function as a data transceiver. The high speed and full speed tests used a flash memory device, while the low speed tests used a mouse. Test connectors J3 and J5 provide a direct connection of the USB device and were used to verify that the analog switch does not distort the data signals.

Figure 7. Schematic of the NLAS7222A USB Demo Board

Figure 8. Block Diagram of the NLAS7222A USB Demo Board

Figure 9. Photograph of the NLAS7222A USB Demo Board

# AND8267/D - NLAS7222A USB 2.0 Signal Quality Compliance Tests

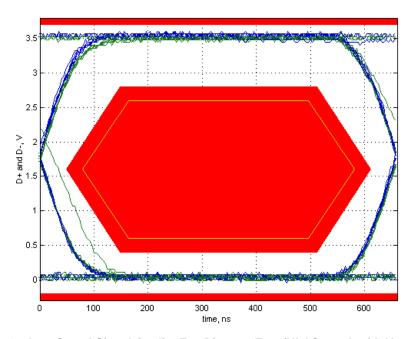

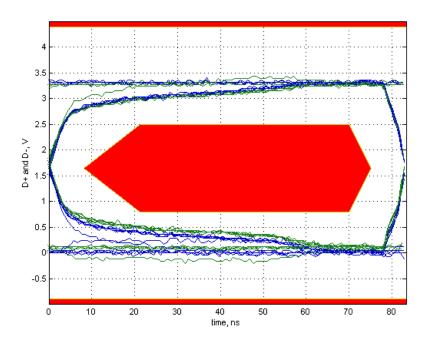

Figures 10, 11 and 12 show the test results for USB eye diagram tests. A summary of the USB tests is provided in Table 3. The NLAS7222A passes the low, full and high

speed signal quality, eye diagram and jitter tests. Application note AND8267/D provides a detailed description of the USB 2.0 test results.

Figure 10. Low Speed Signal Quality Eye Diagram Test (NLAS7222A with  $V_{CC} = 3.6 \text{ V}$ )

Figure 11. Full Speed Signal Quality Eye Diagram Test (NLAS7222A with  $V_{CC} = 3.6 \text{ V}$ )

Figure 12. High Speed Signal Quality Eye Diagram Test (NLAS7222A with  $V_{CC}$  = 3.0 V)

Table 3. Summary of the USB 2.0 Signal Quality Tests Results

| Compliance Test         | Low Speed                                  | Full Speed                                 | High Speed                                |

|-------------------------|--------------------------------------------|--------------------------------------------|-------------------------------------------|

| Signal Quality Test     | Pass                                       | Pass                                       | Pass                                      |

| Signal Eye Test         | Pass                                       | Pass                                       | Pass                                      |

| EOP Width               | 1.29 ms                                    | 166.86 ns                                  | 7.98 bits                                 |

| Measured Signal Rate    | 1.5140 MHz                                 | 12.0016 MHz                                | 480.0685 MHz                              |

| Crossover Voltage Range | 1.75 to 1.83 V,<br>mean crossover = 1.78 V | 1.70 to 1.73 V,<br>mean crossover = 1.71 V | N/A                                       |

| Connective Jitter Range | -2.2 to 2.2 ns,<br>RMS jitter = 1.3 ns     | -0.2 to 0.2 ns,<br>RMS jitter = 0.1 ns     | -79.4 to 77.4 ps,<br>RMS jitter = 35.0 ps |

| Paired JK Jitter Range  | -1.4 to 2.7 ns,<br>RMS jitter = 1.3 ns     | -0.1 to 0.1 ns,<br>RMS jitter = 0.1 ns     | -93.2 to 78.7 ps,<br>RMS jitter = 24.4 ps |

| Paired KJ Jitter Range  | -1.9 to 1.1 ns,<br>RMS jitter = 1.0 ns     | -0.2 to 0.1 ns,<br>RMS jitter = 0.1 ns     | -72.8 to 50.9 ps,<br>RMS jitter = 15.6 ps |

# **ORDERING INFORMATION**

|                     |                      | Device Nomenclature |                    |                       |                      |                    |

|---------------------|----------------------|---------------------|--------------------|-----------------------|----------------------|--------------------|

| Device Order Number | Circuit<br>Indicator | Technology          | Device<br>Function | Tape & Reel<br>Suffix | Package              | Shipping†          |

| NLAS7222AMTR2G      | NL                   | AS                  | 7222               | R2                    | WQFN-10<br>(Pb-Free) | 3000 / Tape & Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

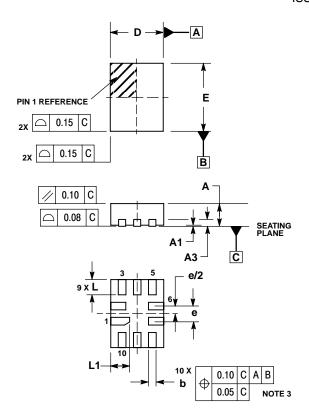

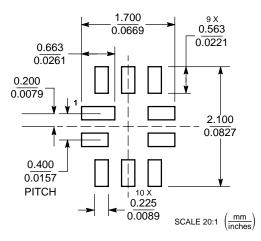

#### PACKAGE DIMENSIONS

### WQFN10, 1.4x1.8x0.4P CASE 488AQ-01 ISSUE B

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS

- DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL.

COPLANARITY APPLIES TO THE EXPOSED PAD

- AS WELL AS THE TERMINALS.

- EXPOSED PADS CONNECTED TO DIE FLAG. USED AS TEST CONTACTS.

|     | MILLIN   | IETERS |  |

|-----|----------|--------|--|

| DIM | MIN      | MAX    |  |

| Α   | 0.70     | 0.80   |  |

| A1  | 0.00     | 0.050  |  |

| A3  | 0.20 REF |        |  |

| b   | 0.15     | 0.25   |  |

| D   | 1.40     | BSC    |  |

| E   | 1.80     | BSC    |  |

| е   | 0.40     | BSC    |  |

| L   | 0.30     | 0.50   |  |

| L1  | 0.40     | 0.60   |  |

#### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 61312, Phoenix, Arizona 85082-1312 USA Phone: 480-829-7710 or 800-344-3860 Toll Free USA/Canada Fax: 480-829-7709 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

Japan: ON Semiconductor, Japan Customer Focus Center 2-9-1 Kamimeguro, Meguro-ku, Tokyo, Japan 153-0051 Phone: 81-3-5773-3850

ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative