# *OXCFU950* DATA SHEET

#### **FEATURES**

- USB/UART multi-function 16-bit PC Card device

- Host interface

- 16-bit PC Card (PCMCIA revision 8.0) compliant

- CompactFlash/CF+ (revision 3.0) compliant

- USB host controller

- Supports USB 2.0/1.1 full-speed compliant (12 Mbps) & low speed (1.5 Mbps) devices

- 8-Kbyte data buffer

- Integrated OHCI-like controller supported by Oxford Semiconductor drivers

- Supports control, bulk, interrupt & isochronous transfers

- Supports USB PORT\_OVER\_CURRENT & PORT\_POWER signals via MIO pins

- Integrated USB PHY transceivers

- Flexible OX16C95x-based UART

- Supports 450 up to 950 (fully programmable)

- Baud rates up to 12 Mbps

- 128-byte deep transmit/receive FIFO

- Software-compatible with standard 16C550

- Readable FIFO levels

- 9-bit data framing as well as 5,6,7 & 8

- Detection of bad data in the receiver FIFO

- Optional wakeup from low-power mode

- Automated in-band flow control using programmable Xon/Xoff characters

- Automated hardware flow control using CTS#/RTS# & DSR#/DTR#

- Integral support for 4-byte I/O access for enhanced host-side data throughput

- 8-Kbitx8 EEPROM for CIS & default configuration.

Programmable using Oxford Semiconductor utilities

- Power management for low-power operation

- USB suspend & resume

- UART sleep mode

- Single 12-MHz crystal oscillator for low power

- 4 multi-purpose I/O pins configurable as interrupts

- UART & MIO pins have variable I/O voltage levels from 1.8 V to 3.3 V nominal

- PC Card/CF+ I/Os are all 3.3 V with 5-V tolerance

- Single supply voltage range 2.85 V to 3.6 V

- Internal regulation for 1.8 V

- Supply current

- Less than 4 mA idle

- Less than 13 mA active

- Industrial temperature range –40°C to +85°C

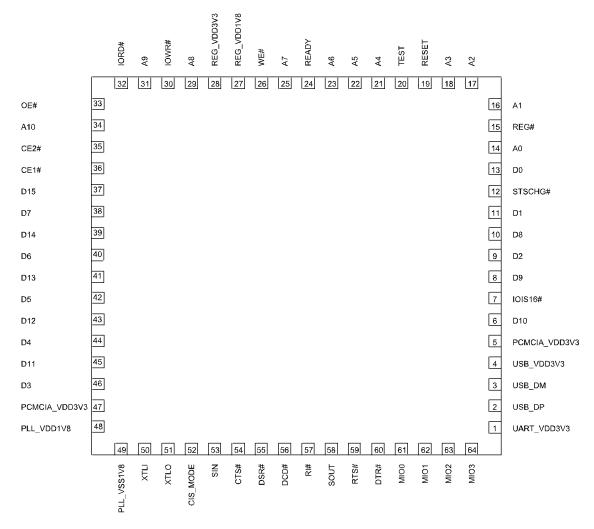

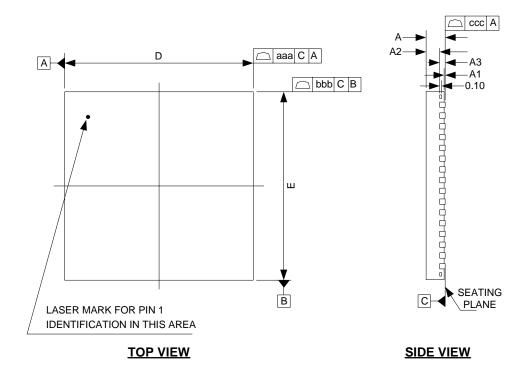

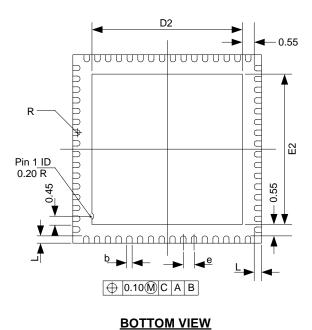

- 64-pin QFN (9 mm x 9 mm) package

## DESCRIPTION

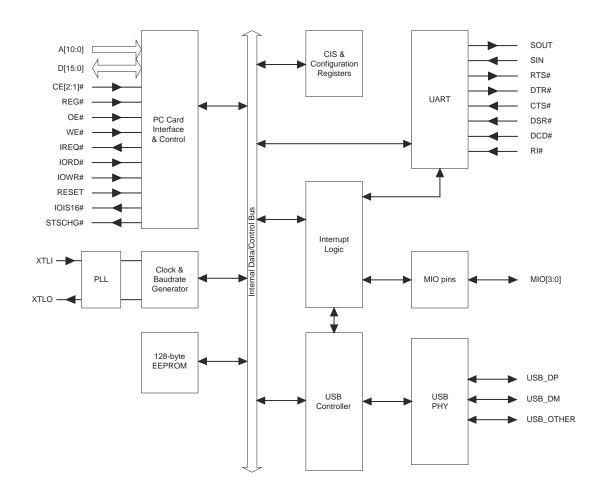

The OXCFU950 is a low-cost, synchronous 16-bit PC Card (PCMCIA) or CompactFlash/CF+ to UART and USB host controller. It combines the high performance of Oxford Semiconductor OX16C95x UART technology with USB host capabilities. The inclusion of both a UART and USB make the OXCFU950 ideal for wireless data cards.

The OXCFU950 integrates an OHCI-based USB host controller, which supports a single USB port via the integrated transceiver. An 8-Kbyte memory provides an efficient interface for buffer and control structures between the USB controller and the device driver.

The attribute memory, UART and USB registers can be programmed via the internal EEPROM during power up or hard/soft reset, allowing different card manufacturers to customize information contained in the attribute memory or UART/USB registers, for example PC Card ID value.

The 3.3-V technology has been specified to operate as low as 2.85 V to allow an in-line regulator to be used for mixed 3-V/5-V applications. CF/PC Card pins are 5-V tolerant and the variable I/O voltage to the UART/MIO pins eases the connection to application chipsets.

A number of power-down modes are included to minimize power consumption, including sleep modes for when a device function is not being used.

The OXCFU950 contains a single-channel ultra-high performance OX16C95x UART offering data rates up to 12 Mbps and 128-byte deep transmitter and receiver FIFOs. Deep FIFOs reduce CPU overhead and allow utilization of higher data rates.

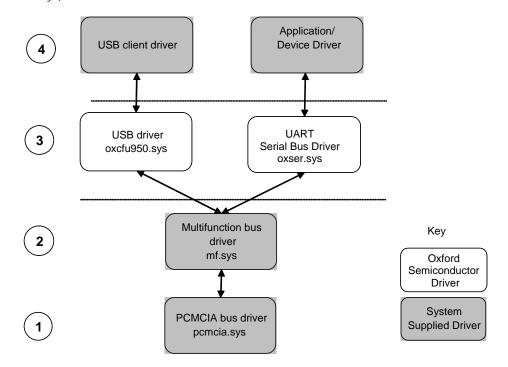

The OXCFU950 USB controller supports OHCI-compliant host stack software (available from Oxford Semiconductor).

The OXCFU950 UART is software-compatible with the widely-used industry-standard 16C550 type devices and compatibles, as well as other OX16C95x family devices.

The addition of software resets enable the device to recover from unforeseen error conditions, allowing drivers to restart gracefully.

The OXCFU950 includes four user I/O pins to enhance external device control. These I/O pins can also be configured as interrupt inputs.

For simplicity, the host interface is referred to as the CompactFlash interface throughout this specification. Unless otherwise stated, this should be taken to include PCMCIA 16-bit Card operation as well as CompactFlash/CF+.

# **CONTENTS**

| DESCRIPTION   CONTENTS   REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FE <i>F</i> | ATURES                                       | ······································ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------|----------------------------------------|

| REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DES         | SCRIPTION                                    |                                        |

| Table   Tabl | COI         | NTENTS                                       |                                        |

| 2 FUNCTIONAL OVERVIEW. 2.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RE۱         | VISION HISTORY                               | !                                      |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1           | BLOCK DIAGRAM                                | -                                      |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2           | FUNCTIONAL OVERVIEW                          |                                        |

| 2.3   COMMON MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |                                              |                                        |

| 10 SPACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.2         | ATTRIBUTE MEMORY                             |                                        |

| 2.5         USB HOST CONTROLLER           2.6         UART INTERFACE           2.7         EEPROM           2.8         SOFTWARE DRIVERS           3         PIN INFORMATION         1           4.1         POWER SUPPLY FILTERING         1           4.1.1         POWER SUPPLY FILTERING         1           4.1.2         INTERNAL VOLTAGE REGULATOR SUPPLY DE-COUPLING         1           4.2         OSCILLATOR SPECIFICATION         1           4.3         I/O PINS FOR EEPROM DIRECT ACCESS PROGRAMMING MODE         1           5         CONFIGURATION & OPERATION         1           5.1.1         NORMAL MODE         1           5.1.2         GENERIC MODE         1           6.1         10-BIT PC CARD & COMPACTFLASH/CF+ OPERATION         1           6.2         10-CARD & COMPACTFLASH/CF+ TARGET CONTROLLER         1           6.3         10-OACCESS WINDOWS         1           6.3.1 <td< td=""><td>2.3</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.3         |                                              |                                        |

| 2.6       UART INTERFACE         2.7       EEPROM         2.8       SOFTWARE DRIVERS         3       PIN INFORMATION       1         4       PIN DESCRIPTIONS       1         4.1       POWER SUPPLY FILTERING       1         4.1.1       PIL SUPPLY DE-COUPLING       1         4.1.2       INTERNAL VOLTAGE REGULATOR SUPPLY DE-COUPLING       1         4.2       OSCILATOR SPECIFICATION       1         4.3       I/O PINS FOR EEPROM DIRECT ACCESS PROGRAMMING MODE       1         5       CONFIGURATION & OPERATION       1         5.1       MODE SELECTION       1         5.1.1       NORMAL MODE       1         5.1.2       GENERIC MODE       1         5.1.1       NORMAL MODE       1         5.1.2       16-BIT PC CARD & COMPACTFLASH/CF+ OPERATION       1         6       PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER       1         6.1       OPERATION       1         6.2       OXCPUSS MINDOWS       1         6.3       I/O ACCESS WINDOWS       1         6.4       I/O SPACE REGISTER MAP       1         6.5       I/O SPACE REGISTER MAP       1         6.6.1       INTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                              |                                        |

| 2.7       EEPROM       SOFTWARE DRIVERS         3       PIN INFORMATION       1         4       PIN DESCRIPTIONS       1         4.1       POWER SUPPLY FILTERING       1         4.1.1       PLL SUPPLY DE-COUPLING       1         4.1.2       INTERNAL VOLTAGE REGULATOR SUPPLY DE-COUPLING       1         4.1.2       INTERNAL VOLTAGE REGULATOR SUPPLY DE-COUPLING       1         4.3       I/O PINS FOR EEPROM DIRECT ACCESS PROGRAMMING MODE       1         5.       CONFIGURATION & OPERATION       1         5.1       MODE SELECTION       1         5.1.1       NORMAL MODE       1         5.1.2       GENERIC MODE       1         5.2       16-BIT PC CARD & COMPACTFLASH/CF+ OPERATION       1         6       PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER       1         6.1       OPERATION       1         6.2       OXCFU950 MEMORY SPACE MAP       1         6.3       FUNCTION ACCESS       1         6.4       I/O SPACE REGISTER MAP       1         6.5       I/O SPACE REGISTER MAP       1         6.6       PC CARD/COMPACTFLASH INTERRUPT       2         6.6.1       INTERRUPT SOURCES       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                              |                                        |

| 2.8 SOFTWARE DRIVERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |                                              |                                        |

| 3 PIN INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |                                              |                                        |

| 4         PIN DESCRIPTIONS.         1           4.1         POWER SUPPLY FILTERING.         1           4.1.1         PLL SUPPLY DE-COUPLING.         1           4.1.2         INTERNAL VOLTAGE REGULATOR SUPPLY DE-COUPLING.         1           4.2         OSCILATOR SPECIFICATION.         1           4.3         I/O PINS FOR EEPROM DIRECT ACCESS PROGRAMMING MODE.         1           5.         CONFIGURATION & OPERATION.         1           5.1.1         NORMAL MODE.         1           5.1.2         GENERIC MODE.         1           5.2         16-BIT PC CARD & COMPACTFLASH/CF+ OPERATION.         1           6         PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER         1           6.1         OPERATION.         1           6.2         OXCFU950 MEMORY SPACE MAP.         1           6.3         FUNCTION ACCESS.         1           6.3.1         I/O ACCESS WINDOWS.         1           6.4         I/O SPACE REGISTER MAP.         1           6.5         I/O SPACE REGISTER MAP.         1           6.6.1         INTERRUPT GENERATION         2           6.6.2         INTERRUPT GENERATION         2           6.6.1         INTERRUPT S.         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                              |                                        |

| 4.1.1       POWER SUPPLY FILTERING.       1         4.1.1       PLL SUPPLY DE-COUPLING.       1         4.1.2       INTERNAL VOLTAGE REGULATOR SUPPLY DE-COUPLING.       1         4.2       OSCILLATOR SPECIFICATION.       1         4.3       I/O PINS FOR EEPROM DIRECT ACCESS PROGRAMMING MODE.       1         5       CONFIGURATION & OPERATION.       1         5.1.1       MODE SELECTION.       1         5.1.2       GENERIC MODE.       1         5.2       16-BIT PC CARD & COMPACTFLASH/CF+ OPERATION.       1         6       PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER.       1         6.1       OPERATION.       1         6.2       OXCFU950 MEMORY SPACE MAP.       1         6.3       FUNCTION ACCESS.       1         6.3.1       I/O ACCESS WINDOWS.       1         6.4       I/O SPACE REGISTER MAP.       1         6.5       I/O SPACE REGISTER MAP.       1         6.6.1       INTERRUPT SOURCES.       2         6.6.2       INTERRUPT SOURCES.       2         6.6.3       MIO INTERRUPTS.       2         6.6.4       UART INTERRUPTS.       2         6.6.5       USB INTERRUPTS.       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | J           |                                              |                                        |

| 4.1.1       PLL SUPPLY DE-COUPLING       1         4.1.2       INTERNAL VOLTAGE REGULATOR SUPPLY DE-COUPLING       1         4.2       OSCILLATOR SPECIFICATION       1         4.3       I/O PINS FOR EEPROM DIRECT ACCESS PROGRAMMING MODE       1         5.1       MODE SELECTION       1         5.1.1       NORMAL MODE       1         5.1.2       GENERIC MODE       1         5.1.2       GENERIC MODE       1         5.2       16-BIT PC CARD & COMPACTFLASH/CF+ OPERATION       1         6       PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER       1         6.1       OPERATION       1         6.2       OXCFU950 MEMORY SPACE MAP       1         6.3       FUNCTION ACCESS       1         6.3.1       I/O ACCESS WINDOWS       1         6.4       I/O SPACE REGISTER MAP       1         6.5       I/O SPACE REGISTER MAP       1         6.6       PC CARD/COMPACTFLASH INTERRUPT       2         6.6.1       INTERRUPT SOURCES       2         6.6.2       INTERRUPT SOURCES       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4           | PIN DESCRIPTIONS                             | 1                                      |

| 4.1.2       INTERNAL VOLTAGE REGULATOR SUPPLY DE-COUPLING       1         4.2       OSCILLATOR SPECIFICATION       1         4.3       I/O PINS FOR EEPROM DIRECT ACCESS PROGRAMMING MODE       1         5       CONFIGURATION & OPERATION       1         5.1       MODE SELECTION       1         5.1.1       NORMAL MODE       1         5.1.2       GENERIC MODE       1         5.1.2       16-BIT PC CARD & COMPACTFLASH/CF+ OPERATION       1         6       PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER       1         6.1       OPERATION       1         6.2       OXCFU950 MEMORY SPACE MAP       1         6.3       FUNCTION ACCESS       1         6.3.1       I/O ACCESS WINDOWS       1         6.4       I/O SPACE REGISTER MAP       1         6.5       I/O SPACE REGISTER MAP       1         6.6       PC CARD/COMPACTFLASH INTERRUPT       2         6.6.1       INTERRUPT GENERATION       2         6.6.2       INTERRUPT SOURCES       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6 <t< td=""><td>4.1</td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4.1         |                                              |                                        |

| 4.2       OSCILLATOR SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                                              |                                        |

| 4.3       I/O PINS FOR EEPROM DIRECT ACCESS PROGRAMMING MODE       1         5       CONFIGURATION & OPERATION       1         5.1       MODE SELECTION       1         5.1.1       NORMAL MODE       1         5.2       16-BIT PC CARD & COMPACTFLASH/CF+ OPERATION       1         6       PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER       1         6.1       OPERATION       1         6.2       OXCFU950 MEMORY SPACE MAP       1         6.3       FUNCTION ACCESS       1         6.3.1       I/O ACCESS WINDOWS       1         6.4       I/O SPACE REGISTER MAP       1         6.5       I/O SPACE REGISTERS       1         6.6       PC CARD/COMPACTFLASH INTERRUPT       2         6.6.1       INTERRUPT SOURCES       2         6.6.2       INTERRUPT SOURCES       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/USB TEST INTERRUPTS       2         6.6.7       CONFIGURATION & STATUS REGISTER —COR (OFFSET 0X00)       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X02)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                                              |                                        |

| 5         CONFIGURATION & OPERATION         1           5.1         MODE SELECTION         1           5.1.1         NORMAL MODE         1           5.1.2         GENERIC MODE         1           5.2         16-BIT PC CARD & COMPACTFLASH/CF+ OPERATION         1           6         PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER         1           6.1         OPERATION         1           6.2         OXCFU950 MEMORY SPACE MAP         1           6.3         FUNCTION ACCESS         1           6.3.1         I/O ACCESS WINDOWS         1           6.4         I/O SPACE REGISTER MAP         1           6.5         I/O SPACE REGISTERS         1           6.6         PC CARD/COMPACTFLASH INTERRUPT         2           6.6.1         INTERRUPT GENERATION         2           6.6.2         INTERRUPT SOURCES         2           6.6.3         MIO INTERRUPTS         2           6.6.4         UART INTERRUPTS         2           6.6.5         USB INTERRUPTS         2           6.6.6         UART/USB TEST INTERRUPTS         2           6.6.7         CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE         2           6.7.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | USCILLATOR SPECIFICATION                     | 14                                     |

| 5.1       MODE SELECTION       1         5.1.1       NORMAL MODE       1         5.2       GENERIC MODE       1         5.2       16-BIT PC CARD & COMPACTFLASH/CF+ OPERATION       1         6       PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER       1         6.1       OPERATION       1         6.2       OXCFU950 MEMORY SPACE MAP       1         6.3       FUNCTION ACCESS       1         6.3.1       I/O ACCESS WINDOWS       1         6.4       I/O SPACE REGISTER MAP       1         6.5       I/O SPACE REGISTER MAP       1         6.6.1       INTERRUPT GENERATION       2         6.6.2       INTERRUPT GURCES       1         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/USB TEST INTERRUPTS       2         6.6.7       PC CARD/COMPACTFLASH FUNCTION CONFIGURATION REGISTERS       2         6.7.1       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X02)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.3         |                                              |                                        |

| 5.1.1       NORMAL MODE       1         5.1.2       GENERIC MODE       1         5.2       16-BIT PC CARD & COMPACTFLASH/CF+ OPERATION       1         6       PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER       1         6.1       OPERATION       1         6.2       OXCFU950 MEMORY SPACE MAP       1         6.3       FUNCTION ACCESS       1         6.3.1       I/O ACCESS WINDOWS       1         6.4       I/O SPACE REGISTER MAP       1         6.5       I/O SPACE REGISTERS       1         6.6       PC CARD/COMPACTFLASH INTERRUPT       2         6.6.1       INTERRUPT GENERATION       2         6.6.2       INTERRUPT GENERATION       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/USB TEST INTERRUPTS       2         6.6.7       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION STATUS REGISTER—CSR (OFFSET 0X02)       2         6.7.3       PIN REPLACEMENT REGISTER—PRR (OFFSET 0X04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                                              |                                        |

| 5.1.2       GENERIC MODE       1         5.2       16-BIT PC CARD & COMPACTFLASH/CF+ OPERATION       1         6       PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER       1         6.1       OPERATION       1         6.2       OXCFU950 MEMORY SPACE MAP       1         6.3       FUNCTION ACCESS       1         6.3.1       I/O ACCESS WINDOWS       1         6.4       I/O SPACE REGISTER MAP       1         6.5       I/O SPACE REGISTERS       1         6.6       PC CARD/COMPACTFLASH INTERRUPT       2         6.6.1       INTERRUPT GENERATION       2         6.6.2       INTERRUPT SOURCES       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/IUSB TEST INTERRUPTS       2         6.6.7       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION STATUS REGISTER—CSR (OFFSET 0X02)       2         6.7.3       PIN REPLACEMENT REGISTER—PRR (OFFSET 0X04)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                                              |                                        |

| 5.2       16-BIT PC CARD & COMPACTFLASH/CF+ OPERATION       1         6       PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER       1         6.1       OPERATION       1         6.2       OXCFU950 MEMORY SPACE MAP       1         6.3       FUNCTION ACCESS       1         6.3.1       I/O ACCESS WINDOWS       1         6.4       I/O SPACE REGISTER MAP       1         6.5       I/O SPACE REGISTERS       1         6.6       PC CARD/COMPACTFLASH INTERRUPT       2         6.6.1       INTERRUPT GENERATION       2         6.6.2       INTERRUPT SOURCES       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/USB TEST INTERRUPTS       2         6.6.7       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7       PC CARD/COMPACTFLASH FUNCTION CONFIGURATION REGISTERS       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION STATUS REGISTER—PRR (OFFSET 0X04)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |                                              |                                        |

| 6         PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER         1           6.1         OPERATION         1           6.2         OXCFU950 MEMORY SPACE MAP         1           6.3         FUNCTION ACCESS         1           6.3.1         I/O ACCESS WINDOWS         1           6.4         I/O SPACE REGISTER MAP         1           6.5         I/O SPACE REGISTERS         1           6.6         PC CARD/COMPACTFLASH INTERRUPT         2           6.6.1         INTERRUPT GENERATION         2           6.6.2         INTERRUPT SOURCES         2           6.6.3         MIO INTERRUPTS         2           6.6.4         UART INTERRUPTS         2           6.6.5         USB INTERRUPTS         2           6.6.6         UART/USB TEST INTERRUPTS         2           6.6.7         CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE         2           6.7         PC CARD/COMPACTFLASH FUNCTION CONFIGURATION REGISTERS         2           6.7.1         CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)         2           6.7.2         CONFIGURATION STATUS REGISTER—COR (OFFSET 0X02)         2           6.7.3         PIN REPLACEMENT REGISTER—PRR (OFFSET 0X04)         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                                              |                                        |

| 6.1       OPERATION       1         6.2       OXCFU950 MEMORY SPACE MAP       1         6.3       FUNCTION ACCESS       1         6.3.1       I/O ACCESS WINDOWS       1         6.4       I/O SPACE REGISTER MAP       1         6.5       I/O SPACE REGISTERS       1         6.6       PC CARD/COMPACTFLASH INTERRUPT       2         6.6.1       INTERRUPT GENERATION       2         6.6.2       INTERRUPT SOURCES       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/USB TEST INTERRUPTS       2         6.6.7       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7       PC CARD/COMPACTFLASH FUNCTION CONFIGURATION REGISTERS       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION STATUS REGISTER—CSR (OFFSET 0X02)       2         6.7.3       PIN REPLACEMENT REGISTER—PRR (OFFSET 0X04)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.2         |                                              |                                        |

| 6.2       OXCFU950 MEMORY SPACE MAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6           | PC CARD & COMPACTFLASH/CF+ TARGET CONTROLLER | 10                                     |

| 6.3       FUNCTION ACCESS       1         6.3.1       I/O ACCESS WINDOWS       1         6.4       I/O SPACE REGISTER MAP       1         6.5       I/O SPACE REGISTERS       1         6.6       PC CARD/COMPACTFLASH INTERRUPT       2         6.6.1       INTERRUPT GENERATION       2         6.6.2       INTERRUPT SOURCES       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/USB TEST INTERRUPTS       2         6.6.7       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7       PC CARD/COMPACTFLASH FUNCTION CONFIGURATION REGISTERS       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION STATUS REGISTER—CSR (OFFSET 0X02)       2         6.7.3       PIN REPLACEMENT REGISTER—PRR (OFFSET 0X04)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6.1         |                                              |                                        |

| 6.3.1       I/O ACCESS WINDOWS.       1         6.4       I/O SPACE REGISTER MAP.       1         6.5       I/O SPACE REGISTERS.       1         6.6       PC CARD/COMPACTFLASH INTERRUPT.       2         6.6.1       INTERRUPT GENERATION.       2         6.6.2       INTERRUPT SOURCES.       2         6.6.3       MIO INTERRUPTS.       2         6.6.4       UART INTERRUPTS.       2         6.6.5       USB INTERRUPTS.       2         6.6.6       UART/USB TEST INTERRUPTS.       2         6.6.7       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7       PC CARD/COMPACTFLASH FUNCTION CONFIGURATION REGISTERS.       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION STATUS REGISTER—CSR (OFFSET 0X02)       2         6.7.3       PIN REPLACEMENT REGISTER—PRR (OFFSET 0X04)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |                                              |                                        |

| 6.4       I/O SPACE REGISTER MAP       1         6.5       I/O SPACE REGISTERS       1         6.6       PC CARD/COMPACTFLASH INTERRUPT       2         6.6.1       INTERRUPT GENERATION       2         6.6.2       INTERRUPT SOURCES       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/USB TEST INTERRUPTS       2         6.6.7       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7       PC CARD/COMPACTFLASH FUNCTION CONFIGURATION REGISTERS       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION STATUS REGISTER—CSR (OFFSET 0X02)       2         6.7.3       PIN REPLACEMENT REGISTER—PRR (OFFSET 0X04)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |                                              |                                        |

| 6.5       I/O SPACE REGISTERS       1         6.6       PC CARD/COMPACTFLASH INTERRUPT       2         6.6.1       INTERRUPT GENERATION       2         6.6.2       INTERRUPT SOURCES       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/USB TEST INTERRUPTS       2         6.6.7       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7       PC CARD/COMPACTFLASH FUNCTION CONFIGURATION REGISTERS       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION STATUS REGISTER—CSR (OFFSET 0X02)       2         6.7.3       PIN REPLACEMENT REGISTER—PRR (OFFSET 0X04)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                                              |                                        |

| 6.6       PC CARD/COMPACTFLASH INTERRUPT       2         6.6.1       INTERRUPT GENERATION       2         6.6.2       INTERRUPT SOURCES       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/USB TEST INTERRUPTS       2         6.6.7       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7       PC CARD/COMPACTFLASH FUNCTION CONFIGURATION REGISTERS       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION STATUS REGISTER—CSR (OFFSET 0X02)       2         6.7.3       PIN REPLACEMENT REGISTER—PRR (OFFSET 0X04)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                                              |                                        |

| 6.6.1       INTERRUPT GENERATION       2         6.6.2       INTERRUPT SOURCES       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/USB TEST INTERRUPTS       2         6.6.7       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7       PC CARD/COMPACTFLASH FUNCTION CONFIGURATION REGISTERS       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION STATUS REGISTER—CSR (OFFSET 0X02)       2         6.7.3       PIN REPLACEMENT REGISTER—PRR (OFFSET 0X04)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |                                              |                                        |

| 6.6.2       INTERRUPT SOURCES       2         6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/USB TEST INTERRUPTS       2         6.6.7       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7       PC CARD/COMPACTFLASH FUNCTION CONFIGURATION REGISTERS       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION STATUS REGISTER—CSR (OFFSET 0X02)       2         6.7.3       PIN REPLACEMENT REGISTER—PRR (OFFSET 0X04)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                                              |                                        |

| 6.6.3       MIO INTERRUPTS       2         6.6.4       UART INTERRUPTS       2         6.6.5       USB INTERRUPTS       2         6.6.6       UART/USB TEST INTERRUPTS       2         6.6.7       CONFIGURATION & STATUS REGISTER INTERRUPT REQUEST/ACKNOWLEDGE       2         6.7       PC CARD/COMPACTFLASH FUNCTION CONFIGURATION REGISTERS       2         6.7.1       CONFIGURATION OPTIONS REGISTER—COR (OFFSET 0X00)       2         6.7.2       CONFIGURATION STATUS REGISTER—CSR (OFFSET 0X02)       2         6.7.3       PIN REPLACEMENT REGISTER—PRR (OFFSET 0X04)       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |                                              |                                        |