## ELECTRICAL SPECIFICATIONS:

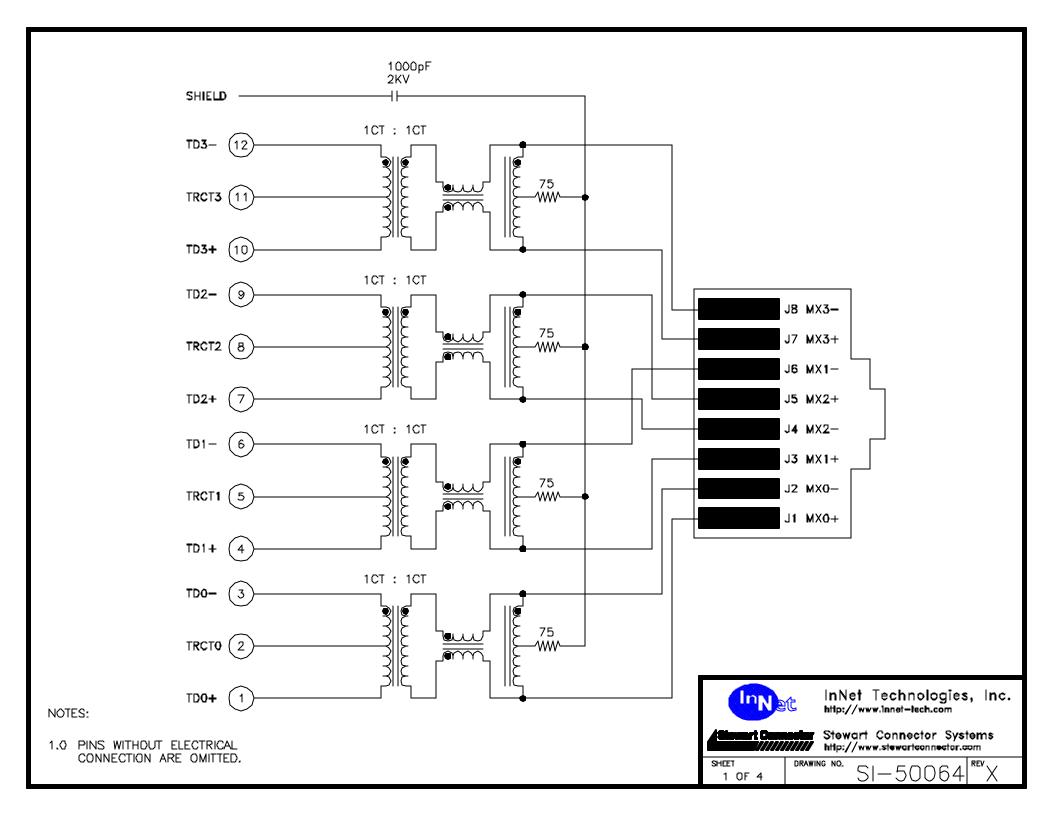

1.0 TURNS RATIO: ((TD-) - (TD+)). ((MX-) - (MX+)) : 1CT : 1CT ±3%

2.0 INDUCTANCE: ((TD-) - (TD+)) : 350 uH MIN. @ 0.01V, 100KHz, 8 mA DC BIAS

3.0 LEAKAGE INDUCTANCE: ((TD-) - (TD+)) (WITH (MX-) AND (MX+) SHORT) : 0.3uH MAX, @ 1MHz

4.0 INTERWINDING CAPACITANCE: ((TD-) - (TD+)) TO ((MX-) - (MX+)) : 70pf MAX @ 1MHz

5.0 DC RESISTANCE: ((MX-) - (MX+)) : 1.2 ohms Max.

6.0 RETURN LOSS: 1MHz TO 30MHz : -18dB MIN.

30MHz TO 80MHz :  $-12+20 LOG \left(\frac{F}{80MHz}\right)$

7.0 DIELECTRIC WITHSTAND: ((TD+) - (TD-)) TO ((MX-) - (MX+)) : 1500 VAC

8.0 INSERTION LOSS: RS=RL=100 ohms 100KHz TO 100MHz : -1.1 dB MAX

9.0 RISE TIME: RS=100 OHMS AND RL = 100 OHMS

OUTPUT VOLTAGE = 1 V peak : 3.0 nS MAX

PULSE WIDTH= 112nS : 3.0 nS MAX

10 0 CROSS TALK: 1-100 MHz : -33 dB MIN

11 0 COMMON TO COMMON MODE ATTENUATION: 1MHz TO 100MHz : -35dB TYP

SHEET DRAWING NO. 2 OF 4

SI-50064

## \*,430 [10,92] -.100 [2,54] (2) ,100 [2.54] (2) ø.040 [1.02] (4)-:050 [1.27] TYP -,100 [2,54] .185 [4.70] ø.035 [0.89] (12) [19.05] ø 062 [157] (2) 1.200 [30.48] MAX. .120 [3.05]φ.126 [3.20] .123 [3.12] .225 [5.72] **→** \*.450 [11.43] <del>→</del> -\*.610 [15 **4**9]-P.C.B. RECOMMENDED HOLE LAYOUT SEEN FROM COMPONENT SIDE TOLERANCE ±.003 [0.08] UNLESS OTHERWISE SPECIFIED

## NOTES:

- TOLERANCES COMPLY WITH F.C.C. DIMENSION REQUIREMENTS

- DIMENSIONS SHOWN WITH \*\*" TO BE CENTRAL ABOUT CENTER LINE

- DIMENSIONS SHOWN ARE SUBJECT TO CHANGE WITHOUT NOTICE.

- PIN NOT ELECTRICALLY CONNECTED MAYBE OMITTED.

SEE ELECTRICAL DRAWING FOR OMITTED PINS.

- 50 MICRO-INCH SELECTIVE GOLD PLATING

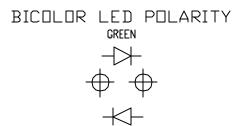

## LED COLOR COMBINATIONS:

- YELLOW, RED & GREEN

- AVAILABLE IN ANY COMBINATION

| STANDARD LED | WAVELENGTH | * Forward V (MAX) | (TYP) |

|--------------|------------|-------------------|-------|

| YELLOW       | 590 nm     | 2.5 V             | 2.1 V |

| GREEN        | 565 nm     | 2.5 V             | 2.2 V |

\* WITH A FORWARD CURRENT OF 20 mA

YELLOW

InNet Technologies, Inc. http://www.innet-tech.com

Stewart Connector Systems http://www.stewartconnector.com

SHEET 3 OF 4 DRAWING NO. SI-50064

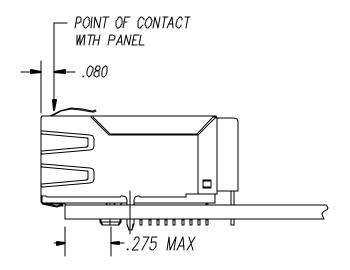

.125 [3.18]±.010 [0.25]

-- .040±.005 [1.02±0.127]

SPD10323-02

GRN

COUNTRY OF ORIGIN

PART NUMBER Date Code

INET/SCS

──\*.635 [16.13] MAX ──

\*.70B [17.98]-REF.

GRN/YEL

550 [13.97] MAX

.616 [15.65] REF.

.014 [0.36] REF.

.0B3 [2.12] — HIGHEST POINT OF BEAM REF.

- .422±.005 <del>-</del> [10.72±0.127]

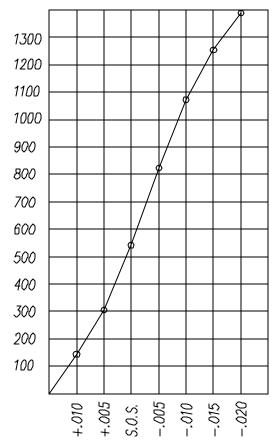

PANEL GROUNDING BEAM DEFLECTION S.O.S. = SUGGESTED OPENING SIZE

SUGGESTED PANEL OPENING

CT720034X1/24-001302

THE SUGGESTED PANEL OPENING IS INTENDED TO GIVE THE USER THE ABILITY TO HAVE REASONABLE JACK / PANEL CLEARANCES YET MAINTAIN RELIABLE GROUNDING CAPABILITY. THESE VARIABLES CAN BE ADJUSTED IN EITHER DIRECTION BUT MAY CARRY SOME CONSEQUENCES IN THE FORM OF LOWER MATING FORCES OR TIGHTER ASSEMBLY TOLERANCES. FORCE VALUES ON THE GRAPH ARE GENERAL AVERAGES TAKEN AT THE POINT OF CONTACT SHOWN ABOVE. THE SUGGESTED PANEL OPENING INCLUDES APPROXIMATELY .020 CLEARANCE ON THE SIDES AND TOP AND .013 ON THE BOTTOM, AT PANEL OPENING.