# 1:6 PCI Clock Generator/Fanout Buffer

## **MPC905**

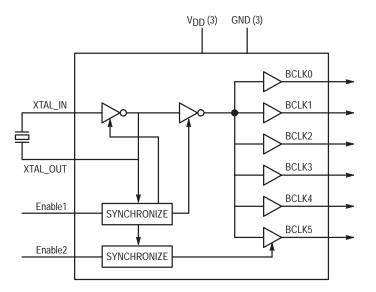

The MPC905 is a six output clock generation device targeted to provide the clocks required in a 3.3V or 5.0V PCI environment. The device operates from a 3.3V supply and can interface to either a TTL input or an external crystal. The inputs to the device can be driven with 5.0V when the V $_{\rm CC}$  is at 3.3V. The outputs of the MPC905 meet all of the specifications of the PCI standard.

- Six Low Skew Outputs

- · Synchronous Output Enables for Power Management

- Low Voltage Operation

- XTAL Oscillator Interface

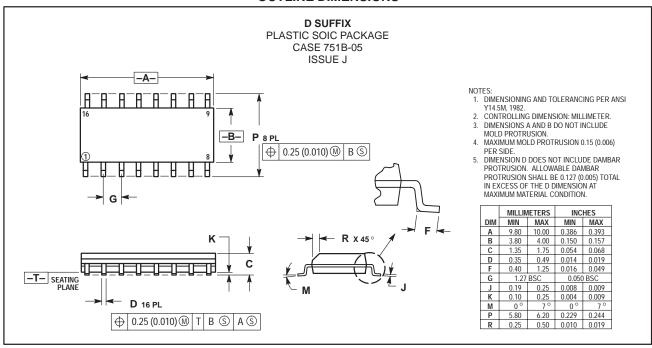

- 16-Lead SOIC Package

- 5.0V Tolerant Enable Inputs

The MPC905 device is targeted for PCI bus or processor bus environments with up to 12 clock loads. Each of the six outputs on the MPC905 can drive two series terminated  $50\Omega$  transmission lines. This capability effectively makes the MPC905 a 1:12 fanout buffer.

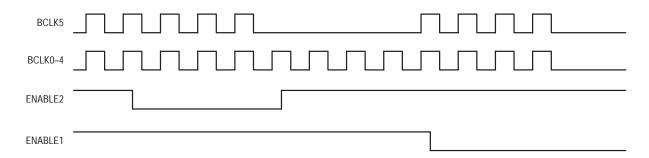

The MPC905 offers two synchronous enable inputs to allow users flexibility in developing power management features for their designs. Both enable signals are active HIGH inputs. A logic '0' on the Enable1 will pull outputs 0 to 4 into the logic '0' state. A logic '1' on the Enable1 input will result in outputs 0 to 4 to be toggling. A logic '0' on Enable2 will cause output BLK5 to a logic '0' state, whereas a logic '1' on Enable2 will cause output BLK5 to toggle. The oscillator remains on.

1:6 PCI CLOCK GENERATOR/ FANOUT BUFFER

The Enable2 input can be used to disable any high power device for system power savings during periods of inactivity. Both enable inputs are synchronized internal to the chip so that the output disabling will happen only when the outputs are already LOW. This feature guarantees no runt pulses will be generated during enabling and disabling.

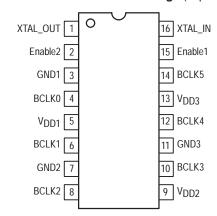

Pinout: 16-Lead Plastic Package (Top View)

#### **PIN CONFIGURATIONS**

| Pin               | I/O    | Туре   | Function                     |

|-------------------|--------|--------|------------------------------|

| XTAL_IN, XTAL_OUT | Input  | Analog | Crystal Oscillator Terminals |

| Enable1, Enable2  | Input  | LVCMOS | Output Enable                |

| BCLK0 - BCLK5     | Output | LVCMOS | Clock Outputs                |

| V <sub>DD</sub>   |        | Supply | Positive Power Supply        |

| GND               |        | Supply | Negative Power Supply        |

#### **FUNCTION TABLE**

| ENABLE1 | ENABLE2 | Outputs 0 to 4 | Output 5 | OSC (On/Off) |

|---------|---------|----------------|----------|--------------|

| 0       | 0       | Low            | Low      | ON           |

| 0       | 1       | Low            | Toggling | ON           |

| 1       | 0       | Toggling       | Low      | ON           |

| 1       | 1       | Toggling       | Toggling | ON           |

#### **ABSOLUTE MAXIMUM RATINGS\***

| Symbol             | Parameter                            | Min  | Max                   | Unit |

|--------------------|--------------------------------------|------|-----------------------|------|

| V <sub>DD</sub>    | Supply Voltage                       | -0.5 | 4.6                   | V    |

| V <sub>IN</sub>    | Input Voltage                        | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| T <sub>oper</sub>  | Operating Temperature Range          | 0    | +70                   | °C   |

| T <sub>stg</sub>   | Storage Temperature Range            | -65  | +150                  | °C   |

| T <sub>sol</sub>   | Soldering Temperature Range (10 Sec) |      | +260                  | °C   |

| Тј                 | Junction Temperature Range           |      | +125                  | °C   |

| ESD                | Static Discharge Voltage             | 1500 |                       | V    |

| I <sub>Latch</sub> | Latch Up Current                     | 50   |                       | mA   |

<sup>\*</sup> Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

#### RECOMMENDED OPERATING CONDITIONS

| Symbol | Parameter                                                                   | Min                              | Max                              | Unit       |

|--------|-----------------------------------------------------------------------------|----------------------------------|----------------------------------|------------|

| TA     | Ambient Temperature Range                                                   | 0                                | 70                               | °C         |

| Vcc    | Positive Supply Voltage (Functional Range)                                  | 3.0                              | 3.6                              | V          |

| tDCin  | T <sub>high</sub> (at XTAL_IN Input)<br>T <sub>low</sub> (at XTAL_IN Input) | 0.44T <b>1</b><br>0.44T <b>1</b> | 0.56T <b>1</b><br>0.56T <b>1</b> | T = Period |

<sup>1.</sup> When using External Source for reference, requirement to meet PCI clock duty cycle requirement on the output.

## DC CHARACTERISTICS ( $T_A = 0-70$ °C; $V_{DD} = 3.3V \pm 0.3V$ )

| Symbol          | Characteristic                      | Min | Тур            | Max          | Unit           | Condition                           |

|-----------------|-------------------------------------|-----|----------------|--------------|----------------|-------------------------------------|

| VIH             | High Level Input Voltage            | 2.0 |                | 5.5 <b>2</b> | V              |                                     |

| V <sub>IL</sub> | Low Level Input Voltage             |     |                | 0.8          | V              |                                     |

| VOH             | High Level Output Voltage           | 2.4 |                |              | V              | $I_{OH} = -36 \text{mA}^{1}$        |

| V <sub>OL</sub> | Low Level Output Voltage            |     |                | 0.4          | V              | I <sub>OL</sub> = 36mA <sup>1</sup> |

| liH             | Input High Current                  |     |                | 2.5 <b>2</b> | μΑ             |                                     |

| I <sub>IL</sub> | Input Low Current                   |     |                | 2.5          | μΑ             |                                     |

| Icc             | Power Supply Current DC 33MHz 66MHz | :   | 20<br>37<br>78 | 45<br>95     | μΑ<br>mA<br>mA |                                     |

| C <sub>IN</sub> | Input Capacitance XTAL_IN Others    |     |                | 9.0<br>4.5   | pF             |                                     |

<sup>1.</sup> The MPC905 can drive  $50\Omega$  transmission lines on the incident edge. Each output drives one  $50\Omega$  parallel terminated transmission line to  $V_{TT} = V_{CC}/2$ . Alternately, the device drives up to two  $50\Omega$  series terminated transmission lines per output.

<sup>2.</sup> XTAL\_IN input will sink up to 10mA when driven to 5.5V. There are no reliability concerns associated with the condition. Note that the Enable1 input must be a logic HIGH. Do not take the Enable1 input to a logic LOW with >VCC volts on the XTAL\_IN input.

## AC CHARACTERISTICS ( $T_A = 0-70$ °C; $V_{DD} = 3.3V \pm 0.3V$ )

| Symbol                          | Characteristic                                                                       | Min                              | Тур | Max                                                                  | Unit         | Condition                               |

|---------------------------------|--------------------------------------------------------------------------------------|----------------------------------|-----|----------------------------------------------------------------------|--------------|-----------------------------------------|

| F <sub>max</sub>                | Maximum Operating Using External Crystr<br>Frequency Using External Clock Source     |                                  |     | 50<br>100                                                            | MHz          |                                         |

| t <sub>pw</sub>                 | Output Pulse Width HIGH (Above 2.0\ LOW (Below 0.8\ HIGH (Above 2.0\ LOW (Below 0.8\ | 0.40T <b>1</b><br>0.45T <b>2</b> |     | 0.60T <b>1</b><br>0.60T <b>1</b><br>0.55T <b>2</b><br>0.55T <b>2</b> |              | T = Periods                             |

| t <sub>per</sub>                | Output Period                                                                        | T – 400ps                        |     |                                                                      |              | T = Desired Period                      |

| tos                             | Output-to-Output Skew Rising Edge Falling Edge                                       |                                  |     | 400<br>500                                                           | ps           |                                         |

| t <sub>r</sub> , t <sub>f</sub> | Rise/Fall Times (Slew Rate)                                                          | 1                                |     | 4                                                                    | V/ns         | Series Terminated<br>Transmission Lines |

| <sup>t</sup> EN                 | Enable Time Enable Enable                                                            | 1                                |     | 5<br>4                                                               | ms<br>Cycles |                                         |

| <sup>t</sup> DIS                | Disable Time Enable Enable                                                           | 1                                |     | 4<br>4                                                               | Cycles       |                                         |

| A <sub>osc</sub>                | XTAL_IN to XTAL_OUT Oscillator Gain                                                  | 6                                |     |                                                                      | db           |                                         |

| Phase                           | Loop Phase Shift Modulo 360° +                                                       | 30                               |     |                                                                      | Degrees      |                                         |

- 1. Assuming input duty cycle specs from Recommended Operationg Conditions table are met.

- 2. Assuming external crystal or 50% duty cycle external reference is used.

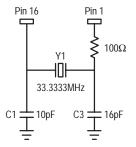

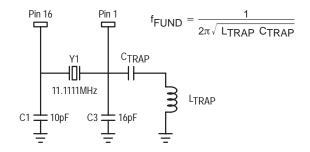

Figure 1. Crystal Oscillator Interface (Fundamental)

Figure 2. Crystal Oscillator Interface (3rd Overtone)

**Table 1. Crystal Specifications**

| Parameter                          | Value                   |

|------------------------------------|-------------------------|

| Crystal Cut                        | Fundamental AT Cut      |

| Resonance                          | Parallel Resonance*     |

| Frequency Tolerance                | ±75ppm at 25°C          |

| Frequency/Temperature Stability    | ±150pm 0 to 70°C        |

| Operating Range                    | 0 to 70°C               |

| Shunt Capacitance                  | 5–7pF                   |

| Equivalent Series Resistance (ESR) | 50 to 80Ω               |

| Correlation Drive Level            | 100μW                   |

| Aging                              | 5ppm/Yr (First 3 Years) |

Figure 3. Enable Timing Diagram

#### APPLICATIONS INFORMATION

#### **Driving Transmission Lines**

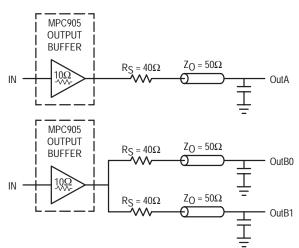

The MPC905 clock driver was designed to drive high speed signals in a terminated transmission line environment. To provide the optimum flexibility to the user the output drivers were designed to exhibit the lowest impedance possible. With an output impedance of approximately  $10\Omega$  the drivers can drive either parallel or series terminated transmission lines. For more information on transmission lines the reader is referred to application note AN1091 in the Timing Solutions data book (DL207/D).

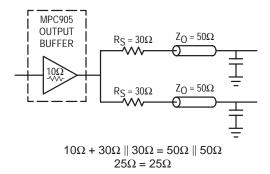

In most high performance clock networks point–to–point distribution of signals is the method of choice. In a point–to–point scheme either series terminated or parallel terminated transmission lines can be used. The parallel technique terminates the signal at the end of the line with a  $50\Omega$  resistance to VCC/2. This technique draws a fairly high level of DC current and thus only a single terminated line can be driven by each output of the MPC905 clock driver. For the series terminated case however there is no DC current draw, thus the outputs can drive multiple series terminated lines. Figure 4 illustrates an output driving a single series terminated line vs two series terminated lines in parallel. When taken to its extreme the fanout of the MPC905 clock driver is effectively doubled due to its capability to drive multiple lines.

Figure 4. Single versus Dual Transmission Lines

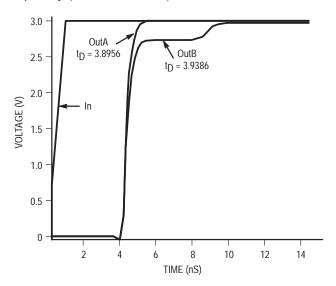

The waveform plots of Figure 5 show the simulation results of an output driving a single line vs two lines. In both cases the drive capability of the MPC905 output buffers is more than sufficient to drive  $50\Omega$  transmission lines on the incident edge. Note from the delay measurements in the simulations a delta of only 43ps exists between the two differently loaded outputs. The output waveform in Figure 5

shows a step in the waveform, this step is caused by the impedance mismatch seen looking into the driver. The parallel combination of the  $40\Omega$  series resistor plus the output impedance does not match the parallel combination of the line impedances. The voltage wave launched down the two lines will equal:

$$VL = VS (Zo / Rs + Ro + Zo) = 3.0 (25/55) = 1.36V$$

At the load end the voltage will double, due to the near unity reflection coefficient, to 2.73V. It will then increment towards the quiescent 3.0V in steps separated by one round trip delay (in this case 4.0ns).

Figure 5. Single versus Dual Waveforms

Since this step is well above the threshold region it will not cause any false clock triggering, however designers may be uncomfortable with unwanted reflections on the line. To better match the impedances when driving multiple lines the situation in Figure 6 should be used. In this case the series terminating resistors are reduced such that when the parallel combination is added to the output buffer impedance the line impedance is perfectly matched.

Figure 6. Optimized Dual Line Termination

#### **OUTLINE DIMENSIONS**

## Innovate with IDT and accelerate your future networks. Contact:

## www.IDT.com

## For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

## **For Tech Support**

netcom@idt.com 480-763-2056

## **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

## Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### **Europe**

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339