# Data Capture and Interface Board for a PC

#### Features

- Versatile measurement tool used for the evaluation of Crystal<sup>®</sup> analog to digital converters.

- Updatable via on-board RAM-based DSP and Altera programmable logic device

- Easy interface to a PC compatible computer.

- LabWindows<sup>®</sup> based evaluation software for data analysis.

- Includes time domain, FFT, noise distribution histogram, and DNL analysis options.

- Can be used to evaluate the ADC in your equipment.

- Interfaces to an ADC evaluation board via 10pin serial ribbon cable or S/PDIF Link.

- Enhanced Replacement for the CDBCAPTURE and the CDBCAPTAUDIO

### **General Description**

The CDBCapture+ interface board is a development tool that interfaces a Crystal<sup>®</sup> analog to digital converter to a PC-compatible computer. Digital data is collected in a high speed digital SRAM, then transferred to the PC over a serial COM port. Evaluation software is included to analyze the data and demonstrate the analog to digital converter's performance.

The CDBCapture+ interface board is designed to be easily interfaced to Crystal evaluation boards. Application software is loaded via the PC's serial COM port. The software adjusts the CDBCapture+ interface board for the appropriate signal timing and polarity, coding format and number of bits, thus allowing the same hardware to be used with a variety of Crystal ADCs.

Evaluation software is included with the CDBCapture+ interface board. The software was developed with Lab-Windows<sup>®</sup>, a software development system for instrument control, data acquisition, and analysis applications. The evaluation software permits time domain, frequency domain, histogram, and DNL analysis.

ORDERING INFORMATION CDBCapture+

Preliminary Product Information

This document contains information for a new product. Cirrus Logic reserves the right to modify this product without notice.

Cirrus Logic, Inc. Crystal Semiconductor Products Division P.O. Box 17847, Austin, Texas 78760 (512) 445 7222 FAX: (512) 445 7581 http://www.crystal.com

Copyright © Cirrus Logic, Inc. 1998 (All Rights Reserved)

NOV '98 DS327F1

#### **OVERVIEW**

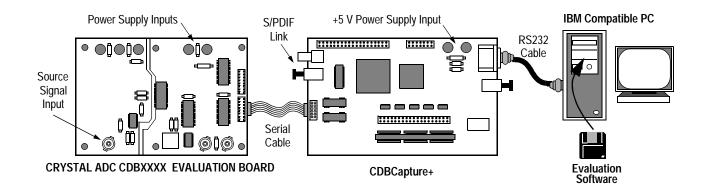

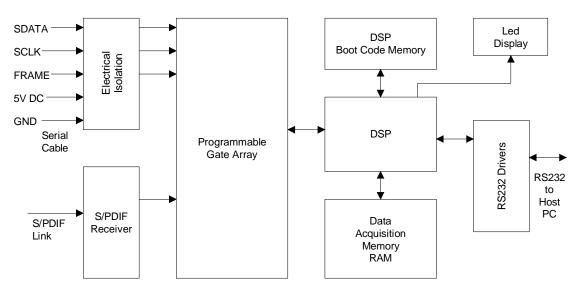

The CDBCapture+ interface board and software are used to capture blocks of serial data from an A/D converter on an evaluation board. This data can be transferred to a PC for analysis and storage. The CDBCapture+ board buffers the digital data in on-board RAM memory and transfers the data to the PC via an RS232 COM port. Figure 1 is a functional block diagram that illustrates the data acquisition process.

The setup for the CDBCapture+ board is simple. A serial cable is connected from the evaluation board to the CDBCapture+ board. This cable will in some cases be a multi-wire conductor and in other cases, depending on the evaluation board being tested, it may be an RCA phono jack or optical input for S/PDIF audio data. The interface circuits are provided with electrical isolation between the evaluation board and the CDBCapture+ board to eliminate ground loops. An RS232 cable is connected from the CDBCapture+ board to a PC COM port and the PC is loaded with the CDBCapture+ software. An external +5 Volt power supply is required to power the CDBCapture+ board, in addition to any power required for the evaluation board. Upon power-up, the DSP on the CDBCapture+ board starts monitoring the serial COM port for application software that allows the DSP to program a gate-array on the board to act as an interface for the specific A/D converter on the evaluation board. In this manner, the CDBCapture+ board can be reprogrammed to communicate with a large variety of different A/D converters and evaluation boards.

Once the on-board gate-array is programmed, the data collection process is started by sending a command from the PC to the CDBCapture+ board. LED indicators on the CDBCapture+ board indicate system status during acquisition of data from the evaluation board and during transfer of data to the PC. The CDBCapture+ board can be directed to collect one or, depending on the A/D converter being evaluated, two channels of data from the evaluation board. The data is stored in an on-board RAM until data acquisition is complete, then upon command from the PC, it is sent to the PC via the RS232 COM port.

The evaluation and display software provided for the PC was developed using LabWindows and performs the post processing of the digitized signals. Time plots, FFT analysis, noise analysis, and differential nonlinearity (DNL) analysis are included. The software allows as many as 32768 samples to be acquired and analyzed. DNL analysis is supported only for converters with 16 bits or lower resolutions. For more sophisticated data analysis, the LabWindows® development system can be purchased from National Instruments (512-794-0100).

LabWindows is a registered trademark of National Instruments Corp.

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise). Furthermore, no part of this publication way be used as a basis for manufacture or sale of any items without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks can be found at http://www.cirrus.com.

The CDBCapture+ board and software currently support the following Crystal A/D converter evaluation boards:

Data Acquisition Parts via a dual row 10 position header interface:

CS5012ACS5014CS5016CS5101ACS5102ACS5126CS5180CS5181CS5317CS5322CS5501CS5503CS5505CS5506CS5507CS5508CS5509CS5506CS5507

Audio Parts via RCA phono jack and optical inputs for S/PDIF audio data (for sample rates from 30 KHz to 96 KHz):

| CS5330 | CS5331 | CS5334 | CS5335 |

|--------|--------|--------|--------|

| CS5360 | CS5390 | CS5394 | CS5396 |

Future products will be added with software updates. Software updates are provided with the Crystal Product Guide CD-ROM and on the Crystal Website at www.crystal.com.

#### **Packaging List:**

CDBCapture+ Interface Board Serial 10 position ribbon cable connector RS232 Cable Note: To use the S/PDIF interface, a phono-jack cable must be purchased from an outside vendor.

The Capture+ evaluation software is installed using the setup utility provided on the Product Guide CD-ROM. The location for installation may be any drive/directory. README and HELP text files are provided and offer step-by-step instructions on setting up and operating both the hardware and software as well as providing information specific to each supported evaluation board. Once the software is installed and launched, the Startup Screen is displayed on the monitor, as shown in Figure 2.

Pressing the "OK" button starts the software that allows the user to setup the serial port between the Capture+ module and the PC and configure the module for a specific A/D converter. Screens showing the variety of analysis functions that can be utilized for evaluation of an A/D converter are shown and described below.

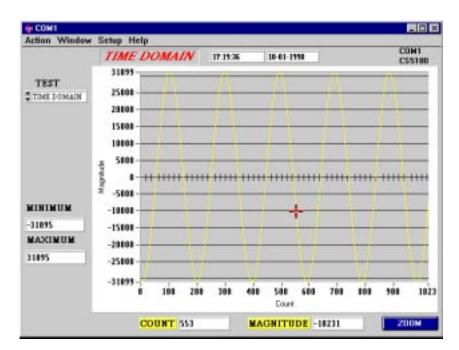

A Time Domain Analysis is initiated by connecting a signal source to the evaluation board and acquiring a user-selectable number of samples. The results of capturing a sine wave are shown in Figure 3. A reconstruction of the data samples is displayed, along with the sample count on the horizontal axis and magnitude (A/D counts) on the

Figure 1. Functional Block Diagram

Figure 2. Startup Screen

vertical axis. A mouse-controlled cursor can be used to select any point on the graph and display it's specific count and magnitude, shown below the graph. To the left of the graph, the maximum and minimum count values from all the data samples are displayed. A ZOOM button allows for zooming in on a group of points for a more detailed view.

Figure 3. Time Domain Analysis

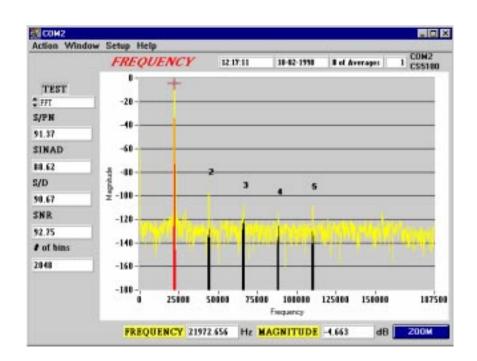

Using the same sine wave acquired data, a Frequency Domain Analysis can be performed and is shown in Figure 4, below. The Frequency Domain Analysis is performed by selecting "FFT" under the TEST window. The results of this analysis are displayed to the left and bottom of the graph. The graph shows the magnitude vs. frequency spectrum from DC to one half the sampling frequency, with the number of frequency bins equal to one half the number of samples taken. The fundamental and first four harmonics are defined by numbers on the graph while the fundamental frequency and its magnitude are shown below the graph. Four basic statistics relating to the FFT are shown to the left of the graph, these being Signal to Peak Noise (S/PN), Signal to Noise and Distortion (SINAD), Signal to Distortion (S/D), and Signal to Noise Ratio (SNR). The software allows the user to select the number of samples (binary numbers) to be used in acquiring the data for the FFT. Note: if the number of samples selected is too small or if the input frequency is set too low, it may not be possible for the FFT to discern the fundamental from the DC bins. In this case the software will display the following recommendation: "The test signal frequency falls within the DC bins and is therefore indistinguishable. Either increase the number of samples or increase the frequency of the test signal. Then acquire and try the FFT test again."

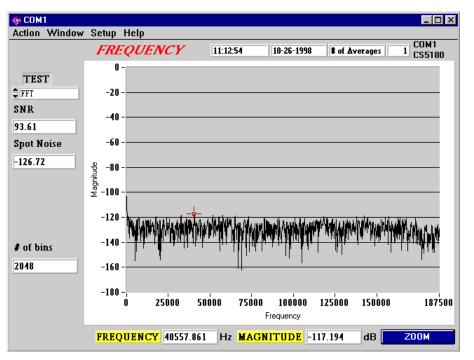

The software offers the user the option of performing a FFT frequency analysis without having to apply a sine wave signal input. By grounding the input and telling the computer what the maximum A/D count is for a full scale signal, the software will sample the grounded input and assume a full scale signal was applied, providing a theoretical Signal to Noise Ratio based on the internal noise of the system and converter. The display for a grounded input FFT is shown in Figure 5.

Figure 4. Frequency Domain Analysis

Figure 5. Grounded Input FFT

Figure 6 shows the results of a Histogram Analysis. This analysis was obtained by grounding the signal input to the evaluation board and acquiring data. The results of this analysis are useful in determining how much noise and offset error is in the system and A/D converter. In an ideal system with the input grounded, all readings should be zero, but due to noise and offsets, there will be some variation in the readings. A DC offset will result in the mean value of the readings being non-zero, and the MEAN value displayed to the left of the graph is an indication of the offset, in lsb's. If the histogram fits the normal Gaussian distribution, then the Standard Deviation (STD DEV) will be a measure of the RMS noise in the system. The overall peak-topeak variation in A/D counts is available by viewing the MINIMUM COUNT and MAXIMUM COUNT values shown to the left of the histogram. The statistical peak-to-peak noise is defined as the interval which contains six standard deviations, or 99.6% of all count occurrences, so multiplying the STD\_DEV value to the left of the histogram by six will yield the peak to peak noise.

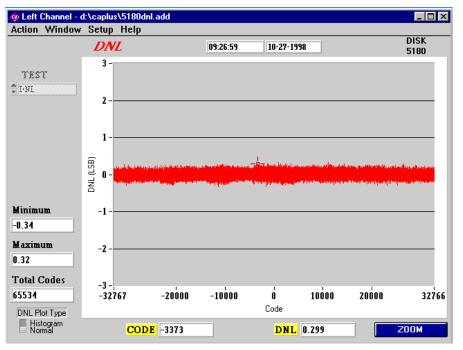

Figure 7 shows the analysis screen for a calculation of a converter's Differential Nonlinearity (DNL). To test for DNL, samples are taken using a linear over-ranged triangle wave for the signal. If a large number of samples are taken, then the number of occurrences of each code should be the same if the converter has perfect differential nonlinearity. Codes that occur less than average will have a negative DNL and codes that occur more often than average will have a DNL greater than zero. The graph shown in Figure 6 shows the variation in DNL for each count of the converter. A mouse-controlled cursor allows the operator to select a particular code and read out its specific DNL below the graph. To the left of the graph the maximum and minimum DNL values for all the codes are displayed. If a code has a DNL of -1, then that is a missing code, it never occurred during the sampling.

|                                                                                              | HISTOC                                                                                                              |    | M  | 12 | 28:50 | 1  | 10-02-1  | 998 | 11 |   |   | CON:<br>CSS1 |  |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----|----|----|-------|----|----------|-----|----|---|---|--------------|--|

| TEST<br>ENTOGRAM<br>(EAN<br>114<br>TD_DEV<br>142<br>VARIANCE<br>17<br>(INIMUM<br>1<br>AXIMUM | 6656<br>6144<br>5632<br>5120<br>4688<br>4096<br>4096<br>4096<br>4096<br>3584<br>4096<br>2048<br>1536<br>1024<br>512 |    |    |    |       |    | ÷        |     |    |   |   |              |  |

|                                                                                              | 1-3                                                                                                                 | -5 | à. | -3 | -2    | -1 | ů<br>Bin | i   | ż  | ż | à | ś            |  |

Figure 6. Histogram Analysis

Figure 7. Differential Nonlinearity Analysis

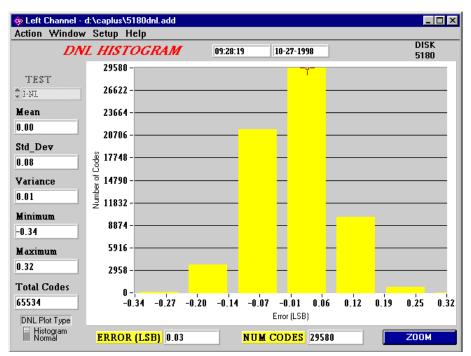

For high resolution converters, as shown in Figure 7, the DNL graph is very compressed, since 65534 codes are displayed over a length of several inches. This makes it very difficult to get a complete picture of the overall performance of the A/D converter. The DNL histogram screen, shown in Figure 8, can be used to get a better picture of the parts DNL performance. The histogram displays the same data that is in Figure 7, but breaks the

DNL error into groups, shown on the horizontal axis, and shows the number of codes within each group on the vertical axis. This view shows the relative number of codes that have large positive or negative DNL values, as opposed to a perfect converter where all the values would be under one vertical bar, corresponding to zero DNL. Statistical values for the entire distribution are displayed to the left of the histogram.

Figure 8. Differential Nonlinearity Histogram

## • Notes •