## CS8952

## CrystalLAN<sup>™</sup> 100BASE-X and 10BASE-T Transceiver

#### **Features**

- Single-Chip IEEE 802.3 Physical Interface IC for 100BASE-TX, 100BASE-FX and 10BASE-T

- Adaptive Equalizer provides Extended Length Operation (>160 m) with Superior Noise Immunity and NEXT Margin

- Extremely Low Transmit Jitter (<400 ps)

- Low Common Mode Noise on TX Driver for Reduced EMI Problems

- Integrated RX and TX Filters for 10BASE-T

- Compensation for Back-to-Back "Killer Packets"

- Digital Interfaces Supported

- Media Independent Interface (MII) for 100BASE-X and 10BASE-T

- Repeater 5-bit code-group interface (100BASE-X)

- 10BASE-T Serial Interface

- Register Set Compatible with DP83840A

- IEEE 802.3 Auto-Negotiation with Next Page Support

- Six LED drivers (LNK, COL, FDX, TX, RX, and SPD)

- Low power (135 mA Typ) CMOS design operates on a single 5 V supply

#### Description

The CS8952 uses CMOS technology to deliver a highperformance, low-cost 100BASE-X/10BASE-T Physical Layer (PHY) line interface. It makes use of an adaptive equalizer optimized for noise and near end crosstalk (NEXT) immunity to extend receiver operation to cable lengths exceeding 160 m. In addition, the transmit circuitry has been designed to provide extremely low transmit jitter (<400 ps) for improved link partner performance. Transmit driver common mode noise has been minimized to reduce EMI for simplified FCC certification.

The CS8952 incorporates a standard Media Independent Interface (MII) for easy connection to a variety of 10 and 100 Mb/s Media Access Controllers (MACs). The CS8952 also includes a pseudo-ECL interface for use with 100Base-FX fiber interconnect modules.

#### **ORDERING INFORMATION**

See "Ordering Information" on page 80.

## TABLE OF CONTENTS

| 1. SPECIFICATIONS AND CHARACTERISTICS                    |    |

|----------------------------------------------------------|----|

| 2. INTRODUCTION                                          |    |

| 2.1 High Performance Analog                              |    |

| 2.2 Low Power Consumption                                |    |

| 2.3 Application Flexibility                              |    |

| 2.4 Typical Connection Diagram                           |    |

| 3. FUNCTIONAL DESCRIPTION                                | 18 |

| 3.1 Major Operating Modes                                |    |

| 3.1.1 100BASE-X MII Application (TX and FX)              | 20 |

| Symbol Encoding and Decoding                             | 20 |

| 100 Mb/s Loopback                                        | 22 |

| 3.1.2 100BASE-X Repeater Application                     | 22 |

| 3.1.3 10BASE-T MII Application                           | 23 |

| Full and Half Duplex operation                           |    |

| Collision Detection                                      |    |

| Jabber                                                   |    |

| Link Pulses                                              |    |

| Receiver Squelch                                         |    |

| 10BASE-T Loopback                                        |    |

| Carrier Detection                                        |    |

| 3.1.4 10BASE-T Serial Application                        |    |

| 3.2 Auto-Negotiation                                     |    |

| 3.3 Reset Operation                                      |    |

| 3.4 LED Indicators                                       |    |

| 4. MEDIA INDEPENDENT INTERFACE (MII)                     |    |

| 4.1 MII Frame Structure                                  |    |

| 4.2 MII Receive Data                                     |    |

| 4.3 MII Transmit Data                                    |    |

| 4.4 MII Management Interface                             |    |

| 4.5 MII Management Frame Structure                       |    |

| 5. CONFIGURATION                                         |    |

| 5.1 Configuration At Power-up/Reset Time                 |    |

| 5.2 Configuration Via Control Pins                       |    |

| 5.2 Configuration via Control Pins                       |    |

| 6. CS8952 REGISTERS                                      |    |

| 7. DESIGN CONSIDERATIONS                                 |    |

| 7.1 Twisted Pair Interface                               |    |

| 7.1 TWISTED Pair Interface                               |    |

|                                                          |    |

| 7.3 Internal Voltage Reference                           |    |

| 7.4 Clocking Schemes                                     |    |

| 7.5 Recommended Magnetics                                |    |

| 7.6 Power Supply and Decoupling                          |    |

| 7.7 General Layout Recommendations                       |    |

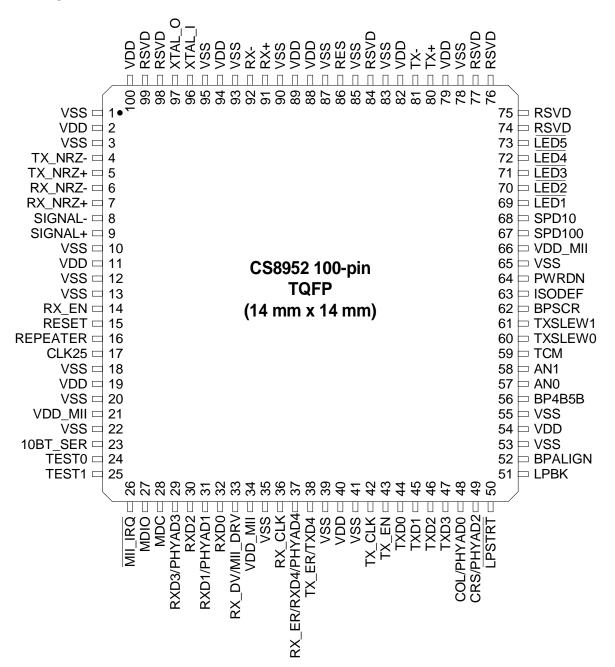

| 8. PIN DESCRIPTIONS                                      |    |

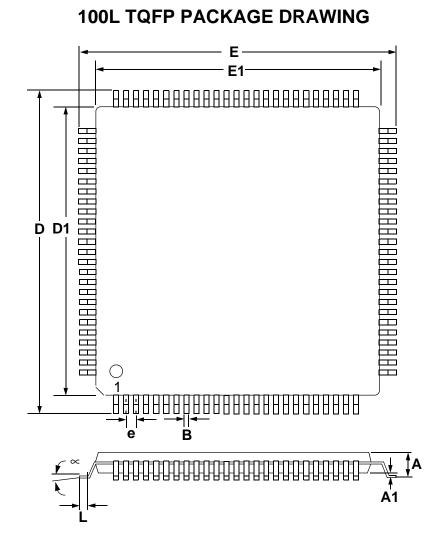

| 9. PACKAGE DIMENSIONS.                                   |    |

| 10. ORDERING INFORMATION                                 |    |

| 11. ENVIRONMENTAL, MANUFACTURING, & HANDLING INFORMATION |    |

| 12. REVISION HISTORY                                     | 81 |

#### 1. SPECIFICATIONS AND CHARACTERISTICS

#### **ABSOLUTE MAXIMUM RATINGS** (AVSS, DVSS = 0 V, all voltages with respect to 0 V.)

| Parar               | neter              | Symbol              | Min  | Max                   | Unit |

|---------------------|--------------------|---------------------|------|-----------------------|------|

| Power Supply        |                    | V <sub>DD</sub>     | -0.3 | 6.0                   | V    |

|                     |                    | V <sub>DD_MII</sub> | -0.3 | 6.0                   |      |

| Input Current       | Except Supply Pins |                     | -    | +/-10.0               | mA   |

| Input Voltage       |                    |                     | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| Ambient Temperature | Power Applied      |                     | -55  | +125                  | °C   |

| Storage Temperature |                    |                     | -65  | +150                  | °C   |

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

## **RECOMMENDED OPERATING CONDITIONS** (AVSS, DVSS = 0 V, all voltages with respect

to 0 V.)

| Parameter                     | Symbol            | Min  | Max  | Unit |

|-------------------------------|-------------------|------|------|------|

| Power Supply Col              | e V <sub>DD</sub> | 4.75 | 5.25 | V    |

| N                             |                   | 3.0  | 5.25 | V    |

| Operating Ambient Temperature | T <sub>A</sub>    | 0    | 70   | °C   |

## QUARTZ CRYSTAL REQUIREMENTS (If a 25 MHz quartz crystal is used, it must meet the fol-

lowing specifications.)

| Parameter                                            | Min | Тур   | Max | Unit |

|------------------------------------------------------|-----|-------|-----|------|

| Parallel Resonant Frequency                          | -   | 25.0  | -   | MHz  |

| Resonant Frequency Error (CL = 15 pF)                | -50 | -     | +50 | ppm  |

| Resonant Frequency Change Over Operating Temperature | -40 | -     | +40 | ppm  |

| Crystal Load Capacitance                             | -   | 15    | -   | pF   |

| Motional Crystal Capacitance                         | -   | 0.021 | -   | pF   |

| Series Resistance                                    | -   | -     | 18  | Ω    |

| Shunt Capacitance                                    | -   | -     | 7   | pF   |

## **DC CHARACTERISTICS** (Over recommended operating conditions)

| Parameter                                             | Symbol           | Min        | Тур | Max         | Unit |

|-------------------------------------------------------|------------------|------------|-----|-------------|------|

| External Oscillator                                   |                  |            |     |             |      |

| XTAL_I Input Low Voltage                              | V <sub>IXH</sub> | -0.3       | -   | 0.5         | V    |

| XTAL_I Input High Voltage                             | V <sub>IXH</sub> | 3.5        | -   | VDD+0.5     | V    |

| XTAL_I Input Low Current                              | I <sub>IXL</sub> | -40        | -   | -           | μA   |

| XTAL_I Input High Current                             | I <sub>IXH</sub> | -          | -   | 40          | μA   |

| XTAL_I Input Capacitance                              | CL               |            | -   | 35          | pF   |

| XTAL_I Input Cycle Time                               | t <sub>IXC</sub> | 39.996     | -   | 40.004      | ns   |

| XTAL_I Input Low Time                                 | t <sub>IXL</sub> | 18         | -   | 22          | ns   |

| XTAL_I Input High Time                                | t <sub>XH</sub>  | 18         | -   | 22          | ns   |

| Power Supply                                          |                  |            | 1   |             |      |

| Power Supply Current 100BASE-TX (Note 1)              | I <sub>DD</sub>  | -          | 135 | 145         | mA   |

| 100BASE-FX (Note 1)                                   |                  | -          | 90  | -           |      |

| 10BASE-T (Note 1)                                     |                  | -          | 80  | -           |      |

| Hardware Power-Down (Note 1)                          | BBIII BI         | -          | 900 | -           | μA   |

| Software Power-Down (Note 1)                          | DDOI DI          | -          | 20  | -           | mA   |

| Low Power Power-Up (Note 1)                           | IDDSLPUP         | -          | 900 | -           | μA   |

| Digital I/O                                           |                  |            | 1   | -           |      |

| Output Low Voltage                                    | V <sub>OL</sub>  |            |     |             | V    |

| CLK25, MII_IRQ, SPD10, SPD100 I <sub>OL</sub> = 4.0mA |                  | -          | -   | 0.4         |      |

|                                                       |                  | _          | _   | 0.4         |      |

|                                                       |                  |            |     | 0.4         |      |

| LED[4:0] I <sub>OL</sub> = 10.0mA                     |                  |            |     |             |      |

| Output Low Voltage (MII_DRV = 1)                      | V <sub>OL</sub>  |            |     |             | V    |

| COL, CRS, MDIO, RXD[3:0],                             |                  |            |     |             |      |

| RX_CLK, RX_DV, RX_ER,                                 |                  |            |     | 0.4         |      |

| TX_CLK $I_{OL} = 4.0 \text{mA}$                       |                  | -          | -   | 0.4<br>3.05 |      |

| $VDD_MII = 5V; I_{OL} = 43.0 \text{mA}$               |                  | _          | -   | 2.1         |      |

| VDD_MII = 3.3V, I <sub>OL</sub> = 26.0mA              |                  |            |     |             |      |

| Output Low Voltage (MII_DRV = 0)                      | V <sub>OL</sub>  |            |     |             | V    |

| COL, CRS, MDIO, RXD[3:0],<br>RX_CLK, RX_DV, RX_ER,    |                  |            |     |             |      |

| $TX_CLK$ $I_{OL} = 4.0 \text{mA}$                     |                  | _          | _   | 0.4         |      |

|                                                       |                  |            |     |             |      |

| Output High Voltage                                   | V <sub>OH</sub>  |            |     |             | V    |

| CLK25, SPD10, SPD100 $I_{OH} = -4.0$ mA               |                  | 2.4        | -   | -           |      |

|                                                       |                  |            |     |             |      |

| Output High Voltage (MII_DRV = 1)                     | V <sub>OH</sub>  |            |     |             | V    |

| COL, CRS, MDIO, RXD[3:0],                             | 0.1              |            |     |             |      |

| RX_CLK, RX_DV, RX_ER,                                 |                  |            |     |             |      |

| TX_CLK I <sub>OH</sub> = -4.0mA                       |                  | 2.4        | -   | -           |      |

| $VDD_MII = 5V; I_{OH} = -20.0mA$                      |                  | 1.1<br>1.1 | -   |             |      |

| VDD_MII = 3.3V, I <sub>OH</sub> = -20.0mA             |                  | 1.1        | _   | _           |      |

#### **DC CHARACTERISTICS** (CONTINUED) (Over recommended operating conditions)

| Parameter                                                                               |                          | Symbol            | Min                              | Тур | Max                              | Unit |

|-----------------------------------------------------------------------------------------|--------------------------|-------------------|----------------------------------|-----|----------------------------------|------|

| Output High Voltage (MII_DRV = 0)<br>COL, CRS, MDIO, RXD[3:0],<br>RX_CLK, RX_DV, RX_ER, | )                        | V <sub>OH</sub>   |                                  |     |                                  | V    |

| TX_CLK                                                                                  | I <sub>OH</sub> = -4.0mA |                   | 2.4                              | -   | -                                |      |

| Input Low Voltage<br>All Inputs Except AN[1:0], TCM, TX                                 | (SLEW[1:0]               | V <sub>IL</sub>   | -                                | -   | 0.8                              | V    |

| Input High Voltage<br>All Inputs Except AN[1:0], TCM, TX                                | (SLEW[1:0]               | V <sub>IH</sub>   | 2.0                              | -   | -                                | V    |

| Tri-Level Input Voltages<br>AN[1:0], TCM, TXSLEW[1:0]                                   |                          | V <sub>IL</sub>   | -                                | -   | 1/3 V <sub>DD_MII</sub><br>- 20% | V    |

|                                                                                         |                          | $V_{IM}$          | 1/3 V <sub>DD_MII</sub><br>+ 20% | -   | 2/3 V <sub>DD_MII</sub><br>- 20% |      |

|                                                                                         |                          | $V_{\text{IH}}$   | 2/3 V <sub>DD_MII</sub><br>+ 20% | -   | -                                |      |

| Input Low Current<br>MDC, TXD[3:0], TX_CLK, TX_EN,                                      |                          | Ι <sub>ΙL</sub>   |                                  |     |                                  | μA   |

| TX_ER                                                                                   | $V_{I} = 0.0V$           |                   | -20                              | -   | -                                |      |

| MDIO                                                                                    | $V_{1} = 0.0V$           |                   | -3800                            | -   | -                                |      |

| Input High Current<br>MDC, TXD[3:0], TX_CLK, TX_EN,                                     | 1                        | I <sub>IH</sub>   |                                  |     |                                  | μΑ   |

| TX_ER                                                                                   | $V_{I} = 5.0V$           |                   | -                                | -   | 200                              |      |

| MDIO                                                                                    | V <sub>I</sub> = 5.0V    |                   | -                                | -   | 20                               |      |

| Input Leakage Current<br>All Other Inputs                                               | 0<=V<=V <sub>DD</sub>    | I <sub>LEAK</sub> | -10                              |     | +10                              | μΑ   |

Notes: 1. With digital outputs connected to CMOS loads.

## **10BASE-T CHARACTERISTICS**

| Parameter                                                       | Symbol            | Min | Тур | Max     | Unit |

|-----------------------------------------------------------------|-------------------|-----|-----|---------|------|

| 10BASE-T Interface                                              |                   |     |     |         |      |

| Transmitter Differential Output Voltage (Peak)                  | V <sub>OD</sub>   | 2.2 | -   | 2.8     | V    |

| Receiver Normal Squelch Level (Peak)                            | V <sub>ISQ</sub>  | 300 | -   | 525     | mV   |

| Receiver Low Squelch Level (LoRxSquelch bit set)                | V <sub>SQL</sub>  | 125 | -   | 290     | mV   |

| 10BASE-T Transmitter                                            |                   |     |     |         |      |

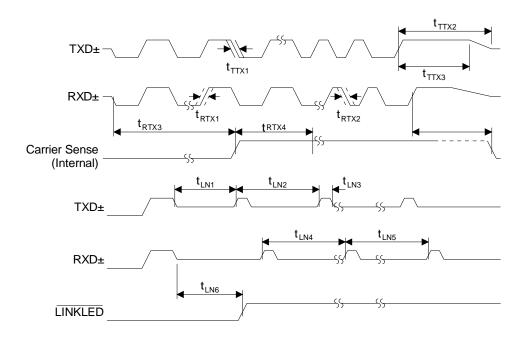

| TXD Pair Jitter into 100 $\Omega$ Load                          | t <sub>TTX1</sub> | -   | -   | 8       | ns   |

| TXD Pair Return to $\leq$ 50 mV after Last Positive Transition  | t <sub>TTX2</sub> | -   | -   | 4.5     | μs   |

| TXD Pair Positive Hold Time at End of Packet                    | t <sub>TTX3</sub> | 250 | -   | -       | ns   |

| 10BASE-T Receiver                                               |                   |     |     |         |      |

| Allowable Received Jitter at Bit Cell Center                    | t <sub>TRX1</sub> | -   | -   | +/-13.5 | ns   |

| Allowable Received Jitter at Bit Cell Boundary                  | t <sub>TRX2</sub> | -   | -   | +/-13.5 | ns   |

| 10BASE-T Link Integrity                                         |                   |     |     | -       |      |

| First Transmitted Link Pulse after Last Transmit-<br>ted Packet | t <sub>LN1</sub>  | 15  | 16  | 17      | ms   |

| Time Between Transmitted Link Pulses                            | t <sub>LN2</sub>  | 15  | 16  | 17      | ms   |

| Width of Transmitted Link Pulses                                | t <sub>LN3</sub>  | 60  | -   | 200     | ns   |

| Minimum Received Link Pulses Separation                         | t <sub>LN4</sub>  | 2   | 5   | 7       | ms   |

| Maximum Received Link Pulse Separation                          | t <sub>LN5</sub>  | 25  | 52  | 150     | ms   |

| Last Receive Activity to Link Fail (Link Loss<br>Timer)         | t <sub>LN6</sub>  | 50  | 52  | 150     | ms   |

| 10Base-T Jabber/Unjabber Timing                                 |                   |     |     |         |      |

| Maximum Transmit Time                                           |                   | -   | 105 | -       | ms   |

| Unjabber Time                                                   |                   | -   | 406 | -       | ms   |

## **100BASE-X CHARACTERISTICS**

| Parameter                                 | Symbol            | Min    | Тур  | Max    | Unit             |

|-------------------------------------------|-------------------|--------|------|--------|------------------|

| 100BASE-TX Transmitter                    |                   |        | •    |        | •                |

| TX Differential Output Voltage (Peak)     | V <sub>OP</sub>   | 0.95   | -    | 1.05   | V                |

| Signal Amplitude Symmetry                 | V <sub>SYM</sub>  | 98     | -    | 102    | %                |

| Signal Rise/Fall Time                     | t <sub>RF</sub>   | 3.0    | -    | 5.0    | ns               |

| Rise/Fall Symmetry                        | t <sub>RFS</sub>  | -      | -    | 0.5    | ns               |

| Duty Cycle Distortion                     | t <sub>DCD</sub>  | -      | -    | +/-0.5 | ns               |

| Overshoot/Undershoot                      | t <sub>OS</sub>   | -      | -    | 5      | %                |

| Transmit Jitter                           | t <sub>JT</sub>   | -      | 400  | 1400   | ps               |

| TX Differential Output Impedance          | Z <sub>OUT</sub>  | -      | 100  | -      | ohms             |

| 100BASE-TX Receiver                       |                   |        |      |        |                  |

| Receive Signal Detect Assert Threshold    |                   | -      | -    | 1.0    | V <sub>p-p</sub> |

| Receive Signal Detect De-assert Threshold |                   | 0.2    | -    | -      | V <sub>p-p</sub> |

| Receive Signal Detect Assert Time         |                   | -      | -    | 1000   | μs               |

| Receive Signal Detect De-assert Time      |                   | -      | -    | 350    | μs               |

| 100BASE-FX Transmitter                    |                   |        |      |        |                  |

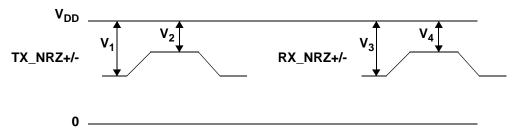

| TX_NRZ+/- Output Voltage - Low            | V <sub>1</sub>    | -1.830 | -    | -1.605 | V                |

| TX_NRZ+/- Output Voltage - High           | V <sub>2</sub>    | -1.035 | -    | -0.880 | V                |

| Signal Rise/Fall Time                     | T <sub>RF</sub>   | -      | -    | 1.6    | ns               |

| 100Base-FX Receiver                       |                   |        |      | ÷      |                  |

| RX_NRZ+/- Input Voltage - Low             | V <sub>3</sub>    | -1.830 | -    | -1.605 | V                |

| RX_NRZ+/- Input Voltage - High            | V <sub>4</sub>    | -1.035 | -    | -0.880 | V                |

| Common Mode Input Range                   | V <sub>CMIP</sub> | -      | 3.56 | -      | V                |

RX/TX Signaling for 100Base-FX

## **100BASE-TX MII RECEIVE TIMING - 4B/5B ALIGNED MODES**

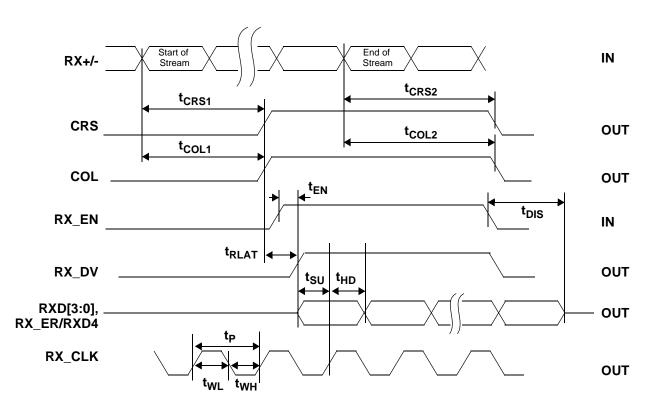

| Parameter                                                                   | Symbol                           | Min | Тур   | Max | Unit |

|-----------------------------------------------------------------------------|----------------------------------|-----|-------|-----|------|

| RX_CLK Period                                                               | t <sub>P</sub>                   | -   | 40    | -   | ns   |

| RX_CLK Pulse Width                                                          | t <sub>WL,</sub> t <sub>WH</sub> | -   | 20    | -   | ns   |

| RXD[3:0],RX_ER/RXD4,RX_DV setup to rising edge of RX_CLK                    | t <sub>SU</sub>                  | 10  | -     | -   | ns   |

| RXD[3:0],RX_ER/RXD4,RX_DV hold from rising edge of RX_CLK                   | t <sub>HD</sub>                  | 10  | -     | -   | ns   |

| CRS to RXD latency 4B Aligned                                               |                                  | 2   | 3 - 6 | 8   | BT   |

| 5B Aligned                                                                  |                                  | 2   | 3 - 6 | 8   |      |

| "Start of Stream" to CRS asserted                                           | t <sub>CRS1</sub>                | -   | 10    | 11  | BT   |

| "End of Stream" to CRS de-asserted                                          | t <sub>CRS2</sub>                | -   | -     | 21  | BT   |

| "Start of Stream" to COL asserted                                           | t <sub>COL1</sub>                | -   | -     | 11  | BT   |

| "End of Stream" to COL de-asserted                                          | t <sub>COL2</sub>                | -   | -     | 21  | BT   |

| RX_EN asserted to RX_DV, RXD[3:0] valid                                     | t <sub>EN</sub>                  | -   | TBD   | -   | ns   |

| RX_EN de-asserted to RX_DV, RXD[3:0].<br>RX_ER/RXD4 in high impedance state | t <sub>DIS</sub>                 | -   | TBD   | -   | ns   |

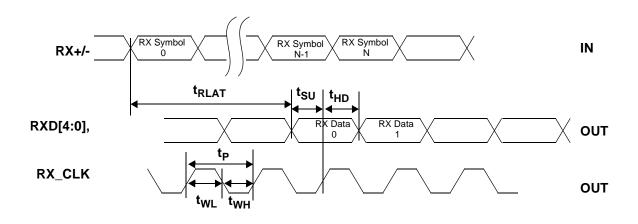

## **100BASE-TX MII RECEIVE TIMING - 5B BYPASS ALIGN MODE**

| Parameter                                      | Symbol                           | Min | Тур | Max | Unit |

|------------------------------------------------|----------------------------------|-----|-----|-----|------|

| RX_CLK Period                                  | t <sub>P</sub>                   | -   | 40  | -   | ns   |

| RX_CLK Pulse Width                             | t <sub>WL,</sub> t <sub>WH</sub> | -   | 20  | -   | ns   |

| RXD[4:0] setup to rising edge of RX_CLK        | t <sub>SU</sub>                  | 10  | -   | -   | ns   |

| RXD[4:0] hold after rising edge of RX_CLK      | t <sub>HD</sub>                  | 10  | -   | -   | ns   |

| Start of 5B symbol to symbol output on RX[4:0] | t <sub>RLAT</sub>                | 5   | -   | 9   | BT   |

| 5B Mode                                        |                                  |     |     |     |      |

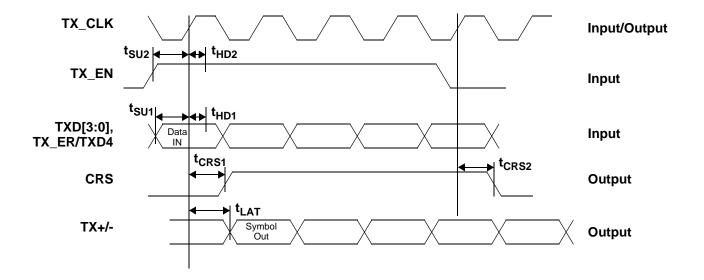

## 100BASE-TX MII TRANSMIT TIMING - 4B/5B ALIGN MODES

| Parameter                                 | Symbol            | Min | Тур | Max | Unit |

|-------------------------------------------|-------------------|-----|-----|-----|------|

| TXD[3:0] Setup to TX_CLK High             | t <sub>SU1</sub>  | 10  | -   | -   | ns   |

| TX_EN Setup to TX_CLK High                | t <sub>SU2</sub>  | 10  | -   | -   | ns   |

| TXD[3:0] Hold after TX_CLK High           | t <sub>HD1</sub>  | 0   | -   | -   | ns   |

| TX_ER Hold after TX_CLK High              | t <sub>HD2</sub>  | 0   | -   | -   | ns   |

| TX_EN Hold after TX_CLK High              | t <sub>HD3</sub>  | 0   | -   | -   | ns   |

| TX_EN "high" to CRS asserted latency      | t <sub>CRS1</sub> | -   |     | 8   | BT   |

| TX_EN "low" to CRS de-asserted latency    | t <sub>CRS2</sub> | -   |     | 8   | BT   |

| TX_EN "high" to TX+/- output (TX Latency) | t <sub>LAT</sub>  | 6   | 7   | 8   | BT   |

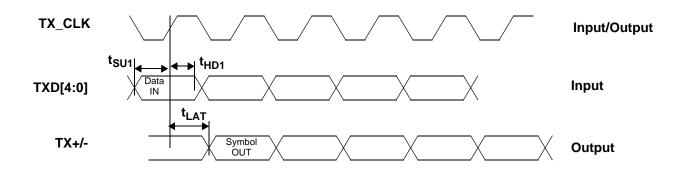

## **100BASE-TX MII TRANSMIT TIMING - 5B BYPASS ALIGN MODE**

| Parameter                                     | Symbol           | Min | Тур | Max | Unit |

|-----------------------------------------------|------------------|-----|-----|-----|------|

| TXD[4:0] Setup to TX_CLK High                 | t <sub>SU1</sub> | 10  | -   | -   | ns   |

| TXD[4:0] Hold after TX_CLK High               | t <sub>HD1</sub> | 0   | -   | -   | ns   |

| TX_ER Hold after TX_CLK High                  | t <sub>HD2</sub> | 0   | -   | -   | ns   |

| TXD[4:0] Sampled to TX+/- output (TX Latency) | t <sub>LAT</sub> | -   | 6   | 7   | ns   |

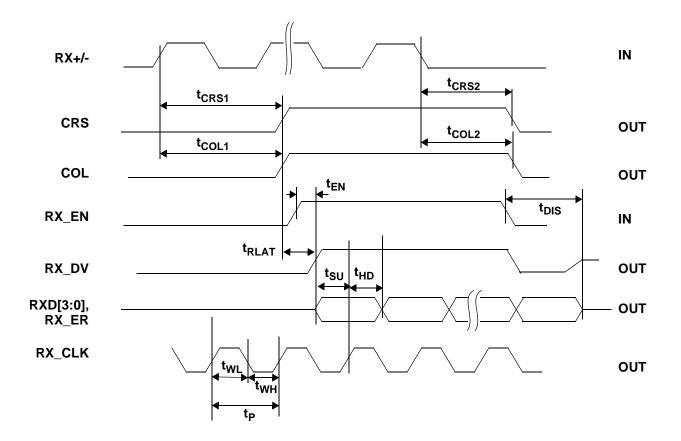

## **10BASE-T MII RECEIVE TIMING**

| Parameter                                                              | Symbol                           | Min | Тур | Max | Unit |

|------------------------------------------------------------------------|----------------------------------|-----|-----|-----|------|

| RX_CLK Period                                                          | t <sub>P</sub>                   | -   | 400 | -   | ns   |

| RX_CLK Pulse Width                                                     | t <sub>WL,</sub> t <sub>WH</sub> | -   | 200 | -   | ns   |

| RXD[3:0], RX_ER, RX_DV setup to rising edge of<br>RX_CLK               | t <sub>SU</sub>                  | 30  | -   | -   | ns   |

| RXD[3:0], RX_ER, RX_DV hold from rising edge<br>of RX_CLK              | t <sub>HD</sub>                  | 30  | -   | -   | ns   |

| RX data valid from CRS                                                 | t <sub>RLAT</sub>                | -   | 8   | 10  | BT   |

| RX+/- preamble to CRS asserted                                         | t <sub>CRS1</sub>                | -   | 5   | 7   | BT   |

| RX+/- end of packet to CRS de-asserted                                 | t <sub>CRS2</sub>                |     | 2.5 | 3   | BT   |

| RX+/- preamble to COL asserted                                         | t <sub>COL1</sub>                | 0   | -   | 7   | BT   |

| RX+/- end of packet to COL de-asserted                                 | t <sub>COL2</sub>                | -   | -   | 3   | BT   |

| RX_EN asserted to RX_DV, RXD[3:0], RX_ER valid                         | t <sub>EN</sub>                  | -   | -   | 60  | ns   |

| RX_EN de-asserted to RX_DV, RXD[3:0]. RX_ER<br>in high impedance state | t <sub>DIS</sub>                 | -   | -   | 60  | ns   |

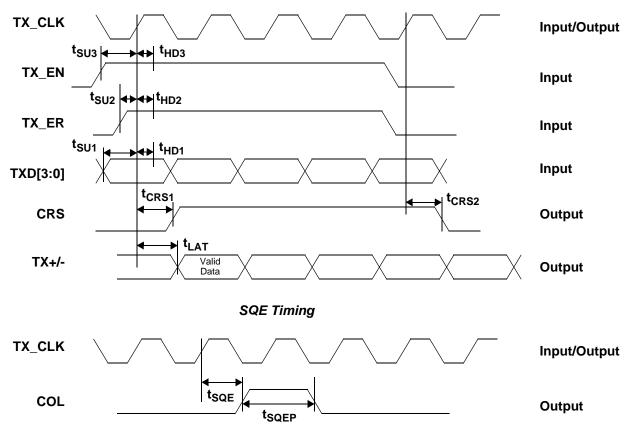

## **10BASE-T MII TRANSMIT TIMING**

| Parameter                                 | Symbol            | Min  | Тур | Max | Unit |

|-------------------------------------------|-------------------|------|-----|-----|------|

| TXD[3:0] Setup to TX_CLK High             | t <sub>SU1</sub>  | 10   | -   | -   | ns   |

| TX_ER Setup to TX_CLK High                | t <sub>SU2</sub>  | 10   | -   | -   | ns   |

| TX_EN Setup to TX_CLK High                | t <sub>SU3</sub>  | 10   | -   | -   | ns   |

| TXD[3:0] Hold after TX_CLK High           | t <sub>HD1</sub>  | 0    | -   | -   | ns   |

| TX_ER Hold after TX_CLK High              | t <sub>HD2</sub>  | 0    | -   | -   | ns   |

| TX_EN Hold after TX_CLK High              | t <sub>HD3</sub>  | 0    | -   | -   | ns   |

| TX_EN "high" to CRS asserted latency      | t <sub>CRS1</sub> | 0    | -   | 4   | BT   |

| TX_EN "low" to CRS de-asserted latency    | t <sub>CRS2</sub> | 0    | -   | 16  | BT   |

| TX_EN "high" to TX+/- output (TX Latency) | t <sub>LAT</sub>  | 6    | -   | 14  | BT   |

| SQE Timing                                | ·                 |      |     |     | -    |

| COL (SQE) Delay after CRS de-asserted     | t <sub>COL</sub>  | 0.65 | 0.9 | 1.6 | μs   |

| COL (SQE) Pulse Duration                  | t <sub>COLP</sub> | 0.65 | 1.0 | 1.6 | μs   |

10BASE-T Transmit Timing

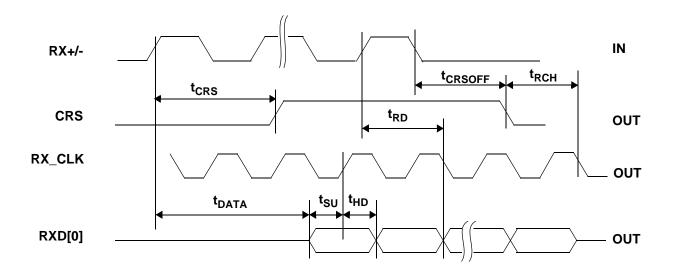

## **10BASE-T SERIAL RECEIVE TIMING**

| Parameter                     | Symbol              | Min | Тур | Max  | Unit |

|-------------------------------|---------------------|-----|-----|------|------|

| RX+/- active to RXD[0] active | t <sub>DATA</sub>   | -   | -   | 1200 | ns   |

| RX+/- active to CRS active    | t <sub>CRS</sub>    | -   | -   | 600  | ns   |

| RXD[0] setup from RX_CLK      | t <sub>RDS</sub>    | 35  | -   | -    | ns   |

| RXD[0] hold from RX_CLK       | t <sub>RDH</sub>    | 50  | -   | -    | ns   |

| RX_CLK hold after CRS off     | t <sub>RCH</sub>    | 5   | -   | -    | ns   |

| RXD[0] throughput delay       | t <sub>RD</sub>     | -   | -   | 250  | ns   |

| CRS turn off delay            | t <sub>CRSOFF</sub> | -   | -   | 400  | ns   |

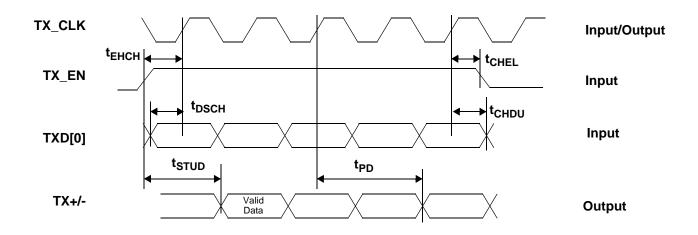

## **10BASE-T SERIAL TRANSMIT TIMING**

| Parameter                 | Symbol            | Min | Тур | Max | Unit |

|---------------------------|-------------------|-----|-----|-----|------|

| TX_EN Setup from TX_CLK   | t <sub>EHCH</sub> | 10  | -   | -   | ns   |

| TX_EN Hold after TX_CLK   | t <sub>CHEL</sub> | 10  | -   | -   | ns   |

| TXD[0] Setup from TX_CLK  | t <sub>DSCH</sub> | 10  | -   | -   | ns   |

| TXD[0] Hold after TX_CLK  | t <sub>CHDU</sub> | 10  | -   | -   | ns   |

| Transmit start-up delay   | t <sub>STUD</sub> | -   | -   | 500 | ns   |

| Transmit throughput delay | t <sub>TPD</sub>  | -   | -   | 500 | ns   |

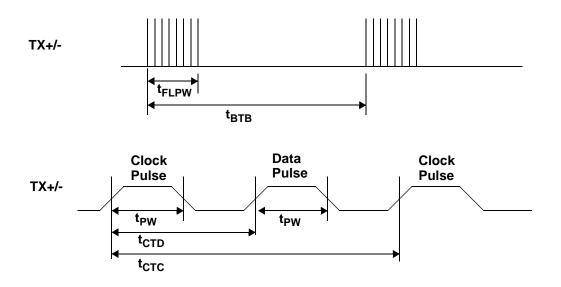

## **AUTO NEGOTIATION / FAST LINK PULSE TIMING**

| Parameter                   | Symbol            | Min  | Тур | Мах  | Unit |

|-----------------------------|-------------------|------|-----|------|------|

| FLP burst to FLP burst      | t <sub>BTB</sub>  | 15   | 16  | 17   | ms   |

| FLP burst width             | t <sub>FLPW</sub> | -    | 2   | -    | ms   |

| Clock/Data pulses per burst | -                 | 17   | -   | 33   | ea.  |

| Clock/Data pulse width      | t <sub>PW</sub>   | -    | 100 | -    | ns   |

| Clock pulse to Data pulse   | t <sub>CTD</sub>  | 55.5 | 64  | 69.5 | μs   |

| Clock pulse to clock pulse  | t <sub>CTC</sub>  | 111  | 128 | 139  | μs   |

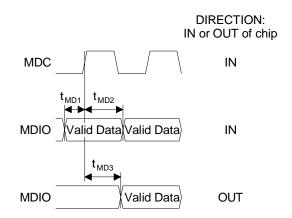

## SERIAL MANAGEMENT INTERFACE TIMING

| Parameter                           | Symbol                           | Min | Тур | Max | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| MDC Period                          | t <sub>p</sub>                   | 60  | -   | -   | ns   |

| MDC Pulse Width                     | t <sub>WL</sub> ,t <sub>WH</sub> | 40  | -   | 60  | %    |

| MDIO Setup to MDC (MDIO as input)   | t <sub>MD1</sub>                 | 10  | -   | -   | ns   |

| MDIO Hold after MDC (MDIO as input) | t <sub>MD2</sub>                 | 10  | -   | -   | ns   |

| MDC to MDIO valid (MDIO as output)  | t <sub>MD3</sub>                 | 0   | -   | 40  | ns   |

#### 2. INTRODUCTION

The CS8952 is a complete physical-layer transceiver for 100BASE-TX and 10BASE-T applications. Additionally, the CS8952 can be used with an external optical module for 100BASE-FX.

#### 2.1 High Performance Analog

The highly integrated mixed-signal design of the CS8952 eliminates the need for external analog circuitry such as external transmit or receive filters. The CS8952 builds upon Cirrus Logic's experience in pioneering the high-volume manufacturing of 10BASE-T integrated circuits with "true" internal filters. The CS8952, CS8920, CS8904, and CS8900 include fifth-order, continuous-time Butterworth 10BASE-T transmit and receive filters, allowing those products to meet 10BASE-T wave shape, emission, and frequency content requirements without external filters.

#### 2.2 Low Power Consumption

The CS8952 is implemented in low power CMOS, consuming only 135 mA typically. Three low-power modes are provided to make the CS8952 ideal for power sensitive applications such as CardBus.

#### 2.3 Application Flexibility

The CS8952's digital interface and operating modes can be tailored to efficiently support a wide variety of applications. For example, the Media Independent Interface (MII) supports 100BASE-TX, 100BASE-FX and 10BASE-T NIC cards, switch ports and router ports. Additionally, the low-latency "repeater" interface mode minimizes data delay through the CS8952, facilitating system compliance with overall network delay budgets. To support 10BASE-T applications, the CS8952 provides a 10BASE-T serial port (Seven-wire ENDEC interface).

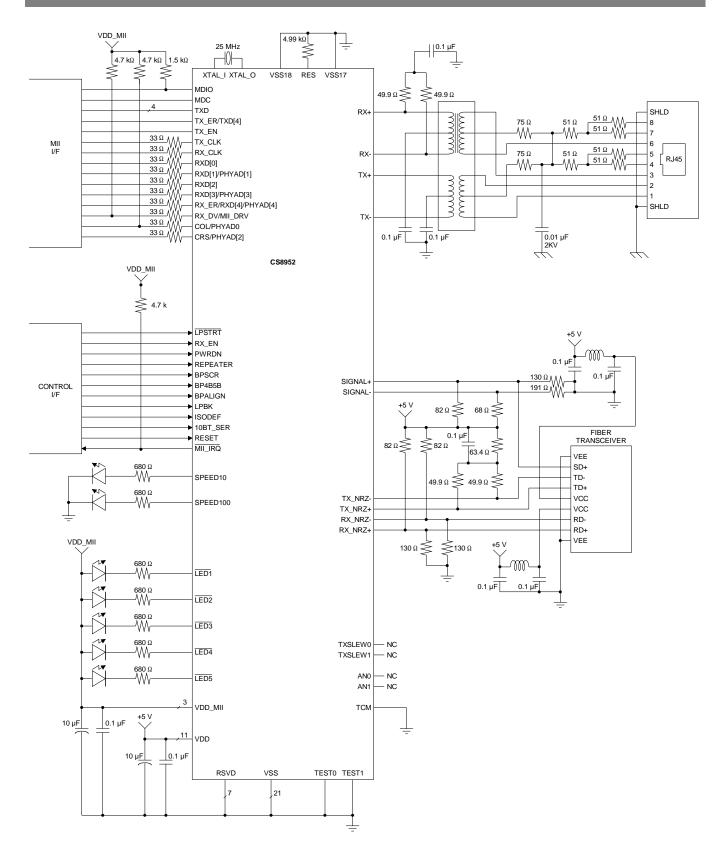

#### 2.4 Typical Connection Diagram

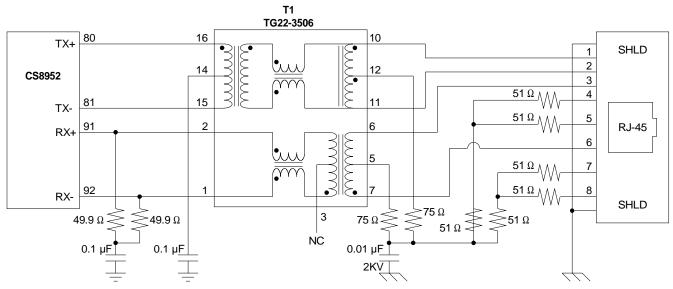

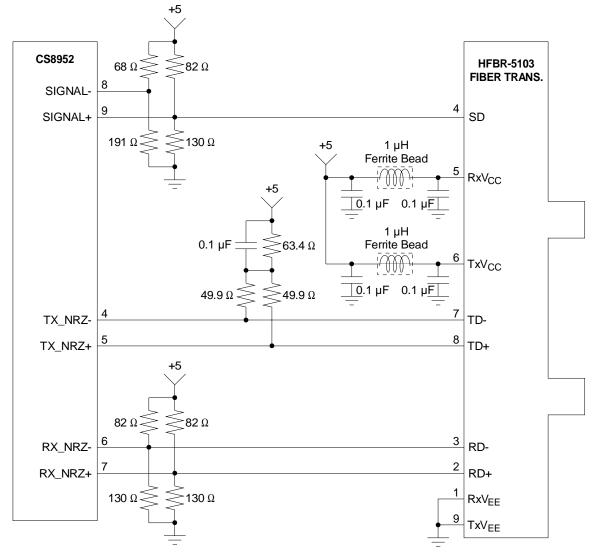

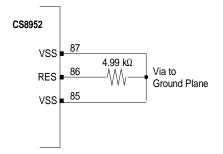

**Figure 1** illustrates a typical MII to CS8952 application with twisted-pair and fiber interfaces. Refer

to the Analog Design Considerations section for detailed information on power supply requirements and decoupling, crystal and magnetics requirements, and twisted-pair and fiber transceiver connections.

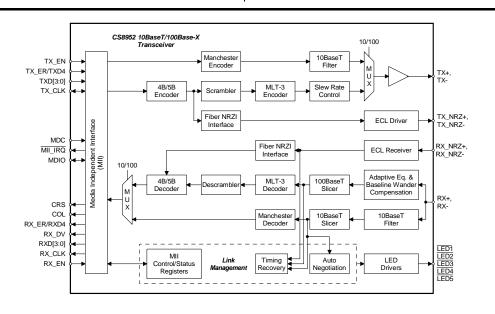

#### 3. FUNCTIONAL DESCRIPTION

The CS8952 is a complete physical-layer transceiver for 100BASE-TX and 10BASE-T applications. It provides a Physical Coding Sub-layer for communication with an external MAC (Media Access Controller). The CS8952 also includes a complete Physical Medium Attachment layer and a 100BASE-TX and 10BASE-T Physical Medium Dependent layer. Additionally, the CS8952 provides a PECL interface to an external optical module for 100BASE-FX applications.

The primary digital interface to the CS8952 is an enhanced IEEE 802.3 Media Independent Interface (MII). The MII supports parallel data transfer, access to the CS8952 Control and Status registers, and several status and control pins. The CS8952's operating modes can be tailored to support a wide variety of applications, including low-latency 100BASE-TX repeaters, switches and MII-based network interface cards.

For 100BASE-TX applications, the digital data interface can be either 4-bit parallel (nibbles) or 5-bit parallel (code-groups). For 10BASE-T applications, the digital data format can be either 4-bit parallel (nibbles) or one-bit serial.

The CS8952 is controlled primarily by configuration registers via the MII Management Interface. Additionally, a number of the most fundamental register bits can be set at power-up and reset time by connecting pull-up or pull-down resistors to external pins.

The CS8952's MII interface is enhanced beyond IEEE requirements by register extensions and the addition of pins for MII\_IRQ, RX\_EN, and ISO-DEF signals. The MII\_IRQ pin provides an inter-

Figure 1. Typical Connection Diagram

rupt signal to the controller when a change of state has occurred in the CS8952, eliminating the need for the system to poll the CS8952 for state changes. The RX\_EN signal allows the receiver outputs to be electrically isolated. The ISODEF pin controls the value of register bit ISOLATE in the Basic Mode Control Register (address 00h) which in turn electrically isolates the CS8952's MII data path.

#### 3.1 Major Operating Modes

The following sections describe the four major operating modes of the CS8952:

- 100BASE-X MII Modes (TX and FX)

- 100BASE-X Repeater Modes

- 10BASE-T MII Mode

- 10BASE-T Serial Mode

The choice of operating speed (10 Mb/s versus 100 Mb/s) is made using the auto-negotiation input pins (AN0, AN1) and/or the auto-negotiation MII registers. The auto-negotiation capability also is used to select a duplex mode (full or half duplex). Both speed and duplex modes can either be forced or negotiated with the far-end link partner.

The digital interface mode (MII, repeater, or 10BASE-T serial) is selected by input pins BPALIGN, BP4B5B and 10BT\_SER as shown in Table 1. Speed and duplex selection are made through the AN[1:0] pins as shown in Table 5.

| 100BASE-X MII 0 0 | 0 |

|-------------------|---|

| 10BASE-T MII 0 0  | 0 |

Table 1.

| Operating Mode  | BPALIGN | BP4B5B | 10BT_SER |

|-----------------|---------|--------|----------|

| 100BASE-X       | 1       | Don't  | 0        |

| Repeater        |         | Care   |          |

|                 | 0       | 1      | 0        |

| 10BASE-T Serial | Don't   | Don't  | 1        |

|                 | Care    | Care   |          |

Table 1.

# 3.1.1 100BASE-X MII Application (TX and FX)

The CS8952 provides an IEEE 802.3-compliant MII interface. Data is transferred across the MII in four-bit parallel (nibble) mode. TX\_CLK and RX\_CLK are nominally 25 MHz for 100BASE-X.

The 100BASE-X mode includes both the TX and FX modes, as determined by pin BPSCR (bypass scrambler), or the BPSCR bit (bit 13) in the Loopback, Bypass, and Receiver Error Mask Register (address 18h). In FX mode, an external optical module is connected to the CS8952 via pins TX\_NRZ+, TX\_NRZ-, RX\_NRZ+, RX\_NRZ-, SIGNAL+, and SIGNAL-. In FX mode, the MLT-3/NRZI conversion blocks and the scrambler/descrambler are bypassed.

#### 3.1.1.1 Symbol Encoding and Decoding

In 100BASE-X modes, 4-bit nibble transmit data is encoded into 5-bit symbols for transmission onto the media as shown in Tables **2** and **3**. The encoding is necessary to allow data and control symbols to be sent consecutively along the same media transparent to the MAC layer. This encoding causes the symbol rate transmitted across the wire (125 symbols/second) to be greater than the actual data rate of the system (100 symbols/second).

| DATA and CONTROL Codes (RX_ER = 0 or TX_ER = 0) |              |              |          |  |  |

|-------------------------------------------------|--------------|--------------|----------|--|--|

| Name                                            | 5-bit Symbol | 4-bit Nibble | Comments |  |  |

| DATA (Note 1)                                   |              |              |          |  |  |

| 0                                               | 11110        | 0000         |          |  |  |

| 1                                               | 01001        | 0001         |          |  |  |

|              | DATA and CONTROL Codes (RX_ER = 0 or TX_ER = 0) |              |                               |  |  |  |  |

|--------------|-------------------------------------------------|--------------|-------------------------------|--|--|--|--|

| Name         | 5-bit Symbol                                    | 4-bit Nibble | Comments                      |  |  |  |  |

| 2            | 10100                                           | 0010         |                               |  |  |  |  |

| 3            | 10101                                           | 0011         |                               |  |  |  |  |

| 4            | 01010                                           | 0100         |                               |  |  |  |  |

| 5            | 01011                                           | 0101         |                               |  |  |  |  |

| 6            | 01110                                           | 0110         |                               |  |  |  |  |

| 7            | 01111                                           | 0111         |                               |  |  |  |  |

| 8            | 10010                                           | 1000         |                               |  |  |  |  |

| 9            | 10011                                           | 1001         |                               |  |  |  |  |

| A            | 10110                                           | 1010         |                               |  |  |  |  |

| В            | 10111                                           | 1011         |                               |  |  |  |  |

| С            | 11010                                           | 1100         |                               |  |  |  |  |

| D            | 11011                                           | 1101         |                               |  |  |  |  |

| E            | 11100                                           | 1110         |                               |  |  |  |  |

| F            | 11101                                           | 1111         |                               |  |  |  |  |

| CONTROL (Not | te <b>2</b> )                                   |              |                               |  |  |  |  |

| I            | 11111                                           | 0101         | IDLE (Note 3)                 |  |  |  |  |

| J            | 11000                                           | 0101         | First Start of Stream Symbol  |  |  |  |  |

| K            | 10001                                           | 0101         | Second Start of Stream Symbol |  |  |  |  |

| Т            | 01101                                           | 0000         | First End of Stream Symbol    |  |  |  |  |

| R            | 00111                                           | 0000         | Second End of Stream Symbol   |  |  |  |  |

1. DATA code groups are indicated by RX\_DV = 1

2. CONTROL code groups are inserted automatically during transmission in response to TX\_EN. They are not generated through any combination of TXD[3:0] or TX\_ER.

3. IDLE is indicated by  $RX_DV = 0$ .

| Table 2. | 4B5B | Symbol | Encoding/Decoding |

|----------|------|--------|-------------------|

|----------|------|--------|-------------------|

|              |              | Code Violations (RX_        | ER = 1 or TX_E                       | R = 1)                                           |

|--------------|--------------|-----------------------------|--------------------------------------|--------------------------------------------------|

| Name         | 5-bit Symbol | Normal Mode 4-bit<br>Nibble | Error Report<br>Mode 4-bit<br>Nibble | Comments                                         |

| CONTROL (Not | te 1)        |                             |                                      |                                                  |

| I            | 11111        | 0000                        | 0000                                 | This portion of the table relates received       |

| J            | 11000        | 0000                        | 0000                                 | 5-bit symbols to received 4-bit nibbles          |

| K            | 10001        | 0000                        | 0000                                 | only. The control code groups may not            |

| Т            | 01101        | 0000                        | 0000                                 | be transmitted in the data portion of the frame. |

| R            | 00111        | 0000                        | 0000                                 | name.                                            |

| CODE VIOLATI | ONS          |                             |                                      |                                                  |

| Н            | 00100        | 0000                        | 0000                                 |                                                  |

| V0           | 00000        | 0110 or 0101 (Note 2)       | 0001                                 |                                                  |

| V1           | 00001        | 0110 or 0101 (Note 2)       | 0111                                 |                                                  |

| V2           | 00010        | 0110 or 0101 (Note 2)       | 1000                                 |                                                  |

| V3           | 00011        | 0110 or 0101 (Note 2)       | 1001                                 |                                                  |

| V4           | 00101        | 0110 or 0101 (Note 2)       | 1010                                 |                                                  |

| V5           | 00110        | 0110 or 0101 (Note 2)       | 1011                                 |                                                  |

|      | Code Violations (RX_ER = 1 or TX_ER = 1) |                             |                                      |          |  |  |  |  |  |

|------|------------------------------------------|-----------------------------|--------------------------------------|----------|--|--|--|--|--|

| Name | 5-bit Symbol                             | Normal Mode 4-bit<br>Nibble | Error Report<br>Mode 4-bit<br>Nibble | Comments |  |  |  |  |  |

| V6   | 01000                                    | 0110 or 0101 (Note 2)       | 1100                                 |          |  |  |  |  |  |

| V7   | 01100                                    | 0110 or 0101 (Note 2)       | 1101                                 |          |  |  |  |  |  |

| V8   | 10000                                    | 0110 or 0101 (Note 2)       | 1110                                 |          |  |  |  |  |  |

| V9   | 11001                                    | 0110 or 0101 (Note 2)       | 1111                                 |          |  |  |  |  |  |

1. CONTROL code groups become violations when found in the data portion of the frame.

Invalid code groups are mapped to 5h unless the Code Error Report select bit in the Loopback, Bypass, and Receiver Error Mask Register (address 18h) is set, in which case invalid code groups are mapped to 6h.

Table 3. 4B5B Code Violation Decoding

#### 3.1.1.2 100 Mb/s Loopback

One of two internal 100BASE-TX loopback modes can be selected. Local loopback redirects the TXD[3:0] input data to RXD[3:0] data outputs through the 4B5B coders and scramblers. Local loopback is selected by asserting pin LPBK, by setting the LPBK bit (bit 14) in the Basic Mode Control Register (address 00h) or by setting bits 8 and 11 in the Loopback, Bypass, and Receiver Error Mask Register (address 18h) as shown in Table **4**.

Remote loopback redirects the analog line interface inputs to the analog line driver outputs. Remote loopback is selected by setting bit 9 in the Loopback, Bypass, and Receiver Error Mask Register (address 18h) as shown in Table **4**.

| Remote<br>Loopback<br>(bit 9) | PMD<br>Loopback<br>(bit 8) | Function                      |

|-------------------------------|----------------------------|-------------------------------|

| 0                             | 0                          | No Loopback                   |

| 0                             | 1                          | Local Loopback (toward MII)   |

| 1                             | 0                          | Remote Loopback (toward line) |

| 1                             | 1                          | Operation is undefined        |

|                               |                            | Tabla 1                       |

Table 4.

When changing between local and non-loopback modes, the data on RXD[3:0] will be undefined for approximately 330 µs.

#### 3.1.2 100BASE-X Repeater Application

The CS8952 provides two low latency modes for repeater applications. These are selected by asserting either pin BPALIGN or BP4B5B. Both pins have the effect of bypassing the 4B5B encoder and decoder. Bypassing the coders decreases latency, and uses a 5-bit wide parallel code group interface on pins RXD[4:0] and TXD[4:0] instead of the 4bit wide MII nibble interface on pins RXD[3:0] and TXD[3:0]. In repeater mode, pin RX\_ER is redefined as the fifth receive data bit (RXD4), and pin TX\_ER is redefined as the fifth transmit data bit (TXD4).

BPALIGN can also be selected by setting bit 12 in Loopback, Bypass, and Receiver Error Mask Register (address 18h). BP4B5B can be selected by setting bit 14 of the same register.

Pin BPALIGN causes more of the CS8952 to be bypassed than the BP4B5B pin. BPALIGN also bypasses the scrambler/descrambler, and the NRZI to NRZ converters (see Figure 1). Also, for repeater applications, pin REPEATER should be asserted to redefine the function of the CRS (carrier sense) pin. The REPEATER function may also be invoked by setting bit 12 in the PCS Sublayer Configuration Register (address 17h).

For repeater applications, the RX\_EN pin can be used to gate the receive data pins (RXD[4:0],

RX\_CLK, RX\_DV, COL, and CRS) onto a shared, external repeater system bus.

#### 3.1.3 10BASE-T MII Application

The digital interface used in this mode is the same as that used in the 100BASE-X MII mode except that TX\_CLK and RX\_CLK are nominally 2.5 MHz.

The CS8952 includes a full-featured 10BASE-T interface, as described in the following sections.

#### 3.1.3.1 Full and Half Duplex operation

The 10BASE-T function supports full and half duplex operation as determined by pins AN[1:0] and/or the corresponding MII register bits. (See Table **5**).

#### 3.1.3.2 Collision Detection

If half duplex operation is selected, the CS8952 detects a 10BASE-T collision whenever the receiver and transmitter are active simultaneously. When a collision is present, the collision is reported on pin COL. Collision detection is undefined for full-duplex operation.

#### 3.1.3.3 Jabber

The jabber timer monitors the transmitter and disables the transmission if the transmitter is active for greater than approximately 105 ms. The transmitter stays disabled until approximately 406 ms after the internal transmit request is no longer enabled.

#### 3.1.3.4 Link Pulses

To prevent disruption of network operation due to a faulty link segment, the CS8952 continually monitors the 10BASE-T receive pair (RXD+ and RXD-) for packets and link pulses. After each packet or link pulse is received, an internal Link-Loss timer is started. As long as a packet or link pulse is received before the Link-Loss timer finishes (between 50 and 100 ms), the CS8952 maintains normal operation. If no receive activity is detected, the CS8952 disables packet transmission to prevent "blind" transmissions onto the network (link pulses are still sent while packet transmission is disabled). To reactivate transmission, the receiver must detect a single packet (the packet itself is ignored), or two normal link pulses separated by more than 6 ms and no more than 50 ms.

The CS8952 automatically checks the polarity of the receive half of the twisted pair cable. To detect a reversed pair, the receiver examines received link pulses and the End-of-Frame (EOF) sequence of incoming packets. If it detects at least one reversed link pulse and at least four frames in a row with negative polarity after the EOF, the receive pair is considered reversed. If the polarity is reversed and bit 1 of the 10BASE-T Configuration Register (address 1Ch), is set, the CS8952 automatically corrects a reversal.

In the absence of transmit packets, the transmitter generates link pulses in accordance with Section 14.2.1.1 of the Ethernet standard. Transmitted link pulses are positive pulses, one bit time wide, typically generated at a rate of one every 16 ms. The 16 ms timer also starts whenever the transmitter completes an End-of-Frame (EOF) sequence. Thus, a link pulse will be generated 16 ms after an EOF unless there is another transmitted packet.

#### 3.1.3.5 Receiver Squelch

The 10BASE-T squelch circuit determines when valid data is present on the RXD+/RXD- pair. Incoming signals passing through the receive filter are tested by the squelch circuit. Any signal with amplitude less than the squelch threshold (either positive or negative, depending on polarity) is rejected.

#### 3.1.3.6 10BASE-T Loopback

When Loopback is selected, the TXD[3:0] pins are looped back into the RXD[3:0] pins through the

Manchester Encoder and Decoder. Selection is made via:

- setting bit 14 in the Basic Mode Control Register (address 00h) or

- setting bits 8 and 11 in the Loopback, Bypass, and Receiver Error Mask Register (address 18h) or

- asserting the LPBK pin.

#### 3.1.3.7 Carrier Detection

The carrier detect circuit informs the MAC that valid receive data is present by asserting the Carrier Sense signal (CRS) as soon it detects a valid bit pattern (1010b or 0101b for 10BASE-T). During normal packet reception, CRS remains asserted while the frame is being received, and is de-asserted within 2.3 bit times after the last low-to-high transition of the End-of-Frame (EOF) sequence. Whenever the receiver is idle (no receive activity), CRS is de-asserted.

#### 3.1.4 10BASE-T Serial Application

This mode is selected when pin 10BT\_SERis asserted during power-up or reset, and operates similar to the 10BASE\_T MII mode except that data is transferred serially on pins RXD0 and TXD0 using a 10 MHz RX\_CLK and TX\_CLK. Receive data is framed by CRS rather than RX\_DV.

#### 3.2 Auto-Negotiation

The CS8952 supports auto-negotiation, which is the mechanism that allows the two devices on either end of an Ethernet link segment to share information and automatically configure both devices for maximum performance. When configured for auto-negotiation, the CS8952 will detect and automatically operate full-duplex at 100 Mb/s if the device on the other end of the link segment also supports full-duplex, 100 Mb/s operation, and auto-negotiation. The CS8952 auto-negotiation capability is fully compliant with the relevant portions of section 28 of the IEEE 802.3u standard.

The CS8952 can auto-negotiate both operating speed (10 versus 100 Mb/s), duplex mode (half duplex versus full duplex), and flow control (pause frames), or alternatively can be set not to negotiate. At power-up and reset times, the auto-negotiation mode is selected via the auto-negotiation input pins (AN[1:0]). This selection can later be changed using the Auto-Negotiation Advertisement Register (address 04h).

Pins AN[1:0] are three level inputs, and have the function shown in Table **5**.

| AN1      | AN0      | Forced/<br>Auto | Speed<br>(Mb/s) | Full/Half<br>Duplex |

|----------|----------|-----------------|-----------------|---------------------|

| Low      | Floating | Forced          | 10              | Half                |

| High     | Floating | Forced          | 10              | Full                |

| Floating | Low      | Forced          | 100             | Half                |

| Floating | High     | Forced          | 100             | Full                |

| Floating | Floating | Auto-Neg        | 100/10          | Full/Half           |

| Low      | Low      | Auto-Neg        | 10              | Half                |

| Low      | High     | Auto-Neg        | 10              | Full                |

| High     | Low      | Auto-Neg        | 100             | Half                |

| High     | High     | Auto-Neg        | 100             | Full                |

|          |          | Table 5.        |                 |                     |

Auto-Negotiation encapsulates information within a burst of closely spaced Link Integrity Test Pulses, referred to as a Fast Link Pulse (FLP) Burst. The FLP Burst consists of a series of Link Integrity Pulses which form an alternating clock / data sequence. Extraction of the data bits from the FLP Burst yields a Link Code Word which identifies the capability of the remote device.

In order to support legacy 10 and 100 Mb/s devices, the CS8952 also supports parallel detection. In parallel detection, the CS8952 monitors activity on the media to determine the capability of the link partner even without auto-negotiation having occurred.

#### 3.3 Reset Operation

Reset occurs in response to six different conditions:

- There is a chip-wide reset whenever the RE-SET pin is high for at least 200 ns. During a chip-wide reset, all circuitry and registers in the CS8952 are reset.

- 2) When power is applied, the CS8952 maintains reset until the voltage at the VDD supply pins reaches approximately 3.6 V. The CS8952 comes out of reset once VDD is greater than approximately 3.6 V and the crystal oscillator has stabilized.

- 3) There is a chip-wide reset whenever the RE-

SET bit (bit 15 of the Basic Mode Control Register (address 00h)) is set.

- Digital circuitry is reset whenever bit 0 of the PCS Sub-Layer Configuration Register (address 17h) is set. Analog circuitry is unaffected.

- 5) Analog circuitry is reset and recalibrated whenever the CS8952 enters or exits the powerdown state, as requested by pin PWRDN.

- 6) Analog circuitry is reset and recalibrated whenever the CS8952 changes between 10 Mb/s and 100 Mb/s modes.

After a reset, the CS8952 latches the signals on various input pins in order to initialize key registers and goes through a self configuration. This includes calibrating on-chip analog circuitry. Time required for the reset calibration is typically 40 ms. External circuitry may access registers internal to the CS8952 during this time. Reset and calibration complete is indicated when bit 15 of the Basic Mode Control Register (address 00h) is clear.

### 3.4 LED Indicators

The LEDx, SPD100, and SPD10 output pins provide status information that can be used to drive LEDs or can be used as inputs to external control circuitry. Indication options include: receive activity, transmit activity, collision, carrier sense, polarity OK, descrambler synchronization status, autonegotiation status, speed (10 vs. 100), and duplex mode.

# 4. MEDIA INDEPENDENT INTERFACE (MII)

The Media Independent Interface (MII) provides a simple interconnect to an external Media Access Controller (MAC). This connection may be chip to chip, motherboard to daughterboard, or a connection between two assemblies attached by a limited length of shielded cable and an appropriate connector.

The MII interface uses the following pins:

#### STATUS Pins

- COL Collision indication, valid only for half duplex modes.

- CRS Carrier Sense indication

#### SERIAL MANAGEMENT Pins

- MDIO a bi-directional serial data path

- MDC clock for MDIO (16.7 MHz max)

- <u>MII\_IRQ</u> Interrupt indicating change in the Interrupt Status Register (address 11h)

#### **RECEIVE DATA Pins**

- RXD[3:0] Parallel data output path

- RX\_CLK Recovered clock output

- RX\_DV Indicates when receive data is present and valid

- RX\_ER Indicates presence of error in received data

- RX\_EN Can be used to tri-state receiver output pins

#### TRANSMIT DATA Pins

- TXD[3:0] Parallel data input path

- TX\_CLK Transmit clock

- TX\_EN Indicates when transmit data is present and valid

- TX\_ER Request to transmit a 100BASE-T HALT symbol, ignored for 10BASE-T operation.

The interface uses TTL signal levels, which are compatible with devices operating at a nominal supply voltage of either 5.0 or 3.3 volts. It is capable of supporting either 10 Mb/s or 100 Mb/s data rates transparently. That is, all signaling remains identical at either data rate; only the nominal clock frequency is changed.

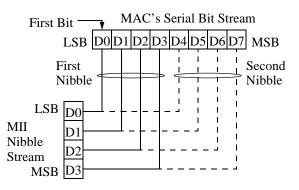

#### 4.1 MII Frame Structure

Data frames transmitted through the MII have the following format:

| Preamble  | Start of  | Data | End of    |

|-----------|-----------|------|-----------|

| (7 Bytes) | Frame     |      | Frame     |

|           | Delimiter |      | Delimiter |

|           | (1 Byte)  |      |           |

Each frame is preceded by an inter-frame gap. The inter-frame gap is an unspecified time during which no data activity occurs on the media as indicated by the de-assertion of CRS for the receive path and TX\_EN for the transmit path.

The Preamble consists of seven bytes of 10101010.

The Start of Frame Delimiter consists of a single byte of 10101011.

Data may be any number of bytes.

The End of Frame Delimiter is conveyed by the deassertion of RX\_DV and TX\_EN for receive and transmit paths, respectively.

Transmission and/or reception of each byte of data is done one nibble at a time in the following order:

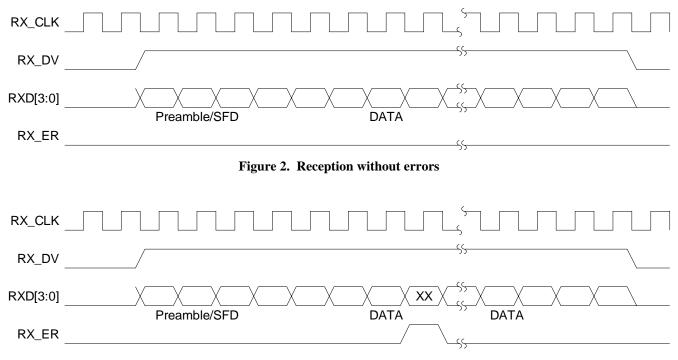

#### 4.2 MII Receive Data

The presence of recovered data on the RXD[3:0] bus is indicated by the assertion of RX\_DV. RX\_DV will remain asserted from the beginning of the preamble (or Start of Frame Delimiter if preamble is not used) to the End of Frame Delimiter. Once RX\_DV is asserted, valid data will be driven

onto RXD[3:0] synchronously with respect to RX\_CLK.

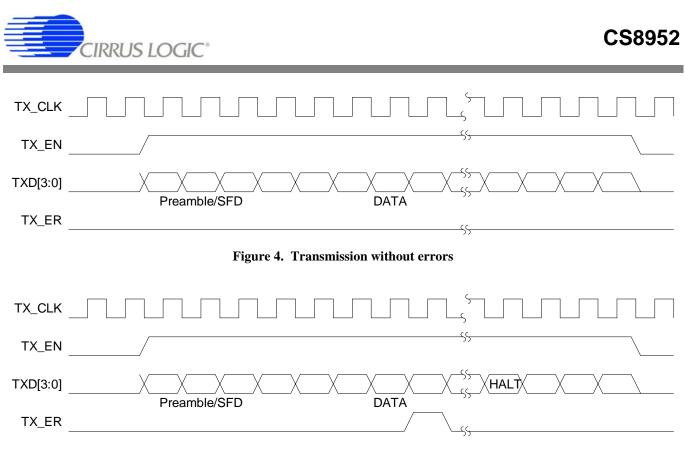

Receive errors are indicated during frame reception by the assertion of RX\_ER. It indicates that an error was detected somewhere in the frame currently being transferred across the MII. RX\_ER will transition synchronously with respect to the RX\_CLK, and will be held high for one cycle for each error received. It is up to the MAC to ensure that a CRC error is detected in that frame by the Logical Link Control. Figure **2** illustrates reception without errors, and Figure **3** illustrates reception with errors.

#### 4.3 MII Transmit Data

TX\_EN is used by the MAC to signal to the CS8952 that valid nibbles of data are being presented across the MII via TXD[3:0]. TX\_EN must be asserted synchronously with the first nibble of preamble, and must remain asserted as long as valid data is being presented to the MII.

TX\_EN must be de-asserted within one TX\_CLK cycle after the last nibble of data (CRC) has been

presented to the CS8952. When TX\_EN is not asserted, data on TXD[3:0] is ignored.

Transmit errors should be signaled by the MAC by asserting TX\_ER for one or more TX\_CLK cycles. TX\_ER must be synchronous with TX\_CLK. This will cause the CS8952 to replace the nibble with a HALT symbol in the frame being transmitted. This invalid data will be detected by the receiving PHY and flagged as a bad frame. Figure 4 illustrates transmission without errors, and Figure 5 illustrates transmission with errors.

#### 4.4 MII Management Interface

The CS8952 provides an enhanced IEEE 802.3 MII Management Interface. The interface consists of three signals: a bi-directional serial data line (MDIO), a data clock (MDC), and an optional interrupt signal (MII\_IRQ). The Management Interface can be used to access status and control registers internal to the CS8952. The CS8952 implements an extended set of 16-bit MII registers. Eight of the registers are defined by the IEEE 802.3

Figure 3. Reception with errors

Figure 5. Transmission with errors

specification, while the remaining registers provide enhanced monitoring and control capabilities.

As many as 31 devices may share a single Management Interface. A unique five-bit PHY address is associated with each device, with all devices responding to PHY address 00000. The CS8952 determines its PHY address at power-up or reset through the PHYAD[4:0] pins.

#### 4.5 MII Management Frame Structure

Frames transmitted through the MII Management Interface have the following format (Table 6): When the management interface is idle, the MDIO signal will be tri-stated, and the MAC is required to keep MDIO pulled to a logic ONE.

At the beginning of each transaction, the MAC will typically send a sequence of 32 contiguous logic ONE bits on MDIO with 32 corresponding clock cycles on MDC to provide the CS8952 with a pattern that it can use to establish synchronization. Optionally, the CS8952 may be configured to operate without the preamble through bit 9 of the PCS Sub-Layer Configuration Register (address 17h).

| Preamble  | Start of | Opcode   | PHY      | Register | Turnaround | Data      | Idle |

|-----------|----------|----------|----------|----------|------------|-----------|------|

| (32 bits) | Frame    | (2 bits) | Address  | Address  | (2 bits)   | (16 bits) |      |

|           | (2 bits) |          | (5 bits) | (5 bits) |            |           |      |

Table 6. Format for Frame Transmitted through the MII Management Interface

The Start of Frame is indicated by a 01 bit pattern.

A read transaction is indicated by an Opcode of 10 and a write by 01.

The PHY Address is five bits, with the most significant bit sent first. If the PHY address included in the frame is not 00000 or does not match the PHY-AD field of the Self Status Register (address 19h), the rest of the frame is ignored.

The register address is five bits, with the most significant bit sent first, and indicates the CS8952 register to be written to/read from.

The Turnaround time is a two bit time spacing between when the MAC drives the last register address bit onto MDIO and the data field of a management frame in order to avoid contention during a read transaction. For a read transaction, the MAC should tri-state the MDIO pin beginning on the first bit time, and the CS8952 will begin driving the MDIO signal to a logic ZERO during the second bit time. During write transactions, since the MDIO direction does not need to be reversed, the MAC will drive the MDIO to a logic ONE for the first bit time and a logic ZERO for the second.

The data field is always 16 bits in length, with the most significant bit sent first.

#### 5. CONFIGURATION

The CS8952 can be configured in a variety of ways. All control and status information can be accessed via the MII Serial Management Interface. Additionally, many configuration options can be set at power-up or reset times via individual control lines. Some configuration capabilities are available at any time via individual control lines.

#### 5.1 Configuration At Power-up/Reset

#### Time

At power-up and reset time, the following pins are used to configure the CS8952.

| Pin Name    | Function                                                                                 |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------|--|--|--|--|

| 10BT_SER    | Select 10BASE-T serial mode                                                              |  |  |  |  |

| AN[1:0]     | Select auto-negotiation mode                                                             |  |  |  |  |

| BP4B5B      | Bypass 4B5B coders                                                                       |  |  |  |  |

| BPALIGN     | Bypass 4B5B coders and scramblers                                                        |  |  |  |  |

| BPSCR       | Bypass scramblers, enter FX mode                                                         |  |  |  |  |

| ISODEF      | Electrically isolate MII after reset                                                     |  |  |  |  |

| LPSTRT      | Start in low power mode                                                                  |  |  |  |  |

| PHYAD[4:0]  | Set MII PHY address                                                                      |  |  |  |  |

| REPEATER    | Control definition of CRS pin, enable<br>carrier integrity monitor and SQE func-<br>tion |  |  |  |  |

| MII_DRV     | Set MII driver strength                                                                  |  |  |  |  |

| ТСМ         | Set TX_CLK mode                                                                          |  |  |  |  |

| TXSLEW[1:0] | Set 100BASE-TX transmitter output slew rate                                              |  |  |  |  |

#### 5.2 Configuration Via Control Pins

The following pins are for dedicated control signals and can be used at any time to configure the CS8952.

| Pin Name | Function              |

|----------|-----------------------|

| LPBK     | Enter loopback mode   |

| PWRDN    | Enter power-down mode |

| RESET    | Reset                 |

#### 5.3 Configuration via the MII

The CS8952 supports configuration by software control through the use of 16-bit configuration and status registers accessed via the MDIO/MDC pins (MII Management Interface). The first seven registers are defined by the IEEE 802.3 specification. Additional registers extend the register set to provide enhanced monitoring and control capabilities.

#### 6. CS8952 REGISTERS

The CS8952 register set is comprised of the 16-bit status and control registers described below. A detailed description each register follows.

| Register Address | Description                                       | Туре       |

|------------------|---------------------------------------------------|------------|

| 0h               | Basic Mode Control Register                       | Read/Write |

| 1h               | Basic Mode Status Register                        | Read-Only  |

| 2h               | PHY Identifier #1                                 | Read-Only  |

| 3h               | PHY Identifier #2                                 | Read-Only  |

| 4h               | Auto-Negotiation Advertisement Register           | Read/Write |

| 5h               | Auto-Negotiation Link Partner Ability Register    | Read-Only  |

| 6h               | Auto-Negotiation Expansion Register               | Read-Only  |

| 7h               | Auto-Negotiation Next Page Transmit Register      | Read/Write |

| 8h through Fh    | Reserved by IEEE 802.3 Working Group              | -          |

| 10h              | Interrupt Mask Register                           | Read/Write |

| 11h              | Interrupt Status Register                         | Read-Only  |

| 12h              | Disconnect Count Register                         | Read-Only  |

| 13h              | False Carrier Count Register                      | Read-Only  |

| 14h              | Scrambler Key Initialization Register             | Read/Write |

| 15h              | Receive Error Count Register                      | Read-Only  |

| 16h              | Descrambler Key Initialization Register           | Read/Write |

| 17h              | PCS Sub-Layer Configuration Register              | Read/Write |

| 18h              | Loopback, Bypass and Receiver Error Mask Register | Read/Write |

| 19h              | Self-Status Register                              | Read/Write |

| 1Ah              | Reserved                                          | -          |

| 1Bh              | 10BASE-T Status Register                          | Read-Only  |

| 1Ch              | 10BASE-T Configuration Register                   | Read/Write |

| 1Dh through 1Fh  | Reserved                                          | -          |

#### 6.1 Basic Mode Control Register - Address 00h

| 1       | 15           | 14        | 13                 | 12                                                                                              | 11                                                                              | 10                                                                                         | 9                                                                                | 8                                                                         |

|---------|--------------|-----------|--------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|         | ware<br>eset | Loopback  | Speed<br>Selection | Auto-Neg<br>Enable                                                                              | Power Down                                                                      | Isolate                                                                                    | Restart<br>Auto-Neg                                                              | Duplex Mode                                                               |

|         | 7            | 6         | 5                  | 4                                                                                               | 3                                                                               | 2                                                                                          | 1                                                                                | 0                                                                         |

| Collisi | on Test      |           |                    |                                                                                                 | Reserved                                                                        |                                                                                            |                                                                                  |                                                                           |

| BIT     |              | NAME      | TYPE               | RESET                                                                                           |                                                                                 | DES                                                                                        | CRIPTION                                                                         |                                                                           |

| 15      |              | re Reset  | Read/Set           | 0                                                                                               | Setting thi                                                                     |                                                                                            |                                                                                  | eset. All status                                                          |

|         |              |           |                    |                                                                                                 | and contro<br>and the ar<br>Act-Once<br>calibration<br>This bit wi              | bl registers are<br>halog circuitry<br>bit which is clo<br>have comple<br>Il also be set a | e set to their de<br>is re-calibrated<br>eared once the<br>ted.                  | efault states,<br>d. This bit is an<br>e reset and re-<br>hile the analog |

| 14      | Loopba       | ack       | Read/Write         | 0                                                                                               | When set,<br>mode. Any<br>returned of<br>entered re<br>operation<br>This bit wi | y data sent on<br>on the receive<br>gardless of w<br>has been con<br>Il be set upon        | hether 10 Mb/<br>figured.<br>the assertion                                       | lata path is<br>pback mode is<br>s or 100 Mb/s                            |

| 13      | Speed        | Selection | Read/Write         | If auto-negotiation<br>is enabled via th<br>AN[1:0] pins, res<br>to 1; otherwise,<br>reset to 0 | e CS8952 fo                                                                     | or 100 Mb/s op<br>uration at 10 M                                                          |                                                                                  | nfigures the<br>ing this bit sets<br>t 12 is set, this                    |

| 12      | Auto-N       | eg Enable | Read/Write         | If auto-negotiation<br>is enabled via th<br>AN[1:0] pins, res<br>to 1; otherwise,<br>reset to 0 | e When this<br>et the link co<br>mined by                                       | bit is set, bits<br>onfiguration. Tl                                                       | 13 and 8 have<br>he link configu<br>tiation process                              | iation process.<br>e no affect on<br>ration is deter-<br>s. Clearing this |