# PI310MC-DR 300DPI CIS Two Level Digital Output Module Engineering Data Sheet

## **Key Features**

- Light source, lens, and sensor are integrated into a single module

- 11.8 dpm resolution, 89 mm scanning length

- Up to 423 µsec/line scanning speed, with 2.5 MHz pixel rate (See Table 3, Note 3.)

- Wide dynamic range

- Two-Level Tracking Digital Output ("Dynamic Threshold Digitizer")

- Standard Yellow-Green light source (Other colors are available)

- Compact size

15 mm x 25.6 mm x 102 mm

- Low power

- Light weight

### **General Description**

The PI310MC-DR is a contact image sensor, CIS, module with an additional on board circuit that digitizes the analog pixels from the CIS image sensor to a "background-tracking", two-level digital output signal. It is based on the PI305M-A6 CIS module manufactured by PIC, but with a shorter read length of 89 mm. Hence, its performance is equivalent to the PI305M-A6 that uses MOS image sensor technology to gains its high-speed performance and high sensitivity. The PI310MC-DR is suitable for scanning documents with widths up to 89 mm and with resolution of 11.8 dots per millimeter. It has broad applications, but was specially designed for the following areas:

- Where data compression is required, such as in data transmissions.

- Where component pin-out count must be kept to a minimum.

The background-tracking-digitizing circuits in the PI310MC-DR have been referred to as the "dynamic threshold" two-level A/D converter. For the purpose of describing the module's characteristics this "dynamic threshold" processing circuit shall herein be referred to as the "tracking digitizer".

## **Module Description**

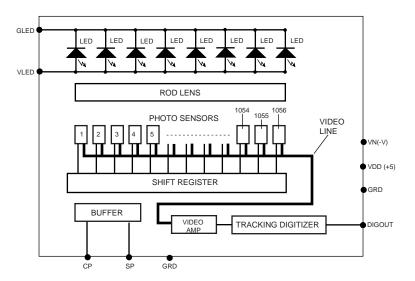

Figure 1. PI310MC-DR Module Block Diagram.

The PI310MC-DR module consists of 11 sensors that are cascaded to provide 1056 photo-detectors with their associated multiplex switches, and a digital shift register that controls its sequential readout. Mounted in the module is a one-to-one graded-indexed micro lens array that focuses the scanned documents to image onto its sensing plane. A buffer amplifier amplifies the video pixels from the image sensors and passes them to the analog digitizing circuit, where video pixels are converted to a digital signal and outputted from the module. See Figure 1, the block diagram of the PI310MC-DR module.

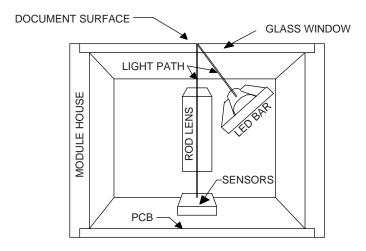

Illumination is by means of an integrated LED light source. All components are housed in a small plastic housing which has a cover glass that acts as the focal point for the object being scanned and protects the imaging array, micro lens assembly, and LED light source from dust. The pictorial of PI310MC-DR cross section is shown in Figure 2.

Figure 2. PI310MC-DR Module Cross Section

I/O to the module is a 8-pin flex cable connector (See I/O Connector, under Specifications) located on one end of the module. It is on the top of the module with the glass window facing down and it is on the opposite side of the module. See the Mechanical Housing under Mechanical Structure.

## **Circuit Description and Operation**

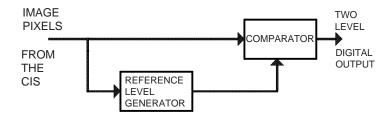

Figure 3 depicts a simplified block diagram of the analog tracking digitizer. Fundamentally, the tracking digitizer transforms the signal output from a CIS module existing on the

FIGURE 3. ANALOG SIGNAL REFERENCE GENERATOR AND A SINGLE BIT COMPARATOR

market today. It takes the analog signal from the CIS section of PI310MC-DR and derives a tracking background reference signal. This reference is then compared against the output signals from the CIS section. The resulting signal by comparison produces a two-level digital signal that is high when the pixel signal is brighter than the background and remains at zero as long as the signal is darker than the background signal.

Figure 1, PI310MC-DR block diagram depicts the two basic circuits, the CIS (image sensors and video amplifier) and the tracking digitizer. In the CIS section, the module has 11 serially concatenated PI3012A image sensors. Accordingly, the image sensors will span one scanning-read line width that is 11 sensor times 96 pixel elements/sensor, or 1056 pixel elements.

In operation, the CIS module produces the analog image pixel signals (video) that are proportional to the exposure on the corresponding document picture element. The video is then inputted to the tracking digitizer. In turn, the digitizer converts the analog image pixels to digital image pixels. The analog image pixels, at test point TV, are separated into two signals. One generates the reference signal and the other remains unmodified. The unmodified signal (image pixels) are applied to one input of the comparator. The reference signal is applied to the second input of the comparator. The results of the comparison are the digital image pixels. This digital output is produced in two levels, determined by the difference between the background reference signal and the analog image pixels. A digital pixel output of value "one" represents the analog image pixel that is brighter than the background and digital pixel level of value "zero" represents the image pixel that is darker than background.

## **Specifications**

## I/O Connector

The table of pins and their functions are listed in Table I, Pin Configuration.

| Pin Number | Symbol          | Names and Functions                |

|------------|-----------------|------------------------------------|

| 1          | DIGOUT          | Digital Video Output               |

| 2          | Vdd (+5 V)      | Ground; 0 V                        |

| 3          | Vn (-10 to -5V) | Negative power supply              |

| 4          | SP              | Start Pulse for the shift register |

| 5          | GRD             | Ground; 0 V                        |

| 6          | CLOCK           | Clock for the shift register       |

| 7          | GLED            | Return for the LED light source    |

| 8          | VLED            | Power in for the LED light         |

|            |                 | source.                            |

Table 1. Pin configuration

The connector is a 8-pin 1-mm surface mount flex input, Molex 52207-0890.

## Inputs:

There are five inputs:

- Clock is on Pin 6 of the I/O Connector. This is main clock input into the CIS Module.

- SP is on Pin 4. This is the start clock input to the CIS Module.

- VDD is on Pin 2. This is a + 5 Volts supply.

- VN is on Pin 3. This is a (-10 to -5) Volts supply.

- VLED is on Pin 8. This is a +24 Volts supply for the LED light source.

Note: Power return for the LED light source is GLED on Pin 7 and the ground return for the CIS modules is pin 5.

## Video Output:

DIGOUT is on pin 1 of the I/O connector. This is the digital video output from the CIS module. Reflection off the dark target produces a digital signal of "0" level, while the white reflection off the white target produces a digital level of "one". The amplitudes of the white and dark are listed in the table below:

Electro-Optical Characteristics (25° C)

Table 2. Electro-optical characteristics at 25° C.

| Parameter                 | Symbol              | Parameter | Units    | Note                      |

|---------------------------|---------------------|-----------|----------|---------------------------|

| Number of photo detectors |                     | 1056      | elements |                           |

| Pixel to pixel spacing    |                     | 84.7      | mm       |                           |

| Line scanning rate        | Tint <sup>(1)</sup> | 528       | µsec     | @ 2.0 MHz clock frequency |

| Clock frequency           | f                   | 2.0       | MHz      |                           |

| Bright output             | Digital Video       | >3.2      | Volts    |                           |

| Dark output               | Output Signal       | <0.8      | Volts    |                           |

(1) The Tint is specified with a 2.0 MHz clock frequency. In operation the time constants in the reference generator is set to match the initial exposure time, hence the time constant will determine the optimum integration time. Note the integration time is also a function of the clock frequency. Accordingly, it is highly recommended that the parameters be factory adjusted for the specific application.

Table 3. Recommended Operating Conditions (25 °C)

| Item                          | Symbol | Min     | Mean              | Max | Units |

|-------------------------------|--------|---------|-------------------|-----|-------|

| Power Supply                  | Vdd    |         | 5.0               |     | V     |

|                               | Vn.    | -10     |                   | -5  | V     |

|                               | VLED   |         | 24 <sup>(1)</sup> |     | V     |

|                               | ldd    |         | 25                |     | mA    |

|                               | lvn    |         | 10                |     | mA    |

|                               | ILED   |         | 85                |     | mA    |

| Input voltage at digital high | Vih    | Vdd-1.0 | Vdd5              | Vdd | V     |

| Input voltage at digital low  | Vil    | 0       |                   | 0.8 | V     |

| Clock frequency               | f      |         |                   | 2.5 | MHz   |

| Clock pulse high duty cycle   |        | 25      |                   |     | %     |

Table 3. (Continued)

| Clock pulse high duration | Clock | 100 <sup>(2)</sup> |    |    | ns |

|---------------------------|-------|--------------------|----|----|----|

| Integration time          | Tint  | 0.423 (3)          |    |    | ms |

| Operating temperature     | Тор   |                    | 25 | 50 | °C |

#### Note:

- (1) VLED sources are also available in 5 Volts.

- (2) Clock pulse high is specified at 2.5 MHz at 25% duty.

- (3) The Tint is specified with a 2.5 MHz clock frequency. In operation the time constant in the reference generator is set to match the initial exposure time, hence the time constant will determine the optimum integration time. Accordingly, it is highly recommended that the parameters be factory adjusted for the specific application.

## **Switching Characteristics (25°C)**

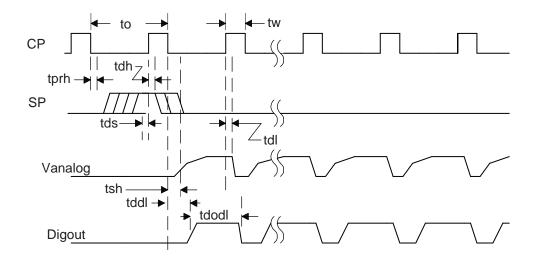

The switching characteristics for the I/O clocks are shown in Figure 4, Module Timing Diagram. The timing parametric values and their symbols are given in the Table 4.

FIGURE 4. Module Timing Diagram

Table 4. Switching Parameter and Timing Symbol Definition

|                                       | Symbol | Min. | Typical | Max. | Units |

|---------------------------------------|--------|------|---------|------|-------|

| Clock cycle time                      | to     |      | 0.50    |      | μs    |

| Clock pulse width                     | tw     | 100  |         |      | ns    |

| Clock duty cycle                      |        | 25   |         | 50   | %     |

| Prohibit crossing time of Start Pulse | tprh   | 15   |         |      | ns    |

| Data setup time                       | tds    | 20   |         |      | ns    |

| Data hold time                        | tdh    | 20   |         |      | ns    |

| Signal delay time                     | tdl    | 50   |         |      | ns    |

| Signal settling time                  | tsh    | 120  |         |      | ns    |

| Digital Signal<br>Delay               | tddl   |      | 60      |      | ns    |

| Digital Signal<br>Off Delay           | tdodl  |      | 300     |      | ns    |

Table 5 Absolute Maximum Rating:

| Parameter                      | Symbols | Maximum<br>Rating | Units |

|--------------------------------|---------|-------------------|-------|

| Power supply voltage           | Vdd     | 10                | V     |

|                                | Idd     | 50                | mA    |

|                                | Vn      | -15               | V     |

|                                | Ivn     | 30                | mA    |

|                                | VLED    | 26                | V     |

|                                | ILED    | 100               | mA    |

| Input clock pulse (high level) | Vih     | Vdd – 0.5         | V     |

| Input clock pulse (low         | Vil     | -0.8              | V     |

## Table 6 Operating Environment

| Operating temperature | Тор  | 0 to 50    | °C |

|-----------------------|------|------------|----|

| Operating humidity    | Нор  | 10 to 85   | %  |

| Storage temperature   | Tstg | -25 to +75 | °C |

| Storage humidity      | Hstg | 5 to 95    | %  |

## **Setup and Adjustments**

## The Clock Rate and Integration Time

The following values were factory set for a specific application. See note 1 under Table 2, Electro-optical characteristics at 25° C.

The clock frequency was set to 2.4 MHz.

The total integration time was set to 560 µsec.

## The Required Power

The required power is slightly greater than the specified values in Table 3.

Circuit Power:

Positive Supply: +5 Volts @ 25 mA

Negative Supply: -10 Volts @ 10 mA

LED Power: +24 Volts @ 90 mA

## Adjustments

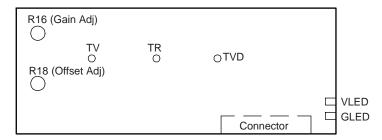

General Location of Test, Adjustment and Monitor Points

BACK SIDE OF THE PCB AS VIEWED ON MODULE WITH THE GLASS WINDOW FACING DOWN.

FIGURE 5. PI310MC-DR PCB Monitor & Test Points

Figure 5, PI310MC-DR PCB MONITOR AND TEST POINTS, shows the pictorial layout of the controls and the tests points. These adjustment potentiometers and the test points are shown relative to the connector and to the output pads for LED light power. This is a bird's eye view of the PCB's backside with the glass window of the module facing down on the documents.

Test point labeled TV is for the analog image pixels, just as it is produced at the output of the CIS array section, and prior to its entry into the tracking digitizer circuit.

Test point labeled TR is the output of the tracking reference level from the tracking digitizer circuit.

Test point labeled TVD is the digital output from the comparator.

Offset adjust, R18, is a screw driver adjustment potentiometer that is accessed through adjustment hole as viewed in figure 5.

Gain adjust, R16, is a screw driver adjustment potentiometer that is accessed through the hole as it is viewed in figure 5.

## There are only two adjustments:

These adjustments will be pre-set to the customer's specific application at the factory, therefore, in general will not require trimming by the user. Test point TV is probed with a scope to monitor the analog image pixel levels. The probe should be grounded as close to the CIS module as possible. If possibly right on the ground input lead, pin 5, of the I/O connector.

Analog Zero signal adjust (OFFSET ADJ) as it is shown in Figure 5. This pot is adjusted to place the dark level of the analog image pixel signal to approximately –0.9 to –0.7 Volts. Normally adjusted with intended targets.

Analog Gain adjust, "GAIN", is adjusted greater than 2.0 and less then 3.5 Volts with the CIS imaged on a standard white target similar to the standard white copy or typing paper.

## **Mechanical Structure**

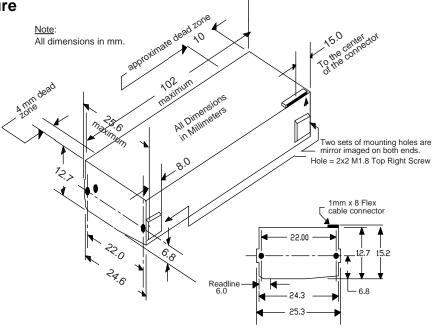

FIGURE 6. Mechanical Structure

Figure 6 is a pictorial of the PI310MC-DR. It illustrates the mechanical dimensions of the housing and its mounting hole locations. The "dead zones" represent the package extremes that are outside the image sensor active area.