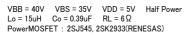

## STEREO 60W-100W DIGITAL AUDIO POWER AMPLIFIER CONTROLLER

## ■Outline

YDA136 (D-60) is a high efficient and high output digital audio power amplifier controller IC.

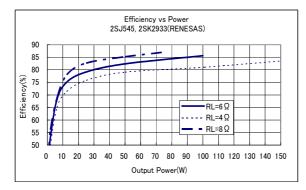

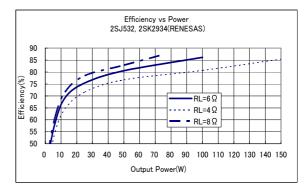

By combining a general purpose PowerMOSFET (hereafter called PowerMOSFET) which is connected with YDA136 and BTL, it is able to compose a high efficient audio power amplifier such as 60Wx2ch (Supplied voltage=32V, RL= $6\Omega$ ) and 100Wx2ch (Supplied voltage=40V, RL= $6\Omega$ ).

YDA136 has 24bit 192kHz (max) DAC and 6 to -73dB(1dB Step) of electron volumes in addition to a digital amplifier controller, and supports a digital audio signal input. Furthermore, it also supports an analog audio signal input with DAC bypasses.

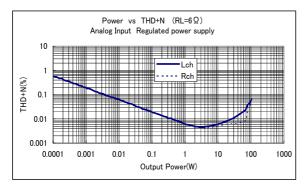

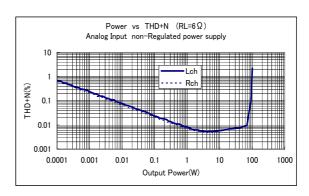

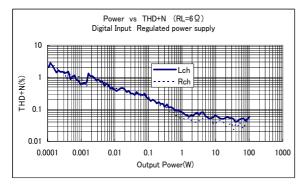

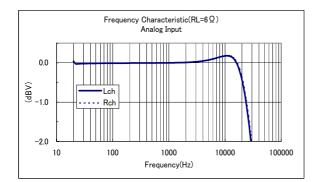

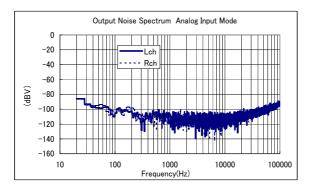

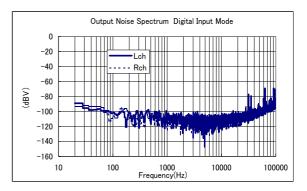

YDA136 realizes a high-standing audio characteristic that is lower noise and distortion rate by performing an analog feedback from PowerMOSFET output, and by using Yamaha's unique modulation method.

YDA136 also equips a function (Over current detection function) which protects a circuit from a short of speaker output terminal (after the LC filter) and a function (Supplied voltage detection function) which prevents a malfunction by detecting a power supply falling.

Moreover, it has a function (Clock stop detection function) to protect a circuit by detecting a stop termination of PWM carrier clock and a function (High-temperature detection function) to protect a circuit by detecting the unusual high-temperature condition of it-self.

At last, by making three YDA136 to daisy-chain connection, the audio system of 6ch is easily realizable.

## Features

| •High Out | put Power                                        |

|-----------|--------------------------------------------------|

| 100W      | (VBB=40V, RL=6 $\Omega$ )                        |

| 60W       | (VBB=32V, RL= $6\Omega$ )                        |

| •Low Dist | ortion Rate(THD+N)                               |

| 0.05%     | (Po=50W, 1kHz, RL=6 $\Omega$ , at digital input) |

| 0.03%     | (Po=50W, 1kHz, RL=6 $\Omega$ , at analog input)  |

| •High S/N | Ratio                                            |

| 100dB     | (VBB=40V, A-filter, Gain=21.7+6dB, RL=6Ω,        |

|           | at digital input                                 |

| •Low Resi | idual Noise                                      |

| 100µV     | (VBB=40V, Gain=21.7+6dB, at digital input)       |

| 70µV      | (VBB=40V, Gain=21.7+6dB, at analog input)        |

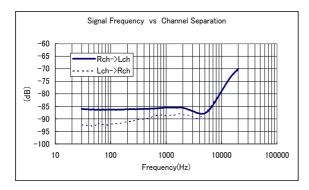

| •Channel  | Separation                                       |

| <i>-</i>  |                                                  |

<sup>80</sup>dB (1kHz, Po=50W)

- Supports 24bit Digital input and Analog input

- Built-in 6 to -73dB(1dB Step) of electron volume

- Multi-channel synchronous operation by switching Master/Slave function.

- Protect reset function

- Hard mute function

- Monophonic function

- Unusual operation detection protection function (Over current, Supplied voltage, Speaker terminal short, Clock stop, Heat)

- Pop noise rejection function at the time of power-up

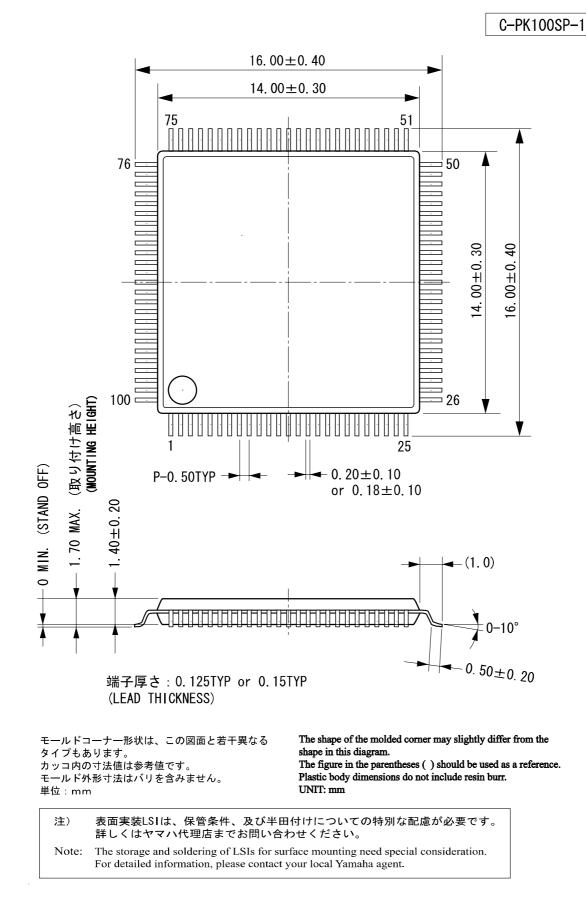

- 100 pin plastic SQFP Pin lead plating with Pd-free (YDA136-SZ)

## YAMAHA CORPORATION

| YDA136 CATALOG            |

|---------------------------|

| CATALOG No.:LSI-4DA136A20 |

| 2005.4                    |

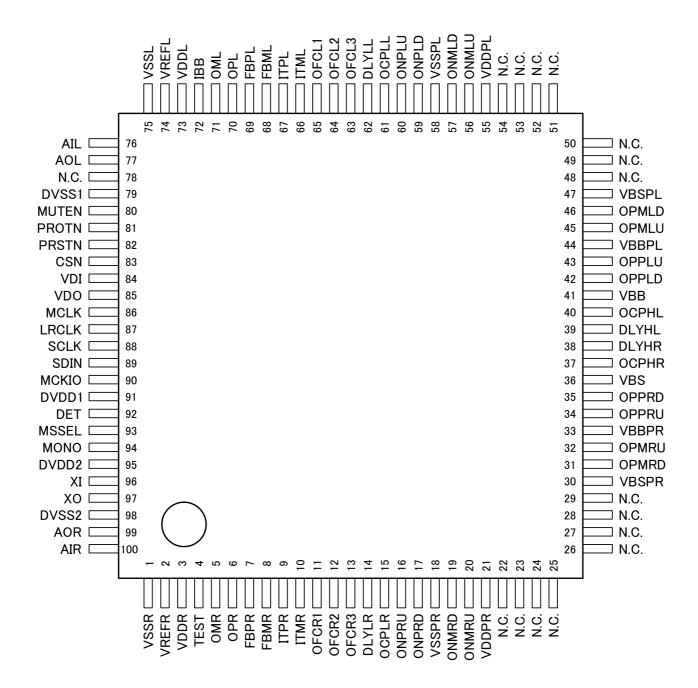

## ■Terminal Configuration

<100pin SQFP Top View>

## ■Terminal Functions

| No.      | Name  | I/O  | Function                                                          |  |  |  |

|----------|-------|------|-------------------------------------------------------------------|--|--|--|

| 1        | VSSR  | PWR  | Rch Analog Ground Terminal                                        |  |  |  |

| 2        | VREFR | AO   | Rch Reference Voltage Output Terminal                             |  |  |  |

| 3        | VDDR  | PWR  | Reh Analog Power Terminal                                         |  |  |  |

| 4        | TEST  | DI   | Test Terminal: Usually, use it by "L" fixation.                   |  |  |  |

| 5        | OMR   | AO   | Rch Electron Volume Output Terminal Inverted side                 |  |  |  |

| 6        | OPR   | AO   | Rch Electron Volume Output Terminal Noninverted side              |  |  |  |

| 7        | FBPR  | AU   | Rch Digital Amplifier Input Terminal Noninverted side             |  |  |  |

| 8        | FBMR  | AI   | Rch Digital Amplifier Input Terminal Inverted side                |  |  |  |

| <u> </u> | ITPR  | AO   | Rch External Filter Element Connection Terminal Noninverted side  |  |  |  |

| 10       | ITMR  | AO   | Rch External Filter Element Connection Terminal Inverted side     |  |  |  |

| 10       | OFCR1 | AU   | Hold to "H" level.                                                |  |  |  |

|          |       |      | Hold to "L" level.                                                |  |  |  |

| 12       | OFCR2 | AI   |                                                                   |  |  |  |

| 13       | OFCR3 | AI   | Hold to "L" level.                                                |  |  |  |

| 14       | DLYLR | AI   | Rch Low-Side Driver Off-time Setting Terminal                     |  |  |  |

| 15       | OCPLR | AI   | Rch Low-Side Over Current Detection Terminal                      |  |  |  |

| 16       | ONPRU | DO   | Rch Low-Side Driver Output Terminal Noninverted side (Pull-up)    |  |  |  |

| 17       | ONPRD | DO   | Rch Low-Side Driver Output Terminal Noninverted side (Pull-down)  |  |  |  |

| 18       | VSSPR | PWR  | Rch Low-Side Driver Ground Terminal                               |  |  |  |

| 19       | ONMRD | DO   | Rch Low-Side Driver Output Terminal Inverted side (Pull-down)     |  |  |  |

| 20       | ONMRU | DO   | Rch Low-Side Driver Output Terminal Inverted side (Pull-up)       |  |  |  |

| 21       | VDDPR | PWR  | Rch Low-Side Driver Power Terminal                                |  |  |  |

| 22       | N.C.  | -    | Non connection.                                                   |  |  |  |

| 23       | N.C.  | _    | Non connection.                                                   |  |  |  |

| 24       | N.C.  | _    | Non connection.                                                   |  |  |  |

| 25       | N.C.  |      | Non connection.                                                   |  |  |  |

| 26       | N.C.  |      | Non connection.                                                   |  |  |  |

| 27       | N.C.  |      | Non connection.                                                   |  |  |  |

| 28       | N.C.  | Ι    | Non connection.                                                   |  |  |  |

| 29       | N.C.  | -    | Non connection.                                                   |  |  |  |

| 30       | VBSPR | PWRH | Rch High-Side Driver Power Terminal                               |  |  |  |

| 31       | OPMRD | DOH  | Rch High-Side Driver Output Terminal Inverted side (Pull-down)    |  |  |  |

| 32       | OPMRU | DOH  | Rch High-Side Driver Output Terminal Inverted side (Pull-up)      |  |  |  |

| 33       | VBBPR | PWRH | Rch High-Side Driver Power Terminal                               |  |  |  |

| 34       | OPPRU | DOH  | Rch High-Side Driver Output Terminal Noninverted side (Pull-up)   |  |  |  |

| 35       | OPPRD | DOH  | Rch High-Side Driver Output Terminal Noninverted side (Pull-down) |  |  |  |

| 36       | VBS   | PWRH | High-Side Common Circuit Power Terminal                           |  |  |  |

| 37       | OCPHR | AIH  | Rch High-Side Over Current Detection Terminal                     |  |  |  |

| 38       | DLYHR | AIH  | Rch High-Side Driver Off-time Setting Terminal                    |  |  |  |

| 39       | DLYHL | AIH  | Lch High-Side Driver Off-time Setting Terminal                    |  |  |  |

| 40       | OCPHL | AIH  | Lch High-Side Over Current Detection Terminal                     |  |  |  |

| 41       | VBB   | PWRH | High-Side Common Circuit Power Terminal                           |  |  |  |

| 42       | OPPLD | DOH  | Lch High-Side Driver Output Terminal Noninverted side (Pull-down) |  |  |  |

| 43       | OPPLU | DOH  | Leh High-Side Driver Output Terminal Noninverted side (Pull-up)   |  |  |  |

| 44       | VBBPL | PWRH | Leh High-Side Driver Power Terminal                               |  |  |  |

| 45       | OPMLU | DOH  | Leh High-Side Driver Output Terminal Inverted side (Pull-up)      |  |  |  |

| 46       | OPMLD | DOII | Leh High-Side Driver Output Terminal Inverted side (Pull-down)    |  |  |  |

| 40       | VBSPL | PWRH | Leh High-Side Driver Power Terminal                               |  |  |  |

| 47       | N.C.  |      |                                                                   |  |  |  |

| 48       | N.C.  |      | Non connection.   Non connection.                                 |  |  |  |

| 49<br>50 | N.C.  |      |                                                                   |  |  |  |

|          | N.C.  |      | Non connection.                                                   |  |  |  |

Note: DI: Digital Input Terminal, DO: Digital Output Terminal, DIO: Digital I/O Terminal, DOH: High-Side Digital Output Terminal AI: Analog Input Terminal, AO: Analog Output Terminal, AIH: High-Side Analog Input Terminal

PWR:Low-Side Power Terminal, PWRH:High-Side Power Terminal

| No. | Name  | I/O        | Function                                                                                           |  |  |  |

|-----|-------|------------|----------------------------------------------------------------------------------------------------|--|--|--|

| 51  | N.C.  | -          | Non connection.                                                                                    |  |  |  |

| 52  | N.C.  | _          | Non connection.                                                                                    |  |  |  |

| 53  | N.C.  | _          | Non connection.                                                                                    |  |  |  |

| 54  | N.C.  | _          | Non connection.                                                                                    |  |  |  |

| 55  | VDDPL | PWR        | Lch Low-Side Driver Power Terminal                                                                 |  |  |  |

| 56  | ONMLU | DO         | Leh Low-Side Driver Output Terminal Inverted side (Pull-up)                                        |  |  |  |

| 57  | ONMLD | DO         | Lch Low-Side Driver Output Terminal Inverted side (Pull-down)                                      |  |  |  |

| 58  | VSSPL | PWR        | Leh Low-Side Driver Ground Terminal                                                                |  |  |  |

| 59  | ONPLD | DO         | Lch Low-Side Driver Output Terminal Noninverted side (Pull-down)                                   |  |  |  |

| 60  | ONPLU | DO         | Lch Low-Side Driver Output Terminal Noninverted side (Pull-up)                                     |  |  |  |

| 61  | OCPLL | DO         | Leh Low-Side Over Current Detection Terminal                                                       |  |  |  |

| 62  | DLYLL | AI         | Leh Low-Side Driver Off-time Setting Terminal                                                      |  |  |  |

| 63  | OFCL3 | AI         | Hold to "L" level.                                                                                 |  |  |  |

| 64  | OFCL2 | AI         | Hold to "L" level.                                                                                 |  |  |  |

| 65  | OFCL1 | AI         | Hold to "H" level.                                                                                 |  |  |  |

| 66  | ITML  | AO         | Lch External Filter Elements Connection Terminal Inverted side                                     |  |  |  |

| 67  | ITPL  | AO         | Lch External Filter Elements Connection Terminal Noninverted side                                  |  |  |  |

| 68  | FBML  | AI         | Leh Digital Amplifier Input Terminal Inverted side                                                 |  |  |  |

| 69  | FBPL  | AI         | Leh Digital Amplifier Input Terminal Noninverted side                                              |  |  |  |

| 70  | OPL   | AO         | Lch Electron Volume Output Terminal Noninverted side                                               |  |  |  |

| 71  | OML   | AO         | Leh Electron Volume Output Terminal Inverted side                                                  |  |  |  |

| 72  | IBB   | AI         | VBB Power-voltage Detection Terminal (Supplied-voltage feedback Terminal)                          |  |  |  |

| 73  | VDDL  | PWR        | Leh Analog Power Terminal                                                                          |  |  |  |

| 74  | VREFL | AO         | Len Analog Power Terminal<br>Leh Reference Power-voltage Output Terminal                           |  |  |  |

| 75  | VSSL  | PWR        | Leh Analog Ground Terminal                                                                         |  |  |  |

| 76  | AIL   | AI         | Lch Electron Volume Input Terminal (Analog Signal Input Terminal)                                  |  |  |  |

| 77  | AOL   | AO         | Leh DAC Output Terminal                                                                            |  |  |  |

| 78  | N.C.  | _          | Non connection.                                                                                    |  |  |  |

| 79  | DVSS1 | PWR        | Digital Ground Terminal                                                                            |  |  |  |

| 80  | MUTEN | DI         | Mute Control Terminal                                                                              |  |  |  |

| 81  | PROTN | DO         | Unusual Detection Output Terminal (Open-drain)                                                     |  |  |  |

| 82  | PRSTN | DI         | Protect Reset Control Terminal                                                                     |  |  |  |

| 83  | CSN   | DI         | MPU Interface Chip-select Input Terminal                                                           |  |  |  |

| 84  | VDI   | DI         | MPU Interface Serial Data Input Terminal                                                           |  |  |  |

| 85  | VDO   | DO         | MPU Interface Serial Data Output Terminal                                                          |  |  |  |

| 86  | MCLK  | DI         | MPU Interface Serial Clock Input Terminal                                                          |  |  |  |

| 87  | LRCLK | DI         | DAC Interface Serial Word Clock Input Terminal                                                     |  |  |  |

| 88  | SCLK  | DI         | DAC Interface Serial Clock Input Terminal                                                          |  |  |  |

| 89  | SDIN  | DI         | DAC Interface Serial Data Input Terminal                                                           |  |  |  |

| 90  | MCKIO | DIO        | Clock Input/Output Terminal                                                                        |  |  |  |

| 91  | DVDD1 | PWR        | Digital Power Terminal                                                                             |  |  |  |

| 92  | DET   | DO         | Startup Standby Time Setting Terminal                                                              |  |  |  |

| 93  | MSSEL | DI         | Slave mode/Master mode Change Terminal                                                             |  |  |  |

| 94  | MONO  | DI         | Monophonic Control Terminal                                                                        |  |  |  |

| 95  | DVDD2 | PWR        | CERALOCK Power Terminal                                                                            |  |  |  |

| 96  | XI    | DI         | CERALOCK Connection Terminal                                                                       |  |  |  |

| 97  | XO    | DO         | CERALOCK Connection Terminal                                                                       |  |  |  |

| 98  | DVSS2 | PWR        | CERALOCK Ground Terminal                                                                           |  |  |  |

| 99  | AOR   | AO         | Rch DAC Output Terminal                                                                            |  |  |  |

| 100 | AIR   | AI         | Rch Electron Volume Input Terminal (Analog Signal Input Terminal)                                  |  |  |  |

|     |       | out Termin | al, DO: Digital Output Terminal, DIO: Digital I/O Terminal, DOH: High-Side Digital Output Terminal |  |  |  |

Note: DI: Digital Input Terminal, DO: Digital Output Terminal, DIO: Digital I/O Terminal, DOH:High-Side Digital Output Terminal AI: Analog Input Terminal, AO: Analog Output Terminal, AIH:High-Side Analog Input Terminal PWR:Low-Side Power Terminal, PWRH:High-Side Power Terminal "CERALOCK" is the trademark of Murata Manufacturing Co., Ltd.

**YAMAHA**

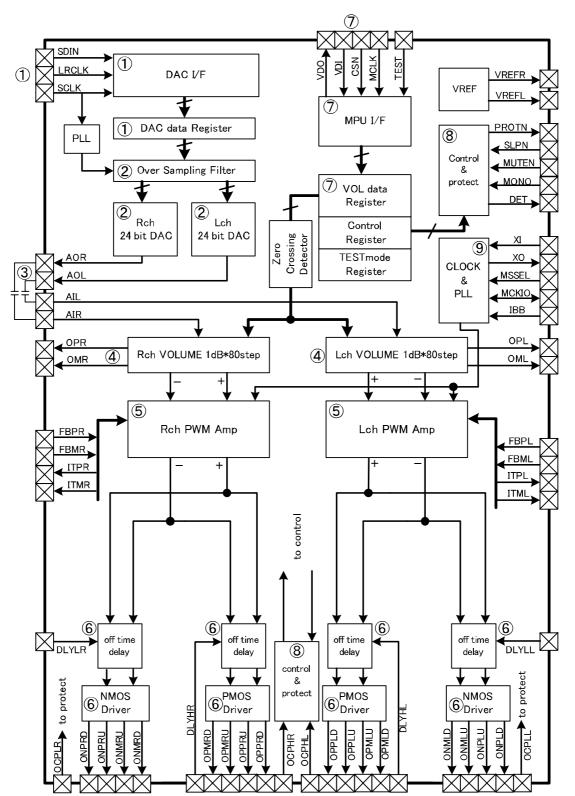

Block Diagram

## Description of Block Functions

- ① Stores the digital audio signal into DAC data register through a DAC interface.

- ② Inputs into DAC through an over-sampling filter, and converts into an analog signal.

- ③ Performs a DC cut to DAC output data with the exterior capacitor of IC.

- ④ Performs a volume control and Differential signal conversion.

- ⑤ Performs a pulse width modulation Negative feedbacks from the output of an extern

- Negative feedbacks from the output of an external PowerMOSFET buffer.Performs an Off-time delay control, and drives an external PowerMOSFET(Pch, Nch).

- Wertorns an Off-time delay control, and drives an external PowerMOSFET(Pch, Nch). High current digital pulse signal is output from external PowerMOSFET (Pch, Nch) The digital pulse signal is converted into audio signals by external LC filter and transmitted to speaker.

- ⑦ Stores the 7-bit volume data and control data into volume register and control register respectively through a MPU interface.

- 8 Operation control circuit and protect circuit

- (9) Master clock generation circuit and carrier clock generation circuit

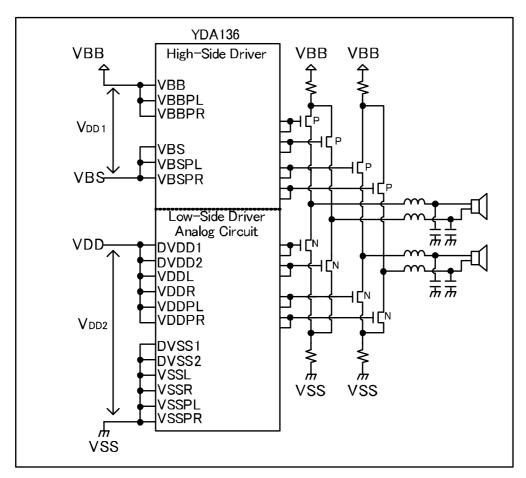

## ■Supply of Power

YDA136 needs to be supplied the following two kinds of power supplies, the object for Low-Side drivers (Analog Circuit), and the object for High-Side drivers, in addition to a power stage power supply (VBB, VSS). Be sure to use VDD power for Low-Side driver and VBS for High-Side driver.

## Description of Terminals Functions

#### • Power Supply Terminal

#### Lo-Side Power Supply Terminal (VDD Power Supply) DVDD1 Digital Power DVDD2 **CERALOCK** Power Lch Analog Power VDDL VDDR Rch Analog Power VDDPL Lch Low-Side Driver Power Rch Low-Side Driver Power VDDPR Lo-Side Ground Terminal (VSS Ground) DVSS1 Digital Ground DVSS2 CERALOCK Ground

| 0,002 |                            |

|-------|----------------------------|

| VSSL  | Lch Analog Ground          |

| VSSR  | Rch Analog Ground          |

| VSSPL | Lch Low-Side Driver Ground |

| VSSPR | Rch Low-Side Driver Ground |

## High-Side Power Supply Terminal (VBB Power Supply)

| VBB   | High-Side Power            |

|-------|----------------------------|

| VBBPL | Lch High-Side Driver Power |

| VBBPR | Rch High-Side Driver Power |

## High-Side Power Supply Terminal (VBS Power Supply)

| VBS   | High-Side Power            |

|-------|----------------------------|

| VBSPL | Lch High-Side Driver Power |

| VBSPR | Rch High-Side Driver Power |

## Control Terminal

| MUTEN | Hard Mute Control Terminal                                                            |

|-------|---------------------------------------------------------------------------------------|

|       | L: Hard mute mode                                                                     |

|       | H: Normal mode                                                                        |

| PRSTN | Protect Reset Control Terminal                                                        |

|       | L: Protect reset mode                                                                 |

|       | H: Normal mode                                                                        |

| PROTN | Unusual Detection Output Terminal                                                     |

|       | L: Protect mode                                                                       |

|       | Hi-Z: Normal mode                                                                     |

|       | Since it is an OpenDrain output, be sure to pull-up by resistance.                    |

| MONO  | Monophonic Control Terminal                                                           |

|       | L: Stereo mode                                                                        |

|       | H: Monophonic mode                                                                    |

| DET   | Start up Standby Time Setting Terminal                                                |

|       | Sets up a Start up Standby Time (TWAIT) by connecting a capacitor into this terminal. |

| TEST  | Test Terminal                                                                         |

|       | Hold to "L" level.                                                                    |

# **YAMAHA**

## Clock Terminal

| XI    | CERALOCK Connection Terminal                              |

|-------|-----------------------------------------------------------|

|       | Master mode: Connects a CERALOCK for 4.19MHz oscillation. |

|       | Slave mode: Fixes to "L."                                 |

| XO    | CERALOCK Connection Terminal                              |

|       | Master mode: Connects a CERALOCK for 4.19MHz oscillation. |

|       | Slave mode: Makes to "OPEN".                              |

| MSSEL | Slave mode/ Master mode Selection Terminal                |

|       | L: Master mode                                            |

|       | H: Slave mode                                             |

| MCKIO | 4. 19MHz Clock I/O Terminal                               |

|       | Master mode: Clock Output                                 |

|       | Slave mode: Clock Input                                   |

<u>YDA136</u>

## •Digital Interface Terminal

| MPU Interface |     |                              |

|---------------|-----|------------------------------|

| CSN           | MPU | Interface Chip-select Input  |

| MCLK          | MPU | Interface Serial Clock Input |

| VDI           | MPU | Interface Serial Data Input  |

| VDO           | MPU | Interface Serial Data Output |

|               |     | -                            |

## DAC Interface

| LRCLK | DAC | Interface Serial Word Clock Input |

|-------|-----|-----------------------------------|

| SCLK  | DAC | Interface Serial Clock Input      |

| SDIN  | DAC | Interface Serial Data Input       |

## Analog I/O Terminal

| DAC Output Term | inal   |                                                             |

|-----------------|--------|-------------------------------------------------------------|

| AOL             | Lch    | DAC Output                                                  |

| AOR             | Rch    | DAC Output                                                  |

| Be sure to make | ke AOI | R to an OPEN state or to connect to VSS in Monophonic mode. |

## **Electron Volume Input**

| AIL        | Lch        | Volume Input Signal                                       |

|------------|------------|-----------------------------------------------------------|

| AIR        | Rch        | Volume Input Signal                                       |

| Be sure to | o make AIR | to an OPEN state or to connect to GND in Monophonic mode. |

## Electron Volume Output

| OPL | Lch | Electron Volume Output Terminal N | Noninverted side |

|-----|-----|-----------------------------------|------------------|

| OML | Lch | Electron Volume Output Terminal   | Inverted side    |

| OPR | Rch | Electron Volume Output Terminal   | Noninverted side |

| OMR | Rch | Electron Volume Output Terminal   | Inverted side    |

Be sure to make both OPR and OMR to a OPEN state or to connect to VSS in Monophonic mode.

### •Terminals for PWM modulation Circuits

| FBPL<br>FBML<br>ITPL<br>ITML<br>DLYLL<br>DLYHL | Lch<br>Lch<br>Lch<br>Lch<br>Lch<br>Lch |                                                                                                                                                                                                         | ction | de<br>Noninverted side                                                 |

|------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------|

| FBPR<br>FBMR<br>ITPR<br>ITMR<br>DLYLR<br>DLYHR | Rch<br>Rch<br>Rch<br>Rch<br>Rch<br>Rch | Digital Amplifier Input<br>Digital Amplifier Input<br>for External Filter Element Connec<br>for External Filter Element Connec<br>Low-Side Driver Off-time Setting<br>High-Side Driver Off-time Setting | ction | Noninverted side<br>Inverted side<br>Noninverted side<br>Inverted side |

Be sure to make each terminal of Rch to an OPEN state or to connect to VSS in Monophonic mode. In addition, as for a High-side terminal, be sure to make it to an OPEN state and to connect to VBS.

#### PowerMOSFET Drive Terminal

| OPPLU<br>OPPLD<br>ONPLU<br>ONPLD | Lch High-Side Driver Output<br>Lch High-Side Driver Output<br>Lch Low-Side Driver Output<br>Lch Low-Side Driver Output | Noninverted sidePull-upNoninverted sidePull-downNoninverted sidePull-upNoninverted sidePull-down |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| OPMLU<br>OPMLD<br>ONMLU<br>ONMLD | Lch High-Side Driver Output<br>Lch High-Side Driver Output<br>Lch Low-Side Driver Output<br>Lch Low-Side Driver Output | Inverted sidePull-upReversal sidePull-downInverted sidePull-upInverted sidePull-down             |

| OPPRU<br>OPPRD<br>ONPRU<br>ONPRD | Rch High-Side Driver Output<br>Rch High-Side Driver Output<br>Rch Low-Side Driver Output<br>Rch Low-Side Driver Output | Noninverted sidePull-upNoninverted sidePull-downNoninverted sidePull-upNoninverted sidePull-down |

| OPMRU<br>OPMRD<br>ONMRU<br>ONMRD | Rch High-Side Driver Output<br>Rch High-Side Driver Output<br>Rch Low-Side Driver Output<br>Rch Low-Side Driver Output | Noninverted sidePull-upNoninverted sidePull-downNoninverted sidePull-upNoninverted sidePull-down |

Low-Side Driver means the PowerMOSFET (Nch). High-Side Driver means the PowerMOSFET(Pch). The through rate control of PowerMOSFET is performed by connecting a resistor between the pull-up side output of a Low-Side driver and PowerMOSFET (Nch) and between the pull-down side of a High-Side driver and PowerMOSFET (Pch).

## •Terminal for Protect Function

| OCPHL | Lch High-Side Over Current Detection Terminal                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OCPLL | Lch Low-Side Over Current Detection Terminal                                                                                                                                              |

| OCPHR | Rch High-Side Over Current Detection Terminal                                                                                                                                             |

| OCPLR | Rch Low-Side Over Current Detection Terminal                                                                                                                                              |

| IBB   | VBB Supplied Voltage Detection Terminal<br>This terminal operates also as a supplied voltage feedback terminal.<br>Be sure to input a specific voltage divided by a resistor VBB and VSS. |

YDA136

## VREF Terminal

| VREFL | Lch | Reference Voltage Output Terminal         |

|-------|-----|-------------------------------------------|

|       | Be  | sure to connect a stabilization capacity. |

| VREFR | Rch | Reference Voltage Output Terminal         |

|       | Be  | sure to connect a stabilization capacity. |

## •Test Terminal etc.

| TEST  | Hold to "L" level. |

|-------|--------------------|

| OFCL1 | Hold to "H" level. |

| OFCR1 | Hold to "H" level. |

| OFCL2 | Hold to "L" level. |

| OFCR2 | Hold to "L" level. |

| OFCL3 | Hold to "L" level. |

| OFCR3 | Hold to "L" level. |

|       |                    |

## ■Terminal Condition in each Mode

## Operation Mode

YDA136 becomes an operation mode as the following table by the state in each input terminal.

|                                    |                      |                      |                     |                                  | Current<br>ction                 | Pov    | wer Detec           | tion                |                         |                      |                      | tput                        | tput                       | tput                        | tput                       |

|------------------------------------|----------------------|----------------------|---------------------|----------------------------------|----------------------------------|--------|---------------------|---------------------|-------------------------|----------------------|----------------------|-----------------------------|----------------------------|-----------------------------|----------------------------|

|                                    | PRSTN Terminal Level | MUTEN Terminal Level | MONO Terminal Level | VBB - V(OCPHL)<br>VBB - V(OCPHR) | V(OCPLL) - VSS<br>V(OCPLR) - VSS | V(IBB) | VDD1 =<br>VBB - VBS | VDD2 =<br>VDD - VSS | Carrier Clock Frequency | Junction Temperature | PROTN Terminal Level | Lch High-Side Driver Output | Lch Low-Side Driver Output | Rch High-Side Driver Output | Rch Low-Side Driver Output |

|                                    | -                    | -                    | -                   | -                                | -                                | < VIB  | -                   | -                   | -                       | -                    | Hi-z                 | Н                           | L                          | Н                           | L                          |

| Low Voltage<br>Detection Mode      | -                    | -                    | -                   | -                                | -                                | -      | < VVB               | -                   | -                       | -                    | Hi-z                 | Н                           | L                          | Н                           | L                          |

|                                    | -                    | -                    | -                   | -                                | -                                | -      | -                   | < Vvd               | -                       | -                    | Hi-z                 | Н                           | L                          | Н                           | L                          |

| Protect Reset Mode                 | L                    | -                    | -                   | -                                | -                                | > VIB  | > VvB               | > VvD               | -                       | -                    | Hi-z                 | Н                           | L                          | Н                           | L                          |

| High temperature<br>Detection Mode | Н                    | -                    | -                   | -                                | -                                | Î      | ſ                   | ſ                   | -                       | > Tmax               | L                    | Н                           | L                          | Н                           | L                          |

| Hardware Mute<br>Mode              | Н                    | L                    | -                   | -                                | -                                | Î      | Î                   | Î                   | -                       | < Tmax               | Hi-z                 | Н                           | L                          | Н                           | L                          |

| Over Current                       | Н                    | Н                    | -                   | > Voc1                           | -                                | Î      | Î                   | Î                   | -                       | -                    | L                    | Н                           | L                          | Н                           | L                          |

| Detection Mode                     | Н                    | Н                    | -                   | 1                                | < VOC2                           | Î      | Î                   | Î                   | -                       | -                    | L                    | Н                           | L                          | Н                           | L                          |

| Clock Stop                         | Н                    | Н                    | -                   | < Voc1                           | < Voc1<br>> Voc2                 | Î      | Î                   | Î                   | < Fc1                   | < Tmax               | Hi-z                 | Н                           | L                          | Н                           | L                          |

| Detection Mode                     | Н                    | Н                    | -                   | Î                                | Î                                | Î      | Î                   | Î                   | > Fc2                   | Î                    | Hi-z                 | Н                           | L                          | Н                           | L                          |

| Stereo Mode                        | Н                    | Н                    | L                   | Î                                | Î                                | Î      | Î                   | Ť                   | > FC1<br>< FC2          | Î                    | Hi-z                 | Р                           | Р                          | Р                           | Р                          |

| Monaural Mode                      | Н                    | Н                    | Н                   | Î                                | Î                                | Î      | Î                   | Î                   | Î                       | Î                    | Hi-z                 | Р                           | Р                          | *1                          | L                          |

Note:

- 1) "-" means all input conditions.

- 2) "H" means "H" level, and "L" means "L" level. In addition, "P" means "Pulse oscillation condition".

- 3) "\*1" means indefinite state.

- 4) Rch over current detection terminal "OCPLR and OCPHR" can not be operated in Monophonic mode.

- 5) In the over current detection mode, the mode is continued even if it goes out of the over current condition. The over current detection mode is canceled by protect reset mode.

- 6) All registers are initialized when VDD2 voltage (VDD-VSS) becomes below VVD in the low voltage detection modes.

- 7) When YDA136 it-self heats higher than the unusual temperature (Tmax), it will become a high temperature detection mode.

### • Digital Audio Signal Input Mode / Analog Audio Signal Input Mode

YDA136 can input both Digital Audio Signal and Analog Audio Signal.

In case of input for the digital audio signal, be sure to connect DAC output terminal (AOL, AOR) and electron volume input terminal (AIL, AIR) through capacitor for DC cut.

In addition, in case of input for the analog audio signal; be sure to connect an analog audio signal to electron volume input terminal (AIL,AIR) through a capacitor for DC cut.

At this time, the output of DAC can be made into High-Z by setting the DAC input format of a control register as MODE8.

## ■Functional Explanation of Operations

## •Description of Registers

The volume register and the control register are allocated to address "0" and "1" in the register, respectively. Each 14-bit register is mapped as follows.

Register Map

|                  | Address |      |     |      |      |      |      | В   | lit |    |    |    |    |    |    |

|------------------|---------|------|-----|------|------|------|------|-----|-----|----|----|----|----|----|----|

|                  | Audiess | D13  | D12 | D11  | D10  | D9   | D8   | D7  | D6  | D5 | D4 | D3 | D2 | D1 | D0 |

| Volume Register  | 0       | R6   | R5  | R4   | R3   | R2   | RI   | R0  | L6  | LS | L4 | L3 | L2 | L1 | L0 |

| Control Register | 1       | ZERO | CF  | OSFN | MOD2 | MOD1 | MOD0 | FS1 | FS0 | T5 | T4 | T3 | Τ2 | ΓI | T0 |

R6...R0 :Rch Volume Register

L6...L0 :Lch Volume Register

ZERO : Volume Zero-cross Function Selection Register

CF : Carrier Clock Frequency Selection Register

OSFN : Over Sampling Filter Function Selection Register

MOD2...0 : DAC Input Format Selection Register

FS1...0 : Over Sampling Mode Selection Register

T5...T0 :(Reserved) Be held at "0."

## Volume Register

|                            |                                                     | -  | r  |    |    | -  |               |   |                        |    | _  |    |    |               |               |    |

|----------------------------|-----------------------------------------------------|----|----|----|----|----|---------------|---|------------------------|----|----|----|----|---------------|---------------|----|

| Valuma Dagistan            | L6                                                  | L5 | L4 | L3 | L2 | L1 | L0            |   | Valuma Dagistan        | L6 | L5 | L4 | L3 | L2            | L1            | L0 |

| Volume Register            | R6                                                  |    | R4 |    |    |    | R0            |   | Volume Register        | R6 | R5 | R4 | R3 | R2            | R1            | R0 |

| vol=Mute                   | 1                                                   | 1  | 1  | 1  | 1  | 1  | 1             | _ | vol= -57dB             | 0  | 1  | 1  | 1  | 1             | 1             | 1  |

| vol= 6dB                   | 1                                                   | 1  | 1  | 1  | 1  | 1  | 0             | _ | vol= -58dB             | 0  | 1  | 1  | 1  | 1             | 1             | 0  |

| vol= 5dB                   | 1                                                   | 1  | 1  | 1  | 1  | 0  | 1             | _ | vol=-59dB              | 0  | 1  | 1  | 1  | 1             | 0             | 1  |

| vol= 4dB                   | 1                                                   | 1  | 1  | 1  | 1  | 0  | 0             | _ | vol=-60dB              | 0  | 1  | 1  | 1  | 1             | 0             | 0  |

| vol=3dB                    | 1                                                   | 1  | 1  | 1  | 0  | 1  | 1             | _ | vol=-61dB              | 0  | 1  | 1  | 1  | 0             | 1             | 1  |

| vol= 2dB                   | 1                                                   | 1  | 1  | 1  | 0  | 1  | 0             | _ | vol=-62dB              | 0  | 1  | 1  | 1  | 0             | 1             | 0  |

| vol=2dB<br>vol=1dB         | 1                                                   | 1  | 1  | 1  | 0  | 0  | 1             | _ | vol=-63dB              | 0  | 1  | 1  | 1  | 0             | 0             | 1  |

| vol= 0dB                   | 1                                                   | 1  | 1  | 1  | 0  | 0  | $\frac{1}{0}$ | _ | vol=-64dB              | 0  | 1  | 1  | 1  | 0             | 0             | 0  |

| vol= -1dB                  | 1                                                   | 1  | 1  | 0  | 1  | 1  | 1             | _ | vol=-65dB              | 0  | 1  | 1  | 0  | 1             | 1             | 1  |

| vol= -2dB                  | 1                                                   | 1  | 1  | 0  | 1  | 1  | 0             | _ | vol= -66dB             | 0  | 1  | 1  | 0  | 1             | 1             | 0  |

| vol=-2dB<br>vol=-3dB       | 1                                                   | 1  | 1  | 0  | 1  | 0  | 1             | _ | vol=-67dB              | 0  | 1  | 1  | 0  | 1             | $\frac{1}{0}$ | 1  |

| vol=-3dB<br>vol=-4dB       | 1                                                   | 1  | 1  | 0  | 1  | 0  | 0             | _ | vol=-68dB              | 0  | 1  | 1  | 0  | 1             | 0             | 0  |

| vol=-4dB<br>vol=-5dB       | 1                                                   | 1  | 1  | 0  | 0  | 1  | 1             | _ | vol=-69dB              | 0  | 1  | 1  | 0  | 0             | 1             | 1  |

|                            | 1                                                   | 1  | 1  | 0  | 0  | 1  | 0             | _ | vol= -09dB             | 0  | 1  | 1  | 0  | 0             | 1             | 0  |

| vol=-6dB                   | 1                                                   | _  |    | 0  | 0  | 0  | 1             | _ | vol=-70dB<br>vol=-71dB | 0  | 1  |    | 0  | 0             | _             |    |

| vol=-7dB<br>vol=-8dB       | 1                                                   | 1  | 1  | 0  | 0  | 0  | $\frac{1}{0}$ | _ |                        | 0  | 1  | 1  | 0  | 0             | 0             | 1  |

|                            | -                                                   |    |    | -  |    |    |               | _ | vol=-72dB              | 0  | _  | -  |    | -             |               |    |

| vol=-9dB                   | 1                                                   | 1  | 0  | 1  | 1  | 1  | 1             | _ | vol=-73dB              |    | 1  | 0  | 1  | 1             | 1             | 1  |

| vol=-10dB                  | 1                                                   | 1  | 0  | 1  | 1  | 1  | 0             | _ |                        | 0  | 1  | 0  | 1  | 1             | 1             | 0  |

| vol=-11dB                  | 1                                                   | 1  | 0  | 1  | 1  | 0  | 1             | _ |                        | 0  | 1  | 0  | 1  | 1             | 0             | 1  |

| vol=-12dB                  | 1                                                   | 1  |    | 1  | 1  |    | 0             | _ |                        |    | 1  |    | 1  | 1             | 0             | 0  |

| vol=-13dB                  | 1                                                   | 1  | 0  | 1  | 0  | 1  | 1 0           | _ |                        | 0  | 1  | 0  | 1  | 0             | 1             | 1  |

| vol=-14dB                  | 1                                                   | 1  | -  | 1  |    | 1  |               | _ |                        | -  | 1  | 0  | 1  | -             | 1             |    |

| vol=-15dB                  | 1                                                   | 1  | 0  | 1  | 0  | 0  | 1             | _ |                        | 0  | 1  | 0  | 1  | 0             | 0             | 1  |

| vol=-16dB                  | 1                                                   | 1  | 0  | 1  | 0  | 0  | 0             | _ |                        | 0  | 1  | 0  | 1  | 0             | 0             | 0  |

| vol=-17dB                  | 1                                                   | 1  | 0  | 0  | 1  | 1  | 1             | _ |                        | 0  | 1  | 0  | 0  | 1             | 1             | 1  |

| vol=-18dB                  | 1                                                   | 1  | 0  | 0  | 1  | 1  | 0             | _ |                        | 0  | 1  | 0  | 0  | 1             | 1             | 0  |

| vol=-19dB                  | 1                                                   | 1  | 0  | 0  | 1  | 0  | 1             | _ |                        | 0  | 1  | 0  | 0  | 1             | 0             | 1  |

| vol= -20dB                 | 1                                                   | 1  | 0  | 0  | 1  | 0  | 0             | _ |                        | 0  | 1  | 0  | 0  | 1             | 0             | 0  |

| vol= -21dB                 | 1                                                   | 1  | 0  | 0  | 0  | 1  | 1             | _ |                        | 0  | 1  | 0  | 0  | 0             | 1             | 1  |

| vol= -22dB                 | 1                                                   | 1  | 0  | 0  | 0  | 1  | 0             | _ |                        | 0  | 1  | 0  | 0  | 0             | 1             | 0  |

| vol=-23dB                  | 1                                                   | 1  | 0  | 0  | 0  | 0  | 1             | _ |                        | 0  | 1  | 0  | 0  | 0             | 0             | 1  |

| vol=-24dB                  | 1                                                   | 1  | 0  | 0  | 0  | 0  | 0             | _ |                        | 0  | 1  | 0  | 0  | 0             | 0             | 0  |

| vol=-25dB                  | 1                                                   | 0  | 1  | 1  | 1  | 1  | 1             | _ |                        | 0  | 0  | 1  | 1  | 1             | 1             | 1  |

| vol=-26dB                  | 1                                                   | 0  | 1  | 1  | 1  | 1  | 0             | _ |                        | 0  | 0  | 1  | 1  | 1             | 1             | 0  |

| vol= -27dB<br>vol= -28dB   | 1                                                   | 0  | 1  | 1  | 1  | 0  | 1 0           | _ |                        | 0  | 0  | 1  | 1  | 1             | 0             | 1  |

| vol= -28dB                 | 1                                                   | 0  | 1  | 1  | 0  | 1  | 1             | _ |                        | 0  | 0  | 1  | 1  | 1             | 1             | 1  |

| vol=-29dB<br>vol=-30dB     | 1                                                   | 0  | 1  | 1  | 0  | 1  | $\frac{1}{0}$ | _ |                        | 0  | 0  | 1  | 1  | 0             | 1             | 0  |

| vol= -31dB                 | 1                                                   | 0  | 1  | 1  | 0  | 0  | 1             | _ |                        | 0  | 0  | 1  | 1  | 0             | $\frac{1}{0}$ | 1  |

| vol= -31dB                 | 1                                                   | 0  | 1  | 1  | 0  | 0  | $\frac{1}{0}$ | _ |                        | 0  | 0  | 1  | 1  | 0             | 0             | 0  |

| vol=-32dB<br>vol=-33dB     | 1                                                   | 0  | 1  | 0  | 1  | 1  | 1             | _ | vol=Mute               | 0  | 0  | 1  | 0  | 1             | 1             | 1  |

| vol= -34dB                 | 1                                                   | 0  | 1  | 0  | 1  | 1  | 0             | _ | voi-iviute             | 0  | 0  | 1  | 0  | 1             | 1             | 0  |

| vol=-34dB<br>vol=-35dB     | 1                                                   | 0  | 1  | 0  | 1  | 0  | 1             | _ |                        | 0  | 0  | 1  | 0  | 1             | 0             | 1  |

| vol=-36dB                  | 1                                                   | 0  | 1  | 0  | 1  | 0  | 0             | _ |                        | 0  | 0  | 1  | 0  | 1             | 0             | 0  |

| vol=-30dB<br>vol=-37dB     | 1                                                   | 0  | 1  | 0  | 0  | 1  | 1             | - |                        | 0  | 0  | 1  | 0  | $\frac{1}{0}$ | 1             | 1  |

| vol= -3/dB                 | 1                                                   | 0  | 1  | 0  | 0  | 1  | $\frac{1}{0}$ | _ |                        | 0  | 0  | 1  | 0  | 0             | 1             | 0  |

| vol= -39dB                 | 1                                                   | 0  | 1  | 0  | 0  | 0  | 1             | _ |                        | 0  | 0  | 1  | 0  | 0             | $\frac{1}{0}$ | 1  |

| vol= -39dB                 | 1                                                   | 0  | 1  | 0  | 0  | 0  | $\frac{1}{0}$ | _ |                        | 0  | 0  | 1  | 0  | 0             | 0             | 0  |

| vol=-40dB<br>vol=-41dB     | 1                                                   | 0  | 0  | 1  | 1  | 1  | 1             | _ |                        | 0  | 0  | 0  | 1  | 1             | 1             | 1  |

| vol=-41dB<br>vol=-42dB     | 1                                                   | 0  | 0  | 1  | 1  | 1  | $\frac{1}{0}$ | _ |                        | 0  | 0  | 0  | 1  | 1             | 1             | 0  |

| vol=-42dB<br>vol=-43dB     | 1                                                   | 0  | 0  | 1  | 1  | 1  | 1             | _ |                        | 0  | 0  | 0  | 1  | 1             | $\frac{1}{0}$ | 1  |

| vol=-43dB<br>vol=-44dB     | 1                                                   | 0  | 0  | 1  | 1  | 0  | $\frac{1}{0}$ | _ |                        | 0  | 0  | 0  | 1  | 1             | 0             | 1  |

| vol = -44dB<br>vol = -45dB | 1                                                   | 0  | 0  |    | 1  | 1  | 1             | _ |                        | 0  | 0  | 0  |    | 1             | _             | 1  |

| vol = -45dB<br>vol = -46dB | 1                                                   | -  |    | 1  | -  | _  |               | - |                        | -  | -  |    | 1  | -             | 1             | -  |

| vol = -46dB<br>vol = -47dB | 1                                                   | 0  | 0  | 1  | 0  | 1  | 0             | _ |                        | 0  | 0  | 0  | 1  | 0             | 1             | 0  |

| vol = -4/dB<br>vol = -48dB | 1                                                   | 0  | 0  | 1  | 0  | 0  | $\frac{1}{0}$ | _ |                        | 0  | 0  | 0  | 1  | 0             | 0             | 1  |

| vol = -48dB<br>vol = -49dB | 1                                                   | 0  | -  | 1  | 1  | 1  | 1             | _ |                        | 0  | 0  | 0  | 1  | 1             | -             | 1  |

|                            | -                                                   | _  | 0  | -  |    | _  |               | _ |                        | -  | -  | -  |    |               | 1             | -  |

| vol = -50dB                | 1                                                   | 0  | 0  | 0  | 1  | 1  | 0             | _ |                        | 0  | 0  | 0  | 0  | 1             | 1             | 0  |

| vol=-51dB                  | 1                                                   | 0  | 0  | 0  | 1  | 0  | 1             | _ |                        | 0  | 0  | 0  | 0  | 1             | 0             | 1  |

| vol=-52dB                  | 1                                                   | 0  | 0  | 0  | 1  | 0  | 0             | _ |                        | 0  | 0  | 0  | 0  | 1             | 0             | 0  |

| vol=-53dB                  | 1                                                   | 0  | 0  | 0  | 0  | 1  | 1             | _ |                        | 0  | 0  | 0  | 0  | 0             | 1             | 1  |

| vol=-54dB                  | 1                                                   | 0  | 0  | 0  | 0  | 1  | 0             | _ |                        | 0  | 0  | 0  | 0  | 0             | 1             | 0  |

| vol=-55dB                  | vol= -55dB 1 0 0 0 0 1   vol= -56dB 1 0 0 0 0 0 0 0 |    |    |    |    |    |               | 0 | 0                      | 0  | 0  | 0  | 0  | 1             |               |    |

| V01300B                    |                                                     | U  | 0  | U  | U  | 0  | U             | _ |                        | 0  | 0  | 0  | 0  | 0             | 0             | 0  |

## •Volume Zero-cross Function Selection

| Control Register<br>Zero-cross Function Termination |   | CF | OSFN | MOD2 | MOD1 | MOD0 | FS1 | FS0 | Τ5 | Τ4 | Т3 | T2 | T1 | T0 |

|-----------------------------------------------------|---|----|------|------|------|------|-----|-----|----|----|----|----|----|----|

| Zero-cross Function Termination                     | 0 | *  | *    | *    | *    | *    | *   | *   | *  | *  | *  | *  | *  | *  |

| Zero-cross Function Operation                       | 1 | *  | *    | *    | *    | *    | *   | *   | *  | *  | *  | *  | *  | *  |

After a rewrite of register, be sure to cancel mute after waiting for  $T_{ZERO}$ .

#### •Carrier Clock Frequency Selection

| Control Register             | ZERO | CF | OSFN | MOD2 | MOD1 | MOD0 | FS1 | FS0 | Τ5 | T4 | Т3 | T2 | T1 | T0 |

|------------------------------|------|----|------|------|------|------|-----|-----|----|----|----|----|----|----|

| Carrier Frequency $=$ 524kHz | *    | 0  | *    | *    | *    | *    | *   | *   | *  | *  | *  | *  | *  | *  |

| Carrier Frequency=466kHz     | *    | 1  | *    | *    | *    | *    | *   | *   | *  | *  | *  | *  | *  | *  |

After rewrite of register, be sure to cancel mute after waiting for  $T_{CF}$ .

## •Over Sampling Filter Function Selection

| Control Register                 | ZERO | CF | OSFN | MOD2 | MOD1 | MOD0 | FS1 | FS0 | 75 | T4 | Т3 | Τ2 | T1 | T0 |

|----------------------------------|------|----|------|------|------|------|-----|-----|----|----|----|----|----|----|

| Over Sampling Filter Operation   | *    | *  | 0    | *    | *    | *    | *   | *   | *  | *  | *  | *  | *  | *  |

| Over Sampling Filter Termination | *    | *  | 1    | *    | *    | *    | *   | *   | *  | *  | *  | *  | *  | *  |

After a rewrite of register, be sure to cancel mute after waiting for T<sub>OSFN</sub>.

### •DAC Input Format Selection

| Control Register | ZERO | CF | OSFN | MOD2 | MOD1 | MOD0 | FS1 | FS0 | T5 | T4 | T3 | T2 | T1 | T0 |

|------------------|------|----|------|------|------|------|-----|-----|----|----|----|----|----|----|

| MODE1            | *    | *  | *    | 0    | 0    | 0    | *   | *   | *  | *  | *  | *  | *  | *  |

| MODE2            | *    | *  | *    | 0    | 0    | 1    | *   | *   | *  | *  | *  | *  | *  | *  |

| MODE3            | *    | *  | *    | 0    | 1    | 0    | *   | *   | *  | *  | *  | *  | *  | *  |

| MODE4            | *    | *  | *    | 0    | 1    | 1    | *   | *   | *  | *  | *  | *  | *  | *  |

| MODE5            | *    | *  | *    | 1    | 0    | 0    | *   | *   | *  | *  | *  | *  | *  | *  |

| MODE6            | *    | *  | *    | 1    | 0    | 1    | *   | *   | *  | *  | *  | *  | *  | *  |

| MODE7            | *    | *  | *    | 1    | 1    | 0    | *   | *   | *  | *  | *  | *  | *  | *  |

| MODE8            | *    | *  | *    | 1    | 1    | 1    | *   | *   | *  | *  | *  | *  | *  | *  |

After a rewrite of register, be sure to cancel mute after waiting for  $T_{MOD}$ .

## Over Sampling Mode Selection

| Control Register | ZERO | CF | OSFN | MOD2 | MOD1 | MOD0 | FS1 | FSO | T5 | T4 | T3 | T2 | $\mathbf{II}$ | TO |

|------------------|------|----|------|------|------|------|-----|-----|----|----|----|----|---------------|----|

| 4x Mode          | *    | *  | *    | *    | *    | *    | 0   | 0   | *  | *  | *  | *  | *             | *  |

| 2x Mode          | *    | *  | *    | *    | *    | *    | 0   | 1   | *  | *  | *  | *  | *             | *  |

| 1x Mode          | *    | *  | *    | *    | *    | *    | 1   | 0   | *  | *  | *  | *  | *             | *  |

| Auto Mode        | *    | *  | *    | *    | *    | *    | 1   | 1   | *  | *  | *  | *  | *             | *  |

After a rewrite of register, be sure to cancel mute after waiting for  $T_{FS}$ .

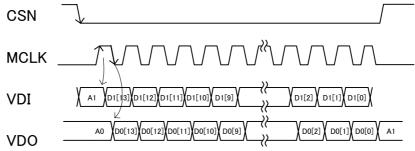

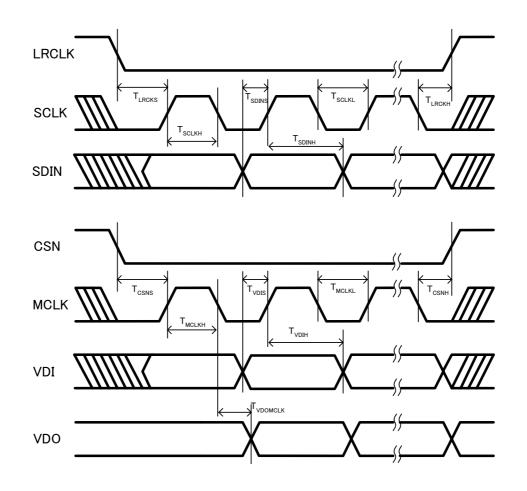

## ■MPU Interface Function

By using the following three terminals "CSN, MCLK, and VDI", data is written into Volume register and Control register. In case of writing data in the Control register, be sure to set mute to Volume register in advance. After a write of Control register or after the given time ( $T_{ZERO}$ ,  $T_{CF}$ ,  $T_{OSFN}$ ,  $T_{MOD}$ , and  $T_{FS}$ ), be sure to cancel mute condition.

## Input Format

Please input the data of each 14-bit register into a VDI terminal in MSB first following address bits. The data input from VDI terminal is taken into internal shift register at the rising edge of MCLK terminal when CSN terminal is "L." The data input into shift register is written into the register of the appointed address at the rising edge of CSN terminal. All the values of registers after a power up are set to "0."

After a power supply starting, the MPU interface works after passing over a serial access prohibition time ( $T_{PUP}$ ).

Be sure to perform a power supply staring first, and then perform a write of the data to a register after a serial access prohibition time  $(T_{PUP})$ .

Here, A1 and D1 [13:0] indicates a register to update and data. In addition, A0 and D0 [13:0] indicates a data input into VDI terminal before 16-clock.

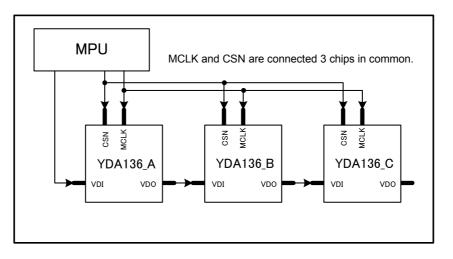

### Daisy-chain

Multiple Daisy-chain connections for multi-channel system are available in YDA136. For example, 6ch system can be realized by connecting three YDA136 with Daisy-chain connection.

By connecting a VDO terminal of first YDA136 to VDI terminal of the second YDA136; and then, connecting a VDO output of second YDA136 to a VDI terminal of the third YDA136, it becomes available to control those three YDA136 simultaneously without a complex addressing.

The data in which it overflowed from the internal 15-bit shift register among the data inputted into each VDI terminal of YDA136 is output from a VDO terminal synchronizing with falling edge of a MCLK terminal.

By setting CSN terminal to "L" during the number of  $YDA136 \times 15$ -clock which daisy-chain connection was made, an input data is taken into each shift register of YDA136.

Then, writing is simultaneously performed to a volume register (control register) from the shift register of all YDA136 connected to the daisy-chain by setting the CSN terminal of YDA136 to "H."

## ■DAC Function

YDA136 has a 24-bit×2ch of DAC.

The DAC supports the following eight kinds of sampling frequencies (Fs), and it has an over sampling filter corresponding to each sampling frequencies.

32kHz, 44.1kHz, 48kHz, 64kHz, 88.4kHz, 96kHz, 176.4kHz, 192kHz The output full-scale of this DAC is 1Vrms.

## •DAC Interface

Be sure to input a digital audio signal from the following three terminals, SDIN, LRCLK, and SCLK. DAC interface of YDA136 supports the seven DAC input formats.

Be sure to set up control registers, MOD2, MOD1, and MOD0, and then select a DAC input format to use.

When using the YDA136 as Digital Audio Signal mode, be sure not to stop a SCLK signal except when electronic volume is mute, protection reset mode, or hard mute mode.

| DAC Input Format                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE1(16bit) MODE2(20bit) MODE3(24bit)                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                 |

| LRCLK / Left channel // Right channel                                                                                                                                                                                                                                                                                                                           |

| A SDIN bit is sampled by the rising edge of SCLK.<br>When LRCLK is "H", be sure to input data for Left channel by right justified.<br>When LRCLK is "L", be sure to input data for Right channel by right justified.<br>SDIN data is written into a DAC data register by the rising edge of LRCLK.<br>64-clock for one-word.                                    |

| MODE4(16bit) MODE5(20bit) MODE6(24bit)                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                 |

| LRCLK Left channel                                                                                                                                                                                                                                                                                                                                              |

| A SDIN bit is sampled by the rising edge of SCLK.<br>When LRCLK is "L", be sure to input data for Left channel in left justified with a vacant bit.<br>When LRCLK is "H", be sure to input data for Right channel in left justified with a vacant bit.<br>SDIN data is written into a DAC data register by the falling edge of LRCLK.<br>64-clock for one-word. |

| MODE7                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                 |

| LRCLK / Left channel //                                                                                                                                                                                                                                                                                                                                         |

| A SDIN bit is sampled by the rising edge of SCLK.<br>When LRCLK is "H", be sure to input data for Left channel by right justified.<br>When LRCLK is "L", be sure to input data for Right channel by right justified.<br>SDIN data is written into a DAC data register by the rising edge of LRCLK.<br>64-clock for one-word.                                    |

| MODE8<br>Analog Audio Signal Input Mode                                                                                                                                                                                                                                                                                                                         |

## Over Sampling Filter

Be sure to set up the Over Sampling mode according to a sampling frequency (Fs) of audio signals to input. Over sampling filter mode can be set up by FS1 and FS0 in the control register.

In addition, an over sampling filter can be bypassed by the setting of control register OSF.

When Fs is 32kHz, 44.1kHz or 48kHz When Fs is 64kHz, 88.2kHz, or 96kHz : Sets up to the 4x mode.

When Fs is 176.4kHz or 192kHz

: Sets up to the 2x mode. : Sets up to the 1x mode.

When it is set as Auto mode, the above mentioned over sampling modes are set up by detecting a sampling frequency (Fs) of audio signal which was input.

## ■Volume Function

YDA136 has the electronic volume which can be set up in the range from +6dB to -73dB by 1dB step.

By inputting an analog signal from AIL (AIR) terminal, and attenuating with the set up volume value, this electronic volume outputs a differential analog signal from an OPL (OPR) terminal and OML (OMR) terminal.

Non-inverted signal from OPL (OPR) terminal and inverted signal from OML (OMR) terminal is output.

The maximum input level is 1Vrms and the maximum output level is 1Vrms.

Be sure to set a volume value to a volume register through a MPU serial data interface.

Moreover, in order to suppress the noise at the time of volume value change, a mode (Zero-cross mode) which changes a volume value when an output signal carries out a zero-cross, is provided as an option.

### Volume Register

D [13:7] of a volume register shows the volume value of R channels, and D [6:0] shows the volume value of L channels. "1111111" and from "0101110" to "0000000" becomes mute among each volume value.

At this time, a DAC output signal turns into a non-signal irrespective of an input.

## Zero-cross Mode

This is the volume change mode, which reduces the noise generated at the time of change of the volume value of electronic volume.

When this mode is selected, the volume value is changed under the following conditions.

- At the time of an audio signal carries out a Zero-cross

- After the volume change is set up

- After the volume value setting time (T<sub>ZEROWAIT</sub>)

When not selected, the volume is changed regardless of the input after the volume setting.

By ZERO of a control register, Zero-cross mode can be set.

## Digital Amplifier Function

YDA136 has a 2-channel differential analog signal input digital amplifier controller.

This digital amplifier controller consists of High-Side and Low-Side PowerMOSFET drivers and a PWM circuit.

By combining the two sets of Pch/Nch PowerMOSFET in each channel, a digital amplifier (60W to 100W) can be configured.

To each PowerMOSFET driver, it is possible to set up an off-time individually, and it can be set as the optimal driver according to PowerMOSFET to be used.

AM intermodulation can be performed with AM reception interference reduction function.

Moreover, it can be optimized to the digital amplifier which has a lower distortion by adding a filter element to a PWM circuit.

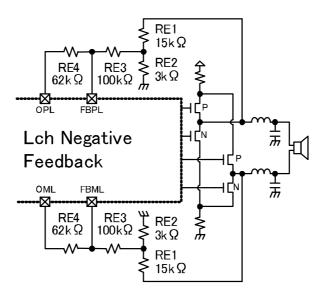

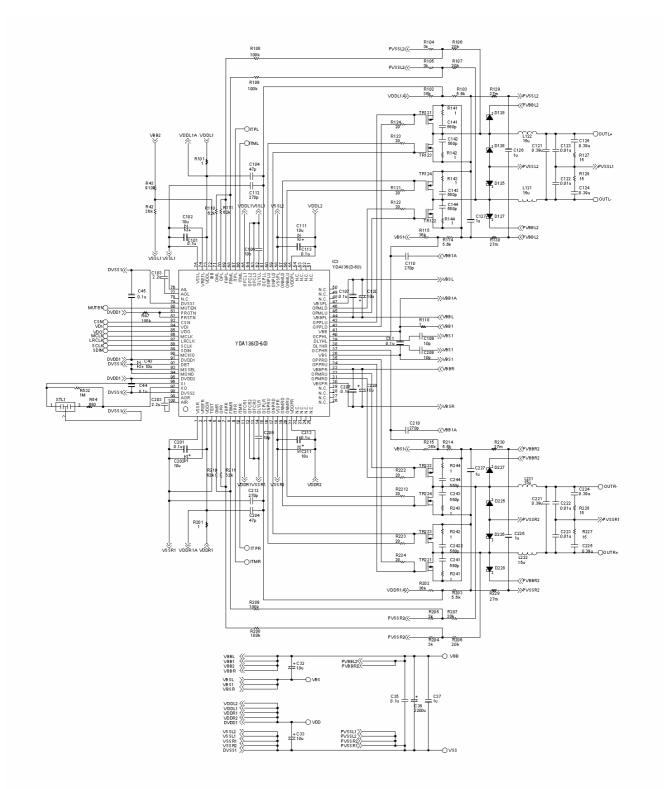

## •Gain Setup Method

The gain of digital amplifier can be set up by external resistance (RE1 to RE4).

The gain of digital amplifier can be calculated with the following formula.

$$Av(dB) = 20 \cdot \log\left(\frac{RE1 \cdot RE2 + RE2 \cdot RE3 + RE1 \cdot RE3}{RE2 \cdot (RE4 + 400\Omega)}\right)$$

However, be sure to set RE4 as more than  $10k_{\Omega}$  according to the capability of a built-in operational amplifier.

### •Characteristic Improvement by External Filter Element Connection

Although it is possible to realize high performance digital amplifier by the PWM circuit, by adding resistor and a capacitor between DBPL(FBPR) and ITPL (ITPR), and between FBML (FBMR) and ITML (ITMR), it is possible to optimize a circuit further and to improve distortion rate.

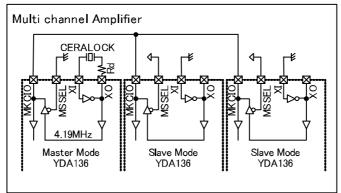

## Clock Input

YDA136 operates synchronizing with 4.19MHz clock.

Be sure to connect a 4.16MHz CERALOCK or to supply a clock to YDA136 from the outside.

Be sure to always supply a clock except protection reset mode and hard mute mode.

When using a CERALOCK, be sure to set MSSEL terminal to "L" and to set YDA136 to a master mode.

In case of supplying a clock from the outside, be sure to set MSSL terminal to "H" and to set YDA136 to a slave mode.

#### Master mode

Be sure to set MSSEL terminal to "L." Connects CELALOCK to XI and XO terminal. Be sure to set the oscillation frequency to 4.19MHz. At this time, a master clock (4.19MHz) is output from a MCKIO terminal. Slave mode Be sure to set MSSEL terminal to "H." Be sure to input a master clock (4.19MHz) into a MCKIO terminal.

At this time, be sure to set XI terminal to "L" and set XO terminal to open state.

When making a multi channel amplifier by using multiple YDA136, a system with little interference between channels can be constituted by using one YDA136 in master mode, and using the remainder in slave mode as shown in the following figure.

### •AM Reception Interference Reduction Function

YDA136 outputs the pulse made by modulating the career clock, which is made by dividing the input master clock. In order to reduce cross talk caused by the coincidence between harmonics of the output pulse and AM radio frequency, YDA136 has the changing (frequency hopping) function of two carrier clock frequencies. A carrier clock frequency can be chosen by the control register CF.

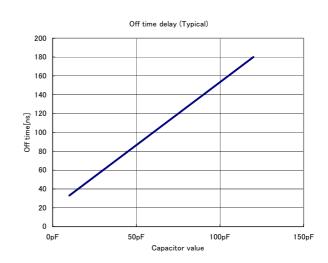

### Off-time Setup Function

A setup of an off-time is individually possible for YDA136 to the High-Side driver and Low-Side driver of Lch and each Rch.

Off-time adjustment of the Low-Side driver of Lch and each Rch is possible by the capacitor that is connected to a

DLYLL terminal and a DLYLR terminal.

Moreover, off-time adjustment of the High-Side driver of Lch and each Rch is possible by the capacitor connected to a DLYHL terminal and a DLYHR terminal.

Relation between capacitance value of the capacitor and the relation of an off-time is shown in the figure.

(Under characteristic adjustment)

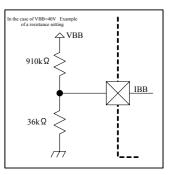

## •IBB Terminal Setting

In the PWM circuit, the IBB terminal is used and VBB power supply voltage is feedbacked. Simultaneously, under voltage detection of VBB power supply voltage is performed by monitoring the voltage of the terminal.

After making 1.5V by dividing VBB voltage with resistors, an then be sure to input it into IBB terminal.

Set for the voltage of the IBB terminal not to become 1.6V or more even if the VBB voltage moves.

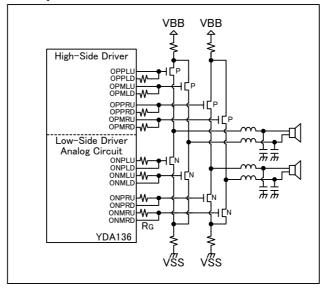

#### PowerMOSFET Drive Function

Since it is BTL connection digital amplifier, external connection of two sets per channel of Pch and Nch PowerMOSFET is made.

A High-Side driver output is connected to Pch PowerMOSFET, and a Low-Side driver output is connected to Nch PowerMOSFET as shown below.

| Non-inverted side Pch PowerMOSFE | T: Be sure to connect to OPPLU and OPPLD (OPPRU, OPPRD).   |

|----------------------------------|------------------------------------------------------------|

|                                  | (High-Side Driver Output)                                  |

| Non-inverted side Nch PowerMOSFI | ET : Be sure to connect to ONPLU and ONPLD (ONPRU, ONPRD). |

|                                  | (Low-Side Driver Output)                                   |

| Inverted side Pch PowerMOSFET    | : Be sure to connect to OPMLU and OPMLD (OPMRU, OPMRD).    |

|                                  | (High-Side Driver Output)                                  |

| Inverted side Nch PowerMOSFET    | : Be sure to connect to ONMLU and ONMLD (ONMRU,ONMRD)      |

|                                  | (Low-Side Driver Output)                                   |

There are two output terminals to one PowerMOSFET, and they mean the pull-up output and the pull-down output, respectively.

By connecting gate resistor (RG) between each driver output and PowerMOSFET, slew-rate of both pull-up and pull-down side separately.

In the example of peripheral circuit connection, resistor (RG) of  $20 \Omega$  is connected with the pull-down side output of Pch PowerMOSFET and the pull-up side output of Nch PowerMOSFET.

In addition, total amount of electric charges (Qg) of gates in PowerMOSFET, which is used by connecting to YDA136, should be 20nC or less (Vgs=5V).

## ■Protect Function

## •Over Current Detection Function

YDA136 has a function to perform an over current protection by detecting a voltage drop of the current detection resistor connected to the source side of PowerMOSFET.

When the voltage of an over-current detection terminal fulfills the following conditions, it judges that it is in an over-current condition, and becomes over-current detection mode, and then a circuit is protected.

| Voltage to be monitored                                                                       | Over-current detection mode threshold |

|-----------------------------------------------------------------------------------------------|---------------------------------------|

| Low-Side over-current detection terminal (OCPLL, OCPLR) Voltage                               | < V <sub>OC2</sub>                    |

| High-Side over-current detection terminal (OCPHL, OCPHR) Voltage and VBB Potential difference | > V <sub>OC1</sub>                    |

In the example of peripheral circuit connection, the following four over-current conditions are detected, and then it becomes an over-current detection mode.

- A condition in which signals after LC filter and VSS power supply is shorted.

- A condition in which signals after LC filter of non-inverted side and signals after LC filter of inverted side is shorted.

- A condition in which one side of a speaker was connected to LC filter, and another side of a speaker is shorted to the VSS power supply.

In over-current detection mode, PROTN terminal is set to "L", simultaneously it turns off all PowerMOSFET (hard mute) and protects a circuit.

After it is made to over-current detection mode, even if an over-current condition is canceled, it is not canceled but is held as it is.

Over-current detection mode can be canceled by intercepting a power supply or setting a PRSTN terminal to "L" at once.

### •Power Detection Function

YDA136 monitors the following three kinds voltage.

When which voltage is less than regular voltage, it becomes low voltage detection mode.

| Voltage to be monitored                            | Constant Voltage Detection Mode Threshold |

|----------------------------------------------------|-------------------------------------------|

| IBB Terminal Voltage(It is proportional to the     | V <sub>IB2</sub>                          |

| voltage between $V_{BB}$ and $V_{SS}$ )            |                                           |

| $V_{DD1}$ (Voltage between $V_{BB}$ and $V_{BS}$ ) | $V_{VB2}$                                 |

| $V_{DD2}$ (Voltage between $V_{DD}$ and $V_{SS}$ ) | V <sub>VD2</sub>                          |