# 18–23 GHz GaAs MMIC Power Amplifier

AA022P1-00

#### **Features**

- Single Bias Supply Operation (6 V)

- 14 dB Typical Small Signal Gain

- 24.5 dBm Typical P<sub>1 dB</sub> Output Power at 23 GHz

- 0.25 µm Ti/Pd/Au Gates

- 100% On-Wafer RF and DC Testing

- 100% Visual Inspection to MIL-STD-883 MT 2010

#### **Description**

Alpha's two-stage balanced K band GaAs MMIC power amplifier has a typical P $_{1\ dB}$  of 24.5 dBm with 13 dB associated gain and 11% power added efficiency at 23 GHz. The chip uses Alpha's proven 0.25  $\mu m$  MESFET technology, and is based upon MBE layers and electron beam lithography for the highest uniformity and repeatability. The FETs employ surface passivation to ensure a rugged reliable part with through-substrate via holes and gold-based backside metallization to facilitate a conductive epoxy die attach process. All chips are screened for small signal S-parameters and power characteristics prior to shipment for guaranteed performance. A broad range of applications exist in both the high reliability and commercial areas where high power and gain are required.

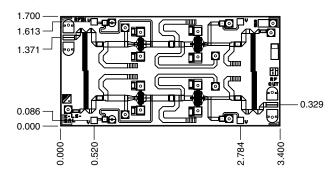

## **Chip Outline**

Dimensions indicated in mm. All DC (V) pads are  $0.1 \times 0.1 \text{ mm}$  and RF In, Out pads are 0.07 mm wide. Chip thickness = 0.1 mm.

# **Absolute Maximum Ratings**

| Characteristic                          | Value             |  |

|-----------------------------------------|-------------------|--|

| Operating Temperature (T <sub>C</sub> ) | -55°C to +90°C    |  |

| Storage Temperature (T <sub>ST</sub> )  | -65°C to +150°C   |  |

| Bias Voltage (V <sub>D</sub> )          | 7 V <sub>DC</sub> |  |

| Power In (P <sub>IN</sub> )             | 22 dBm            |  |

| Junction Temperature (T <sub>J</sub> )  | 175°C             |  |

# Electrical Specifications at $25^{\circ}$ C ( $V_{DS} = 6$ V)

| Parameter                             | Condition     | Symbol            | Min. | Typ. <sup>2</sup> | Max. | Unit |

|---------------------------------------|---------------|-------------------|------|-------------------|------|------|

| Drain Current (at Saturation)         |               | I <sub>DS</sub>   |      | 300               | 390  | mA   |

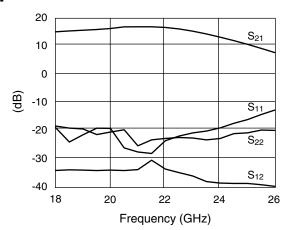

| Small Signal Gain                     | F = 18–23 GHz | G                 | 12   | 14                |      | dB   |

| Input Return Loss                     | F = 18–23 GHz | RL                |      | -15               | -10  | dB   |

| Output Return Loss                    | F = 18–23 GHz | RLO               |      | -17               | -10  | dB   |

| Output Power at 1 dB Gain Compression | F = 23 GHz    | P <sub>1 dB</sub> | 22   | 24.5              |      | dBm  |

| Saturated Output Power                | F = 23 GHz    | P <sub>SAT</sub>  | 24   | 25.5              |      | dBm  |

| Gain at Saturation                    | F = 23 GHz    | G <sub>SAT</sub>  |      | 13                |      | dB   |

| Thermal Resistance <sup>1</sup>       |               | Θ <sub>JC</sub>   |      | 39                |      | °C/W |

<sup>1.</sup> Calculated value based on measurement of discrete FET.

Typical represents the median parameter value across the specified frequency range for the median chip.

# **Typical Performance Data**

Typical Small Signal Performance S-Parameters (V<sub>DS</sub> = 6 V)

#### 26 PIN 25 16 24 12 23 Pout (dBm) 22 10 21 20 8 19 18 17 16 21 22 23 25 18 24 Frequency (GHz)

Output Characteristics as a Function of Frequency and Input Drive Level (V<sub>DS</sub> = 6 V)

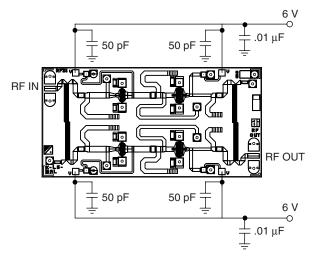

# **Bias Arrangement**

For biasing on, adjust  $V_{DS}$  from zero to the desired value (6 V recommended). For biasing off, reverse the biasing on procedure.

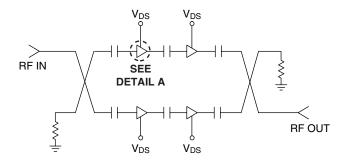

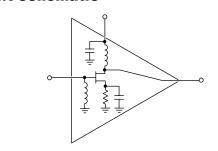

### **Circuit Schematic**

Detail A