### 12-Channel High Voltage Analog Switch

### **Ordering Information**

|                                     | Package Options |        |  |  |  |  |  |

|-------------------------------------|-----------------|--------|--|--|--|--|--|

| $\mathbf{V}_{PP} - \mathbf{V}_{NN}$ | 48-pin TQFP Die |        |  |  |  |  |  |

| 200V                                | HV209FG         | HV209X |  |  |  |  |  |

### **Features**

- HVCMOS technology for high performance

- Operating voltage of up to 200V

- Output On-resistance typically 22Ω

- ☐ Integrated bleed resistors on the outputs

- Very low quiescent power dissipation -10μA

- Low parasitic capacitances

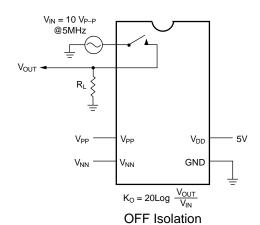

- -58dB typical output off isolation at 5MHz

- 5.0V to 12V CMOS logic circuitry

- Excellent noise immunity

- ☐ Flexible high voltage supplies

### **Absolute Maximum Ratings\***

|                                                  | _                                  |

|--------------------------------------------------|------------------------------------|

| $V_{\rm DD}$ Logic power supply voltage          | -0.5V to +15V                      |

| V <sub>PP</sub> - V <sub>NN</sub> Supply voltage | +220V                              |

| V <sub>PP</sub> Positive high voltage supply     | -0.5V to +200V                     |

| V <sub>NN</sub> Negative high voltage supply     | +0.5V to -200V                     |

| Logic input voltages                             | -0.5V to V <sub>DD</sub> +0.3V     |

| V <sub>SIG</sub> Analog Signal Range             | V <sub>NN</sub> to V <sub>PP</sub> |

| Peak analog signal current/channel               | 3.0A                               |

| Storage temperature                              | -65°C to +150°C                    |

| Power dissipation                                | 1.0W                               |

|                                                  |                                    |

<sup>\*</sup> All voltages are referenced to ground. Absolute maximum ratings are those values which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability.

### **General Description**

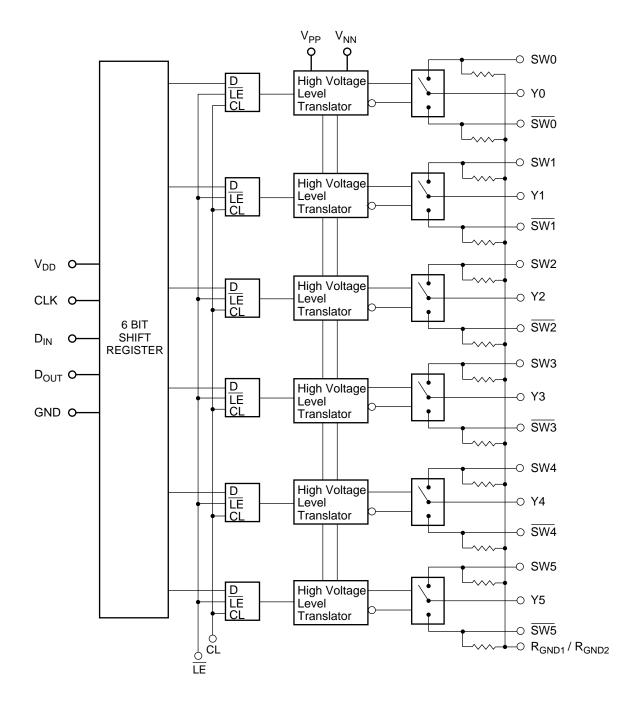

The Supertex HV209 is a 200V low charge injection 12-channel high voltage analog switch configured as 6 SPDT analog switch intended for medical ultrasound applications. Bleed resistors are integrated on the output switches to eliminate charge built up on the piezo electric transducers. The bleed resistors are at a nominal value of  $35 \mathrm{K}\Omega$ . Using HVCMOS technology, this device combines high voltage bilateral DMOS switches and low power CMOS logic to provide efficient control of high voltage analog signals. The outputs are configured as single pole double throw analog switches. Data is shifted into a 6-bit shift register using an external clock. The LE latches the shift register data into the individual switch latches. A logic high connects a switch common  $Y_X$  to  $SW_X$ . A logic low connects  $Y_X$  to  $SW_X$ . A logic high connects all switches to  $\overline{SW_X}$  simultaneously.

## **Electrical Characteristics**

**DC Characteristics** (over recommended operating conditions unless otherwise noted)

|                                                 |                   | 0°C  |     | +25°C |      | +70°C |      | T   | T     |                                                                    |                              |  |

|-------------------------------------------------|-------------------|------|-----|-------|------|-------|------|-----|-------|--------------------------------------------------------------------|------------------------------|--|

| Characteristics                                 | Sym               | min  | max | min   | typ  | max   | min  | max | Units | Test Conditions                                                    |                              |  |

|                                                 |                   |      | 30  |       | 26   | 38    |      | 48  |       | I <sub>SIG</sub> = 5mA                                             | V <sub>PP</sub> = 40V,       |  |

|                                                 |                   |      | 25  |       | 22   | 27    |      | 32  | ] [   | I <sub>SIG</sub> = 200mA                                           | V <sub>NN</sub> = -160V      |  |

| Small Signal Switch (ON)                        | R <sub>ONS</sub>  |      | 25  |       | 22   | 27    |      | 30  | ohms  | I <sub>SIG</sub> = 5mA                                             | V <sub>PP</sub> = 100V,      |  |

| Resistance                                      |                   |      | 18  |       | 18   | 24    |      | 27  | ] [   | I <sub>SIG</sub> = 200mA                                           | V <sub>NN</sub> = -100V      |  |

|                                                 |                   |      | 23  |       | 20   | 25    |      | 30  | ] [   | I <sub>SIG</sub> = 5mA                                             | V <sub>PP</sub> = 190V,      |  |

|                                                 |                   |      | 22  |       | 16   | 25    |      | 27  | ] [   | I <sub>SIG</sub> = 200mA                                           | V <sub>NN</sub> = -10V       |  |

| Small Signal Switch (ON)<br>Resistance Matching | $\Delta R_{ONS}$  |      | 20  |       | 5.0  | 20    |      | 20  | %     | $I_{SW} = 5\text{mA}, V_{PP} = 100\text{V}, V_{NN} = -100\text{V}$ |                              |  |

| Large Signal Switch (ON)<br>Resistance          | R <sub>ONL</sub>  |      |     |       | 15   |       |      |     | ohms  | $V_{SIG} = V_{PP} - 10$                                            | )V, I <sub>SIG</sub> = 1A    |  |

| Output Switch Shunt<br>Resistance               | R <sub>INT</sub>  |      |     | 20    | 35   | 50    |      |     | Kohms | Output switch                                                      | to R <sub>GND</sub>          |  |

| DC Offset Switch Off                            |                   |      | 50  |       |      | 50    |      | 50  | mV    | No Load, R <sub>GND</sub>                                          | ) = 0V                       |  |

| DC Offset Switch On                             |                   |      | 50  |       |      | 50    |      | 50  | mV    | No Load, R <sub>GND</sub>                                          | ) = 0V                       |  |

| Pos. HV Supply Current                          | I <sub>PPQ</sub>  |      |     |       | 10   | 50    |      |     | μΑ    | ALL SWs OFF                                                        |                              |  |

| Neg. HV Supply Current                          | I <sub>NNQ</sub>  |      |     |       | -10  | -50   |      |     | μΑ    | ALL SWs OFF                                                        | •                            |  |

| Pos. HV Supply Current                          | I <sub>PPQ</sub>  |      |     |       | 10   | 50    |      |     | μΑ    | ALL SWs ON I <sub>SW</sub> = 5mA                                   |                              |  |

| Neg. HV Supply Current                          | I <sub>NNQ</sub>  |      |     |       | -10  | -50   |      |     | μΑ    | ALL SWs ON I <sub>SW</sub> = 5mA                                   |                              |  |

| Switch Output<br>Peak Current                   |                   |      | 3.0 |       | 3.0  | 2.0   |      | 2.0 | А     | V <sub>SIG</sub> duty cycle ≤ 0.1%                                 |                              |  |

| Output Switch Frequency                         | f <sub>SW</sub>   |      |     |       |      | 50    |      |     | KHz   | Duty Cycle = 5                                                     | 60%                          |  |

|                                                 |                   |      | 6.5 |       |      | 7.0   |      | 8.0 |       | $V_{PP} = 40V, V_{NN} = -160V$                                     |                              |  |

| I <sub>PP</sub> Supply Current                  | I <sub>PP</sub>   |      | 4.0 |       |      | 5.0   |      | 5.5 | mA    | $V_{PP} = 100V,$<br>$V_{NN} = -100V$                               | 50KHz<br>Output<br>Switching |  |

|                                                 |                   |      | 4.0 |       |      | 5.0   |      | 5.5 |       | $V_{PP} = 190V, V_{NN} = -10V$                                     |                              |  |

|                                                 |                   |      | 6.5 |       |      | 7.0   |      | 8.0 |       | $V_{PP} = 40V, V_{NN} = -160V$                                     | Frequency<br>with no<br>load |  |

| I <sub>NN</sub> Supply Current                  | I <sub>NN</sub>   |      | 4.0 |       |      | 5.0   |      | 5.5 | mA    | $V_{PP} = 100V, V_{NN} = -100V$                                    | - Ioad                       |  |

|                                                 |                   |      | 4.0 |       |      | 5.0   |      | 5.5 |       | $V_{PP} = 190V,$ $V_{NN} = -10V$                                   |                              |  |

| Logic Supply<br>Average Current                 | I <sub>DD</sub>   |      | 4.0 |       |      | 4.0   |      | 4.0 | mA    | $f_{CLK} = 5MHz, V$                                                | / <sub>DD</sub> = 5.0V       |  |

| Logic Supply<br>Quiescent Current               | I <sub>DDQ</sub>  |      | 10  |       |      | 10    |      | 10  | μА    |                                                                    |                              |  |

| Data Out Source Current                         | I <sub>SOR</sub>  | 0.45 |     | 0.45  | 0.70 |       | 0.40 |     | mA    | $V_{OUT} = V_{DD} - 0$                                             | .7V                          |  |

| Data Out Sink Current                           | I <sub>SINK</sub> | 0.45 |     | 0.45  | 0.70 |       | 0.40 |     | mA    | $V_{OUT} = 0.7V$                                                   |                              |  |

| Logic Input Capacitance                         | C <sub>IN</sub>   |      | 10  |       |      | 10    |      | 10  | pF    |                                                                    |                              |  |

## **Electrical Characteristics**

**AC Characteristics** (over operating conditions  $V_{DD} = 5V$ , unless otherwise noted)

| Characteristics                          | Corre                | 0°  | °C  | +25°C |     |     | +70°C |     | Unita | Test Conditions                                    |

|------------------------------------------|----------------------|-----|-----|-------|-----|-----|-------|-----|-------|----------------------------------------------------|

| Characteristics                          | Sym                  | min | max | min   | typ | max | min   | max | Units | rest conditions                                    |

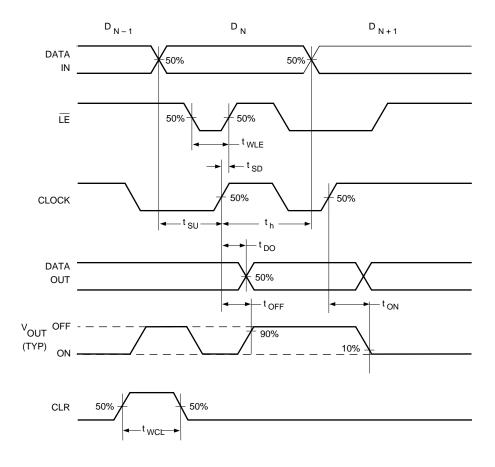

| Set Up Time Before LE Rises              | t <sub>SD</sub>      | 150 |     | 150   |     |     | 150   |     | ns    |                                                    |

| Time Width of LE                         | t <sub>WLE</sub>     | 150 |     | 150   |     |     | 150   |     | ns    |                                                    |

| Clock Delay Time to Data Out             | t <sub>DO</sub>      |     | 150 |       |     | 150 |       | 150 | ns    |                                                    |

| Time Width of CL                         | t <sub>WCL</sub>     | 150 |     | 150   |     |     | 150   |     | ns    |                                                    |

| Set Up Time Data to Clock                | t <sub>SU</sub>      | 15  |     | 15    | 8.0 |     | 20    |     | ns    |                                                    |

| Hold Time Data from Clock                | t <sub>h</sub>       | 35  |     | 35    |     |     | 35    |     | ns    |                                                    |

| Clock Freq                               | f <sub>CLK</sub>     |     | 5.0 |       |     | 5.0 |       | 5.0 | MHz   | 50% duty cycle $f_{DATA} = f_{CLK}/2$              |

| Turn On Time                             | t <sub>ON</sub>      |     | 5.0 |       |     | 5.0 |       | 5.0 | μS    | $V_{SIG} = V_{PP} - 10V,$<br>$R_{L} = 10K\Omega$   |

| Turn Off Time                            | t <sub>OFF</sub>     |     | 5.0 |       |     | 5.0 |       | 5.0 | μS    | $V_{SIG} = V_{PP} - 10V,$<br>$R_{L} = 10K\Omega$   |

|                                          |                      |     | 20  |       |     | 20  |       | 20  |       | V <sub>PP</sub> = 40V,<br>V <sub>NN</sub> = -160V  |

| Maximum V <sub>SIG</sub> Slew Rate       | dv/dt                |     | 20  |       |     | 20  |       | 20  | V/ns  | V <sub>PP</sub> = 100V,<br>V <sub>NN</sub> = -100V |

|                                          |                      |     | 20  |       |     | 20  |       | 20  |       | V <sub>PP</sub> = 190V,<br>V <sub>NN</sub> = -10V  |

| Off Isolation                            | КО                   | -30 |     | -30   | -33 |     | -30   |     | dB    | f = 5MHz,<br>1KΩ//15pF load                        |

|                                          |                      | -58 |     | -58   |     |     | -58   |     | dB    | f = 5MHz, $50Ω$ load                               |

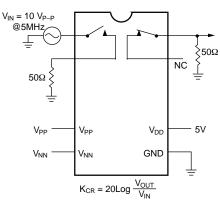

| Switch Crosstalk                         | K <sub>CR</sub>      | -60 |     | -60   | -70 |     | -60   |     | dB    | $f = 5MHz$ , $50\Omega$ load                       |

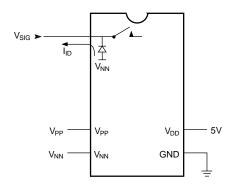

| Output Switch Isolation<br>Diode Current | I <sub>ID</sub>      |     | 300 |       |     | 300 |       | 300 | mA    | 300ns pulse width, 2.0% duty cycle                 |

| Off Capacitance SW to GND                | C <sub>SG(OFF)</sub> | 5.0 | 17  | 5.0   | 12  | 17  | 5.0   | 17  | pF    | 0V, 1MHz                                           |

| On Capacitance SW to GND                 | C <sub>SG(ON)</sub>  | 25  | 50  | 25    | 38  | 50  | 25    | 50  | pF    | 0V, 1MHz                                           |

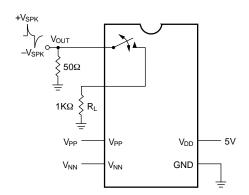

| Positive Output Voltage Spike            | +V <sub>SPK</sub>    |     | 150 |       |     | 150 |       | 150 | mV    | $R_{LOAD} = 50\Omega$                              |

| Negative Output Voltage Spike            | -V <sub>SPK</sub>    |     | 150 |       |     | 150 |       | 150 | mV    | $R_{LOAD} = 50\Omega$                              |

# **Operating Conditions**\*

| Symbol           | Parameter                                       | Value                                        |

|------------------|-------------------------------------------------|----------------------------------------------|

| V <sub>PP</sub>  | Positive high voltage supply <sup>1</sup>       | +40V to V <sub>NN</sub> + 200V               |

| V <sub>NN</sub>  | Negative high voltage supply <sup>1</sup>       | -10V to -160V                                |

| V <sub>DD</sub>  | Logic power supply voltage <sup>1</sup>         | +4.5V to +13.2V                              |

| V <sub>IH</sub>  | High-level input voltage                        | $0.8 V_{DD}$ to $V_{DD}$                     |

| V <sub>IL</sub>  | Low-level input voltage                         | 0V to 0.2V <sub>DD</sub>                     |

| V <sub>SIG</sub> | Analog signal voltage peak-to-peak <sup>2</sup> | V <sub>NN</sub> +10V to V <sub>PP</sub> -10V |

| T <sub>A</sub>   | Operating free air-temperature                  | 0°C to 70°C                                  |

#### Notes:

- 1 Power up/down sequence is arbitrary except GND must be powered-up first and powered-down last.

- $2~~V_{SIG}$  must be within  $V_{PP}$  and  $V_{NN}$  voltage range or floating during power up/down transition.

### **Truth Table**

|    | IUDI        |    |    |    |    |    |    |                      |     |     |            |     |     |

|----|-------------|----|----|----|----|----|----|----------------------|-----|-----|------------|-----|-----|

|    | Data Inputs |    |    |    |    |    |    |                      |     | Sv  | vitch Stat | es  |     |

| DO | D1          | D2 | D3 | D4 | D5 | LE | CL | Y0                   | Y1  | Y2  | Y3         | Y4  | Y5  |

| L  |             |    |    |    |    | L  | L  | SW0                  |     |     |            |     |     |

| Н  |             |    |    |    |    | L  | L  | SW0                  |     |     |            |     |     |

|    | L           |    |    |    |    | L  | L  |                      | SW1 |     |            |     |     |

|    | Н           |    |    |    |    | L  | L  |                      | SW1 |     |            |     |     |

|    |             | L  |    |    |    | L  | L  |                      |     | SW2 |            |     |     |

|    |             | Н  |    |    |    | L  | L  |                      |     | SW2 |            |     |     |

|    |             |    | L  |    |    | L  | L  |                      |     |     | SW3        |     |     |

|    |             |    | Н  |    |    | L  | L  |                      |     |     | SW3        |     |     |

|    |             |    |    | L  |    | L  | L  |                      |     |     |            | SW4 |     |

|    |             |    |    | Н  |    | L  | L  |                      |     |     |            | SW4 |     |

|    |             |    |    |    | L  | L  | L  |                      |     |     |            |     | SW5 |

|    |             |    |    |    | Н  | L  | L  |                      |     |     |            |     | SW5 |

| Х  | Х           | Х  | Х  | Х  | Х  | Н  | L  | HOLDS PREVIOUS STATE |     |     |            |     |     |

| Х  | Х           | Х  | Х  | Х  | Х  | Х  | Н  | SW0                  | SW1 | SW2 | SW3        | SW4 | SW5 |

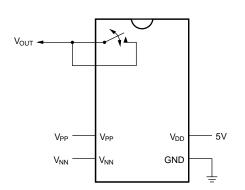

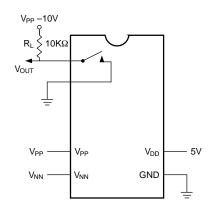

### **Test Circuits**

DC Offset ON/OFF

$T_{ON}/T_{OFF}$  Test Circuit

**Isolation Diode Current**

Crosstalk

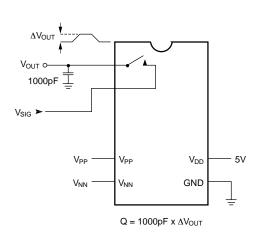

Charge Injection

Output Voltage Spike

# **Logic Timing Waveforms**

## **Block Diagram**

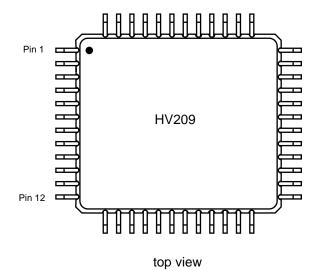

## **Pin Configuration**

### HV209 48-Pin TQFP

| Pin | Function | Pin | Function          |

|-----|----------|-----|-------------------|

| 1   | N/C      | 25  | SW5               |

| 2   | SW0      | 26  | Y5                |

| 3   | Y0       | 27  | SW5               |

| 4   | SW0      | 28  | N/C               |

| 5   | N/C      | 29  | SW3               |

| 6   | SW2      | 30  | Y3                |

| 7   | Y2       | 31  | SW3               |

| 8   | SW2      | 32  | N/C               |

| 9   | N/C      | 33  | SW1               |

| 10  | SW4      | 34  | Y1                |

| 11  | Y4       | 35  | SW1               |

| 12  | SW4      | 36  | N/C               |

| 13  | N/C      | 37  | $R_{GND1}$        |

| 14  | N/C      | 38  | N/C               |

| 15  | N/C      | 39  | $D_OUT$           |

| 16  | $V_{NN}$ | 40  | V <sub>DD</sub>   |

| 17  | N/C      | 41  | D <sub>IN</sub>   |

| 18  | N/C      | 42  | CLR               |

| 19  | N/C      | 43  | LE                |

| 20  | N/C      | 44  | CLK               |

| 21  | $V_{PP}$ | 45  | GND               |

| 22  | N/C      | 46  | N/C               |

| 23  | N/C      | 47  | N/C               |

| 24  | N/C      | 48  | $R_{\text{GND2}}$ |

## **Package Outline**

48-pin TQFP