## **Document Title**

128Kx32-Bit Synchronous Pipelined Burst SRAM

## **Revision History**

| <u>Rev.No.</u> | History                                                                                      | Draft Date      | <u>Remark</u> |

|----------------|----------------------------------------------------------------------------------------------|-----------------|---------------|

| 1.0            | Initial draft                                                                                | May . 19. 1998  | Final         |

| 2.0            | change toyo from 8.5ns to 10.0ns.<br>Modify Rev No. from 0.0 to 1.0.                         | June . 02. 1998 | Final         |

| 3.0            | Modify DC characteristics(Input Leakage Current test Conditions) form VDD=Vss to VDD to Max. | June. 08. 1998  | Final         |

| 4.0            | Add VDDQ Supply voltage( 2.5V )                                                              | Dec. 02. 1998   | Final         |

| 5.0            | Remove 119BGA(7x17 Ball Grid Array Package) .                                                | Feb. 10. 1999   | Final         |

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any questions, please contact the SAMSUNG branch office near your office, call or contact Headquarters.

## 128Kx32-Bit Synchronous Pipelined Burst SRAM

#### FEATURES

- Synchronous Operation.

- 2 Stage Pipelined operation with 4 Burst.

- On-Chip Address Counter.

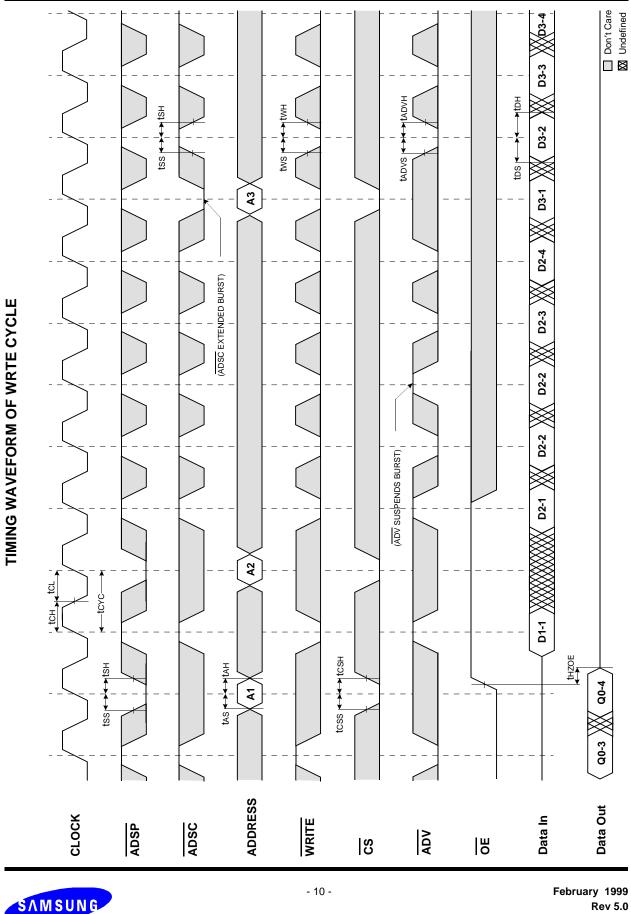

- Self-Timed Write Cycle.

- On-Chip Address and Control Registers.

- VDD= 3.3V+0.3V/-0.165V Power Supply.

- VDDQ Supply Voltage 3.3V+0.3V/-0.165V for 3.3V I/O or 2.5V+0.4V/-0.125V for 2.5V I/O.

- 5V Tolerant Inputs Except I/O Pins.

- Byte Writable Function.

- Global Write Enable Controls a full bus-width write.

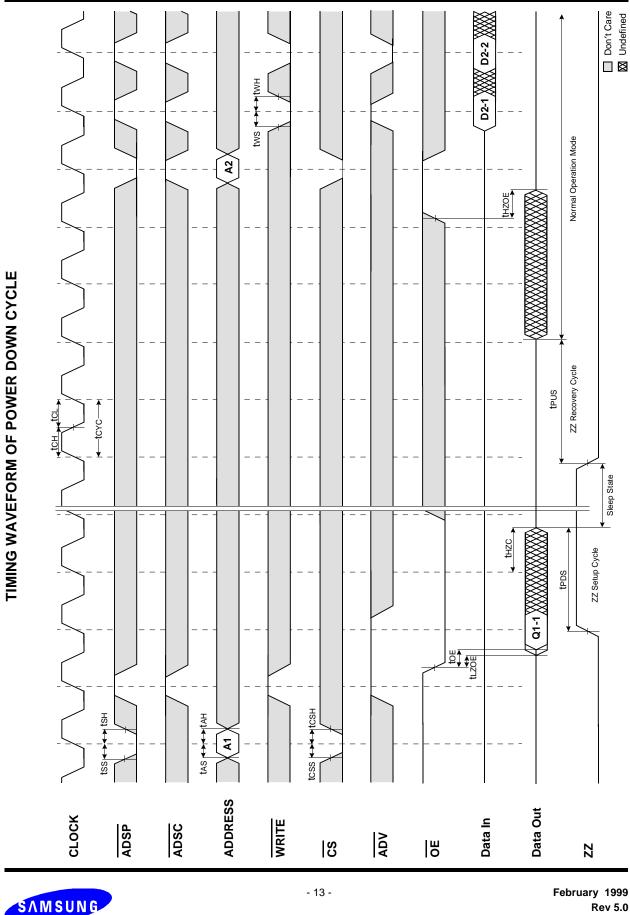

- Power Down State via ZZ Signal.

- LBO Pin allows a choice of either a interleaved burst or a linear burst.

- Three Chip Enables for simple depth expansion with No Data Contention ; 2cycle Enable, 1cycle Disable.

- Asynchronous Output Enable Control.

- ADSP, ADSC, ADV Burst Control Pins.

- TTL-Level Three-State Output.

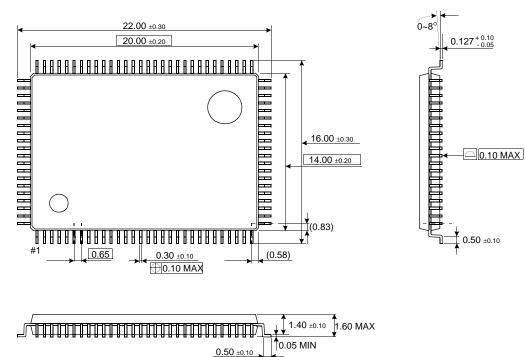

- 100-TQFP-1420A

## FAST ACCESS TIMES

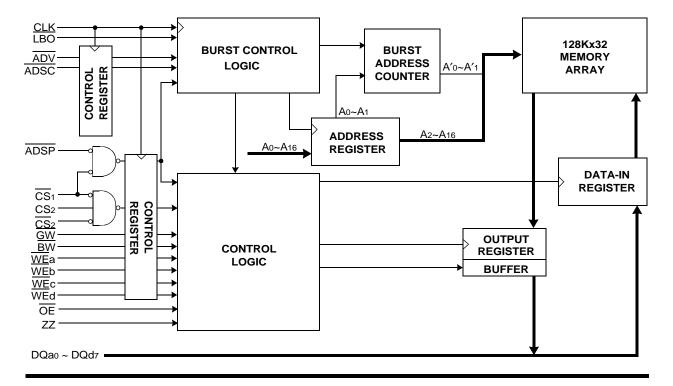

LOGIC BLOCK DIAGRAM

| PARAMETER                 | Symbol | 60  | 67  | 72  | 10  | Unit |

|---------------------------|--------|-----|-----|-----|-----|------|

| Cycle Time                | tcyc   | 6.0 | 6.7 | 7.2 | 10  | ns   |

| Clock Access Time         | tCD    | 3.5 | 3.8 | 4.0 | 4.5 | ns   |

| Output Enable Access Time | tOE    | 3.5 | 3.8 | 4.0 | 4.5 | ns   |

#### **GENERAL DESCRIPTION**

The KM732V789 is a 4,194,304-bit Synchronous Static Random Access Memory designed for high performance second level cache of Pentium and Power PC based System.

It is organized as 128K words of 32bits and integrates address and control registers, a 2-bit burst address counter and added some new functions for high performance cache RAM applications; GW, BW, LBO, ZZ. Write cycles are internally self-timed and synchronous.

Full bus-width write is done by  $\overline{GW}$ , and each byte write is performed by the combination of  $\overline{WEx}$  and  $\overline{BW}$  when  $\overline{GW}$  is high. And with  $\overline{CS_1}$  high,  $\overline{ADSP}$  is blocked to control signals.

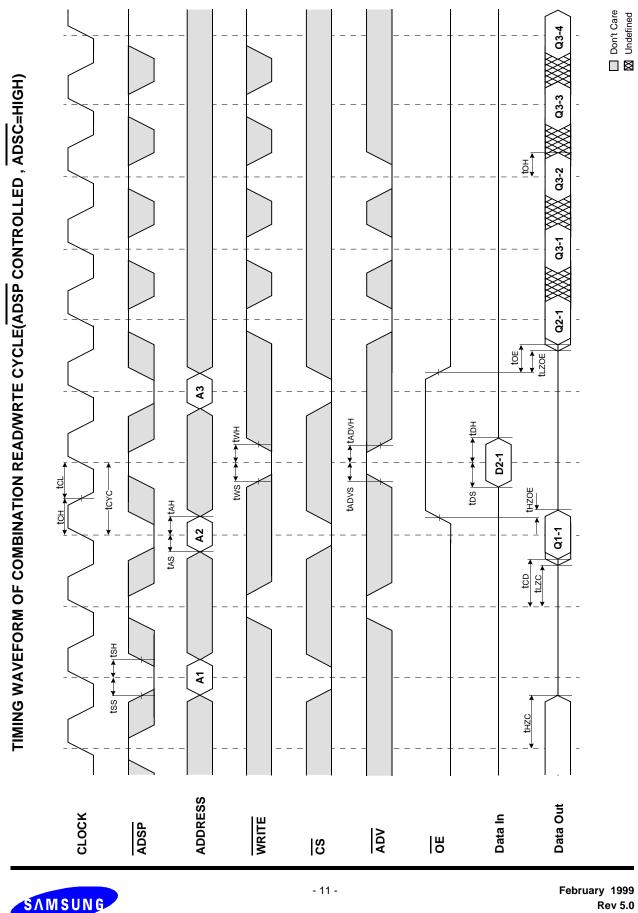

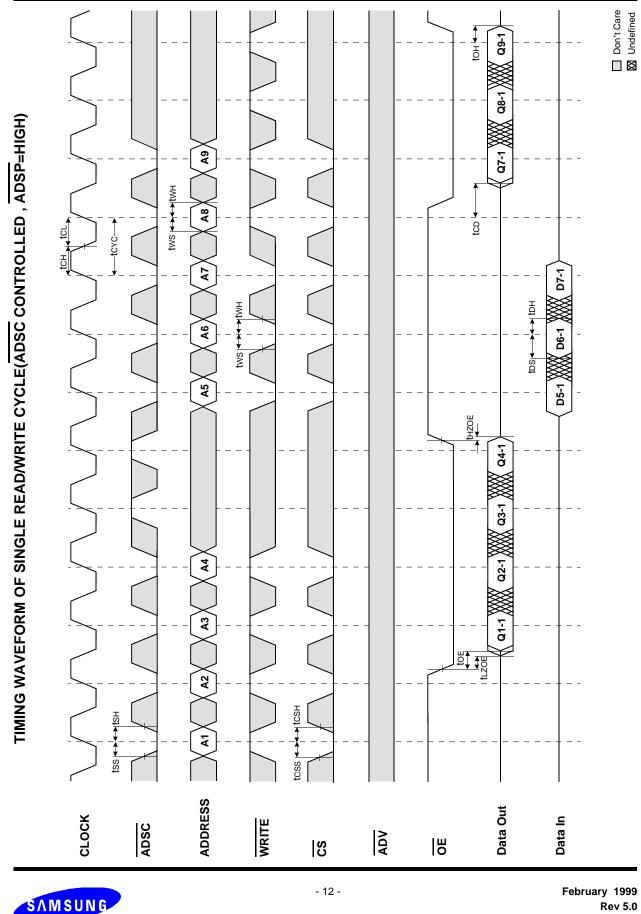

Burst cycle can be initiated with either the address status processor( $\overline{ADSP}$ ) or address status cache controller( $\overline{ADSC}$ ) inputs. Subsequent burst addresses are generated internally in the system's burst sequence and are controlled by the burst address advance( $\overline{ADV}$ ) input.

LBO pin is DC operated and determines burst sequence(linear or interleaved).

ZZ pin controls Power Down State and reduces Stand-by current regardless of CLK.

The KM732V789 is fabricated using SAMSUNG's high performance CMOS technology and is available in a 100pin TQFP package. Multiple power and ground pins are utilized to minimize ground bounce.

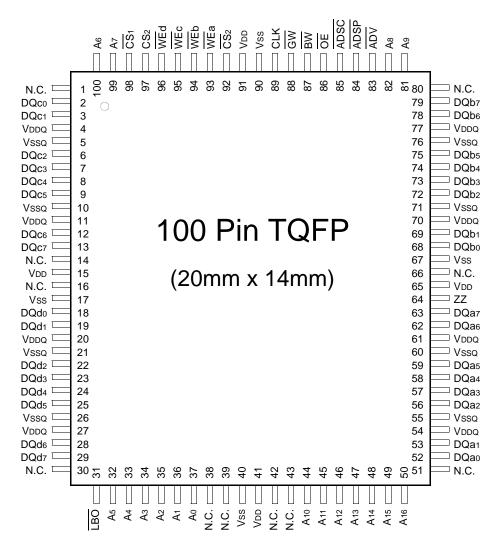

#### PIN CONFIGURATION(TOP VIEW)

#### **PIN NAME**

| SYMBOL                      | PIN NAME                  | TQFP PIN NO.       | SYMBOL  | PIN NAME            | TQFP PIN NO.            |

|-----------------------------|---------------------------|--------------------|---------|---------------------|-------------------------|

| A0 - A16                    | Address Inputs            | 32,33,34,35,36,37, | Vdd     | Power Supply(+3.3V) | 15,41,65,91             |

|                             |                           | 44,45,46,47,48,49, | Vss     | Ground              | 17,40,67,90             |

|                             |                           | 50,81,82,99,100    | N.C.    | No Connect          | 1,14,16,30,38,39,42,43  |

| ADV                         | Burst Address Advance     | 83                 |         |                     | 51,66,80                |

| ADSP                        | Address Status Processor  | 84                 | DQao~a7 | Data Inputs/Outputs | 52,53,56,57,58,59,62,63 |

| ADSC                        | Address Status Controller | 85                 | DQbo~b7 |                     | 68,69,72,73,74,75,78,79 |

| CLK<br>CS1                  | Clock                     | 89                 | DQc0~c7 |                     | 2,3,6,7,8,9,12,13       |

| CS1                         | Chip Select               | 98                 | DQdo~d7 |                     | 18,19,22,23,24,25,28,29 |

| CS2<br>CS2                  | Chip Select               | 97                 |         |                     |                         |

| CS <sub>2</sub>             | Chip Select               | 92                 | Vddq    | Output Power Supply | 4,11,20,27,54,61,70,77  |

| $\overline{WE}x(x=a,b,c,d)$ | Byte Write Inputs         | 93,94,95,96        |         | (2.5V or 3.3V)      |                         |

| OE                          | Output Enable             | 86                 | Vssq    | Output Ground       | 5,10,21,26,55,60,71,76  |

| GW<br>BW                    | Global Write Enable       | 88                 |         |                     |                         |

| BW                          | Byte Write Enable         | 87                 |         |                     |                         |

| ZZ                          | Power Down Input          | 64                 |         |                     |                         |

| LBO                         | Burst Mode Control        | 31                 |         |                     |                         |

## FUNCTION DESCRIPTION

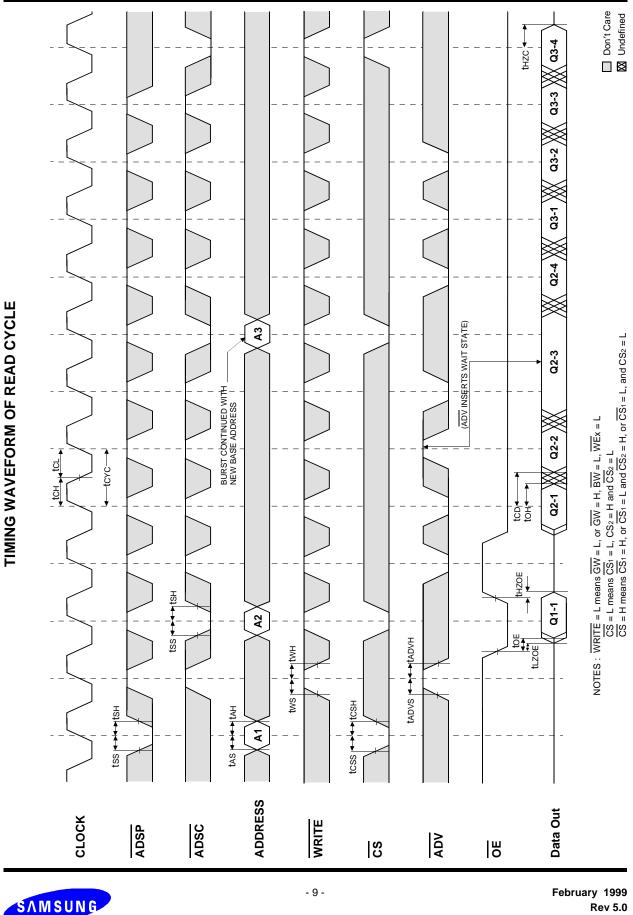

The KM732V789 is a synchronous SRAM designed to support the burst address accessing sequence of the P6 and Power PC based microprocessor. All inputs (with the exception of  $\overline{OE}$ , LBO and ZZ) are sampled on rising clock edges. The start and duration of the burst access is controlled by  $\overline{ADSC}$ ,  $\overline{ADSP}$  and  $\overline{ADV}$  and chip select pins.

The accesses are enabled with the chip select signals and output enabled signals. Wait states are inserted into the access with ADV.

When ZZ is pulled high, the SRAM will enter a Power Down State. At this time, internal state of the SRAM is preserved. When ZZ returns to low, the SRAM normally operates after 2cycles of wake up time. ZZ pin is pulled down internally.

Read cycles are initiated with ADSP (regardless of WEx and ADSC) using the new external address clocked into the on-chip address register whenever ADSP is sampled low, the chip selects are sampled active, and the output buffer is enabled with OE. In read operation the data of cell array accessed by the current address, registered in the Data-out registers by the positive edge of CLK, are carried to the Data-out buffer by the next positive edge of CLK. The data, registered in the Data-out buffer, are projected to the output pins. ADV is ignored on the clock edge that samples ADSP asserted, but is sampled on the subsequent clock edges. The address increases internally for the next access of the burst when WEx are sampled High and ADV is sampled low. And ADSP is blocked to control signals by disabling CS1.

All byte write is done by  $\overline{GW}$  (regadless of  $\overline{BW}$  and  $\overline{WEx}$ .), and each byte write is performed by the combination of  $\overline{BW}$  and  $\overline{WEx}$  when  $\overline{GW}$  is high.

Write cycles are performed by disabling the output buffers with  $\overline{OE}$  and asserting  $\overline{WEx}$ .  $\overline{WEx}$  are ignored on the clock edge that samples ADSP low, but are sampled on the subsequent clock edges. The output buffers are disabled when  $\overline{WEx}$  are sampled Low(regaedless of  $\overline{OE}$ ). Data is clocked into the data input register when  $\overline{WEx}$  sampled Low. The address increases internally to the next address of burst, if both  $\overline{WEx}$  and  $\overline{ADV}$  are sampled Low. Individual byte write cycles are performed by any one or more byte write enable signals( $\overline{WEa}$ ,  $\overline{WEb}$ ,  $\overline{WEc}$  or  $\overline{WEd}$ ) sampled low. The  $\overline{WEa}$  control DQao ~ DQa7 ,  $\overline{WEb}$  controls DQbo ~ DQb7 ,  $\overline{WEc}$  controls DQco ~ DQc7 , and  $\overline{WEd}$  control DQdo ~ DQd7 . Read or write cycle may also be initiated with  $\overline{ADSC}$ , instead of  $\overline{ADSP}$ . The differences between cycles initiated with  $\overline{ADSC}$  and  $\overline{ADSP}$  as are follows;

$\overline{\text{ADSP}}$  must be sampled high when  $\overline{\text{ADSC}}$  is sampled low to initiate a cycle with  $\overline{\text{ADSC}}$ . WEx are sampled on the same clock edge that sampled  $\overline{\text{ADSC}}$  low(and  $\overline{\text{ADSP}}$  high).

Addresses are generated for the burst access as shown below, The starting point of the burst sequence is provided by the external address. The burst address counter wraps around to its initial state upon completion. The burst sequence is determined by the state of the  $\overline{\text{LBO}}$  pin. When this pin is Low, linear burst sequence is selected. When this pin is High, Interleaved burst sequence is selected.

| LBO PIN        | HIGH          | Case 1     |    | Cas        | Case 2 |            | Case 3 |            | Case 4 |  |

|----------------|---------------|------------|----|------------|--------|------------|--------|------------|--------|--|

| LBOTIN         |               | <b>A</b> 1 | Ao | <b>A</b> 1 | Ao     | <b>A</b> 1 | Ao     | <b>A</b> 1 | Ao     |  |

| Fi             | First Address |            | 0  | 0          | 1      | 1          | 0      | 1          | 1      |  |

|                |               | 0          | 1  | 0          | 0      | 1          | 1      | 1          | 0      |  |

|                | $\downarrow$  |            | 0  | 1          | 1      | 0          | 0      | 0          | 1      |  |

| Fourth Address |               | 1          | 1  | 1          | 0      | 0          | 1      | 0          | 0      |  |

#### **BURST SEQUENCE TABLE**

| LBO PIN        | LOW | Case 1     |    | Case 2     |    | Case 3     |    | Case 4     |    |

|----------------|-----|------------|----|------------|----|------------|----|------------|----|

| LBOTIN         | LOW | <b>A</b> 1 | Ao |

| First Address  |     | 0          | 0  | 0          | 1  | 1          | 0  | 1          | 1  |

|                |     |            | 1  | 1          | 0  | 1          | 1  | 0          | 0  |

| $\checkmark$   |     | 1          | 0  | 1          | 1  | 0          | 0  | 0          | 1  |

| Fourth Address |     | 1          | 1  | 0          | 0  | 0          | 1  | 1          | 0  |

**Note :** 1. LBO pin must be tied to High or Low, and Floating State must not be allowed.

(Interleaved Burst)

(Linear Burst)

#### TRUTH TABLES SYNCHRONOUS TRUTH TABLE

| CS <sub>1</sub> | CS <sub>2</sub> | CS <sub>2</sub> | ADSP | ADSC | ADV | WRITE | CLK        | ADDRESS ACCESSED | OPERATION                  |

|-----------------|-----------------|-----------------|------|------|-----|-------|------------|------------------|----------------------------|

| Н               | Х               | Х               | Х    | L    | Х   | Х     | <b>↑</b>   | N/A              | Not Selected               |

| L               | L               | Х               | L    | Х    | Х   | Х     | $\uparrow$ | N/A              | Not Selected               |

| L               | Х               | Н               | L    | Х    | Х   | Х     | $\uparrow$ | N/A              | Not Selected               |

| L               | L               | Х               | Х    | L    | Х   | Х     | $\uparrow$ | N/A              | Not Selected               |

| L               | Х               | Н               | Х    | L    | Х   | Х     | Ŷ          | N/A              | Not Selected               |

| L               | Н               | L               | L    | Х    | Х   | Х     | Ŷ          | External Address | Begin Burst Read Cycle     |

| L               | Н               | L               | Н    | L    | Х   | L     | $\uparrow$ | External Address | Begin Burst Write Cycle    |

| L               | Н               | L               | Н    | L    | Х   | н     | Ŷ          | External Address | Begin Burst Read Cycle     |

| Х               | Х               | Х               | Н    | Н    | L   | н     | Ŷ          | Next Address     | Continue Burst Read Cycle  |

| Н               | Х               | Х               | Х    | Н    | L   | н     | Ŷ          | Next Address     | Continue Burst Read Cycle  |

| Х               | Х               | Х               | Н    | Н    | L   | L     | $\uparrow$ | Next Address     | Continue Burst Write Cycle |

| Н               | Х               | Х               | Х    | Н    | L   | L     | $\uparrow$ | Next Address     | Continue Burst Write Cycle |

| Х               | Х               | Х               | Н    | Н    | Н   | н     | Ŷ          | Current Address  | Suspend Burst Read Cycle   |

| Н               | Х               | Х               | Х    | Н    | Н   | Н     | <b>↑</b>   | Current Address  | Suspend Burst Read Cycle   |

| Х               | Х               | Х               | Н    | Н    | Н   | L     | <b>↑</b>   | Current Address  | Suspend Burst Write Cycle  |

| Н               | Х               | Х               | Х    | Н    | Н   | L     | $\uparrow$ | Current Address  | Suspend Burst Write Cycle  |

**Notes :** 1. X means "Don't Care". 2. The rising edge of clock is symbolized by  $\uparrow$ .

3. WRITE = L means Write operation in WRITE TRUTH TABLE.

WRITE = H means Read operation in WRITE TRUTH TABLE.

4. Operation finally depends on status of asynchronous input pins(ZZ and  $\overline{OE}$ ).

#### WRITE TRUTH TABLE

| GW | BW | WEa | WEb | WEc | WEd | OPERATION          |  |  |  |

|----|----|-----|-----|-----|-----|--------------------|--|--|--|

| Н  | Н  | Х   | Х   | Х   | Х   | READ               |  |  |  |

| Н  | L  | Н   | Н   | Н   | Н   | READ               |  |  |  |

| Н  | L  | L   | Н   | н   | Н   | WRITE BYTE a       |  |  |  |

| н  | L  | Н   | L   | Н   | Н   | WRITE BYTE b       |  |  |  |

| н  | L  | Н   | Н   | L   | L   | WRITE BYTE c and d |  |  |  |

| н  | L  | L   | L   | L   | L   | WRITE ALL BYTEs    |  |  |  |

| L  | Х  | Х   | Х   | Х   | Х   | WRITE ALL BYTEs    |  |  |  |

Notes : 1. X means "Don't Care".

2. All inputs in this table must meet setup and hold time around the rising edge of CLK(<sup>↑</sup>).

### **ASYNCHRONOUS TRUTH TABLE**

(See Notes 1 and 2):

| OPERATION  | ZZ | OE | I/O STATUS  |

|------------|----|----|-------------|

| Sleep Mode | Н  | Х  | High-Z      |

| Read       | L  | L  | DQ          |

| Redu       | L  | Н  | High-Z      |

| Write      | L  | Х  | Din, High-Z |

| Deselected | L  | Х  | High-Z      |

#### Notes

1. X means "Don't Care".

- 2. ZZ pin is pulled down internally

- 3. For write cycles that following read cycles, the output buffers must be disabled with OE, otherwise data bus contention will occur.

- Sleep Mode means power down state of which stand-by current does not depend on cycle time.

5. Deselected means power down state of which stand-by current depends on cycle time.

#### PASS-THROUGH TRUTH TABLE

| PREVIOUS CYCLE                                    |       | PRESENT C                                                    | YCLE |       |    | NEXT CYCLE                          |

|---------------------------------------------------|-------|--------------------------------------------------------------|------|-------|----|-------------------------------------|

| OPERATION                                         | WRITE | OPERATION                                                    | CS1  | WRITE | OE | NEXTOTOLE                           |

| Write Cycle, All bytes<br>Address=An-1, Data=Dn-1 | All L | Initiate Read Cycle<br>Address=An<br>Data=Qn-1 for all bytes | L    | н     | L  | Read Cycle<br>Data=Qn               |

| Write Cycle, All bytes<br>Address=An-1, Data=Dn-1 | All L | No new cycle<br>Data=Qn-1 for all bytes                      | н    | Н     | L  | No carryover from<br>previous cycle |

| Write Cycle, All bytes<br>Address=An-1, Data=Dn-1 | All L | No new cycle<br>Data=High-Z                                  | н    | Н     | н  | No carryover from<br>previous cycle |

| Write Cycle, One byte<br>Address=An-1, Data=Dn-1  | One L | Initiate Read Cycle<br>Address=An<br>Data=Qn-1 for one byte  | L    | н     | L  | Read Cycle<br>Data=Qn               |

| Write Cycle, One byte<br>Address=An-1, Data=Dn-1  | One L | No new cycle<br>Data=Qn-1 for one byte                       | н    | н     | L  | No carryover from<br>previous cycle |

Note : 1. This operation makes written data immediately available at output during a read cycle preceded by a write cycle.

## **ABSOLUTE MAXIMUM RATINGS\***

| PARAMETER                              | SYMBOL | RATING           | UNIT |

|----------------------------------------|--------|------------------|------|

| Voltage on VDD Supply Relative to Vss  | Vdd    | -0.3 to 4.6      | V    |

| Voltage on VDDQ Supply Relative to Vss | Vddq   | Vdd              | V    |

| Voltage on Input Pin Relative to Vss   | Vin    | -0.3 to 6.0      | V    |

| Voltage on I/O Pin Relative to Vss     | Vio    | -0.3 to VDDQ+0.5 | V    |

| Power Dissipation                      | PD     | 1.6              | W    |

| Storage Temperature                    | Тѕтс   | -65 to 150       | °C   |

| Operating Temperature                  | Topr   | 0 to 70          | °C   |

| Storage Temperature Range Under Bias   | TBIAS  | -10 to 85        | °C   |

\*Note : Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **OPERATING CONDITIONS at 3.3V I/O** (0°C≤ TA≤70°C)

| PARAMETER      | SYMBOL | MIN   | Тур. | MAX | UNIT |

|----------------|--------|-------|------|-----|------|

| Supply Voltage | Vdd    | 3.135 | 3.3  | 3.6 | V    |

| Supply Voltage | Vddq   | 3.135 | 3.3  | 3.6 | V    |

| Ground         | Vss    | 0     | 0    | 0   | V    |

### **OPERATING CONDITIONS at 2.5V I/O**( $0^{\circ}C \le T_A \le 70^{\circ}C$ )

| PARAMETER      | SYMBOL | MIN   | Тур. | MAX | UNIT |

|----------------|--------|-------|------|-----|------|

| Supply Voltage | Vdd    | 3.135 | 3.3  | 3.6 | V    |

| Supply Voltage | Vddq   | 2.375 | 2.5  | 2.9 | V    |

| Ground         | Vss    | 0     | 0    | 0   | V    |

## CAPACITANCE\*(TA=25°C, f=1MHz)

| PARAMETER          | SYMBOL | TEST CONDITION | MIN | MAX | UNIT |  |

|--------------------|--------|----------------|-----|-----|------|--|

| Input Capacitance  | CIN    | VIN=0V         | -   | 5   | pF   |  |

| Output Capacitance | Соит   | Vout=0V        | -   | 7   | pF   |  |

\*Note : Sampled not 100% tested.

| PARAMETER                        | SYMBOL | TEST CONDITIONS                                                         |     | MIN   | MAX       | UNIT |

|----------------------------------|--------|-------------------------------------------------------------------------|-----|-------|-----------|------|

| Input Leakage Current(except ZZ) | lı∟    | VDD = Max ; VIN=Vss to VDD                                              | -2  | +2    | μΑ        |      |

| Output Leakage Current           | IOL    | Output Disabled, VOUT=Vss to VDD                                        | -2  | +2    | μΑ        |      |

| Operating Current                | lcc    |                                                                         | -60 | -     | 425       |      |

|                                  |        | Device Selected, IOUT=0mA,                                              | -67 | -     | 400       | mA   |

|                                  | ICC    | ZZ≤VIL, All Inputs=VIL or VIH<br>Cycle Time ≥ tcyc Min                  | -72 | -     | 375       |      |

|                                  |        | 5                                                                       | -10 | -     | 300       |      |

| Standby Current                  |        |                                                                         | -60 | -     | 130       | mA   |

|                                  | lsв    | Device deselected, IOUT=0mA,                                            | -67 | -     | 120       |      |

|                                  |        | ZZ≤VIL, f=Max,<br>All Inputs≤0.2V or ≥ Vpp-0.2V                         | -72 | -     | 110       |      |

|                                  |        |                                                                         | -10 | -     | 90        |      |

|                                  | ISB1   | Device deselected, IouT=0mA, ZZ<br>f = 0, All Inputs=fixed (VDD-0.2V or | -   | 30    | mA        |      |

|                                  | ISB2   | Device deselected, lou⊤=0mA, ZZ≥<br>f=Max, All Inputs≤VI∟ or ≥VIH       | -   | 30    | mA        |      |

| Output Low Voltage(3.3V I/O)     | Vol    | IOL = 8.0mA                                                             | -   | 0.4   | V         |      |

| Output High Voltage(3.3V I/O)    | Vон    | Юн = -4.0mA                                                             |     | 2.4   | -         | V    |

| Output Low Voltage(2.5V I/O)     | Vol    | lo∟ = 1.0mA                                                             | -   | 0.4   | V         |      |

| Output High Voltage(2.5V I/O)    | Vон    | Іон = -1.0mA                                                            |     | 2.0   | -         | V    |

| Input Low Voltage(3.3V I/O)      | VIL    |                                                                         |     | -0.5* | 0.8       | V    |

| Input High Voltage(3.3V I/O)     | Vін    |                                                                         |     | 2.0   | Vdd+0.5** | V    |

| Input Low Voltage(2.5V I/O)      | VIL    |                                                                         |     | -0.3* | 0.7       | V    |

| Input High Voltage(2.5V I/O)     | Vін    |                                                                         |     | 1.7   | Vdd+0.5** | V    |

### DC ELECTRICAL CHARACTERISTICS(TA=0 to 70°C, VDD=3.3V+0.3V/-0.165V)

\* VIL(Min)=-2.0(Pulse Width  $\leq$  tCYC/2)

\*\* Viн(Max)=4.6(Pulse Width ≤ tCYC/2)

\*\* In Case of I/O Pins, the Max. VIH=VDDQ+0.5V

## **TEST CONDITIONS**

(VDD=3.3V+0.3V/-0.165V,VDDQ=3.3V+0.3/-0.165V or VDD=3.3V+0.3V/-0.165V,VDDQ=2.5V+0.4V/-0.125V, TA=0 to 70°C)

| PARAMETER                                                        | VALUE      |

|------------------------------------------------------------------|------------|

| Input Pulse Level(for 3.3V I/O)                                  | 0 to 3V    |

| Input Pulse Level(for 2.5V I/O)                                  | 0 to 2.5V  |

| Input Rise and Fall Time(Measured at 0.3V and 2.7V for 3.3V I/O) | 2ns        |

| Input Rise and Fall Time(Measured at 0.3V and 2.1V for 2.5V I/O) | 2ns        |

| Input and Output Timing Reference Levels for 3.3V I/O            | 1.5V       |

| Input and Output Timing Reference Levels for 2.5V I/O            | VDDQ/2     |

| Output Load                                                      | See Fig. 1 |

# **KM732V789**

# 128Kx32 Synchronous SRAM

Output Load(A)

Output Load(B) (for tLZC, tLZOE, tHZOE & tHZC)

Fig. 1

| DADAMETED                                                                           | SYMPOL        | -60 |     | -67 |     | -72 |     | -10  |     |       |

|-------------------------------------------------------------------------------------|---------------|-----|-----|-----|-----|-----|-----|------|-----|-------|

| PARAMETER                                                                           | SYMBOL        | MIN | MAX | MIN | MAX | MIN | MAX | MIN  | MAX | UNIT  |

| Cycle Time                                                                          | tCYC          | 6.0 | -   | 6.7 | -   | 7.2 | -   | 10.0 | -   | ns    |

| Clock Access Time                                                                   | tCD           | -   | 3.5 | -   | 3.8 | -   | 4.0 | -    | 4.5 | ns    |

| Output Enable to Data Valid                                                         | tOE           | -   | 3.5 | -   | 3.8 | -   | 4.0 | -    | 4.5 | ns    |

| Clock High to Output Low-Z                                                          | tLZC          | 0   | -   | 0   | -   | 0   | -   | 0    | -   | ns    |

| Output Hold from Clock High                                                         | tон           | 1.5 | -   | 1.5 | -   | 1.5 | -   | 1.5  | -   | ns    |

| Output Enable Low to Output Low-Z                                                   | <b>t</b> LZOE | 0   | -   | 0   | -   | 0   | -   | 0    | -   | ns    |

| Output Enable High to Output High-Z                                                 | tHZOE         | -   | 3.5 | -   | 3.5 | -   | 3.8 | -    | 4.0 | ns    |

| Clock High to Output High-Z                                                         | tHZC          | 1.5 | 6.0 | 1.5 | 6.7 | 1.5 | 7.2 | 1.5  | 9.0 | ns    |

| Clock High Pulse Width                                                              | tсн           | 2.4 | -   | 2.6 | -   | 2.8 | -   | 3.4  | -   | ns    |

| Clock Low Pulse Width                                                               | tCL           | 2.4 | -   | 2.6 | -   | 2.8 | -   | 3.4  | -   | ns    |

| Address Setup to Clock High                                                         | tas           | 1.5 | -   | 1.5 | -   | 1.5 | -   | 1.5  | -   | ns    |

| Address Status Setup to Clock High                                                  | tss           | 1.5 | -   | 1.5 | -   | 1.5 | -   | 1.5  | -   | ns    |

| Data Setup to Clock High                                                            | tDS           | 1.5 | -   | 1.5 | -   | 1.5 | -   | 1.5  | -   | ns    |

| Write Setup to Clock High ( $\overline{GW}$ , $\overline{BW}$ , $\overline{WE}x$ )  | tws           | 1.5 | -   | 1.5 | -   | 1.5 | -   | 1.5  | -   | ns    |

| Address Advance Setup to Clock High                                                 | tadvs         | 1.5 | -   | 1.5 | -   | 1.5 | -   | 1.5  | -   | ns    |

| Chip Select Setup to Clock High                                                     | tcss          | 1.5 | -   | 1.5 | -   | 1.5 | -   | 1.5  | -   | ns    |

| Address Hold from Clock High                                                        | tан           | 0.5 | -   | 0.5 | -   | 0.5 | -   | 0.5  | -   | ns    |

| Address Status Hold from Clock High                                                 | tsн           | 0.5 | -   | 0.5 | -   | 0.5 | -   | 0.5  | -   | ns    |

| Data Hold from Clock High                                                           | tDH           | 0.5 | -   | 0.5 | -   | 0.5 | -   | 0.5  | -   | ns    |

| Write Hold from Clock High ( $\overline{GW}$ , $\overline{BW}$ , $\overline{WE}x$ ) | twн           | 0.5 | -   | 0.5 | -   | 0.5 | -   | 0.5  | -   | ns    |

| Address Advance Hold from Clock High                                                | <b>t</b> advh | 0.5 | -   | 0.5 | -   | 0.5 | -   | 0.5  | -   | ns    |

| Chip Select Hold from Clock High                                                    | tCSH          | 0.5 | -   | 0.5 | -   | 0.5 | -   | 0.5  | -   | ns    |

| ZZ High to Power Down                                                               | tPDS          | 2   | -   | 2   | -   | 2   | -   | 2    | -   | cycle |

| ZZ Low to Power Up                                                                  | tPUS          | 2   | -   | 2   | -   | 2   | -   | 2    | -   | cycle |

#### AC TIMING CHARACTERISTICS(TA=0 to 70°C, VDD=3.3V+0.3V/-0.165V)

Notes : 1. All address inputs must meet the specified setup and hold times for all rising clock edges whenever ADSC and/or ADSP is sampled low and CS is sampled low. All other synchronous inputs must meet the specified setup and hold times whenever this device is chip selected. 2. <u>Both chip selects</u> must be active whenever ADSC or ADSP is sampled low in order for the this device to remain enabled. 3. ADSC or ADSP must not be asserted for at least 2 Clock after leaving ZZ state.

# 128Kx32 Synchronous SRAM

**ELECTRONICS**

Rev 5.0

# 128Kx32 Synchronous SRAM

Rev 5.0

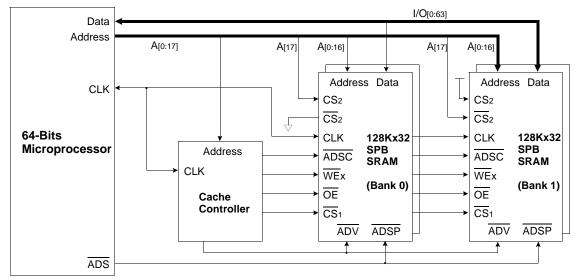

### **APPLICATION INFORMATION**

#### DEPTH EXPANSION

The Samsung 128Kx32 Synchronous Pipelined Burst SRAM has two additional chip selects for simple depth expansion. This permits easy secondary cache upgrades from 128K depth to 256K depth without extra logic.

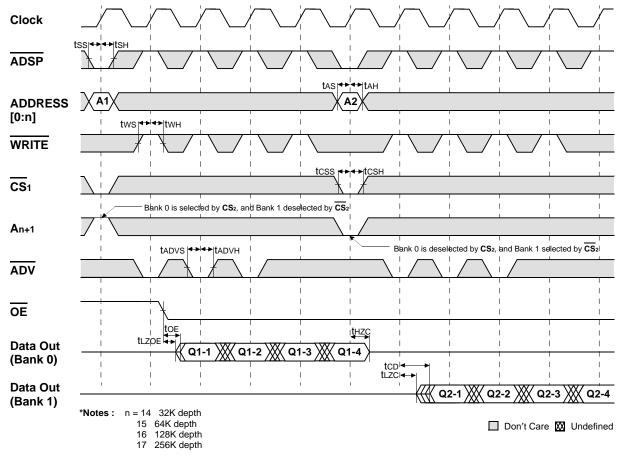

INTERLEAVE READ TIMING (Refer to non-interleave write timing for interleave write timing)

(ADSP CONTROLLED , ADSC=HIGH)

## PACKAGE DIMENSIONS

#### 100-TQFP-1420A

Units ; millimeters/Inches