# 9600-bps Facsimile Modem

## **Preliminary**

#### Overview

The LC89201 is a CMOS single-chip, synchronous, half-duplex, 9600-bps fax modem designed for use with public telephone networks. Built in are such essential features for Group III facsimile systems as modulator, demodulator, transmission filters, and V.24 interface.

The LSI supports the V.29, V.27ter, V.21ch2, T.30, and T.4 telecommunications standards promulgated by the ITU-T (formerly the CCITT) for transmission at 9600, 7200, 4800, 2400 and 300 bps. Advanced signal processing provides reliable data transmissions even under adverse circuit conditions. Built-in High-level Data Link Control (HDLC) support permits the construction of Error Correction Mode (ECM) facsimile machines.

#### **Features**

- Support for the following ITU-T standards: V.29 (9600, 7200 and 4800 bps), V.27ter (4800 and 2400 bps), V.21ch2 (300 bps), T.30, and T.4.

- Half-duplex operation.

- Group III facsimile support.

- Automatic switching between high- (V.29 and V.27ter) and low-speed (V.21ch2) incoming facsimiles.

- Short training (for ITU-T V.27ter only).

- HDLC framing and deframing (V.29, V.27ter, and V.21ch2).

- Tone generation and detection.

- Dual-tone multifrequency (DTMF) generation and detection.

- Call progress tone detection.

- Pseudo link back tone generation.

- Built-in automatic adaptive equalizer.

- Built-in fixed-amplitude amplifier.

- Link amplitude equalizer

- Cable amplitude equalizer

- Built-in transmission filters (digital filters).

- Programmable transmission level adjustment.

- Dynamic range for reception of 0 to -47 dBm.

- Programmable reception sensitivity adjustment.

- DTE interface.

- Serial interface (ITU-T V.24)

- Parallel interface (4 words  $\times$  8 bits, with built-in FIFO)

- Programmable interrupt generator.

- Built-in eye pattern generator.

- Adaptive differential pulse-code modulation (ADPCM).

- Caller ID detection.

- · Built-in diagnostics.

- Energy-saving CMOS design (typ. 250 mW).

- Single 5 V power supply.

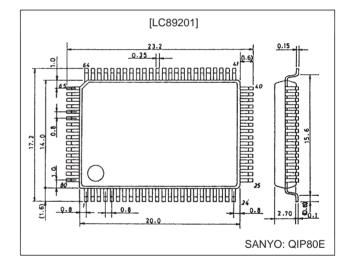

- 80-pin flat package (QIP-80E).

### Package Dimensions

unit: mm

3174-QFP80E

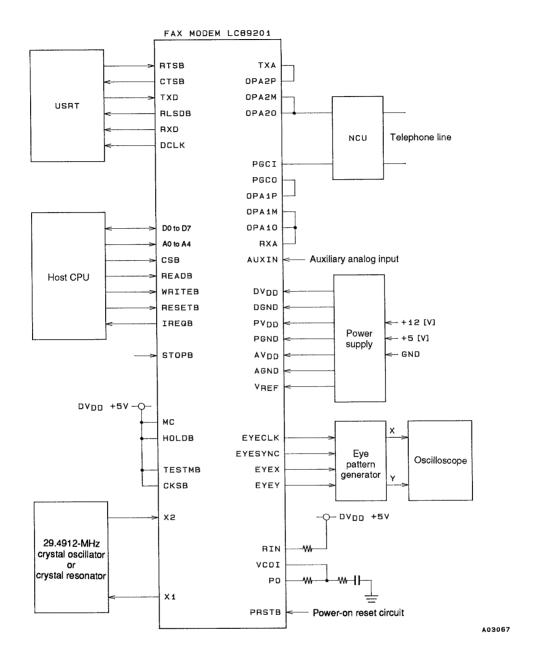

### **System Block Diagram**

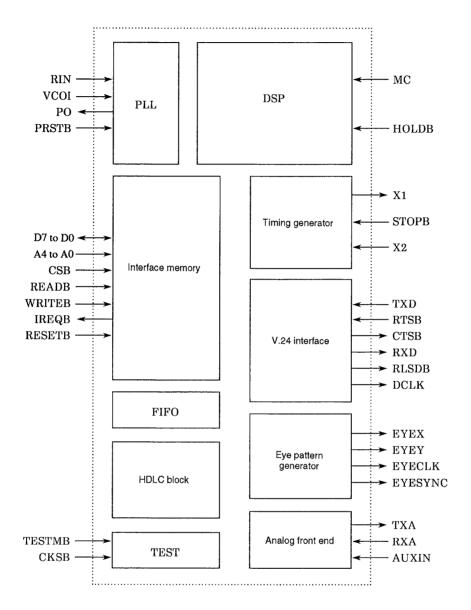

### **Internal Block Diagram**

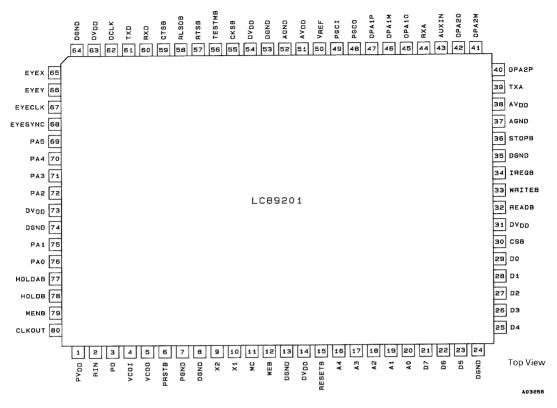

### **Pin Assignment**

#### **Pin Functions**

### 1. Power Supply, Clock and Test Pins

| Pin No.                               | Symbol           | I/O | Function                                                                          |

|---------------------------------------|------------------|-----|-----------------------------------------------------------------------------------|

| 14<br>31<br>54<br>63<br>73            | DV <sub>DD</sub> | Р   | Digital power supply                                                              |

| 8<br>13<br>24<br>35<br>53<br>64<br>74 | DGND             | Р   | Digital ground                                                                    |

| 38<br>51                              | AV <sub>DD</sub> | Р   | Analog power supply                                                               |

| 37<br>52                              | AGND             | Р   | Analog ground                                                                     |

| 1                                     | $PV_{DD}$        | Р   | Frequency multiplier PLL power supply                                             |

| 7                                     | PGND             | Р   | Frequency multiplier PLL ground                                                   |

| 50                                    | $V_{REF}$        | Р   | Reference power supply. This must be half AV <sub>DD</sub> .                      |

| 9                                     | X2               | I   | System clock input (29.4912 MHz)                                                  |

| 10                                    | X1               | 0   | Oscillator amplifier output                                                       |

| 80                                    | CLKOUT           | 0   | Output clock, one-quarter the frequency of the internal master clock (9.216 MHz). |

| 56                                    | TESTMB           | I   | Test pin. Connect to DV <sub>DD</sub> .                                           |

| 55                                    | CKSB             | I   | Test pin. Connect to DV <sub>DD</sub> .                                           |

### LC89201

### 2. DTE Interface Pins

| Pin No.                                | Symbol                                 | I/O | Function                      |

|----------------------------------------|----------------------------------------|-----|-------------------------------|

| 29<br>28<br>27<br>26<br>25<br>23<br>22 | D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6 | В   | Data bus to host CPU          |

| 21                                     | D7                                     |     |                               |

| 20<br>19<br>18<br>17<br>16             | A0<br>A1<br>A2<br>A3<br>A4             | 1   | Address bus to host CPU       |

| 30                                     | CSB                                    | I   | Chip select signal            |

| 32                                     | READB                                  | I   | Interface memory read signal  |

| 33                                     | WRITEB                                 | I   | Interface memory write signal |

| 34                                     | IREQB                                  | 0   | Interrupt request to host CPU |

| 15                                     | RESETB                                 | I   | System reset signal           |

### 3. Eye Pattern Interface Pins

| Pin No.  | Symbol       | I/O | Function                                                                                                     |  |  |  |  |

|----------|--------------|-----|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 67       | EYECLK       | 0   | g clock for generating eye pattern data. This may be used as the shift clock for an external shift register. |  |  |  |  |

| 68       | EYESYNC      | 0   | pattern synchronization signal                                                                               |  |  |  |  |

| 66<br>65 | EYEX<br>EYEY | 0   | Eye pattern data serial outputs (8 bits, MSB first)                                                          |  |  |  |  |

### 4. V.24 (RS-232C) Interface Pins

| Pin No. | Symbol | I/O | Function                                                                                                                                              |

|---------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 57      | RTSB   | I   | Request to send signal. The low level at this pin starts transmission; the high level suspends it.                                                    |

| 59      | CTSB   | 0   | Clear to send signal. The low level at this pin signals the availability of data for transmission; the high level indicates that the data is invalid. |

| 58      | RLSDB  | 0   | Received line signal data signal. The low level at this pin gives the timing for transferring the data received to the terminal.                      |

| 61      | TXD    | I   | Transmit data input                                                                                                                                   |

| 60      | RXD    | 0   | Receive data output                                                                                                                                   |

| 62      | DCLK   | 0   | Transmission data clock output                                                                                                                        |

## 5. Analog Signal Pins

| Pin No. | Symbol | I/O | Function                                                                    |  |  |  |  |

|---------|--------|-----|-----------------------------------------------------------------------------|--|--|--|--|

| 39      | TXA    | 0   | Transmitter analog output                                                   |  |  |  |  |

| 44      | RXA    | I   | ver analog input                                                            |  |  |  |  |

| 43      | AUXIN  | I   | ary analog input                                                            |  |  |  |  |

| 40      | OPA2P  | I   |                                                                             |  |  |  |  |

| 41      | OPA2M  | I   | ransmission buffer input/output pins. (For details, see circuit diagram.)   |  |  |  |  |

| 42      | OPA2O  | 0   |                                                                             |  |  |  |  |

| 47      | OPA1P  | I   |                                                                             |  |  |  |  |

| 46      | OPA1M  | I   | Reception buffer input/output pins (For details, see circuit diagram.)      |  |  |  |  |

| 45      | OPA1O  | 0   |                                                                             |  |  |  |  |

| 49      | PGCI   | I   | Reception gain adjustment circuit input. (For details, seecircuit diagram.) |  |  |  |  |

| 48      | PGCO   | 0   | Reception gain adjustment circuit output.                                   |  |  |  |  |

### 6. System signal pins

| Pin No. | Symbol | I/O | Function                                                                            |  |  |  |

|---------|--------|-----|-------------------------------------------------------------------------------------|--|--|--|

| 11      | MC     | I   | m mode control signal. Connect to DV <sub>DD</sub> .                                |  |  |  |

| 78      | HOLDB  | I   | hold signal. Connect to DV <sub>DD</sub> .                                          |  |  |  |

| 77      | HOLDAB | 0   | hold confirmation signal.                                                           |  |  |  |

| 6       | PRTSB  | I   | uency multiplier PLL reset input. (For details, see circuit diagram.)               |  |  |  |

| 3       | PO     | 0   | Phase comparator output. (For details, see circuit diagram.)                        |  |  |  |

| 4       | VCOI   | I   | Voltage-controlled oscillator input. (For details, seecircuit diagram.)             |  |  |  |

| 5       | VCOO   | 0   | Voltage-controlled oscillator output                                                |  |  |  |

| 2       | RIN    | I   | Voltage-controlled oscillator adjustment input. (For details, see circuit diagram.) |  |  |  |

| 36      | STOPB  | I   | Oscillator amplifier STOP input                                                     |  |  |  |

Note: All other pins are to be left unconnected.

# **Specifications**

# Absolute Maximum Ratings at DGND, AGND, PGND = 0 V

| Parameter                   | Symbol                        | Conditions                 | Ratings                       | Unit |

|-----------------------------|-------------------------------|----------------------------|-------------------------------|------|

|                             | DV <sub>DD</sub> max          | Ta = 25°C                  | -0.3 to +7.0                  | V    |

| Maximum supply voltage      | AV <sub>DD</sub> max          | Ta = 25°C                  | -0.3 to +7.0                  | V    |

|                             | PV <sub>DD</sub> max          | Ta = 25°C                  | -0.3 to +7.0                  | V    |

| I/O voltages                | V <sub>I</sub> V <sub>O</sub> | Ta = 25°C                  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Allowable power dissipation | Pd max                        | Ta ≤ 70°C                  | 400                           | mW   |

| Operating temperature       | Topr                          |                            | -30 to +70                    | °C   |

| Storage temperature         | Tstg                          |                            | -55 to +125                   | °C   |

| Soldering heat registance   |                               | Hand soldering (3 seconds) | 350                           | °C   |

| Soldering heat resistance   |                               | Reflow (10 seconds)        | 235                           | °C   |

# Allowable Operating Ranges at $Ta = -30 \text{ to } +70^{\circ}\text{C}$ , DGND, AGND, PGND = 0 V

| Parameter      | Symbol    | Conditions | min | typ | max             | Unit |

|----------------|-----------|------------|-----|-----|-----------------|------|

| Supply voltage | $DV_DD$   |            | 4.5 | 5.0 | 5.5             | V    |

|                | $AV_{DD}$ |            | 4.5 | 5.0 | 5.5             | V    |

|                | $PV_{DD}$ |            | 4.5 | 5.0 | 5.5             | V    |

| Input voltage  | $V_{IN}$  |            | 0   |     | V <sub>DD</sub> | V    |

# Electrical Characteristics at Ta = -30 to +70°C, DGND, AGND, PGND = 0 V, DV<sub>DD</sub>, AV<sub>DD</sub>, PV<sub>DD</sub> = 4.5 to 5.5 V

| Parameter                      | Symbol           | Conditions                                                                                                                                                                                                                                                                            | min                  | typ                | max                  | Unit |

|--------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|----------------------|------|

| Input high level voltage       | V <sub>IH</sub>  | TTL levels: RESETB, PRSTB, STOPB, A0 to A4, D0 to D7, CSB, READB, WRITEB, RTSB, TXD,                                                                                                                                                                                                  | 2.2                  |                    |                      | ٧    |

| Input low level voltage        | V <sub>IL</sub>  | HOLDB, MC, TESTMB, CKSB                                                                                                                                                                                                                                                               |                      |                    | 0.8                  | V    |

| Input leak current             | IL               | $ \begin{array}{l} \textbf{V}_{\text{IN}} = \text{DGND, AGND, PGND, DV}_{\text{DD}},  \textbf{AV}_{\text{DD}},  \textbf{PV}_{\text{DD}}; \\ \text{RESETB, PRSTB, STOPB, A0 to A4, D0 to D7, CSB,} \\ \text{READB, WRITEB, RTSB, TXD, HOLDB, MC, TESTMB,} \\ \text{CKSB} \end{array} $ | -1                   |                    | +1                   | μA   |

| Output high level voltage      | V <sub>OH</sub>  | I <sub>OH</sub> = -3 mA, TTL levels: WEB, MENB, CLKOUT,<br>HOLDAB, PA0 to PA5, D0 to D7, IREQB, CTSB,<br>RLSDB, RXD, DCLK, VCOO, EYEX, EYEY, EYECLK,<br>EYESYNC                                                                                                                       | 2.4                  |                    |                      | V    |

| Output low level voltage       | V <sub>OL</sub>  | I <sub>OL</sub> = 3 mA, TTL levels: WEB, MENB, CLKOUT,<br>HOLDAB, PA0 to PA5, D0 to D7, IREQB, CTSB,<br>RLSDB, RXD, DCLK, VCOO, EYEX, EYEY, EYECLK,<br>EYESYNC                                                                                                                        |                      |                    | 0.4                  | V    |

| Output leak current            | l <sub>OZ</sub>  | For high-impedance output: D0 to D7                                                                                                                                                                                                                                                   | -10                  | +10                |                      | μA   |

| Oscillator frequency           | fosc             | X2, X1                                                                                                                                                                                                                                                                                |                      | 29.4912            |                      | MHz  |

| V <sub>REF</sub> input voltage | V <sub>REF</sub> | V <sub>REF</sub>                                                                                                                                                                                                                                                                      |                      | V <sub>DD</sub> /2 |                      | V    |

| V <sub>REF</sub> impedance     | R <sub>REF</sub> | V <sub>REF</sub>                                                                                                                                                                                                                                                                      | 1                    |                    |                      | ΜΩ   |

| Input voltage range            | V <sub>IA</sub>  | RIN, VCOI, OPA1M, OPA1P, RAX, OPA2M, OPA2P, PGCI                                                                                                                                                                                                                                      | V <sub>DD</sub> *0.2 |                    | V <sub>DD</sub> *0.8 | V    |

| Output voltage range           | V <sub>OA</sub>  | TXA, PGCO, OPA1O, OPA2O                                                                                                                                                                                                                                                               | V <sub>DD</sub> *0.2 |                    | V <sub>DD</sub> *0.8 | V    |

| Output impedance               | R <sub>O</sub>   | TXA, PGCO, OPA1O, OPA2O                                                                                                                                                                                                                                                               |                      |                    | 7                    | kΩ   |

| Current drain                  |                  | V <sub>DD</sub> = 5.5 V                                                                                                                                                                                                                                                               |                      |                    | 80                   | mA   |

| Current drain                  | I <sub>DD</sub>  | V <sub>DD</sub> = 5.0 V                                                                                                                                                                                                                                                               |                      | 50                 |                      | mA   |

### **AC Characteristics**

### 1. DTE interface timing

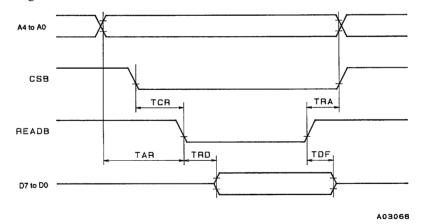

# Read cycle timing

A03069

#### LC89201

| Parameter                                                  | Symbol | Conditions | min | typ | max | Unit |

|------------------------------------------------------------|--------|------------|-----|-----|-----|------|

| Address stabilization time (relative to READB signal)      | TAR    |            | 15  |     |     | ns   |

| Chip select stabilization time (relative to READB signal)  | TCR    |            | 0   |     |     | ns   |

| Data propagation delay                                     | TRD    |            |     |     | 30  | ns   |

| Data float propagation delay                               | TDF    |            | 10  |     |     | ns   |

| Address hold time (relative to READB signal)               | TRA    |            | 10  |     |     | ns   |

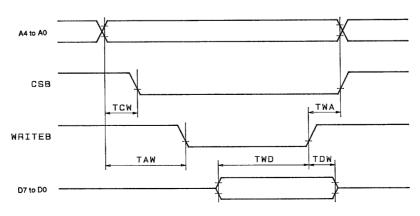

| Address stabilization time (relative to WRITEB signal)     | TAW    |            | 15  |     |     | ns   |

| Chip select stabilization time (relative to WRITEB signal) | TCW    |            | 0   |     |     | ns   |

| Data setup time                                            | TDW    |            | 20  |     |     | ns   |

| Data hold time                                             | TWD    |            | 5   |     |     | ns   |

| Address hold time (relative to WRITEB signal)              | TWA    |            | 10  |     |     | ns   |

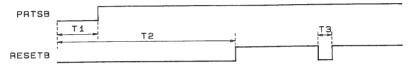

#### 2. Reset timing

A03070

| Parameter                                  | Symbol | Conditions | min | typ | max | Unit |

|--------------------------------------------|--------|------------|-----|-----|-----|------|

| PRTSB pulse width                          | T1     |            | 500 |     |     | μs   |

| PRTSB propagation delay relative to RESETB | T2     |            | 5   |     |     | ms   |

| RESETB pulse width                         | T3     |            | 500 |     |     | ns   |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of September, 1995. Specifications and information herein are subject to change without notice.

# Caption

### P.7/8

P.2

A4 to A0 D7 to D0 A4 to A0 D7 to D0

1. Host CPU

2.

29.4912-MHz crystal oscillator or crystal resonator

3. Telephone line

4.

Power supply

5. Auxiliary analog input

6.

Eye pattern generator

- 7. Oscilloscope

- 8. Power-on reset circuit

### P.3

- 1. Interface memory

- 2. Timing generator

- 3. V.24 interface

4.

Eye pattern generator

- 5. HDLC block

- 6. Analog front end

# New P2/8

2.

29.4912-MHz crystal oscillator or crystal resonator

8. Power-on reset circuit

D0 to D7

A0 to A4

## **P3/8**

D7 to D0

A4 to A0