# M62343GP

# 8-Bit, 3-Channel D/A Converter (Buffered)

REJ03F0075-0200 Rev.2.00 Jun 15, 2007

#### **Description**

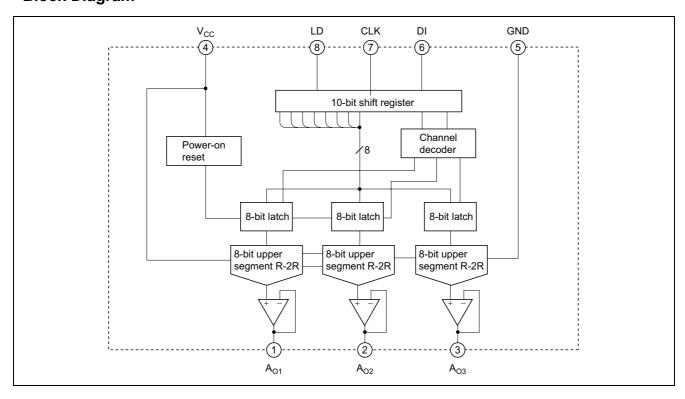

The M62343GP is a CMOS-structure semiconductor integrated circuit incorporating three 8-bit D/A converter channels with output buffer op-amps.

Serial data transfer type input can easily be used through a combination of three lines: DI, CLK, and LD.

Outputs incorporate buffer op-amps that have a drive capacity of 1 mA or above for both sink and source, and can operate over the entire voltage range from almost ground to  $V_{CC}$  (0 to 5 V), making peripheral elements unnecessary and enabling configuration of a system with few component parts.

This product is currently under development, and specifications and other details may be modified at a future date.

#### **Features**

- Data transfer format 10-bit serial data input type

- Output buffer op-amps Operable over entire voltage range from almost ground to  $V_{CC}$  (0 to 5 V)

- High output current capacity ±1 mA or higher

#### **Application**

Signal gain setting and automatic adjustment in DSC, CTV, and display monitors, conversion from digital data to analog data in consumer and industrial products

#### **Block Diagram**

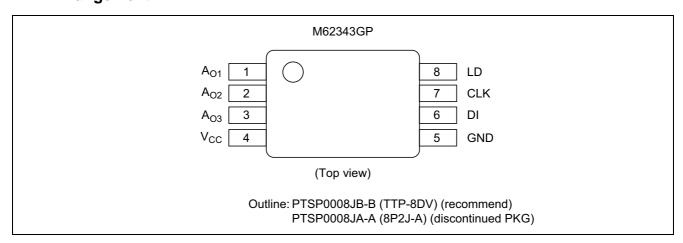

## **Pin Arrangement**

## **Pin Description**

| Pin No. | Symbol          | Function                                                                                                                    |

|---------|-----------------|-----------------------------------------------------------------------------------------------------------------------------|

| 6       | DI              | Serial data input pin. Inputs serial data with a 10-bit data length.                                                        |

| 7       | CLK             | Serial clock input pin. Input signal from DI pin is input to 10-bit shift register at rise of shift clock.                  |

| 8       | LD              | Load pin. When "H" level is input to LD pin, value in 10-bit shift register is loaded into decoder and D/A output register. |

| 1       | A <sub>O1</sub> | 8-bit resolution D/A converter output pins                                                                                  |

| 2       | A <sub>O2</sub> | (After power-on, all channels are reset and DAC data 00h is output.)                                                        |

| 3       | A <sub>O3</sub> |                                                                                                                             |

| 4       | V <sub>CC</sub> | Power supply voltage pin                                                                                                    |

| 5       | GND             | GND pin                                                                                                                     |

## **Absolute Maximum Ratings**

| Item                          | Symbol          | Rated Value                    | Unit |

|-------------------------------|-----------------|--------------------------------|------|

| Power supply voltage          | V <sub>CC</sub> | -0.3 to 7.0                    | V    |

| Input voltage                 | Vin             | $-0.3$ to $V_{CC}+0.3 \le 7.0$ | V    |

| Output voltage                | Vo              | $-0.3$ to $V_{CC}+0.3 \le 7.0$ | V    |

| Internal power consumption    | Pd              | 200                            | mW   |

| Operating ambient temperature | Topr            | -20 to +85                     | °C   |

| Storage temperature           | Tstg            | -55 to +125                    | °C   |

### **Electrical Characteristics**

(Unless specified otherwise,  $V_{CC}$  = +5 V ±10%, GND = 0 V, Ta = -20°C to 85°C)

|                                      |                   | Specification Values |     |         |      |                                                                                  |

|--------------------------------------|-------------------|----------------------|-----|---------|------|----------------------------------------------------------------------------------|

| Item                                 | Symbol            | Min                  | Тур | Max     | Unit | Test Conditions                                                                  |

| Power supply voltage                 | Vcc               | 2.7                  | 5.0 | 5.5     | V    |                                                                                  |

| Power supply current                 | Icc               | 0                    | 0.8 | 2.7     | mA   | At CLK = 1 MHz operation, $I_{AO} = 0 \mu A$ D/A data: 6 Ah (at maximum current) |

|                                      |                   | 0                    | 0.6 | 1.8     |      | $DI = CLK = LD = GND$ , $I_{AO} = 0 \mu A$                                       |

| Input leakage current                | I <sub>ILK</sub>  | -10                  | _   | 10      | μΑ   | $V_{IN} = 0$ to $V_{CC}$                                                         |

| Input voltage "L"                    | V <sub>IL</sub>   | 0                    | _   | 0.2Vcc  | V    |                                                                                  |

| Input voltage "H"                    | V <sub>IH</sub>   | 0.5Vcc               | _   | Vcc     | V    |                                                                                  |

| Buffer amp output                    | $V_{AO}$          | 0.1                  | _   | Vcc-0.1 | V    | $I_{AO} = \pm 100 \mu A$                                                         |

| voltage range                        |                   | 0.1                  | _   | Vcc-0.2 |      | $I_{AO} = \pm 500 \mu A$                                                         |

| Buffer amp output drive range        | I <sub>AO</sub>   | -1.0                 | _   | 1.0     | mA   | Upper saturation voltage = 0.3 V<br>Lower saturation voltage = 0.2 V             |

| Differential nonlinearity error      | S <sub>DL</sub>   | -1.0                 | _   | 1.0     | LSB  | V <sub>CC</sub> = 5.12 V (20 mV/LSB)<br>No load (I <sub>AO</sub> = 0)            |

| Nonlinearity error                   | S <sub>L</sub>    | -1.5                 | _   | 1.5     | LSB  |                                                                                  |

| Zero point error                     | S <sub>ZERO</sub> | -2.0                 |     | 2.0     | LSB  |                                                                                  |

| Full-scale error                     | S <sub>FULL</sub> | -2.0                 | _   | 2.0     | LSB  |                                                                                  |

| Oscillation limit output capacitance | Co                | _                    | _   | 0.1     | μF   |                                                                                  |

| Buffer amp output impedance          | Ro                | _                    | 5.0 |         | Ω    |                                                                                  |

### **AC Characteristics**

(Unless specified otherwise,  $V_{CC}$  = +5 V ±10%, GND = 0 V, Ta = -20°C to 85°C)

|                          |                  | Specification Values |     |     |      |                                   |

|--------------------------|------------------|----------------------|-----|-----|------|-----------------------------------|

| Item                     | Symbol           | Min                  | Тур | Max | Unit | Test Conditions                   |

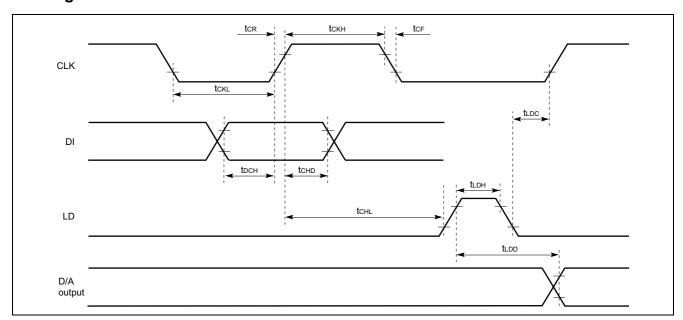

| Clock "L" pulse width    | t <sub>CKL</sub> | 200                  | _   | _   | ns   |                                   |

| Clock "H" pulse width    | t <sub>CKH</sub> | 200                  | _   | _   | ns   |                                   |

| Clock rise time          | t <sub>CR</sub>  | _                    | _   | 200 | ns   |                                   |

| Clock fall time          | t <sub>CF</sub>  | _                    | _   | 200 | ns   |                                   |

| Data setup time          | t <sub>DCH</sub> | 30                   | _   | _   | ns   |                                   |

| Data hold time           | t <sub>CHD</sub> | 60                   | _   | _   | ns   |                                   |

| Load setup time          | t <sub>CHL</sub> | 200                  | _   | _   | ns   |                                   |

| Load hold time           | t <sub>LDC</sub> | 100                  | _   | _   | ns   |                                   |

| Load "H" pulse width     | t <sub>LDH</sub> | 100                  | _   | _   | ns   |                                   |

| D-A output settling time | t <sub>LDD</sub> | _                    | _   | 300 | μS   | Until output reaches last 1/2 LSB |

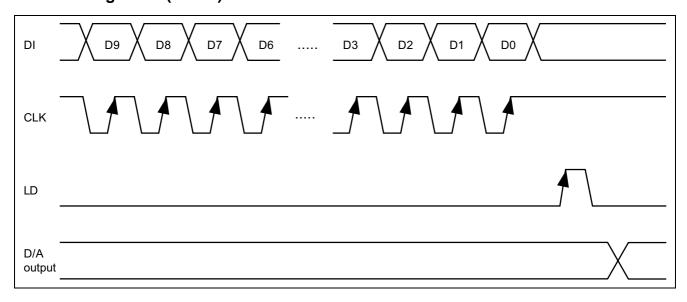

# **Timing Chart**

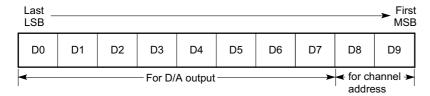

## **Digital Data Format**

#### D/A Data

| D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D-A output               |

|----|----|----|----|----|----|----|----|--------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | V <sub>CC</sub> /256×1   |

| 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | V <sub>CC</sub> /256×2   |

| 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | V <sub>CC</sub> /256×3   |

| 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | V <sub>CC</sub> /256×4   |

| •  | •  | •  | •  | •  | •  | •  | •  | •                        |

| :  | •  | •  | •  | •  | •  | •  | •  | :                        |

|    | ·  | ·  | ·  | ·  | ·  | ·  | ·  | •                        |

| 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | V <sub>CC</sub> /256×255 |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | V <sub>CC</sub> /256×256 |

#### **Channel Select Data**

| D8 | D9 | Channel Selection |  |  |  |

|----|----|-------------------|--|--|--|

| 0  | 0  | AO1 selected      |  |  |  |

| 1  | 0  | AO2 selected      |  |  |  |

| 0  | 1  | AO3 selected      |  |  |  |

| 1  | 1  | Don't care        |  |  |  |

## **Data Timing Chart (Model)**

### **Usage Notes**

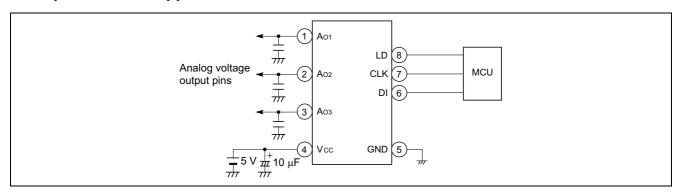

- 1. With this IC, D/A converter upper reference voltage setting is performed by means of the power supply voltage. If ripples or spikes are imposed on this pin, conversion accuracy may fall. When using this IC, a capacitor must be inserted between the power supply pin and GND in order to ensure stable D/A conversion.

- 2. The output buffer amps of this IC are highly tolerant of capacitive loads. Therefore, connecting capacitors (0.1  $\mu$ F max.) between the output pins and ground in order to eliminate jitter or noise due to output line wiring presents no problems whatever in terms of operation.

### **Sample Standard Application Circuit**

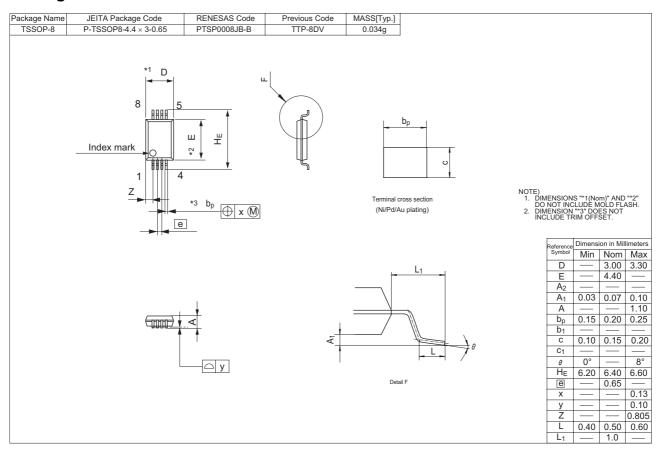

## **Package Dimensions**

#### Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information in this document nor grants any license to any intellectual property rights or any other rights of Renesas or shy third party with respect to the information in this document.

2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, but not limited to, product data, diagrams, algorithms, and application circuit examples.

3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass and regulations, and procedures required by such laws and regulations and procedures required by such laws and regulations, and procedures required by such laws and regulations. All procedures required by such laws and regulations and procedures required by such laws and regulations and procedures required by such laws and regulations. All procedures required by such laws and regulations and procedures required by such laws and regulations, and procedures required by such laws and regulations, and procedures are such as a result of errors or omissions in the information with a Renesas sales office of the date of

**RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

**Renesas Technology America, Inc.** 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

| L |  |  |

|---|--|--|