19-3756; Rev 1; 7/07

# 16-Bit, 500Msps, Interpolating and Modulating Dual DAC with Interleaved LVDS Inputs

### **General Description**

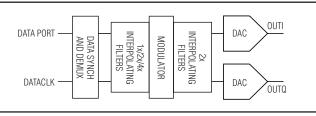

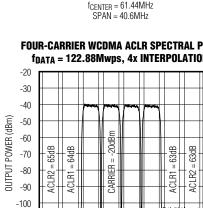

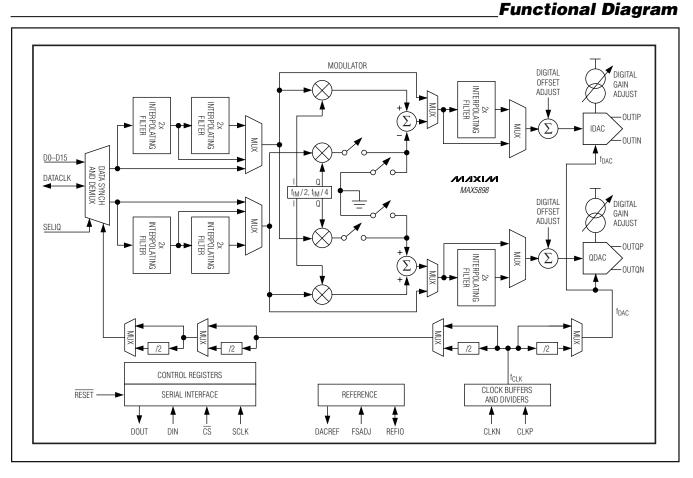

The MAX5898 programmable interpolating, modulating, 500Msps, dual digital-to-analog converter (DAC) offers superior dynamic performance and is optimized for high-performance wideband, single- and multicarrier transmit applications. The device integrates a selectable 2x/4x/8x interpolating filter, a digital quadrature modulator, and dual 16-bit, high-speed DACs on a single integrated circuit. At 30MHz output frequency and 500Msps update rate, the in-band SFDR is 81dBc, while only consuming 1.2W. The device also delivers 71dB ACLR for four-carrier WCDMA at a 61.44MHz output frequency.

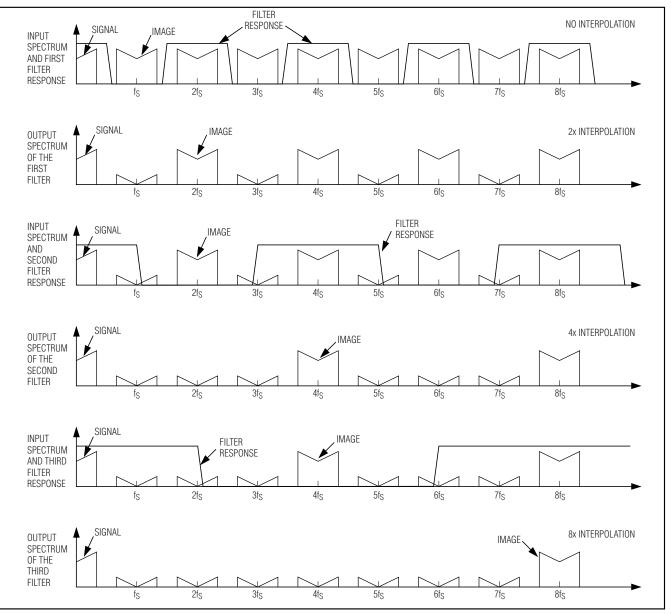

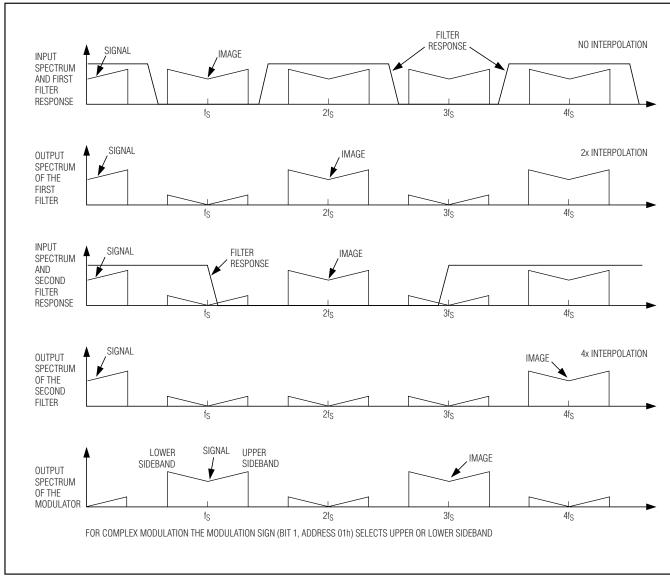

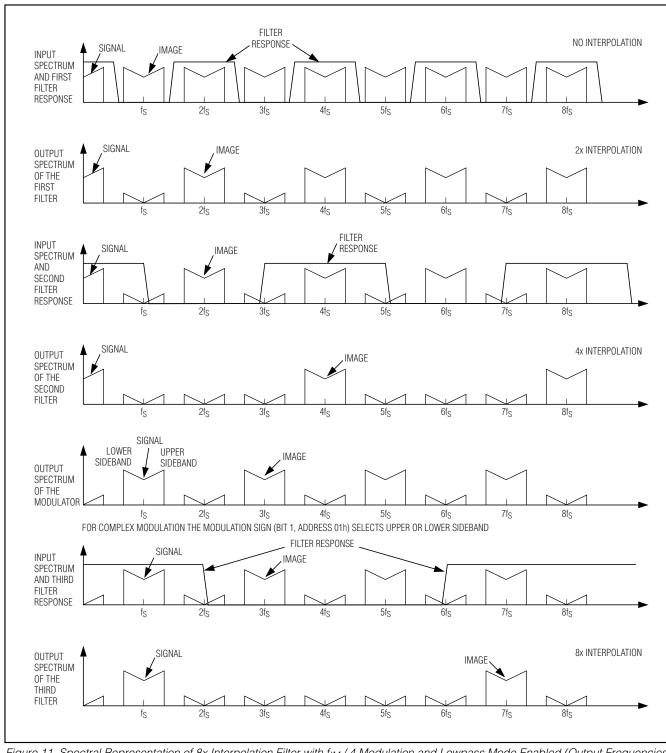

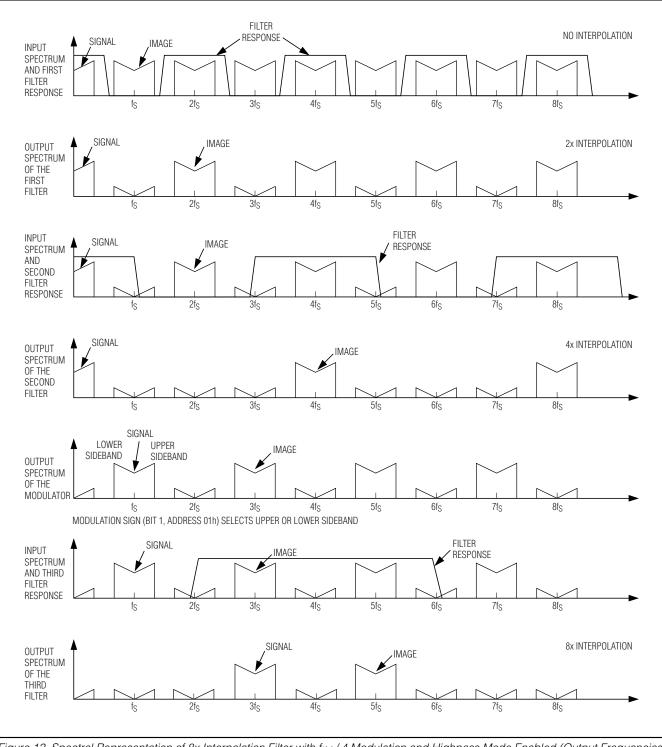

The selectable interpolating filters allow lower input data rates while taking advantage of the high DAC update rates. These linear-phase interpolation filters ease reconstruction filter requirements and enhance the passband dynamic performance. Each channel includes offset and gain programmability, allowing the user to calibrate out local oscillator (LO) feedthrough and sideband suppression errors generated by analog quadrature modulators.

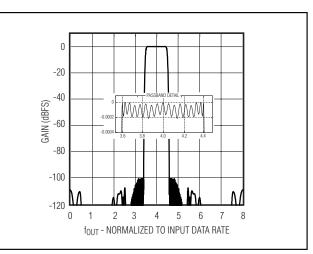

The MAX5898 features a f<sub>IM</sub> / 4 digital image-reject modulator. This modulator generates a quadrature-modulated IF signal that can be presented to an analog I/Q modulator to complete the upconversion process. A second digital modulation mode allows the signal to be frequency-translated with image pairs at f<sub>IM</sub> / 2 or f<sub>IM</sub> / 4.

The MAX5898 features a standard LVDS interface for low electromagnetic interference (EMI). Interleaved data is applied through a single 16-bit bus. A 3.3V SPI<sup>TM</sup> port is provided for mode configuration. The programmable modes include the selection of 2x/4x/8x interpolating filters, f<sub>IM</sub> / 2, f<sub>IM</sub> / 4 or no digital quadrature modulation with image rejection, individual channel gain and offset adjustment, and offset binary or two's-complement data interface.

Compatible versions with CMOS interfaces and 12-, 14-, and 16-bit resolutions are also available. Refer to the MAX5893 data sheet for 12-bit CMOS, MAX5894 for 14-bit CMOS, and the MAX5895 for 16-bit CMOS versions.

### **Applications**

Base Stations: 3G Multicarrier UMTS, CDMA, and GSM

Broadband Wireless Transmitters

Broadband Cable Infrastructure

Instrumentation and Automatic Test Equipment (ATE)

Analog Quadrature Modulation Architectures

SPI is a trademark of Motorola, Inc.

cdma2000 is a registered trademark of Telecommunications Industry Association.

### \_Features

♦ 71dB ACLR at four = 61.44MHz (Four-Carrier WCDMA)

- Meets Multicarrier UMTS, cdma2000<sup>®</sup>, GSM Spectral Masks (four = 122MHz)

- Noise Spectral Density = -160dBFS/Hz at four = 16MHz

- 90dBc SFDR at Low-IF Frequency (10MHz)

- ♦ 88dBc SFDR at High-IF Frequency (50MHz)

- Low Power: 831mW (f<sub>CLK</sub> = 250MHz)

- User Programmable

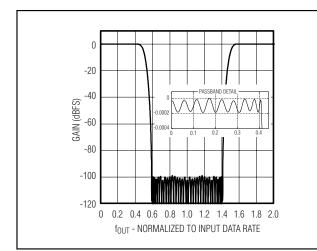

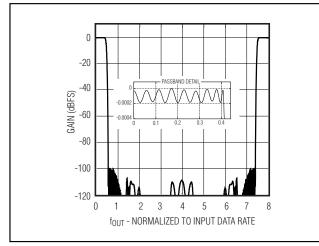

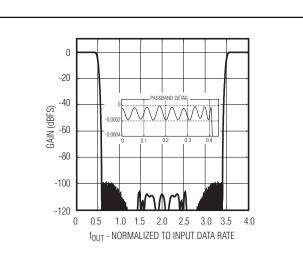

- Selectable 2x, 4x, or 8x Interpolating Filters < 0.01dB Passband Ripple

- > 95dB Stopband Rejection

Selectable Real or Complex Modulator Operation Selectable Modulator LO Frequency: OFF,  $f_{IM}$  / 2, or  $f_{IM}$  / 4

Selectable Output Filter: Lowpass or Highpass Per Channel Gain and Offset Adjustment

• EV Kit Available (Order the MAX5898EVKIT)

### \_Ordering Information

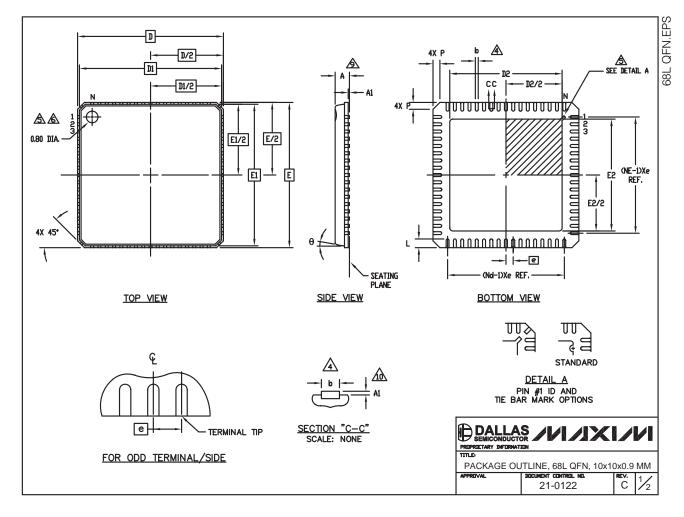

| PART                               | TEMP RANGE     | PIN-PACKAGE                 | PKG<br>CODE |

|------------------------------------|----------------|-----------------------------|-------------|

| MAX5898EGK+D                       | -40°C to +85°C | 68 QFN-EP*<br>(10mm x 10mm) | G6800-4     |

| MAX5898EGK-D                       | -40°C to +85°C | 68 QFN-EP*<br>(10mm x 10mm) | G6800-4     |

| +Denotes a lead-f<br>D = Dry pack. | ree package.   | *EP = Exposed µ             | oaddle.     |

### **Selector Guide**

| PART    | RESOLUTION<br>(BITS) | DAC UPDATE<br>RATE (Msps) | INPUT<br>LOGIC |

|---------|----------------------|---------------------------|----------------|

| MAX5893 | 12                   | 500                       | CMOS           |

| MAX5894 | 14                   | 500                       | CMOS           |

| MAX5895 | 16                   | 500                       | CMOS           |

| MAX5898 | 16                   | 500                       | LVDS           |

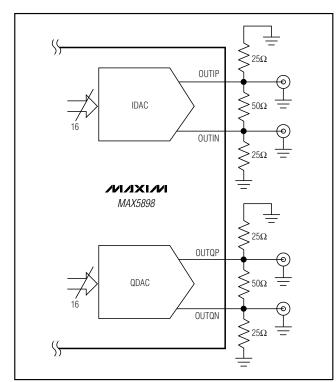

### Simplified Diagram

Pin Configuration appears at end of data sheet.

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# **MAX5898**

### **ABSOLUTE MAXIMUM RATINGS**

| DVDD1.8, AVDD1.8 to GND, DACREF                                 |

|-----------------------------------------------------------------|

| DATACLKP, DATACLKN, DOP-D15P,                                   |

| D0N–D15N, SELIQP, SELIQN to GND,                                |

| DACREF0.3V to (DV <sub>DD1.8</sub> + 0.3V)                      |

| CS, RESET, SCLK, DIN, DOUT to                                   |

| GND, DACREF0.3V to (DV <sub>DD3.3</sub> + 0.3V)                 |

| CLKP, CLKN to GND, DACREF0.3V to (AV <sub>CLK</sub> + 0.3V)     |

| REFIO, FSADJ to GND, DACREF0.3V to (AV <sub>DD3.3</sub> + 0.3V) |

| OUTIP, OUTIN, OUTQP,                                            |

| OUTQN to GND, DACREF0.3V to (AV <sub>DD3.3</sub> + 0.3V)        |

|                                                                 |

DOUT, DATACLKP, DATACLKN Continuous Current .......8mA Continuous Power Dissipation (TA = +70°C)

| 68-Pin QFN (derate 41.7mW/°C above | ∋ +70°C)      |

|------------------------------------|---------------|

| (Note 1)                           |               |

| Junction Temperature               | +150°C        |

| Operating Temperature Range        | 40°C to +85°C |

| Storage Temperature Range          |               |

| Lead Temperature (soldering, 10s)  | +300°C        |

Note 1: Thermal resistance based on a multilayer board with 4 x 4 via array in exposed paddle area.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

| PARAMETER                    | SYMBOL           | CONDITIONS                                                                                      |                  | MIN   | ТҮР    | МАХ   | UNITS    |

|------------------------------|------------------|-------------------------------------------------------------------------------------------------|------------------|-------|--------|-------|----------|

| STATIC PERFORMANCE           |                  |                                                                                                 |                  |       |        |       | <u> </u> |

| Resolution                   |                  |                                                                                                 |                  |       | 16     |       | Bits     |

| Differential Nonlinearity    | DNL              |                                                                                                 |                  |       | ±1     |       | LSB      |

| Integral Nonlinearity        | INL              |                                                                                                 |                  |       | ±3     |       | LSB      |

| Offset Error                 | OS               |                                                                                                 |                  | -0.02 | ±0.003 | +0.02 | %FS      |

| Offset Drift                 |                  |                                                                                                 |                  |       | ±0.03  |       | ppm/°C   |

| Gain Error                   | GE <sub>FS</sub> | (Note 3)                                                                                        |                  | -4    | ±0.06  | +4    | %FS      |

| Gain-Error Drift             |                  |                                                                                                 |                  |       | ±110   |       | ppm/°C   |

| Full-Scale Output Current    | IOUTFS           | (Note 3)                                                                                        |                  | 2     |        | 20    | mA       |

| Output Compliance            |                  |                                                                                                 |                  | -0.5  |        | +1.1  | V        |

| Output Resistance            | Rout             |                                                                                                 |                  |       | 1      |       | MΩ       |

| Output Capacitance           | Соит             |                                                                                                 |                  |       | 5      |       | pF       |

| DYNAMIC PERFORMANCE          |                  |                                                                                                 |                  |       |        |       | <u>.</u> |

| Maximum Clock Frequency      | fCLK             |                                                                                                 |                  | 500   |        |       | MHz      |

| Minimum Clock Frequency      | fCLK             |                                                                                                 |                  |       |        | 10    | MHz      |

| Maximum DAC Update Rate      | fdac             | $f_{DAC} = f_{CLK} \text{ or } f_{DAC} = f_{CLK}$                                               | clk / 2          | 500   |        |       | Msps     |

| Minimum DAC Update Rate      | fdac             | $f_{DAC} = f_{CLK} \text{ or } f_{DAC} = f_{CLK}$                                               | clk / 2          |       |        | 10    | Msps     |

| Maximum Data Clock Frequency | <b>f</b> DATACLK | Interleaved data                                                                                |                  | 250   |        |       | MHz      |

| Maximum Input Data Rate      | fdata            | Per channel                                                                                     |                  | 125   |        |       | MWps     |

|                              |                  | f <sub>DATA</sub> = 125Mwps,                                                                    | No interpolation |       | -156   |       |          |

|                              |                  | $f_{OUT} = 16MHz, f_{OFFSET}$                                                                   | 2x interpolation |       | -157   |       |          |

|                              |                  | = 10MHz, -12dBFS                                                                                | 4x interpolation | -157  |        | dBFS/ |          |

| Noise Spectral Density       |                  | f <sub>DATA</sub> = 125Mwps,<br>f <sub>OUT</sub> = 16MHz, f <sub>OFFSET</sub><br>= 10MHz, 0dBFS | 4x interpolation |       | -154   |       | Hz       |

### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER SYMB                                |                                                             | CONDITIONS                                                                                           |                                                                             | MIN | ТҮР | MAX | UNITS |

|-----------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|-------|

|                                               |                                                             | f <sub>DATA</sub> = 125Mwps,                                                                         | f <sub>OUT</sub> = 10MHz                                                    |     | 90  |     |       |

|                                               |                                                             | interpolation off,                                                                                   | fout = 30MHz                                                                |     | 84  |     | -     |

|                                               |                                                             | -0.1dBFS                                                                                             | $f_{OUT} = 50 MHz$                                                          |     | 77  |     |       |

|                                               | f <sub>DATA</sub> = 125Mwps, f <sub>OUT</sub> = 10MHz 79 89 |                                                                                                      |                                                                             |     |     |     |       |

| In-Band SFDR<br>(DC to f <sub>DATA</sub> / 2) | SFDR                                                        | 2x interpolation,                                                                                    | fout = 30MHz                                                                |     | 83  |     | dBc   |

|                                               |                                                             | -0.1dBFS                                                                                             | fout = 50MHz                                                                |     | 92  |     |       |

|                                               |                                                             | f <sub>DATA</sub> = 125Mwps,                                                                         | $f_{OUT} = 10MHz$                                                           |     | 89  |     |       |

|                                               |                                                             | 4x interpolation,                                                                                    | $f_{OUT} = 30MHz$                                                           |     | 83  |     |       |

|                                               |                                                             | -0.1dBFS                                                                                             | $f_{OUT} = 50MHz$                                                           |     | 89  |     |       |

|                                               |                                                             | f <sub>DATA</sub> = 125Mwps,                                                                         | No interpolation                                                            |     | -96 |     |       |

|                                               |                                                             | fout1 = 9MHz, fout2 =                                                                                | 2x interpolation                                                            |     | -99 |     |       |

|                                               |                                                             | 10MHz, -6.1dBFS                                                                                      | 4x interpolation                                                            |     | -95 |     |       |

|                                               |                                                             | f <sub>DATA</sub> = 125Mwps,<br>f <sub>OUT1</sub> = 79MHz,                                           | 2x interpolation,<br>f <sub>IM</sub> / 4 complex<br>modulation              |     | -81 |     |       |

|                                               |                                                             | f <sub>OUT2</sub> = 80MHz,<br>-6.1dBFS                                                               | 4x interpolation,<br>f <sub>IM</sub> / 4 complex<br>modulation              |     | -71 |     |       |

| Two-Tone IMD                                  | TTIMD                                                       | $f_{DATA} = 62.5Mwps,$<br>$f_{OUT1} = 9MHz, f_{OUT2} =$<br>10MHz, -6.1dBFS                           | 8x interpolation                                                            |     | -94 |     | dBc   |

|                                               |                                                             | $f_{DATA} = 62.5Mwps,$<br>$f_{OUT1} = 69MHz, f_{OUT2}$<br>= 70MHz, -6.1dBFS                          | 8x interpolation,<br>f <sub>IM</sub> / 4 complex<br>modulation              |     | -71 |     |       |

|                                               |                                                             | f <sub>DATA</sub> = 62.5Mwps,<br>f <sub>OUT1</sub> = 179MHz, f <sub>OUT2</sub><br>= 180MHz, -6.1dBFS | 8x, highpass<br>interpolation,<br>f <sub>IM</sub> / 4 complex<br>modulation |     | -71 |     |       |

| Four-Tone IMD                                 | FTIMD                                                       | f <sub>DATA</sub> = 125Mwps, f <sub>OUT</sub><br>apart from 32MHz, -12df<br>interpolation            |                                                                             |     | -89 |     | dBc   |

|                                               |                                                             | f <sub>DATA</sub> = 61.44Mwps,                                                                       | 4x interpolation                                                            |     | 79  |     |       |

|                                               |                                                             | $f_{OUT} = baseband$                                                                                 | 8x interpolation                                                            |     | 79  |     | İ     |

| ACLR for WCDMA<br>(Note 4)                    | ACLR                                                        | f <sub>DATA</sub> = 122.88Mwps,<br>f <sub>OUT</sub> = 61.44MHz                                       | 2x interpolation,<br>f <sub>IM</sub> / 4 complex<br>modulation              |     | 76  |     | dB    |

|                                               |                                                             | $f_{DATA} = 122.88Mwps,$<br>$f_{OUT} = 122.88MHz$                                                    | 4x interpolation,<br>f <sub>IM</sub> / 4 complex<br>modulation              |     | 68  |     |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                  | SYMBOL             | CONDITIONS                                               | MIN                          | ТҮР            | МАХ                          | UNITS  |

|----------------------------|--------------------|----------------------------------------------------------|------------------------------|----------------|------------------------------|--------|

| Output Propagation Delay   | tPD                | 1x interpolation (Note 5)                                |                              | 2.9            |                              | ns     |

| Output Rise Time           | tRISE              | 10% to 90% (Note 6)                                      |                              | 0.75           |                              | ns     |

| Output Fall Time           | tFALL              | 10% to 90% (Note 6)                                      |                              | 1              |                              | ns     |

| Output Settling Time       |                    | To 0.5% (Note 6) 11                                      |                              |                | ns                           |        |

| Output Bandwidth           |                    | -1dB bandwidth (Note 7)                                  |                              | 240            |                              | MHz    |

| Passband Width             |                    | Ripple < -0.01dB                                         |                              | 0.4 x<br>fdata |                              |        |

|                            |                    | 0.604 x f <sub>DATA</sub> , 2x interpolation             |                              | 100            |                              |        |

| Stopband Rejection         |                    | 0.604 x f <sub>DATA</sub> , 4x interpolation             |                              | 100            |                              | dB     |

|                            |                    | 0.604 x f <sub>DATA</sub> , 8x interpolation             |                              | 100            |                              |        |

|                            |                    | 1x interpolation                                         |                              | 22             |                              |        |

|                            | İ                  | 2x interpolation                                         |                              | 70             |                              | Clock  |

| Data Latency               |                    | 4x interpolation                                         |                              | 146            |                              | Cycles |

|                            |                    | 8x interpolation                                         |                              | 311            |                              |        |

| DAC INTERCHANNEL MATCH     | ING                |                                                          | •                            |                |                              |        |

| Gain Match                 | ∆Gain              | f <sub>OUT</sub> = DC - 80MHz, I <sub>OUTFS</sub> = 20mA |                              | ±0.1           |                              | dB     |

| Gain-Match Tempco          | ∆Gain/°C           | IOUTFS = 20mA                                            |                              | ±0.02          |                              | ppm/°C |

| Phase Match                | ∆Phase             | $f_{OUT} = 60MHz, I_{OUTFS} = 20mA$                      |                              | ±0.13          |                              | Deg    |

| Phase-Match Tempco         | ∆Phase/°C          | IOUTFS = 20mA                                            | ±0.006                       |                |                              | Deg/°C |

| DC Gain Match              |                    | IOUTFS = 20mA (Note 3)                                   | -0.2 ±0.04 +0.2              |                | +0.2                         | dB     |

| Crosstalk                  |                    | $f_{OUT} = 50MHz$ , $f_{DAC} = 250MHz$                   |                              | -95            |                              | dB     |

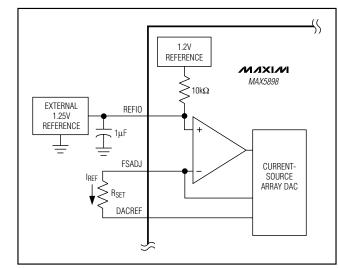

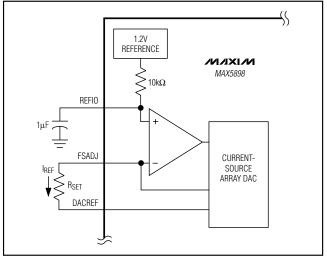

| REFERENCE                  | ·                  |                                                          |                              |                |                              |        |

| Reference Input Range      |                    |                                                          | 0.12                         |                | 1.32                         | V      |

| Reference Output Voltage   | VREFIO             | Internal reference                                       | 1.14                         | 1.2            | 1.28                         | V      |

| Reference Input Resistance | R <sub>REFIO</sub> |                                                          |                              | 10             |                              | kΩ     |

| Reference Voltage Drift    |                    |                                                          |                              | ±50            |                              | ppm/°C |

| CMOS LOGIC INPUTS (SCLK,   | CS, RESET, DI      | ۷)                                                       |                              |                |                              |        |

| Input High Voltage         | VIH                |                                                          | 0.7 x<br>DV <sub>DD3.3</sub> |                |                              | V      |

| Input Low Voltage          | VIL                |                                                          |                              |                | 0.3 x<br>DV <sub>DD3.3</sub> | V      |

| Input Current              | l <sub>IN</sub>    |                                                          | -10                          | ±0.1           | +10                          | μA     |

| Input Capacitance          | CIN                |                                                          |                              | 3              |                              | рF     |

| CMOS LOGIC OUTPUT (DOUT    | )                  |                                                          |                              |                |                              |        |

| Output High Voltage        | Vон                | I <sub>LOAD</sub> = 200µA                                | 0.8 x<br>DV <sub>DD3.3</sub> |                |                              | V      |

| Output Low Voltage         | V <sub>OL</sub>    | I <sub>SINK</sub> = 200μA                                |                              |                | 0.2 x<br>DV <sub>DD3.3</sub> | V      |

| Output Leakage Current     |                    | Tri-state                                                |                              | 1              |                              | μA     |

### **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                          | SYMBOL              | CONDITIONS                                                         | MIN   | TYP                      | MAX   | UNITS |

|------------------------------------|---------------------|--------------------------------------------------------------------|-------|--------------------------|-------|-------|

| Rise/Fall Time                     |                     | C <sub>LOAD</sub> = 10pF, 20% to 80%                               |       | 1.5                      |       | ns    |

| LVDS LOGIC INPUTS (D15P-D0F        | , D15N–D0N          | , SELIQP, SELIQN)                                                  |       |                          |       |       |

| Differential Input Logic High      | VIH                 |                                                                    | 100   |                          |       | mV    |

| Differential Input Logic Low       | VIL                 |                                                                    |       |                          | -100  | mV    |

| Input Common-Mode Voltage          | VICM                |                                                                    | 1.125 | 1.25                     | 1.375 | V     |

| Differential Input Resistance      | RIN                 |                                                                    |       | 110                      |       | Ω     |

| Input Capacitance                  | CIN                 |                                                                    |       | 2.5                      |       | рF    |

| LVDS CLOCK INPUT/OUTPUT (D         | ATACLKP, D          | DATACLKN)                                                          |       |                          |       |       |

| Differential Input Amplitude High  | VIH                 |                                                                    | 250   |                          |       | mV    |

| Differential Input Amplitude Low   | VIL                 |                                                                    |       |                          | -250  | mV    |

| Differential Output Amplitude High | Voh                 | $R_{LOAD} = 100\Omega$ differential (Note 3)                       | 250   | 340                      |       | mV    |

| Differential Output Amplitude Low  | Vol                 | $R_{LOAD} = 100\Omega$ differential (Note 3)                       |       | -340                     | -250  | mV    |

| Output Common-Mode Voltage         | Vocm                |                                                                    |       | 1.25                     |       | V     |

| Output Rise/Fall Time              |                     | $R_{LOAD} = 100\Omega$ differential, $C_{LOAD} = 8pF$ , 20% to 80% |       | 0.9                      |       | ns    |

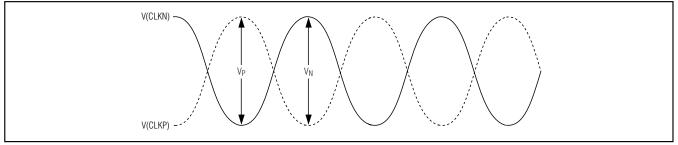

| CLOCK INPUTS (CLKP, CLKN) (        | Note 8)             |                                                                    | •     |                          |       | •     |

|                                    |                     | Sine-wave input                                                    | > 1.5 |                          |       |       |

| Differential Input Voltage Swing   | VDIFF               | Square-wave input                                                  |       | > 0.5                    |       | VP-P  |

| Differential Input Slew Rate       |                     |                                                                    |       | > 100                    |       | V/µs  |

| Common-Mode Voltage                | V <sub>COM</sub>    | AC-coupled                                                         |       | AV <sub>CLK</sub> /<br>2 |       | V     |

| Differential Input Resistance      | RCLK                |                                                                    |       | 5                        |       | kΩ    |

| Differential Input Capacitance     | C <sub>CLK</sub>    |                                                                    |       | 5                        |       | рF    |

| Minimum Clock Duty Cycle           | 0 EIX               |                                                                    |       | 45                       |       | %     |

| Maximum Clock Duty Cycle           |                     |                                                                    |       | 55                       |       | %     |

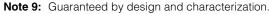

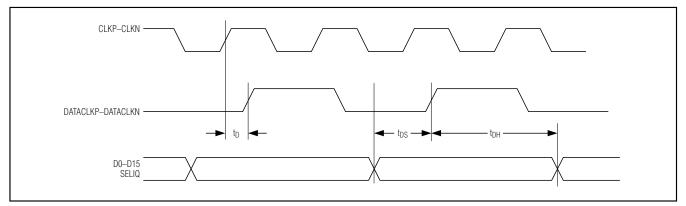

| CLKP/CLKN, DATACLK TIMING          | Figure 4) (No       | ote 9)                                                             |       |                          |       |       |

| CLK to DATACLK Delay               | tD                  | DATACLK output mode                                                |       | 1.4                      |       | ns    |

| Data Hold Time                     | tDH                 |                                                                    | 1.65  |                          |       | ns    |

| Data Setup Time                    | tDS                 |                                                                    | -0.65 |                          |       | ns    |

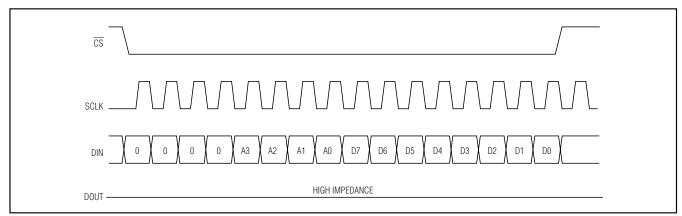

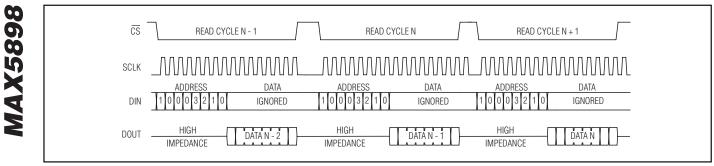

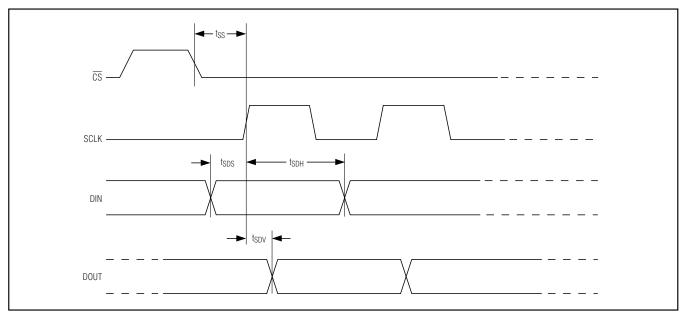

| SERIAL-PORT INTERFACE TIMIN        | G (Figure 3)        | (Note 9)                                                           |       |                          |       |       |

| SCLK Frequency                     | fSCLK               |                                                                    |       |                          | 10    | MHz   |

| CS Setup Time                      | tss                 |                                                                    | 2.5   |                          |       | ns    |

| Input Hold Time                    | tSDH                |                                                                    | 0     |                          |       | ns    |

| Input Setup Time                   | tsds                |                                                                    | 4.5   |                          |       | ns    |

| Data Valid Duration                | tsdv                |                                                                    | 6.5   |                          | 16.5  | ns    |

| POWER SUPPLIES                     |                     |                                                                    |       |                          |       | •     |

| Digital Supply Voltage             | DV <sub>DD1.8</sub> |                                                                    | 1.71  | 1.8                      | 1.89  | V     |

| Digital I/O Supply Voltage         | DV <sub>DD3.3</sub> |                                                                    | 3.0   | 3.3                      | 3.6   | V     |

| ¥                                  |                     |                                                                    | 1     |                          |       | 1     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD1.8} = AV_{DD1.8} = 1.8V, AV_{CLK} = AV_{DD3.3} = DV_{DD3.3} = 3.3V$ , modulator off, 2x interpolation, DATACLK output mode, output is 50 $\Omega$  double-terminated, external reference at 1.25V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                                           | SYMBOL              | CONDITION                                                          | S                                                                               | MIN   | ТҮР   | МАХ   | UNITS |  |

|-----------------------------------------------------|---------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Clock Supply Voltage                                | AVCLK               |                                                                    |                                                                                 |       | 3.3   | 3.465 | V     |  |

| Apples Supply Voltage                               | AV <sub>DD3.3</sub> |                                                                    |                                                                                 | 3.135 | 3.3   | 3.465 | V     |  |

| Analog Supply Voltage                               | AV <sub>DD1.8</sub> |                                                                    |                                                                                 |       | 1.8   | 1.89  | V     |  |

| Apples Supply Ourrent                               | IAVDD3.3            | f <sub>CLK</sub> = 250MHz, 2x interpol<br>f <sub>OUT</sub> = 10MHz | f <sub>CLK</sub> = 250MHz, 2x interpolation, 0dBFS,<br>f <sub>OUT</sub> = 10MHz |       | 111   | 130   |       |  |

| Analog Supply Current                               | IAVDD1.8            | $f_{CLK} = 250MHz$ , 2x interpol<br>$f_{OUT} = 10MHz$              | ation, 0dBFS,                                                                   |       | 27    | 32    | mA    |  |

| Digital Supply Current                              | IDVDD1.8            | $f_{CLK} = 250MHz$ , 2x interpol $f_{OUT} = 10MHz$                 | f <sub>CLK</sub> = 250MHz, 2x interpolation, 0dBFS,<br>f <sub>OUT</sub> = 10MHz |       | 229   | 250   | mA    |  |

| Digital I/O Supply Current                          | IDVDD3.3            | $f_{CLK} = 250MHz$ , 2x interpolation, 0dBFS,<br>$f_{OUT} = 10MHz$ |                                                                                 |       | 9     | 12    | mA    |  |

| Clock Supply Current                                | IAVCLK              | $f_{CLK} = 250MHz$ , 2x interpol<br>$f_{OUT} = 10MHz$              | ation, 0dBFS,                                                                   |       | 2.3   | 4     | mA    |  |

| Total Power Dissipation                             | Ptotal              | f <sub>CLK</sub> = 250MHz, 2x interpol<br>f <sub>OUT</sub> = 10MHz | ation, 0dBFS,                                                                   |       | 831   |       | mW    |  |

|                                                     |                     |                                                                    | AV <sub>DD3.3</sub>                                                             |       | 530   |       |       |  |

|                                                     |                     | All I/O are static high or                                         | AV <sub>DD1.8</sub>                                                             |       | 1     |       |       |  |

| Power-Down Current                                  |                     | low, bit 2 to bit 4 of                                             | DV <sub>DD1.8</sub>                                                             |       | 26    |       | μΑ    |  |

|                                                     |                     | address 00h are set high                                           | DV <sub>DD3.3</sub>                                                             |       | 350   |       | ]     |  |

|                                                     |                     | AV <sub>CLK</sub>                                                  |                                                                                 |       | 2     |       |       |  |

| AV <sub>DD3.3</sub> Power-Supply Rejection<br>Ratio | PSRRA               | (Note 10)                                                          |                                                                                 |       | 0.125 |       | %FS/V |  |

**Note 2:** All specifications are 100% tested at  $T_A \ge +25^{\circ}$ C. Specifications at  $T_A < +25^{\circ}$ C are guaranteed by design and characterization.

**Note 3:** Specification is 100% production tested at  $T_A \ge +25^{\circ}C$ .

Note 4: 3.84MHz bandwidth, single carrier.

Note 5: Excludes data latency.

**Note 6:** Measured single-ended into a  $50\Omega$  load.

**Note 7:** Excludes sin(x)/x rolloff.

Note 8: Differential voltage swing defined as  $|V_P| + |V_N|$ .

Note 10: Parameter defined as the change in midscale output caused by a ±5% variation in the nominal supply voltage.

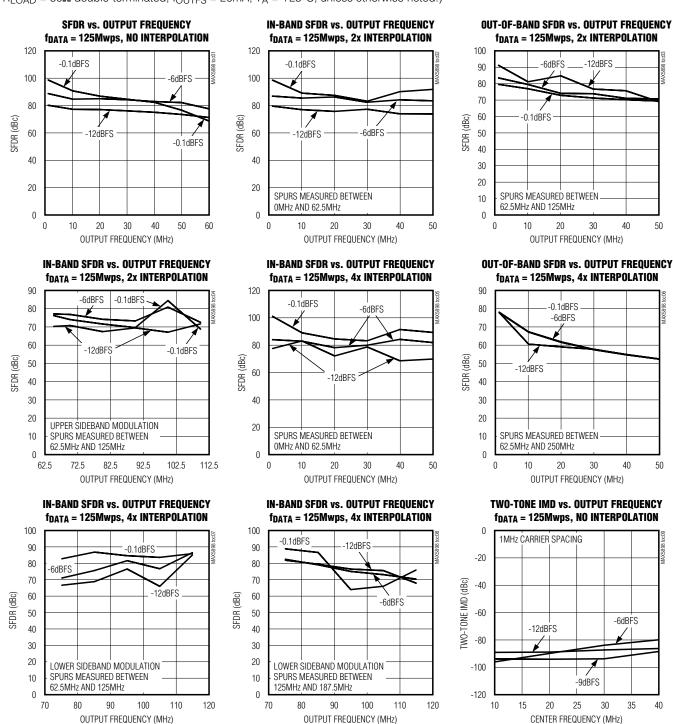

### **Typical Operating Characteristics**

$(DV_{DD1.8} = AV_{DD1.8} = 1.8V, AV_{CLK} = AV_{DD3.3} = DV_{DD3.3} = 3.3V, DATACLK output mode, external reference, V_{REFIO} = +1.25V, R_{LOAD} = 50\Omega$  double-terminated, I<sub>OUTFS</sub> = 20mA, T<sub>A</sub> = +25°C, unless otherwise noted.)

M/IXI/M

**MAX5898**

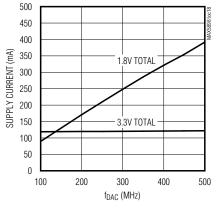

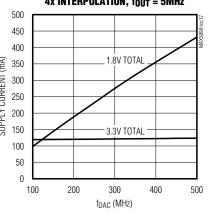

### fDATA = 125Mwps, 2x INTERPOLATION fDATA = 125Mwps, 4x INTERPOLATION 0 0 1MHz CARRIER SPACING 1MHz CARRIER SPACING COMPLEX MODULATION FOR COMPLEX MODULATION FOR -20 **OUTPUT FREQUENCIES** -20 **OUTPUT FREQUENCIES** GREATER THAN 50MHz GREATER THAN 50MHz TWO-TONE IMD (dBc) -40 TWO-TONE IMD (dBc) -40 -6dBFS -60 -60 -12dBFS -12dBFS -80 -80 -100 -100 -9dBFS -9dBFS -6dBFS -6dBES -120 -120 10 25 55 70 85 100 35 60 85 40 10 110 CENTER FREQUENCY (MHz) CENTER FREQUENCY (MHz) **EIGHT-TONE POWER RATIO PLOT** DIFFERENTIAL NONLINEARITY fDATA = 125Mwps, 2x INTERPOLATION vs. DIGITAL INPUT CODE -20 3.0 -30 2.5 -40 20 -50 OUTPUT POWER (dBm) 1.5 -60 DNL (LSB) -70 1.0 -80 0.5 -90 0 -100 -0.5 -110 -120 -10 f<sub>CENTER</sub> = 35.7MHz, 1MHz TONE SPACING 16,384 32,768 49,152 0 $SPAN = 12.5 MHz, A_{OUT1} THROUGH A_{OUT8} = -18 dBFS$ DIGITAL INPUT CODE SUPPLY CURRENT vs. DAC UPDATE RATE SUPPLY CURRENT vs. DAC UPDATE RATE 2x INTERPOLATION, four = 5MHz 4x INTERPOLATION, four = 5MHz 500 500 450 450 400 400 1.8V TOTAL (mA) 350 350 300 300 1.8V TOTAL

### Typical Operating Characteristics (continued)

(DVDD1.8 = AVDD1.8 = 1.8V, AVCLK = AVDD3.3 = DVDD3.3 = 3.3V, DATACLK output mode, external reference, VREFIO = +1.25V,  $R_{LOAD} = 50\Omega$  double-terminated,  $I_{OUTFS} = 20$ mA,  $T_A = +25$ °C, unless otherwise noted.)

-6dBFS

-12dBES

135

160

65,536

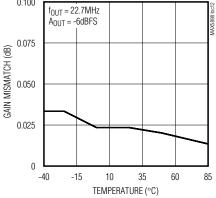

### **CHANNEL-TO-CHANNEL TWO-TONE IMD vs. OUTPUT FREQUENCY GAIN MISMATCH vs. TEMPERATURE** fDATA = 125Mwps, 2x INTERPOLATION 0.100

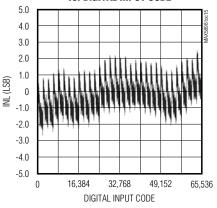

**INTEGRAL NONLINEARITY** vs. DIGITAL INPUT CODE

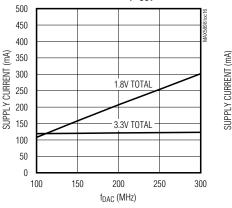

SUPPLY CURRENT vs. DAC UPDATE RATE 8x INTERPOLATION, fout = 5MHz

**TWO-TONE IMD vs. OUTPUT FREQUENCY**

### Typical Operating Characteristics (continued)

(DVDD1.8 = AVDD1.8 = 1.8V, AVCLK = AVDD3.3 = DVDD3.3 = 3.3V, DATACLK output mode, external reference, VREFIO = +1.25V,  $R_{LOAD} = 50\Omega$  double-terminated,  $I_{OUTES} = 20$ mA,  $T_A = +25$ °C, unless otherwise noted.)

-110 -120

**MAX5898**

### Pin Description

| 1         CLKP         Noninverting Differential Clock Input. Internally biased to AV <sub>CLK</sub> / 2.           2         CLKN         Internally Connected. Do not connect.           3         N.C.         Internally Connected. Do not connect.           4         DATACLKP         LVDS Data Clock Input/Output. External 1000 termination to DATACLKP required.           5         DATACLKN         Complementary LVDS Data Clock Input/Output. External 1000 termination to DATACLKP required.           6, 21, 30, 37         DVDD18.         Digital Power Supply. Accepts a 1.71V to 1.89V supply range. Bypass each pin to ground with a 0.1µF capacitor as close to the pin as possible.           7         SELION         complementary LVDS Channel Select Input. Set SELIQN low and SELIQP high to direct data to the channel. Internal 1100 termination to SELIQP.           8         SELIOP         LVDS Channel Select Input. Set SELIQN low and SELIQP high to direct data to the channel. Internal 1100 termination to D15N.           10         D15N         Complementary LVDS Data Bit 15 (MSB). Internal 1100 termination to D15N.           11         D14N         Complementary LVDS Data Bit 15 (MSB). Internal 1100 termination to D15N.           12         D14P         LVDS Data Bit 13. (MSB). Internal 1100 termination to D15N.           13         D13N         Complementary LVDS Data Bit 1.10 (MSB).           14         D13P         LVDS Data Bit 13. Internal 1100 termination to D13N.<                                     | PIN           | NAME                | FUNCTION                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|----------------------------------------------------------------------------------------------------|

| 3         N.C.         Internally Connected. Do not connect.           4         DATACLKP         LVDS Data Clock Input/Output. External 100Ω termination to DATACLKN required.           5         DATACLKN         Complementary LVDS Data Clock Input/Output. External 100Ω termination to DATACLKN required.           6, 21, 30, 37         DV <sub>DD1.8</sub> Digital Power Supply. Accepts a 1.71V to 1.89V supply range. Bypass each pin to ground with a 0.1µF capacitor as close to the pin as possible.           7         SELIQN         Complementary LVDS Channel Select Input. Set SELIQN low and SELIQP high to direct data to the channel. Set SELIQP low and SELIQP low and SELIQP.           8         SELIQP         LVDS Channel Select Input. Set SELIQN low and SELIQP high to direct data to the channel. Set SELIQP low and SELIQN low and SELIQP high to direct data to the channel. Internal 110Ω termination to D15P.           9         D15N         Complementary LVDS Data Bit 15 (MSB). Internal 110Ω termination to D14P.           11         D14N         Complementary LVDS Data Bit 14. Internal 110Ω termination to D14N.           13         D13N         Complementary LVDS Data Bit 13. Internal 110Ω termination to D14N.           14         D13P         Complementary LVDS Data Bit 13. Internal 110Ω termination to D14N.           13         D13N         Complementary LVDS Data Bit 13. Internal 110Ω termination to D14N.           14         D13P         Complementary LVDS Data Bit 13. Internal 110Ω termination to D | 1             | CLKP                | Noninverting Differential Clock Input. Internally biased to AV <sub>CLK</sub> / 2.                 |

| 4         DATACLKP         LVDS Data Clock Input/Output. External 100Ω termination to DATACLKN required.           5         DATACLKN         Complementary LVDS Data Clock Input/Output. External 100Ω termination to DATACLKP required.           6, 21, 30, 37         DVD1.8         Digital Power Supply. Accepts a 1.71V to 1.89V supply range. Bypass each pin to ground with a 0.1µF capacitor as close to the pin as possible.           7         SELION         Complementary LVDS Channel Select Input. Set SELIQN low and SELIOP high to direct data to the channel. Internal 110Ω termination to SELIQP.           8         SELIOP         LVDS Channel Select Input. Set SELIQN low and SELIOP high to direct data to the channel. Internal 110Ω termination to SELIQN.           9         D15N         Complementary LVDS Data Bit 15 (MSB). Internal 110Ω termination to D15P.           10         D15P         LVDS Data Bit 15 (MSB). Internal 110Ω termination to D14P.           11         D14N         Complementary LVDS Data Bit 13. Internal 110Ω termination to D14P.           12         D14P         LVDS Data Bit 13. Internal 110Ω termination to D14P.           13         D13N         Complementary LVDS Data Bit 13. Internal 110Ω termination to D14P.           14         D13P         LVDS Data Bit 13. Internal 110Ω termination to D14P.           15         D12N         Complementary LVDS Data Bit 12. Internal 110Ω termination to D12P.           16         D12P         LVDS D                                               | 2             | CLKN                | Inverting Differential Clock Input. Internally biased to AV <sub>CLK</sub> / 2.                    |

| 5         DATACLKN         Complementary LVDS Data Clock Input/Output. External 100Ω termination to DATACLKP required           6, 21, 30, 37         DV <sub>DD1.8</sub> Digital Power Supply. Accepts a 1.71V to 1.89V supply range. Bypass each pin to ground with a<br>0.1µF capacitor as close to the pin as possible.           7         SELION         Complementary LVDS Channel Select Input. Set SELION low and SELIOP high to direct data to the channel. Internal 110Ω termination to SELIOP.           8         SELIOP         LVDS Channel Select Input. Set SELIOP high to direct data to the channel. Internal 110Ω termination to SELION.           9         D15N         Complementary LVDS Data Bit 15 (MSB). Internal 110Ω termination to D15P.           10         D15P         LVDS Data Bit 15 (MSB). Internal 110Ω termination to D15N.           11         D14N         Complementary LVDS Data Bit 13. Internal 110Ω termination to D14P.           12         D14P         LVDS Data Bit 14. Internal 110Ω termination to D13N.           13         D13N         Complementary LVDS Data Bit 13. Internal 110Ω termination to D13P.           14         D13P         LVDS Data Bit 13. Internal 110Ω termination to D13P.           15         D12N         Complementary LVDS Data Bit 11. Internal 110Ω termination to D12P.           16         D12P         LVDS Data Bit 11. Internal 110Ω termination to D12P.           17         D11N         Complementary LVDS Data Bit 11. Internal 110Ω t                                          | 3             | N.C.                | Internally Connected. Do not connect.                                                              |

| 6, 21, 30, 37         DV <sub>DD1.8</sub> Digital Power Supply. Accepts a 1.71V to 1.89V supply range. Bypass each pin to ground with a 0.1µF capacitor as close to the pin as possible.           7         SELIQN         Complementary LVDS Channel Select Input. Set SELIQN Iow and SELIQP high to direct data to the channel. Internal 1100           8         SELIOP         LVDS Channel Select Input. Set SELIQN low and SELIQP high to direct data to the channel. Internal 1100           9         D15N         Complementary LVDS Data Bit 15 (MSB). Internal 1100 termination to D15P.           10         D15P         LVDS Data Bit 15 (MSB). Internal 1100 termination to D15P.           11         D14N         Complementary LVDS Data Bit 14. Internal 1100 termination to D15P.           12         D14P         LVDS Data Bit 15 (MSB). Internal 1100 termination to D14P.           13         D13N         Complementary LVDS Data Bit 13. Internal 1100 termination to D13P.           14         D13P         LVDS Data Bit 13. Internal 1100 termination to D12P.           16         D12P         LVDS Data Bit 12. Internal 1100 termination to D12P.           17         D11N         Complementary LVDS Data Bit 11. Internal 1100 termination to D12P.           18         D12P         LVDS Data Bit 13. Internal 1100 termination to D12P.           18         D12P         LVDS Data Bit 11. Internal 1100 termination to D12N.           17         D11N<                                                                               | 4             | DATACLKP            | LVDS Data Clock Input/Output. External $100\Omega$ termination to DATACLKN required.               |

| 6, 21, 30, 37       DVDD1.8       0.1µF capacitor as close to the pin as possible.       DVD1.8         7       SELIQN       Complementary LVDS Channel Select Input. Set SELIQN low and SELIQP high to direct data to the channel. Internal 1100 termination to SELIQP.         8       SELIQP       LVDS Channel Select Input. Set SELIQN low and SELIQP high to direct data to the channel. Internal 1100 termination to SELIQP.         9       D15N       Complementary LVDS Data Bit 15 (MSB). Internal 1100 termination to D15P.         10       D15P       LVDS Data Bit 15 (MSB). Internal 1100 termination to D14P.         11       D14N       Complementary LVDS Data Bit 14. Internal 1100 termination to D14P.         12       D14P       LVDS Data Bit 14. Internal 1100 termination to D14P.         13       D13N       Complementary LVDS Data Bit 12. Internal 1100 termination to D13P.         14       D13P       LVDS Data Bit 13. Internal 1100 termination to D13P.         15       D12N       Complementary LVDS Data Bit 12. Internal 1100 termination to D12P.         16       D12P       LVDS Data Bit 12. Internal 1100 termination to D11P.         17       D11N       Complementary LVDS Data Bit 10. Internal 1100 termination to D10P.         20       D10P       LVDS Data Bit 10. Internal 1100 termination to D10P.         21       D11N       Complementary LVDS Data Bit 10. Internal 1100 termination to D10P.                                                                                                                      | 5             | DATACLKN            | Complementary LVDS Data Clock Input/Output. External $100\Omega$ termination to DATACLKP required. |

| 7       SELIQN       the channel. Set SELIOP low and SELIQN high to direct data to the channel. Internal 110Ω termination to SELIQP.         8       SELIOP       LVDS Channel Select Input. Set SELION low and SELIQP high to direct data to the channel. Internal 110Ω termination to SELIQN.         9       D15N       Complementary LVDS Data Bit 15 (MSB). Internal 110Ω termination to D15P.         10       D15P       LVDS Data Bit 15 (MSB). Internal 110Ω termination to D15N.         11       D14N       Complementary LVDS Data Bit 10. Internal 110Ω termination to D14N.         12       D14P       LVDS Data Bit 14. Internal 110Ω termination to D14N.         13       D13N       Complementary LVDS Data Bit 13. Internal 110Ω termination to D13P.         14       D13P       LVDS Data Bit 13. Internal 110Ω termination to D13N.         15       D12N       Complementary LVDS Data Bit 12. Internal 110Ω termination to D12P.         16       D12P       LVDS Data Bit 11. Internal 110Ω termination to D11P.         18       D11P       LVDS Data Bit 11. Internal 110Ω termination to D10P.         20       D10N       Complementary LVDS Data Bit 10. Internal 110Ω termination to D10P.         21       D11N       Complementary LVDS Data Bit 10. Internal 110Ω termination to D10P.         22       D9N       Complementary LVDS Data Bit 10. Internal 110Ω termination to D10P.         23       D9P<                                                                                                                                      | 6, 21, 30, 37 | DV <sub>DD1.8</sub> |                                                                                                    |

| 8         SELIQP         SELIQP low and SELIQN high to direct data to the channel. Internal 110Ω termination to SELIQN.           9         D15N         Complementary LVDS Data Bit 15 (MSB). Internal 110Ω termination to D15P.           10         D15P         LVDS Data Bit 15 (MSB). Internal 110Ω termination to D15N.           11         D14N         Complementary LVDS Data Bit 14. Internal 110Ω termination to D14P.           12         D14P         LVDS Data Bit 14. Internal 110Ω termination to D14N.           13         D13N         Complementary LVDS Data Bit 13. Internal 110Ω termination to D13P.           14         D13P         LVDS Data Bit 13. Internal 110Ω termination to D12P.           16         D12P         LVDS Data Bit 12. Internal 110Ω termination to D12N.           17         D11N         Complementary LVDS Data Bit 11. Internal 110Ω termination to D11P.           18         D11P         LVDS Data Bit 11. Internal 110Ω termination to D10P.           20         D10N         Complementary LVDS Data Bit 10. Internal 110Ω termination to D10P.           21         D9N         Complementary LVDS Data Bit 9. Internal 110Ω termination to D10P.           22         D9N         Complementary LVDS Data Bit 9. Internal 110Ω termination to D3P.           23         D9P         LVDS Data Bit 9. Internal 110Ω termination to D3P.           24         D8N         Com                                                                                                                                       | 7             | SELIQN              | the channel. Set SELIQP low and SELIQN high to direct data to the channel. Internal 110 $\Omega$   |

| 10       D15P       LVDS Data Bit 15 (MSB). Internal 110Ω termination to D15N.         11       D14N       Complementary LVDS Data Bit 14. Internal 110Ω termination to D14P.         12       D14P       LVDS Data Bit 14. Internal 110Ω termination to D14N.         13       D13N       Complementary LVDS Data Bit 13. Internal 110Ω termination to D13P.         14       D13P       LVDS Data Bit 13. Internal 110Ω termination to D13N.         15       D12N       Complementary LVDS Data Bit 12. Internal 110Ω termination to D12P.         16       D12P       LVDS Data Bit 12. Internal 110Ω termination to D11P.         17       D11N       Complementary LVDS Data Bit 11. Internal 110Ω termination to D11P.         18       D11P       LVDS Data Bit 11. Internal 110Ω termination to D10P.         20       D10N       Complementary LVDS Data Bit 10. Internal 110Ω termination to D10P.         21       D9N       Complementary LVDS Data Bit 9. Internal 110Ω termination to D10P.         22       D9N       Complementary LVDS Data Bit 9. Internal 110Ω termination to D8P.         23       D9P       LVDS Data Bit 9. Internal 110Ω termination to D8P.         24       D8N       Complementary LVDS Data Bit 8. Internal 110Ω termination to D7P.         25       D8P       LVDS Data Bit 7. Internal 110Ω termination to D7P.         27       D7P <t< td=""><td>8</td><td>SELIQP</td><td></td></t<>                                                                                                                                              | 8             | SELIQP              |                                                                                                    |

| 11D14NComplementary LVDS Data Bit 14. Internal 110Ω termination to D14P.12D14PLVDS Data Bit 14. Internal 110Ω termination to D14N.13D13NComplementary LVDS Data Bit 13. Internal 110Ω termination to D13P.14D13PLVDS Data Bit 13. Internal 110Ω termination to D13N.15D12NComplementary LVDS Data Bit 12. Internal 110Ω termination to D12P.16D12PLVDS Data Bit 12. Internal 110Ω termination to D12N.17D11NComplementary LVDS Data Bit 11. Internal 110Ω termination to D11P.18D11PLVDS Data Bit 11. Internal 110Ω termination to D10P.20D10PLVDS Data Bit 10. Internal 110Ω termination to D10P.21D9NComplementary LVDS Data Bit 9. Internal 110Ω termination to D9P.22D9NComplementary LVDS Data Bit 9. Internal 110Ω termination to D8P.23D9PLVDS Data Bit 9. Internal 110Ω termination to D8P.24D8NComplementary LVDS Data Bit 8. Internal 110Ω termination to D8P.25D8PLVDS Data Bit 7. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D7P.28D6NComplementary LVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D5P.31D5NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5P.32D5PLVDS Data Bit 5. Internal 110Ω termination to D5P.33D4NComplementary LVDS Data Bit 4. Internal 110Ω termination to D4P.                                                                                                                                                                                                                                                                | 9             | D15N                | Complementary LVDS Data Bit 15 (MSB). Internal $110\Omega$ termination to D15P.                    |

| 12D14PLVDS Data Bit 14. Internal 110Ω termination to D14N.13D13NComplementary LVDS Data Bit 13. Internal 110Ω termination to D13P.14D13PLVDS Data Bit 13. Internal 110Ω termination to D13N.15D12NComplementary LVDS Data Bit 12. Internal 110Ω termination to D12P.16D12PLVDS Data Bit 12. Internal 110Ω termination to D12N.17D11NComplementary LVDS Data Bit 11. Internal 110Ω termination to D11P.18D11PLVDS Data Bit 11. Internal 110Ω termination to D11N.19D10NComplementary LVDS Data Bit 10. Internal 110Ω termination to D10P.20D10PLVDS Data Bit 10. Internal 110Ω termination to D10N.22D9NComplementary LVDS Data Bit 9. Internal 110Ω termination to D9P.23D9PLVDS Data Bit 9. Internal 110Ω termination to D8P.24D8NComplementary LVDS Data Bit 8. Internal 110Ω termination to D8P.25D8PLVDS Data Bit 8. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D7P.28D6NComplementary LVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D5P.31D5NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5P.33D4NComplementary LVDS Data Bit 4. Internal 110Ω termination to D4P.                                                                                                                                                                                                                                                                                                                                     | 10            | D15P                | LVDS Data Bit 15 (MSB). Internal 110 $\Omega$ termination to D15N.                                 |

| 13D13NComplementary LVDS Data Bit 13. Internal 110Ω termination to D13P.14D13PLVDS Data Bit 13. Internal 110Ω termination to D13N.15D12NComplementary LVDS Data Bit 12. Internal 110Ω termination to D12P.16D12PLVDS Data Bit 12. Internal 110Ω termination to D12N.17D11NComplementary LVDS Data Bit 11. Internal 110Ω termination to D11P.18D11PLVDS Data Bit 11. Internal 110Ω termination to D11N.19D10NComplementary LVDS Data Bit 10. Internal 110Ω termination to D10P.20D10PLVDS Data Bit 10. Internal 110Ω termination to D10P.21D9NComplementary LVDS Data Bit 9. Internal 110Ω termination to D9P.23D9PLVDS Data Bit 9. Internal 110Ω termination to D8P.24D8NComplementary LVDS Data Bit 8. Internal 110Ω termination to D8P.25D8PLVDS Data Bit 8. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D7P.28D6NComplementary LVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D5P.31D5NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5P.32D5PLVDS Data Bit 5. Internal 110Ω termination to D4P.33D4NComplementary LVDS Data Bit 4. Internal 110Ω termination to D4P.                                                                                                                                                                                                                                                                                                                                        | 11            | D14N                | Complementary LVDS Data Bit 14. Internal $110\Omega$ termination to D14P.                          |

| 14D13PLVDS Data Bit 13. Internal 110Ω termination to D13N.15D12NComplementary LVDS Data Bit 12. Internal 110Ω termination to D12P.16D12PLVDS Data Bit 12. Internal 110Ω termination to D12N.17D11NComplementary LVDS Data Bit 11. Internal 110Ω termination to D11P.18D11PLVDS Data Bit 11. Internal 110Ω termination to D10P.19D10NComplementary LVDS Data Bit 10. Internal 110Ω termination to D10P.20D10PLVDS Data Bit 10. Internal 110Ω termination to D10N.22D9NComplementary LVDS Data Bit 9. Internal 110Ω termination to D9P.23D9PLVDS Data Bit 9. Internal 110Ω termination to D8N.24D8NComplementary LVDS Data Bit 8. Internal 110Ω termination to D7P.25D8PLVDS Data Bit 7. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D7P.28D6NComplementary LVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D6P.31D5NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5P.32D5PLVDS Data Bit 6. Internal 110Ω termination to D5P.33D4NComplementary LVDS Data Bit 5. Internal 110Ω termination to D4P.                                                                                                                                                                                                                                                                                                                                                                                                                | 12            | D14P                | LVDS Data Bit 14. Internal $110\Omega$ termination to D14N.                                        |

| 15D12NComplementary LVDS Data Bit 12. Internal 110Ω termination to D12P.16D12PLVDS Data Bit 12. Internal 110Ω termination to D12N.17D11NComplementary LVDS Data Bit 11. Internal 110Ω termination to D11P.18D11PLVDS Data Bit 11. Internal 110Ω termination to D11N.19D10NComplementary LVDS Data Bit 10. Internal 110Ω termination to D10P.20D10PLVDS Data Bit 10. Internal 110Ω termination to D10N.22D9NComplementary LVDS Data Bit 9. Internal 110Ω termination to D9P.23D9PLVDS Data Bit 9. Internal 110Ω termination to D8N.24D8NComplementary LVDS Data Bit 7. Internal 110Ω termination to D7P.25D8PLVDS Data Bit 8. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D6P.31D5NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5P.32D5PLVDS Data Bit 5. Internal 110Ω termination to D5N.33D4NComplementary LVDS Data Bit 4. Internal 110Ω termination to D4P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13            | D13N                | Complementary LVDS Data Bit 13. Internal $110\Omega$ termination to D13P.                          |

| 16D12PLVDS Data Bit 12. Internal 110Ω termination to D12N.17D11NComplementary LVDS Data Bit 11. Internal 110Ω termination to D11P.18D11PLVDS Data Bit 11. Internal 110Ω termination to D11N.19D10NComplementary LVDS Data Bit 10. Internal 110Ω termination to D10P.20D10PLVDS Data Bit 10. Internal 110Ω termination to D10N.22D9NComplementary LVDS Data Bit 9. Internal 110Ω termination to D9P.23D9PLVDS Data Bit 9. Internal 110Ω termination to D9N.24D8NComplementary LVDS Data Bit 8. Internal 110Ω termination to D8P.25D8PLVDS Data Bit 8. Internal 110Ω termination to D8N.26D7NComplementary LVDS Data Bit 7. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D6P.28D6NComplementary LVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 7. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D5P.31D5NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5P.32D5PLVDS Data Bit 5. Internal 110Ω termination to D5N.33D4NComplementary LVDS Data Bit 4. Internal 110Ω termination to D4P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14            | D13P                | LVDS Data Bit 13. Internal 110 $\Omega$ termination to D13N.                                       |

| 17D11NComplementary LVDS Data Bit 11. Internal 110Ω termination to D11P.18D11PLVDS Data Bit 11. Internal 110Ω termination to D11N.19D10NComplementary LVDS Data Bit 10. Internal 110Ω termination to D10P.20D10PLVDS Data Bit 10. Internal 110Ω termination to D10N.22D9NComplementary LVDS Data Bit 9. Internal 110Ω termination to D9P.23D9PLVDS Data Bit 9. Internal 110Ω termination to D9N.24D8NComplementary LVDS Data Bit 8. Internal 110Ω termination to D8P.25D8PLVDS Data Bit 8. Internal 110Ω termination to D8N.26D7NComplementary LVDS Data Bit 7. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D6P.28D6NComplementary LVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D6P.31D5NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5P.32D5PLVDS Data Bit 5. Internal 110Ω termination to D5N.33D4NComplementary LVDS Data Bit 4. Internal 110Ω termination to D4P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15            | D12N                | Complementary LVDS Data Bit 12. Internal $110\Omega$ termination to D12P.                          |

| 18D11PLVDS Data Bit 11. Internal 110Ω termination to D11N.19D10NComplementary LVDS Data Bit 10. Internal 110Ω termination to D10P.20D10PLVDS Data Bit 10. Internal 110Ω termination to D10N.22D9NComplementary LVDS Data Bit 9. Internal 110Ω termination to D9P.23D9PLVDS Data Bit 9. Internal 110Ω termination to D9N.24D8NComplementary LVDS Data Bit 8. Internal 110Ω termination to D8P.25D8PLVDS Data Bit 8. Internal 110Ω termination to D8N.26D7NComplementary LVDS Data Bit 7. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D7P.28D6NComplementary LVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D6N.31D5NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5P.32D5PLVDS Data Bit 6. Internal 110Ω termination to D5P.33D4NComplementary LVDS Data Bit 5. Internal 110Ω termination to D4P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16            | D12P                | LVDS Data Bit 12. Internal $110\Omega$ termination to D12N.                                        |

| 19D10NComplementary LVDS Data Bit 10. Internal 110Ω termination to D10P.20D10PLVDS Data Bit 10. Internal 110Ω termination to D10N.22D9NComplementary LVDS Data Bit 9. Internal 110Ω termination to D9P.23D9PLVDS Data Bit 9. Internal 110Ω termination to D9N.24D8NComplementary LVDS Data Bit 8. Internal 110Ω termination to D8P.25D8PLVDS Data Bit 8. Internal 110Ω termination to D8N.26D7NComplementary LVDS Data Bit 7. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D7N.28D6NComplementary LVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D6N.31D5NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5P.32D5PLVDS Data Bit 5. Internal 110Ω termination to D5N.33D4NComplementary LVDS Data Bit 4. Internal 110Ω termination to D4P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17            | D11N                | Complementary LVDS Data Bit 11. Internal $110\Omega$ termination to D11P.                          |

| 20D10PLVDS Data Bit 10. Internal 110Ω termination to D10N.22D9NComplementary LVDS Data Bit 9. Internal 110Ω termination to D9P.23D9PLVDS Data Bit 9. Internal 110Ω termination to D9N.24D8NComplementary LVDS Data Bit 8. Internal 110Ω termination to D8P.25D8PLVDS Data Bit 8. Internal 110Ω termination to D8N.26D7NComplementary LVDS Data Bit 7. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D7N.28D6NComplementary LVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D6N.31D5NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5N.33D4NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5N.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18            | D11P                | LVDS Data Bit 11. Internal 110 $\Omega$ termination to D11N.                                       |

| 22D9NComplementary LVDS Data Bit 9. Internal 110Ω termination to D9P.23D9PLVDS Data Bit 9. Internal 110Ω termination to D9N.24D8NComplementary LVDS Data Bit 8. Internal 110Ω termination to D8P.25D8PLVDS Data Bit 8. Internal 110Ω termination to D8N.26D7NComplementary LVDS Data Bit 7. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D7N.28D6NComplementary LVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D6N.31D5NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5P.32D5PLVDS Data Bit 5. Internal 110Ω termination to D5N.33D4NComplementary LVDS Data Bit 4. Internal 110Ω termination to D4P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19            | D10N                | Complementary LVDS Data Bit 10. Internal $110\Omega$ termination to D10P.                          |

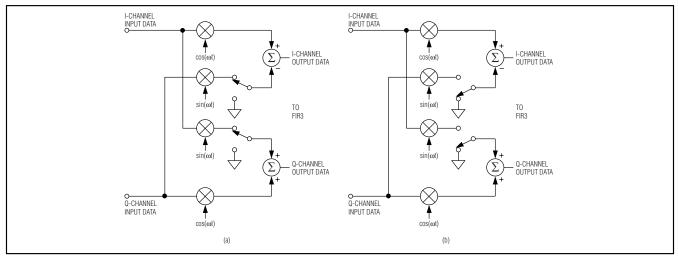

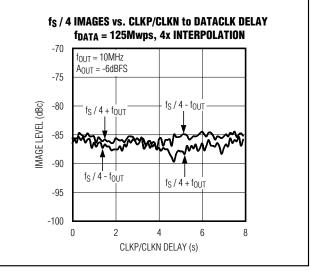

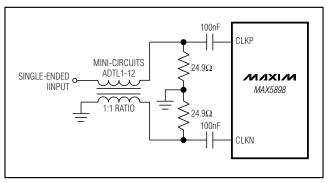

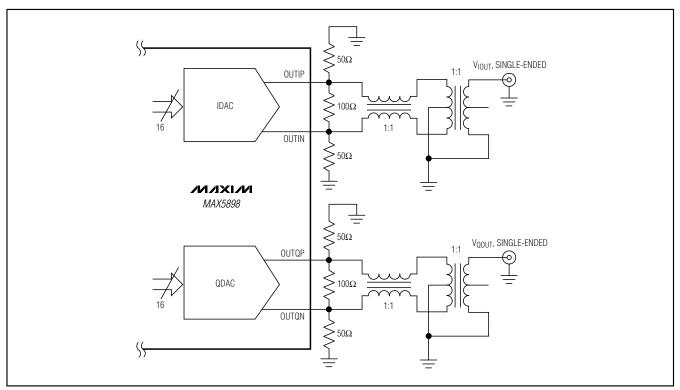

| 23D9PLVDS Data Bit 9. Internal 110Ω termination to D9N.24D8NComplementary LVDS Data Bit 8. Internal 110Ω termination to D8P.25D8PLVDS Data Bit 8. Internal 110Ω termination to D8N.26D7NComplementary LVDS Data Bit 7. Internal 110Ω termination to D7P.27D7PLVDS Data Bit 7. Internal 110Ω termination to D7N.28D6NComplementary LVDS Data Bit 6. Internal 110Ω termination to D6P.29D6PLVDS Data Bit 6. Internal 110Ω termination to D6N.31D5NComplementary LVDS Data Bit 5. Internal 110Ω termination to D5P.32D5PLVDS Data Bit 5. Internal 110Ω termination to D5N.33D4NComplementary LVDS Data Bit 4. Internal 110Ω termination to D4P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20            | D10P                | LVDS Data Bit 10. Internal $110\Omega$ termination to D10N.                                        |