# 128MB 32-bit Direct Rambus DRAM RIMM<sup>™</sup> Module

# MC-4R128FKK8K (32M words × 18 bits × 2 channels)

#### Description

The 32-bit Direct Rambus RIMM module is a generalpurpose high-performance lines of memory modules suitable for use in a broad range of applications including computer memory, personal computers, workstations, and other applications where high bandwidth and latency are required.

The 32-bit RIMM module consists of 288Mb Direct Rambus DRAM (Direct RDRAM) devices. These are extremely high-speed CMOS DRAMs organized as 16M words by 18 bits. The use of Rambus Signaling Level (RSL) technology permits the use of conventional system and board design technologies. The 32-bit RIMM modules support 800MHz transfer rate per pin, resulting in total module bandwidth of 3.2GB/s.

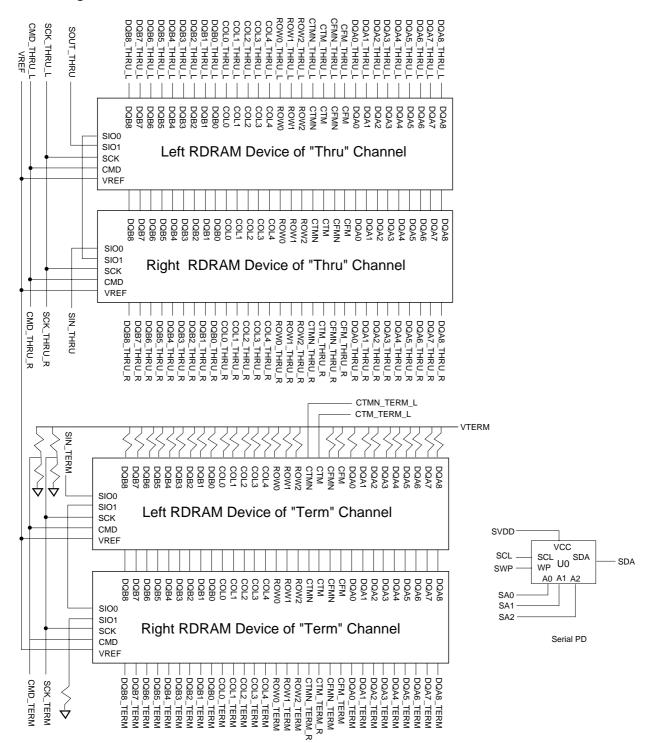

The 32-bit RIMM module provides two independent 18 bit memory channels to facilitate compact system design. The "Thru" Channel enters and exits the module to support a connection to or from a controller, memory slot, or termination. The "Term" Channel is terminated on the module and supports a connection from a controller or another memory slot.

The RDRAM<sup>®</sup> architecture enables the highest sustained bandwidth for multiple, simultaneous, randomly addressed memory transactions. The separate control and data buses with independent row and column control yield over 95% bus efficiency. The RDRAM device multi-bank architecture supports up to four simultaneous transactions per device.

#### Features

- 128MB Direct RDRAM storage and 128 banks total on module

- 2 independent Direct RDRAM channels, 1 pass through and 1 terminated on 32-bit RIMM module

- High speed 800MHz Direct RDRAM devices

- 232 edge connector pads with 1mm pad spacing

- --- Module PCB size: 133.35mm  $\times$  39.925mm  $\times$  1.27mm

- Gold plated edge connector pads contacts

- Serial Presence Detect (SPD) support

- Operates from a 2.5V (±5%) supply

- Low power and power down self refresh modes

- Separate Row and Column buses for higher efficiency

# MC-4R128FKK8K

## **Ordering Information**

| Part number       | Organization | I/O Freq.<br>(MHz) | RAS access<br>time (ns) | Package                                                                           | Mounted devices                                                         |

|-------------------|--------------|--------------------|-------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| MC-4R128FKK8K-840 | 32M x 18 x 2 | 800                | 40                      | 232 edge connector pads<br>RIMM with heat spreader<br>Edge connector: Gold plated | 4 pieces of $\mu$ PD488588FF<br>FBGA ( $\mu$ BGA <sup>®</sup> ) package |

### **Module Pad Names**

| Pad | Signal name |

|-----|-------------|-----|-------------|-----|-------------|-----|-------------|

| A1  | GND         | B1  | GND         | A59 | GND         | B59 | GND         |

| A2  | SCK_THRU_L  | B2  | CMD_THRU_L  | A60 | VTERM       | B60 | VTERM       |

| A3  | GND         | B3  | GND         | A61 | VTERM       | B61 | VTERM       |

| A4  | DQA8_THRU_L | B4  | DQA7_THRU_L | A62 | GND         | B62 | GND         |

| A5  | GND         | B5  | GND         | A63 | DQA3_THRU_R | B63 | DQA4_THRU_R |

| A6  | DQA6_THRU_L | B6  | DQA5_THRU_L | A64 | GND         | B64 | GND         |

| A7  | GND         | B7  | GND         | A65 | DQA5_THRU_R | B65 | DQA6_THRU_R |

| A8  | DQA4_THRU_L | B8  | DQA3_THRU_L | A66 | GND         | B66 | GND         |

| A9  | GND         | B9  | GND         | A67 | DQA7_THRU_R | B67 | DQA8_THRU_R |

| A10 | DQA2_THRU_L | B10 | DQA1_THRU_L | A68 | GND         | B68 | GND         |

| A11 | GND         | B11 | GND         | A69 | VDD         | B69 | VDD         |

| A12 | DQA0_THRU_L | B12 | CTMN_THRU_L | A70 | GND         | B70 | GND         |

| A13 | GND         | B13 | GND         | A71 | SCK_THRU_R  | B71 | CTMN_TERM_L |

| A14 | CFM_THRU_L  | B14 | CTM_THRU_L  | A72 | GND         | B72 | GND         |

| A15 | GND         | B15 | GND         | A73 | CMD_THRU_R  | B73 | CTM_TERM_L  |

| A16 | CFMN_THRU_L | B16 | ROW2_THRU_L | A74 | GND         | B74 | GND         |

| A17 | GND         | B17 | GND         | A75 | VREF        | B75 | VCMOS       |

| A18 | ROW1_THRU_L | B18 | ROW0_THRU_L | A76 | VDD         | B76 | VDD         |

| A19 | GND         | B19 | GND         | A77 | SVDD        | B77 | SWP         |

| A20 | COL4_THRU_L | B20 | COL3_THRU_L | A78 | VDD         | B78 | VDD         |

| A21 | GND         | B21 | GND         | A79 | SCL         | B79 | SDA         |

| A22 | COL2_THRU_L | B22 | COL1_THRU_L | A80 | VDD         | B80 | VDD         |

| A23 | GND         | B23 | GND         | A81 | SA0         | B81 | SA1         |

| A24 | COL0_THRU_L | B24 | DQB0_THRU_L | A82 | VDD         | B82 | VDD         |

| A25 | GND         | B25 | GND         | A83 | SA2         | B83 | SIN_TERM    |

| A26 | DQB1_THRU_L | B26 | DQB2_THRU_L | A84 | GND         | B84 | GND         |

| A27 | GND         | B27 | GND         | A85 | DQB8_TERM   | B85 | DQB7_TERM   |

| A28 | DQB3_THRU_L | B28 | DQB4_THRU_L | A86 | GND         | B86 | GND         |

| A29 | GND         | B29 | GND         | A87 | DQB6_TERM   | B87 | DQB5_TERM   |

| A30 | DQB5_THRU_L | B30 | DQB6_THRU_L | A88 | GND         | B88 | GND         |

| A31 | GND         | B31 | GND         | A89 | DQB4_TERM   | B89 | DQB3_TERM   |

| A32 | DQB7_THRU_L | B32 | DQB8_THRU_L | A90 | GND         | B90 | GND         |

| A33 | GND         | B33 | GND         | A91 | DQB2_TERM   | B91 | DQB1_TERM   |

| A34 | SOUT_THRU   | B34 | SIN_THRU    | A92 | GND         | B92 | GND         |

| A35 | GND         | B35 | GND         | A93 | DQB0_TERM   | B93 | COL0_TERM   |

| A36 | DQB8_THRU_R | B36 | DQB7_THRU_R | A94 | GND         | B94 | GND         |

Preliminary Data Sheet E0252N10 (Ver. 1.0)

# **ΕLΡΙD**Λ

| Pad | Signal name | Pad | Signal name |

|-----|-------------|-----|-------------|

| A37 | GND         | B37 | GND         |

| A38 | DQB6_THRU_R | B38 | DQB5_THRU_R |

| A39 | GND         | B39 | GND         |

| A40 | DQB4_THRU_R | B40 | DQB3_THRU_R |

| A41 | GND         | B41 | GND         |

| A42 | DQB2_THRU_R | B42 | DQB1_THRU_R |

| A43 | GND         | B43 | GND         |

| A44 | DQB0_THRU_R | B44 | COL0_THRU_R |

| A45 | GND         | B45 | GND         |

| A46 | COL1_THRU_R | B46 | COL2_THRU_R |

| A47 | GND         | B47 | GND         |

| A48 | COL3_THRU_R | B48 | COL4_THRU_R |

| A49 | GND         | B49 | GND         |

| A50 | ROW0_THRU_R | B50 | ROW1_THRU_R |

| A51 | GND         | B51 | GND         |

| A52 | ROW2_THRU_R | B52 | CFMN_THRU_R |

| A53 | GND         | B53 | GND         |

| A54 | CTM_THRU_R  | B54 | CFM_THRU_R  |

| A55 | GND         | B55 | GND         |

| A56 | CTMN_THRU_R | B56 | DQA0_THRU_R |

| A57 | GND         | B57 | GND         |

| A58 | DQA1_THRU_R | B58 | DQA2_THRU_R |

| Pad  | Signal name | Pad  | Signal name |

|------|-------------|------|-------------|

| A95  | COL1 TERM   | B95  | COL2 TERM   |

|      | _           |      |             |

| A96  | GND         | B96  | GND         |

| A97  | COL3_TERM   | B97  | COL4_TERM   |

| A98  | GND         | B98  | GND         |

| A99  | ROW0_TERM   | B99  | ROW1_TERM   |

| A100 | GND         | B100 | GND         |

| A101 | ROW2_TERM   | B101 | CFMN_TERM   |

| A102 | GND         | B102 | GND         |

| A103 | CTM_TERM_R  | B103 | CFM_TERM    |

| A104 | GND         | B104 | GND         |

| A105 | CTMN_TERM_R | B105 | DQA0_TERM   |

| A106 | GND         | B106 | GND         |

| A107 | DQA1_TERM   | B107 | DQA2_TERM   |

| A108 | GND         | B108 | GND         |

| A109 | DQA3_TERM   | B109 | DQA4_TERM   |

| A110 | GND         | B110 | GND         |

| A111 | DQA5_TERM   | B111 | DQA6_TERM   |

| A112 | GND         | B112 | GND         |

| A113 | DQA7_TERM   | B113 | DQA8_TERM   |

| A114 | GND         | B114 | GND         |

| A115 | CMD_TERM    | B115 | SCK_TERM    |

| A116 | GND         | B116 | GND         |

# Module Connector Pad Description

| Signal                     | Module<br>connector pads                          | I/O | Туре  | Description                                                                                                                                                                                                                                                             |

|----------------------------|---------------------------------------------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CFM_THRU_L                 | A14                                               | 1   | RSL   | Clock From Master. Connects to left RDRAM device on<br>"Thru" Channel. Interface clock used for receiving RSL<br>signals from the controller. Positive polarity.                                                                                                        |

| CFM_THRU_R                 | B54                                               | I   | RSL   | Clock From Master. Connects to right RDRAM device on<br>"Thru" Channel. Interface clock used for receiving RSL<br>signals from the controller. Positive polarity.                                                                                                       |

| CFMN_THRU_L                | A16                                               | I   | RSL   | Clock From Master. Connects to left RDRAM device on<br>"Thru" Channel. Interface clock used for receiving RSL<br>signals from the controller. Negative polarity.                                                                                                        |

| CFMN_THRU_R                | B52                                               | I   | RSL   | Clock From Master. Connects to right RDRAM device on<br>"Thru" Channel. Interface clock used for receiving RSL<br>signals from the controller. Negative polarity.                                                                                                       |

| CMD_THRU_L                 | B2                                                | I   | VCMOS | Serial Command Input used to read from and write to the control registers. Also used for power management. Connects to left RDRAM device on "Thru" Channel.                                                                                                             |

| CMD_THRU_R                 | A73                                               | I   | VCMOS | Serial Command Input used to read from and write to the<br>control registers. Also used for power management.<br>Connects to right RDRAM device on "Thru" Channel.                                                                                                      |

| COL4_THRU_L<br>COL0_THRU_L | A20, B20, A22, B22,<br>A24                        | I   | RSL   | "Thru" Channel Column bus. 5-bit bus containing control and address information for column accesses. Connects to left RDRAM device on "Thru" Channel.                                                                                                                   |

| COL4_THRU_R<br>COL0_THRU_R | B48, A48, B46, A46,<br>B44                        | I   | RSL   | "Thru" Channel Column bus. 5-bit bus containing control and address information for column accesses. Connects to right RDRAM device on "Thru" Channel.                                                                                                                  |

| CTM_THRU_L                 | B14                                               | I   | RSL   | Clock To Master. Connects to left RDRAM device on "Thru"<br>Channel. Interface clock used for transmitting RSL signals to<br>the controller. Positive polarity.                                                                                                         |

| CTM_THRU_R                 | A54                                               | I   | RSL   | Clock To Master. Connects to right RDRAM device on "Thru"<br>Channel. Interface clock used for transmitting RSL signals to<br>the controller. Positive polarity.                                                                                                        |

| CTMN_THRU_L                | B12                                               | I   | RSL   | Clock To Master. Connects to left RDRAM device on "Thru"<br>Channel. Interface clock used for transmitting RSL signals to<br>the controller. Negative polarity.                                                                                                         |

| CTMN_THRU_R                | A56                                               | I   | RSL   | Clock To Master. Connects to right RDRAM device on "Thru"<br>Channel. Interface clock used for transmitting RSL signals to<br>the controller. Negative polarity.                                                                                                        |

| DQA8_THRU_L<br>DQA0_THRU_L | A4, B4, A6, B6, A8,<br>B8, A10, B10, A12          | I/O | RSL   | "Thru" Channel Data bus A. A 9-bit bus carrying a byte of<br>read or write data between the controller and RDRAM devices<br>on "Thru" Channel. Connects to left RDRAM device on "Thru"<br>Channel. DQA8_THRU_L is non-functional on modules with<br>x16 RDRAM devices.  |

| DQA8_THRU_R<br>DQA0_THRU_R | B67, A67, B65, A65,<br>B63, A63, B58, A58,<br>B56 | I/O | RSL   | "Thru" Channel Data bus A. A 9-bit bus carrying a byte of<br>read or write data between the controller and RDRAM devices<br>on "Thru" Channel. Connects to right RDRAM device on<br>"Thru" Channel. DQA8_THRU_R is non-functional on<br>modules with x16 RDRAM devices. |

| DQB8_THRU_L<br>DQB0_THRU_L | B32, A32, B30, A30,<br>B28, A28, B26, A26,<br>B24 | I/O | RSL   | "Thru" Channel Data bus B. A 9-bit bus carrying a byte of<br>read or write data between the controller and RDRAM devices<br>on "Thru" Channel. Connects to left RDRAM device on "Thru"<br>Channel. DQB8_THRU_L is non-functional on modules with<br>x16 RDRAM devices.  |

| DQB8_THRU_R<br>DQB0_THRU_R | A36, B36, A38, B38,<br>A40, B40, A42, B42,<br>A44 | I/O | RSL   | "Thru" Channel Data bus B. A 9-bit bus carrying a byte of<br>read or write data between the controller and RDRAM devices<br>on "Thru" Channel. Connects to right RDRAM device on<br>"Thru" Channel. DQB8_THRU_R is non-functional on<br>modules with x16 RDRAM devices. |

| ROW2_THRU_L<br>ROW0_THRU_L | B16, A18, B18                                     | I   | RSL   | Row bus. 3-bit bus containing control and address information<br>for row accesses. Connects to left RDRAM device on "Thru"<br>Channel.                                                                                                                                  |

|                            | Module                                                     | 1/0 | T     | Description                                                                                                                                                                                                                                                           |

|----------------------------|------------------------------------------------------------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal                     | connector pads                                             | I/O | Туре  | Description                                                                                                                                                                                                                                                           |

| ROW2_THRU_R<br>ROW0_THRU_R | A52, B50, A50                                              | I   | RSL   | Row bus. 3-bit bus containing control and address information<br>for row accesses. Connects to right RDRAM device on "Thru"<br>Channel.                                                                                                                               |

| SCK_THRU_L                 | A2                                                         | I   | VCMOS | Serial Clock input. Clock source used to read from and write<br>to "Thru" Channel RDRAM control registers. Connects to left<br>RDRAM device on "Thru" Channel.                                                                                                        |

| SCK_THRU_R                 | A71                                                        | I   | VCMOS | Serial Clock input. Clock source used to read from and write<br>to "Thru" Channel RDRAM control registers. Connects to right<br>RDRAM device on "Thru" Channel.                                                                                                       |

| SIN_THRU                   | B34                                                        | I/O | VCMOS | "Thru" Channel Serial I/O for reading from and writing to the control registers. Attaches to SIO0 of right RDRAM device on "Thru" Channel.                                                                                                                            |

| SOUT_THRU                  | A34                                                        | I/O | VCMOS | "Thru" Channel Serial I/O for reading from and writing to the control registers. Attaches to SIO1 of left RDRAM device on "Thru" Channel.                                                                                                                             |

| CFM_TERM                   | B103                                                       | I   | RSL   | Clock from master. Connects to right RDRAM device on<br>"Term" Channel. Interface clock used for receiving RSL<br>signals from the controller. Positive polarity.                                                                                                     |

| CFMN_TERM                  | B101                                                       | I   | RSL   | Clock from master. Connects to right RDRAM device on<br>"Term" Channel. Interface clock used for receiving RSL<br>signals from the controller. Negative polarity.                                                                                                     |

| CMD_TERM                   | A115                                                       | I   | VCMOS | Serial Command Input used to read from and write to the control registers. Also used for power management. Connects to right RDRAM device on "Term" Channel.                                                                                                          |

| COL4_TERM<br>COL0_TERM     | B97, A97, B95, A95,<br>B93                                 | I   | RSL   | "Term" Channel Column bus. 5-bit bus containing control and<br>address information for column accesses. Connects to right<br>RDRAM device on "Term" Channel.                                                                                                          |

| CTM_TERM_L                 | B73                                                        | I   | RSL   | Clock To Master. Connects to left RDRAM device on "Term"<br>Channel. Interface clock used for transmitting RSL signals to<br>the controller. Positive polarity.                                                                                                       |

| CTM_TERM_R                 | A103                                                       | I   | RSL   | Clock To Master. Connects to right RDRAM device on "Term"<br>Channel. Interface clock used for transmitting RSL signals to<br>the controller. Positive polarity.                                                                                                      |

| CTMN_TERM_L                | B71                                                        | I   | RSL   | Clock To Master. Connects to left RDRAM device on "Term"<br>Channel. Interface clock used for transmitting RSL signals to<br>the controller. Negative polarity.                                                                                                       |

| CTMN_TERM_R                | A105                                                       | I   | RSL   | Clock To Master. Connects to right RDRAM device on "Term"<br>Channel. Interface clock used for transmitting RSL signals to<br>the controller. Negative polarity.                                                                                                      |

| DQA8_TERM<br>DQA0_TERM     | B113, A113, B111,<br>A111, B109, A109,<br>B107, A107, B105 | I/O | RSL   | "Term" Channel Data bus A. A 9-bit bus carrying a byte of<br>read or write data between the controller and RDRAM devices<br>on "Term" Channel. Connects to right RDRAM device on<br>"Term" Channel. DQA8_TERM is non-functional on modules<br>with x16 RDRAM devices. |

| DQB8_TERM<br>DQB0_TERM     | A85, B85, A87, B87,<br>A89, B89, A91, B91,<br>A93          | I/O | RSL   | "Term" Channel Data bus B. A 9-bit bus carrying a byte of<br>read or write data between the controller and RDRAM devices<br>on "Term" Channel. Connects to right RDRAM device on<br>"Term" Channel. DQB8_TERM is non-functional on modules<br>with x16 RDRAM devices. |

| ROW2_TERM<br>ROW0_TERM     | A101, B99, A99                                             | I   | RSL   | "Term" Channel Row bus. 3-bit bus containing control and address information for row accesses. Connects to right RDRAM device on "Term" Channel.                                                                                                                      |

| SCK_TERM                   | B115                                                       | 1   | VCMOS | Serial Clock input. Clock source used to read from and write<br>to "Term" Channel RDRAM control registers. Connects to<br>right RDRAM device on "Term" Channel.                                                                                                       |

| SIN_TERM                   | B83                                                        | I/O | VCMOS | "Term" Channel Serial I/O for reading from and writing to the control registers. Attaches to SIO0 of left RDRAM device on "Term" Channel.                                                                                                                             |

| VTERM                      | A60, B60, A61, B61                                         |     |       | "Term" Channel Termination voltage.                                                                                                                                                                                                                                   |

| Signal | Module<br>connector pads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I/O         | Туре | Description                                                                                           |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------------------------------------------------------------------------------------------------------|

| GND    | <ul> <li>A1, A3, A5, A7, A9, A11, A13, A15,</li> <li>A17, A19, A21, A23, A25, A27, A29,</li> <li>A31, A33, A35, A37, A39, A41, A43,</li> <li>A45, A47, A49, A51, A53, A55, A57,</li> <li>A59, A62, A64, A66, A68, A70, A72,</li> <li>A74, A84, A86, A88, A90, A92, A94,</li> <li>A96, A98, A100, A102, A104, A106,</li> <li>A108, A110, A112, A114, A116, B1,</li> <li>B3, B5, B7, B9, B11, B13, B15, B17</li> <li>B19, B21, B23, B25, B27, B29, B31,</li> <li>B33, B35, B37, B39, B41, B43, B45,</li> <li>B47, B49, B51, B53, B55, B57, B59,</li> <li>B62, B64, B66, B68, B70, B72, B74,</li> <li>B84, B86, B88, B90, B92, B94, B96,</li> <li>B98, B100, B102, B104, B106,</li> <li>B108, B110, B112, B114, B116</li> </ul> | ·<br>·<br>· |      | Ground reference for RDRAM core and interface.                                                        |

| SA0    | A81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I           | SVDD | Serial Presence Detect Address 0                                                                      |

| SA1    | B81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I           | SVDD | Serial Presence Detect Address 1.                                                                     |

| SA2    | A83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I           | SVDD | Serial Presence Detect Address 2.                                                                     |

| SCL    | A79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I           | SVDD | Serial Presence Detect Clock.                                                                         |

| SDA    | B79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I/O         | SVDD | Serial Presence Detect Data (Open Collector I/O).                                                     |

| SVDD   | A77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |      | SPD Voltage. Used for signals SCL, SDA, SWE, SA0, SA1 and SA2.                                        |

| SWP    | B77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I           | SVDD | Serial Presence Detect Write Protect (active high). When low, the SPD can be written as well as read. |

| VCMOS  | B75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |      | CMOS I/O Voltage. Used for signals CMD, SCK, SIN, SOUT.                                               |

| VDD    | A69, B69, A76, B76, A78, B78, A80,<br>B80, A82, B82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I           |      | Supply voltage for the RDRAM core and interface logic.                                                |

| VREF   | A75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |      | Logic threshold reference voltage for both<br>"Thru" Channel and "Term" Channel RSL<br>signals.       |

#### **Block Diagram**

### **Electrical Specifications**

#### Absolute Maximum Ratings

| Symbol  | Parameter                                                            | MIN. | MAX.      | Unit |

|---------|----------------------------------------------------------------------|------|-----------|------|

| VI,ABS  | Voltage applied to any RSL or CMOS signal pad with<br>respect to GND | -0.3 | VDD + 0.3 | V    |

| VDD,ABS | Voltage on VDD with respect to GND                                   | -0.5 | VDD + 1.0 | V    |

| TSTORE  | Storage temperature                                                  | -50  | +100      | °C   |

#### Caution

Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

#### **DC Recommended Electrical Conditions**

| Symbol | Parameter and conditions                         | MIN.        | MAX.        | Unit |

|--------|--------------------------------------------------|-------------|-------------|------|

| VDD    | Supply voltage <sup>Note</sup>                   | 2.50 - 0.13 | 2.50 + 0.13 | V    |

| VCMOS  | CMOS I/O power supply at pad<br>2.5V controllers | VDD         | VDD         | V    |

|        | 1.8V controllers                                 | 1.8 – 0.1   | 1.8 + 0.2   |      |

| VREF   | Reference voltage <sup>Note</sup>                | 1.4 – 0.2   | 1.4 + 0.2   | V    |

| SVDD   | Serial Presence Detector- positive power supply  | 2.2         | 3.6         | V    |

| VTERM  | Termination Voltage                              | 1.89 - 0.09 | 1.89 + 0.09 | V    |

Note: See Direct RDRAM datasheet for more details.

Unit Ω Ω ns

ps

ps

ps %

%

Ω

2.0

0.8

| AC Electrical Specifications |                                                                                                   |      |      |      |  |  |

|------------------------------|---------------------------------------------------------------------------------------------------|------|------|------|--|--|

| Symbol                       | Parameter and Conditions <sup>Note1</sup>                                                         | MIN. | TYP. | MAX. |  |  |

| ZL                           | Module Impedance of RSL signals                                                                   | 25.2 | 28.0 | 30.8 |  |  |

| ZUL-CMOS                     | Module Impedance of SCK and CMD signals                                                           | 23.8 | 28.0 | 32.2 |  |  |

| TPD                          | Average clock delay from finger to finger of all RSL clock nets (CTM, CTMN,CFM, and CFMN) Note2   |      |      | 0.89 |  |  |

| ΔTPD                         | Propagation delay variation of RSL signals with respect to TPD $^{\text{Note1, 3}}$               | -21  |      | +21  |  |  |

| ∆TPD-CMOS                    | Propagation delay variation of SCK signal with respect to an average clock delay <sup>Note1</sup> | -250 |      | +250 |  |  |

| ∆TPD- SCK,CMD                | Propagation delay variation of CMD signal with respect to SCK signal                              | -200 |      | +200 |  |  |

| Va/VIN                       | Attenuation Limit                                                                                 |      |      | 16.0 |  |  |

| VXF/VIN                      | Forward crosstalk coefficient<br>(300ps input rise time 20% - 80%)                                |      |      | 4.0  |  |  |

|                              | Backward crosstalk coefficient                                                                    |      |      | 2.0  |  |  |

Notes 1. Specifications apply per channel.

2. TPD or Average clock delay is defined as the average delay from finger to finger of all RSL clock nets (CTM, CTMN, CFM, and CFMN).

3. If the RIMM module meets the following specification, then it is compliant to the specification. If the RIMM module does not meet these specifications, then the specification can be adjusted by the "Adjusted  $\Delta$ TPD Specification" table.

#### Adjusted **ATPD** Specification

VXB/VIN

RDC

|        |                                                                   |                                     | Absolute |      |      |

|--------|-------------------------------------------------------------------|-------------------------------------|----------|------|------|

| Symbol | Parameter and conditions                                          | Adjusted MIN./MAX.                  | MIN.     | MAX. | Unit |

| ΔTPD   | Propagation delay variation of RSL signals with<br>respect to TPD | +/- [17+(18*N*∆Z0)] <sup>Note</sup> | -30      | 30   | ps   |

Note N = Number of RDRAM devices installed on the RIMM module.

(300ps input rise time 20% - 80%)

DC Resistance Limit

$\Delta$ Z0 = delta Z0% = (MAX. Z0 - MIN. Z0) / (MIN. Z0)

(MAX. Z0 and MIN. Z0 are obtained from the loaded (high impedance) impedance coupons of all RSL layers on the module.)

#### **RIMM Module Current Profile**

| IDD  | RIMM module power conditions Note1                                              | MAX. | Unit |

|------|---------------------------------------------------------------------------------|------|------|

| IDD1 | One RDRAM device per channel in Read <sup>Note2</sup> , balance in NAP mode     | 1418 | mA   |

| IDD2 | One RDRAM device per channel in Read <sup>Note2</sup> , balance in Standby mode | 1590 | mA   |

| IDD3 | One RDRAM device per channel in Read <sup>Note2</sup> , balance in Active mode  | 1680 | mA   |

| IDD4 | One RDRAM device per channel in Write,<br>balance in NAP mode                   | 1538 | mA   |

| IDD5 | One RDRAM device per channel in Write,<br>balance in Standby mode               | 1710 | mA   |

| IDD6 | One RDRAM device per channel in Write,<br>balance in Active mode                | 1800 | mA   |

Notes 1. Actual power will depend on individual RDRAM component specifications, memory controller and usage patterns. Please refer to specific RIMM module vendor data sheets for additional information. Power does not include Refresh Current. Max current computed for x16 256Mb RDRAM components. x18 288Mb RDRAM components use 8 mA more current per RDRAM device in Read and 60mA more current per RDRAM device in Write.

I/O current is a function of the % of 1's, to add I/O power for 50 % 1's for a x16 need to add 257mA or 290mA for x18 ECC module for the following : VDD = 2.5V, VTERM = 1.8V, VREF = 1.4V and VDIL = VREF - 0.5V.

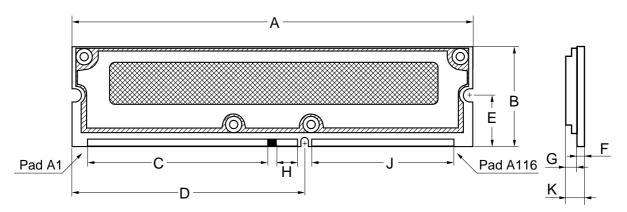

**Physical Outline**

| Item | Description                                                                      | min.   | typ.   | max.   | Unit |

|------|----------------------------------------------------------------------------------|--------|--------|--------|------|

| А    | PCB length                                                                       | 133.22 | 133.35 | 133.48 | mm   |

| В    | PCB height                                                                       | 34.795 | 34.925 | 35.055 | mm   |

| С    | Center-center pad width from pad A1 to A60,<br>B1 to B60                         | -      | 59.00  | -      | mm   |

| D    | Spacing from PCB left edge to connector key notch                                | -      | 78.170 | -      | mm   |

| E    | Spacing from contact pad PCB edge to side edge retainer notch                    | -      | 17.78  | -      | mm   |

| F    | PCB thickness                                                                    | 1.17   | 1.27   | 1.37   | mm   |

| G    | Heat spreader thickness from PCB surface (one side) to heat spreader top surface | -      | -      | 3.09   | mm   |

| Н    | Center-center pad width from pad A61 to A68,<br>B61 to B68                       | -      | 7.00   | -      | mm   |

| J    | Center-center pad width from pad A69 to A116,<br>B69 to B116                     | -      | 47.00  | -      | mm   |

| K    | RIMM thickness                                                                   | -      | -      | 4.46   | mm   |

ECA-TS2-0065-01

# CAUTION FOR HANDLING MEMORY MODULES

When handling or inserting memory modules, be sure not to touch any components on the modules, such as the memory ICs, chip capacitors and chip resistors. It is necessary to avoid undue mechanical stress on these components to prevent damaging them.

In particular, do not push module cover or drop the modules in order to protect from mechanical defects, which would be electrical defects.

When re-packing memory modules, be sure the modules are not touching each other. Modules in contact with other modules may cause excessive mechanical stress, which may damage the modules.

MDE0202

#### - NOTES FOR CMOS DEVICES -

## **①** PRECAUTION AGAINST ESD FOR MOS DEVICES

Exposing the MOS devices to a strong electric field can cause destruction of the gate oxide and ultimately degrade the MOS devices operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it, when once it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. MOS devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. MOS devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor MOS devices on it.

## (2) HANDLING OF UNUSED INPUT PINS FOR CMOS DEVICES

No connection for CMOS devices input pins can be a cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. The unused pins must be handled in accordance with the related specifications.

### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

Power-on does not necessarily define initial status of MOS devices. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the MOS devices with reset function have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. MOS devices are not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for MOS devices having reset function.

CME0107

Rambus, RDRAM and the Rambus logo are registered trademarks of Rambus Inc. RIMM, SO-RIMM, RaSer and QRSL are trademarks of Rambus Inc.  $\mu$ BGA is a registered trademark of Tessera, Inc.

#### The information in this document is subject to change without notice. Before using this document, confirm that this is the latest version.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Elpida Memory, Inc.

Elpida Memory, Inc. does not assume any liability for infringement of any intellectual property rights (including but not limited to patents, copyrights, and circuit layout licenses) of Elpida Memory, Inc. or third parties by or arising from the use of the products or information listed in this document. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of Elpida Memory, Inc. or others.

Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of the customer's equipment shall be done under the full responsibility of the customer. Elpida Memory, Inc. assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

#### [Product applications]

Elpida Memory, Inc. makes every attempt to ensure that its products are of high quality and reliability. However, users are instructed to contact Elpida Memory's sales office before using the product in aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment, medical equipment for life support, or other such application in which especially high quality and reliability is demanded or where its failure or malfunction may directly threaten human life or cause risk of bodily injury.

#### [Product usage]

Design your application so that the product is used within the ranges and conditions guaranteed by Elpida Memory, Inc., including the maximum ratings, operating supply voltage range, heat radiation characteristics, installation conditions and other related characteristics. Elpida Memory, Inc. bears no responsibility for failure or damage when the product is used beyond the guaranteed ranges and conditions. Even within the guaranteed ranges and conditions, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Elpida Memory, Inc. products does not cause bodily injury, fire or other consequential damage due to the operation of the Elpida Memory, Inc. product.

#### [Usage environment]

This product is not designed to be resistant to electromagnetic waves or radiation. This product must be used in a non-condensing environment.

If you export the products or technology described in this document that are controlled by the Foreign Exchange and Foreign Trade Law of Japan, you must follow the necessary procedures in accordance with the relevant laws and regulations of Japan. Also, if you export products/technology controlled by U.S. export control regulations, or another country's export control laws or regulations, you must follow the necessary procedures in accordance with such laws or regulations.

If these products/technology are sold, leased, or transferred to a third party, or a third party is granted license to use these products, that third party must be made aware that they are responsible for compliance with the relevant laws and regulations.

M01E0107