# Freescale Semiconductor, Inc.

Advance Information

Data Sheet

MC72000/D Rev. 2.6, 1/2003

MC72000 Integrated Bluetooth™ Radio

# MC72000

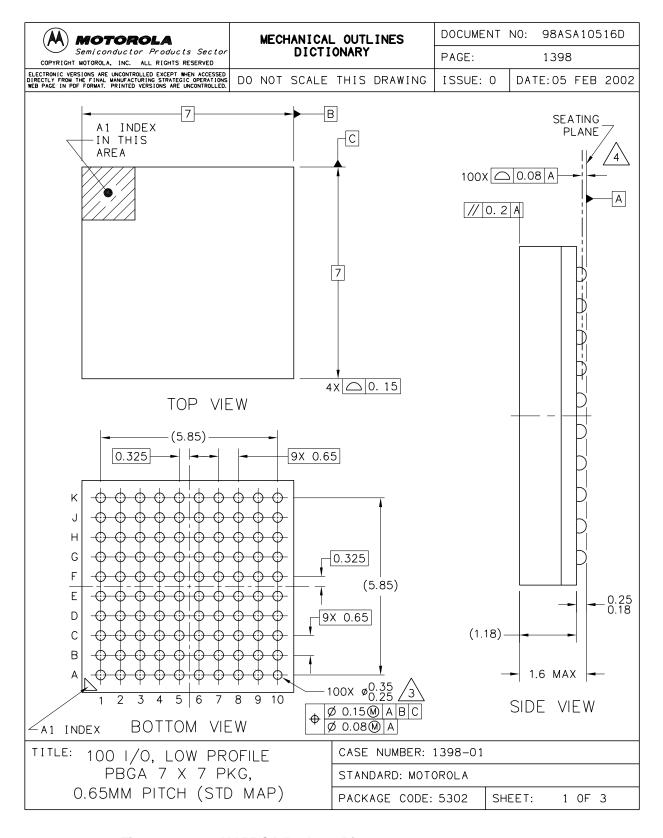

Package Information

Plastic Package

Case 1398-01

(MAPBGA-100)

#### **Ordering Information**

| Device  | Operating<br>Temperature Range | Package      |

|---------|--------------------------------|--------------|

| MC72000 | -40° C to 85° C                | MAPBGA – 100 |

#### **Contents**

| 1  | MC72000 Features 2                  |

|----|-------------------------------------|

| 2  | System Overview 3                   |

| 3  | Electrical                          |

|    | Characteristics4                    |

| 4  | Package Pinout 17                   |

| 5  | System Description 27               |

| 6  | Radio Functional Description31      |

| 7  | Hardware Functional Description49   |

| 8  | Bluetooth Baseband<br>Functionality |

|    | Overview 126                        |

| 9  | HCI Features 134                    |

| 10 | Applications                        |

|    | Information139                      |

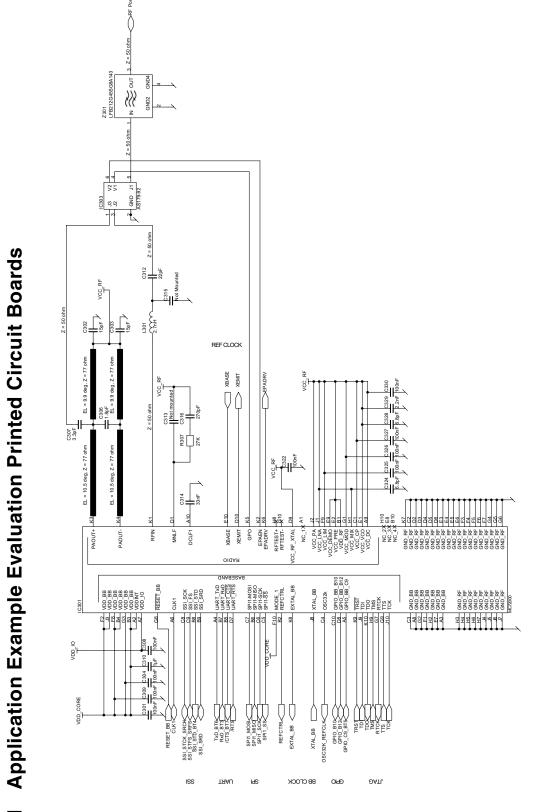

| 11 | Application Example                 |

|    | <b>Evaluation Printed Circuit</b>   |

|    | Boards 150                          |

| 12 | Mechanical Outline<br>(Package      |

|    | Information) 151                    |

| ٨٠ | ppendix A: Radio                    |

| ~1 | Register Map 152                    |

|    | g                                   |

The MC72000 Integrated Bluetooth<sup>™</sup> Radio provides a complete, low-power Bluetooth radio solution. The design is based on Motorola's third-generation Bluetooth architecture that has set a high standard for interoperability, complete functionality, and compliance with the Bluetooth specification.

The MC72000 Integrated Bluetooth Radio from Motorola implements the RF and baseband host controller interface (HCI) of the Bluetooth protocol in a small 7 mm x 7 mm BGA package. The MC72000 is the ideal solution for low-power, short-range Bluetooth applications with small size constraints and includes superior performance features like a dedicated Bluetooth audio processor module and on-chip memory. Debug and production test are fully supported through the joint test action group (JTAG) interface.

The RF portion of the radio provides a unique combination of high sensitivity, excellent C/I performance, and low power consumption. These performance parameters are extremely important to maintaining a robust link in high RF interference environments created by devices such as mobile phones, high density Bluetooth networks, 802.11b networks, and microwave ovens.

The MC72000 uses an innovative, highly advanced packaging technique to combine two die—the RF and baseband functions—into a single, cost-effective package. Motorola's optimized two-chip architecture avoids compromises between cost and performance that other one-chip solutions must make. With Motorola's integrated solution, customers get the best of both. Each die is implemented in its optimal process technology to deliver low cost, low power, and small size.

## 1 MC72000 Features

#### Radio Transceiver

- Low Current Drain

- Power Down Modes for Power Conservation

- Low IF Receiver with On-Chip Filters

- Fully Integrated Demodulator with ADC

- Direct Launch Transmitter

- Multi-Accumulator, Dual-Port, Fractional-N Synthesizer

- RSSI with ADC

- Bluetooth Class 2 Radio (Class 1 supported using external PA)

- Crystal Independent (12 to 15 MHz) Reference Oscillator or 12 to 26 MHz if supplied externally

- Power Supply Range: 2.5 V to 3.1 V

#### **Baseband Controller**

- Bluetooth Specification 1.1 Compliant

- Point-to-multipoint with 7 slaves

- All connection types

- All packet types

- All power saving modes

- Master/Slave switch

- Encryption

- HCI UART transport layer

- Outstanding Audio Performance

- Sample rate synchronization between CODECs and Bluetooth clock domains to avoid clicking effects

- 3 Simultaneous SCO channels supported

- All Bluetooth encoding/decoding schemes supported (CVSD, A-Law, μ-Law)

- Very low audio delay to avoid the need for echo cancellation

- Support for 8, 16, 32, and 64 kHz Sample Rate CODECs

- Bluetooth Link Controller

- Bluetooth Audio Signal Processor

- ARM7 Processor Complex

- · Peripherals

- High-speed UART (up to 2 Mbps)

- High-speed SSI (up to 2 Mbps)

- High-speed SPI (up to 2 Mbps)

- Embedded Memory

- SRAM (64 K)

- ROM (256 K)

- JTAG Test Interface Controller

- 32.768 kHz Oscillator for Low Power Operation

- Operating Voltage: 1.65 V to 1.95 V

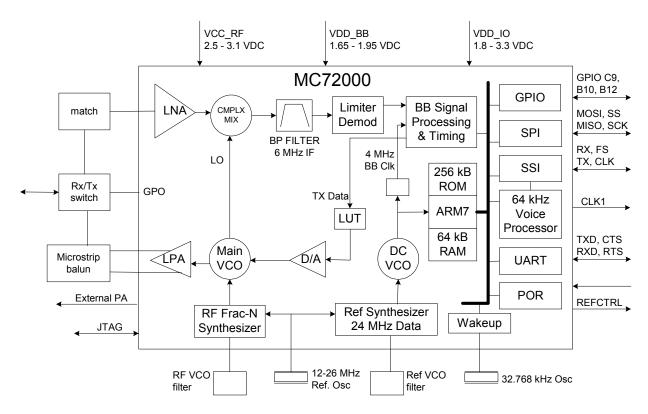

# 2 System Overview

This section provides a brief description of the system for the MC72000.

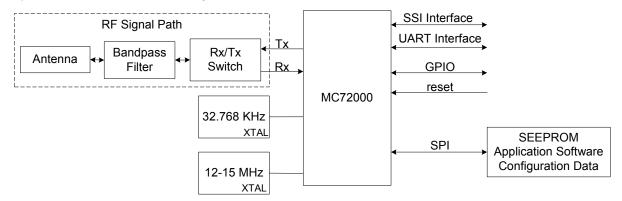

A system overview is shown in Figure 1

Figure 1. MC72000 Example Application Block Diagram

The main block is the MC72000, which will be described in depth in Section 5, "System Description." In addition to the MC72000, there are three other blocks:

- RF signal Path

- Interfaces

- Reference clocks

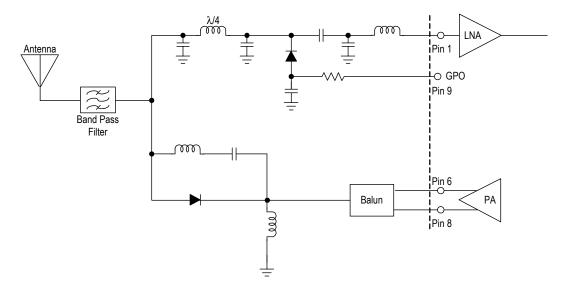

# 2.1 RF Signal Path

The switch for the RX and TX, the bandpass filter, and the antenna are all found in the RF signal path.

#### 2.2 Interfaces

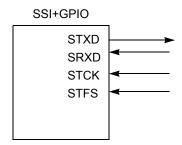

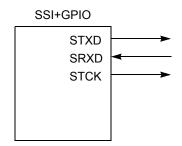

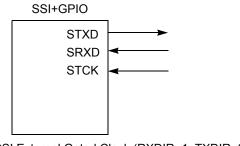

There are four bi-directional interfaces and one reset that only the host can initiate.

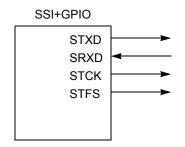

- The SSI interface is used for audio purposes.

- The UART interface is used for all communication to and from the host (for example, HCI commands).

- The SPI is used for communication with the SEEPROM.

- The GPIO pins are used for different configurations set by the MC72000.

# 2.3 Clocks/Crystals

The MC72000 has two clocks:

- The reference clock (12-26 MHz) is used when the MC72000 is active. Note that for a crystal connected to the on-chip oscillator, the frequency range is 12-15 MHz as shown in Figure 1.

- The low power clock (32.768 kHz) is also included and may have high initial tolerance.

## 3 Electrical Characteristics

The absolute maximum ratings given in Table 1 are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond these ratings may affect device reliability or cause permanent damage to the device.

#### WARNING:

This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, normal precautions are advised to avoid application of any voltages higher than maximum rated voltages to the high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either VDD or GND), except for JTAG signals. Refer to Section 10.12, "JTAG Interface," for details on how to handle JTAG signals.

## 3.1 Electrical Characteristics

The following tables provide information on the electrical characteristics of the MC72000.

Table 1. Absolute Maximum Ratings

| Characteristics           | Symbol           | Value              | Unit |

|---------------------------|------------------|--------------------|------|

| Power Supply Voltage, RF  |                  | (GND – 0.3) to 3.2 | VDC  |

| Power Supply Voltage, BB  |                  | (GND – 0.3) to 2.0 | VDC  |

| Power Supply Voltage, IO  |                  | (GND – 0.3) to 3.6 | VDC  |

| Junction Temperature      | T <sub>J</sub>   | 150                | ºC   |

| Storage Temperature Range | T <sub>stg</sub> | -55 to 150         | ōС   |

Table 2. ESD Protection Characteristics

| Characteristics                                                                   | Symbol                                 | Min         | Тур | Max    | Unit |

|-----------------------------------------------------------------------------------|----------------------------------------|-------------|-----|--------|------|

| Human Body Model (HBM) All pins, except RFIN, PAO+, and PAO- RFIN, PAO+, and PAO- | V <sub>HBM</sub><br>V <sub>RFHBM</sub> | 2000<br>100 |     | -<br>- | V    |

| Machine Model (MM) All pins, except RFIN, PAO+, and PAO- RFIN, PAO+, and PAO-     | V <sub>MM</sub><br>V <sub>RFMM</sub>   | 200<br>50   | -   | -      | V    |

# Freescale Semiconductor, Inc. Electrical Characteristics

**Table 3. Recommended Operating Conditions**

| Characteristics                                                         | Symbol            | Min  | Тур              | Max  | Unit |

|-------------------------------------------------------------------------|-------------------|------|------------------|------|------|

| Power Supply Voltage, RF                                                | VCC <sub>RF</sub> | 2.5  | 2.7              | 3.1  | VDC  |

| Power Supply Voltage, BB                                                | VDD <sub>BB</sub> | 1.65 | 1.8              | 1.95 | VDC  |

| Power Supply Voltage, IO                                                | VDD <sub>IO</sub> | 1.8  | -                | 3.3  | VDC  |

| Input Frequency                                                         | f <sub>in</sub>   | 2.4  | -                | 2.5  | GHz  |

| Ambient Temperature Range                                               | T <sub>A</sub>    | -40  | -                | 85   | ōC   |

| Ref Osc Frequency Range (only integral multiples of 20 kHz may be used) | f <sub>ref</sub>  |      |                  |      | MHz  |

| With Crystal                                                            |                   | 12   | 13               | 15   |      |

| External Source                                                         |                   | 12   | -                | 26   |      |

| Low Power Osc Frequency Range<br>With Crystal<br>External Source        | f <sub>lp</sub>   |      | 32.768<br>32.768 |      | kHz  |

## Table 4. Digital DC Electrical Specifications

**Note:** (VCC\_RF = 2.7 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC,  $T_A$ =  $25^{\circ}$  C, Reference Crystal = 13 MHz, Register bit settings according to Figure 94, unless otherwise noted. See Figure 3.)

| Characteristics                                                                                                                                                                            | Symbol          | Min                          | Тур                                    | Max                          | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------|----------------------------------------|------------------------------|------|

| Input Current High (V <sub>IN</sub> = VDD)  BB Digital Pins IO Digital Pins                                                                                                                | I <sub>IH</sub> |                              | -                                      | TBD<br>TBD                   | μΑ   |

| Input Current Low (V <sub>IN</sub> = GND) BB Digital Pins IO Digital Pins                                                                                                                  | I <sub>IL</sub> | TBD<br>TBD                   | 1 1                                    | -                            | μΑ   |

| Output Current High-Impedance State                                                                                                                                                        | I <sub>OZ</sub> | TBD                          | -                                      | TBD                          | μΑ   |

| Output Short-Circuit Current  (V <sub>OUT</sub> = VDD/VCC)  BB Digital Pins  IO Digital Pins  RF Digital Pins  (V <sub>OUT</sub> = GND)  BB Digital Pins  IO Digital Pins  RF Digital Pins | los             | -<br>-<br>-<br>-             | TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD | -<br>-<br>-<br>-             | mA   |

| Input Voltage High<br>BB Digital Pins<br>IO Digital Pins                                                                                                                                   | V <sub>IH</sub> | 0.7 x VDD_BB<br>0.7 x VDD_IO | -                                      | VDD_BB<br>VDD_IO             | V    |

| Input Voltage Low<br>BB Digital Pins<br>IO Digital Pins                                                                                                                                    | V <sub>IL</sub> | -0.3<br>-0.3                 | -<br>-                                 | 0.3 x VDD_BB<br>0.3 x VDD_IO | V    |

## Table 4. Digital DC Electrical Specifications (Continued)

**Note:** (VCC\_RF = 2.7 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC,  $T_A$ = 25° C, Reference Crystal = 13 MHz, Register bit settings according to Figure 94, unless otherwise noted. See Figure 3.)

| Characteristics                                                                                                                                                                                   | Symbol                                                                               | Min                                          | Тур         | Max                                          | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------|-------------|----------------------------------------------|------|

| Output Voltage High BB Digital Pins (I <sub>OH</sub> = -3mA) IO Digital Pins (I <sub>OH</sub> = -3mA) RF Digital Pins (I <sub>OH</sub> = -100μA)                                                  | V <sub>OH</sub>                                                                      | 0.8 x VDD_BB<br>0.8 x VDD_IO<br>0.8 x VCC_RF | -<br>-<br>- | VDD_BB<br>VDD_IO<br>VCC_RF                   | V    |

| Output Voltage Low BB Digital Pins ( $I_{OL} = 3mA$ ) IO Digital Pins ( $I_{OL} = 3mA$ ) RF Digital Pins ( $I_{OL} = 100\mu A$ )                                                                  | V <sub>OL</sub>                                                                      | 0<br>0<br>0                                  | -<br>-<br>- | 0.2 x VDD_BB<br>0.2 x VDD_IO<br>0.2 x VDD_RF | V    |

| Internal Pull-up Device Current IO Digital pins at V <sub>ILMAX</sub> IO Digital pins at V <sub>IHMIN</sub> MODE1, TTS, TMS, TDI at V <sub>ILMAX</sub> MODE1, TTS, TMS, TDI at V <sub>IHMIN</sub> | I <sub>IOPUL</sub><br>I <sub>IOPUH</sub><br>I <sub>BBPUL</sub><br>I <sub>BBPUH</sub> | -<br>-5<br>-<br>-2                           | -<br>-<br>- | -50<br>-<br>-30<br>-                         | μА   |

| Internal Pull-down Device Current RESET_BB, TCK, TRST_B at V <sub>ILMAX</sub> RESET_BB, TCK, TRST_B at V <sub>IHMIN</sub>                                                                         | I <sub>BBPDL</sub><br>I <sub>BBPDH</sub>                                             | - 2                                          | -           | 20<br>-                                      | μΑ   |

| Input Capacitance<br>BB Digital Pins<br>IO Digital Pins                                                                                                                                           | C <sub>BBIN</sub><br>C <sub>IOIN</sub>                                               | -                                            | 5<br>5      | -                                            | pF   |

## Table 5. EPA DAC Electrical Specifications

**Note:** (VCC\_RF = 3.1 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC,  $T_A = 25^{\circ}$  C, Reference Crystal = 13 MHz, Register bit settings according to Figure 94 except R11/7 = 1, unless otherwise noted. See Figure 3.)

| Characteristics                                                                                           | Symbol             | Min         | Тур                  | Max         | Unit |

|-----------------------------------------------------------------------------------------------------------|--------------------|-------------|----------------------|-------------|------|

| Output Voltage EPADAC, I <sub>load</sub> = ± 100 μA<br>PADAC = 000000<br>PADAC = 100000<br>PADAC = 111111 | V <sub>out</sub>   | -<br>-<br>- | 0.02<br>1.60<br>3.08 | -<br>-<br>- | V    |

| Resolution                                                                                                | RESOL              | -           | 6                    | -           | Bits |

| Linearity                                                                                                 | INL/DNL            | -           | ± 1.0                | -           | LSB  |

| Average Supply Current (1-slot packet)                                                                    | I <sub>CCDAC</sub> | -           | 197                  | -           | μΑ   |

# Freescale Semiconductor, Inc. Electrical Characteristics

## **Table 6. Power Consumption Characteristics**

**Note:** (VCC\_RF = 2.7 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC, T<sub>A</sub> = 25° C, Reference Crystal = 13 MHz, Register bit settings according to Figure 94, unless otherwise noted. See Figure 3.)

| Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Symbol                                                                                                                                                                                                                   | Typical<br>Average                                                                                                                     | Max Peak                                                                                                                               | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|

| Total Power Supply Current SCO link, HV1 SCO link, HV2 SCO link, HV3 ACL link, 1-slot symmetric ACL link, 3-slot symmetric ACL link, 5-slot symmetric Standby Mode (No RF activity) Sniff Mode, 0.5 s Sniff Mode, 1.0 s Sniff Mode, 2.0 s Hold Mode Inquiry Scan Mode, 1.28 s interval Page Scan Mode, 1.28 s interval Inquiry and Page Scan Mode, 1.28 s interval                                                                                                                  | TOTHV1                                                                                                                                                                                                                   | TBD                                                                                                | TBD                                                                                                | mA   |

| RF Power Supply Current Transmit, 1 slot ACL Transmit, 3 slot ACL Transmit, 5 slot ACL Transmit, HV1 Transmit, HV2 Transmit, HV3 Transmit, Continuous Receive, 1 slot ACL Receive, 3 slot ACL Receive, 5 slot ACL Receive, HV1 Receive, HV2 Receive, HV3 Receive, Continuous Standby Mode (No RF activity) Sniff Mode, 0.5s Sniff Mode, 1.0s Sniff Mode, 2.0s Hold Mode Inquiry Scan Mode, 1.28s interval Page Scan Mode, 1.28s interval Inquiry and Page Scan Mode, 1.28s interval | CCRFtx1 CCRFtx3 CCRFtx5 CCRFtxHV1 CCRFtxHV2 CCRFtxHV3 CCRFtxc CCRFtxc CCRFrx1 CCRFrx3 CCRFrx5 CCRFrxHV1 CCRFrxHV2 CCRFrxHV3 CCRFrxE CCRFrxHV3 CCRFrxC CCRFstby CCRFs0.5 CCRFs1.0 CCRFs2.0 CCRFsbold CCRFs5 CCRFps CCRFps | 22<br>25<br>26<br>22<br>TBD<br>TBD<br>26<br>33<br>36<br>37<br>32<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD | 26<br>26<br>26<br>28<br>TBD<br>TBD<br>26<br>38<br>38<br>38<br>40<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD | mA   |

## **Table 6. Power Consumption Characteristics (Continued)**

**Note:** (VCC\_RF = 2.7 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC,  $T_A = 25^{\circ}$  C, Reference Crystal = 13 MHz, Register bit settings according to Figure 94, unless otherwise noted. See Figure 3.)

| Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Typical<br>Average                                                                                                                              | Max Peak                                                                                                                          | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|

| BB Power Supply Current Transmit, 1 slot ACL Transmit, 3 slot ACL Transmit, 5 slot ACL Transmit, HV1 Transmit, HV2 Transmit, HV3 Transmit, Continuous Receive, 1 slot ACL Receive, 3 slot ACL Receive, 5 slot ACL Receive, HV1 Receive, HV2 Receive, HV3 Receive, Continuous Standby Mode (No RF activity) Sniff Mode, 0.5s Sniff Mode, 1.0s Sniff Mode (2.0s Hold Mode Inquiry Scan Mode, 1.28s interval Inquiry and Page Scan Mode, 1.28s interval                                             | ICCBBtx1 ICCBBtx3 ICCBBtx5 ICCBBtxHV1 ICCBBtxHV2 ICCBBtxHV3 ICCBBrx1 ICCBBrx1 ICCBBrx5 ICCBBrxHV1 ICCBBrxHV2 ICCBBrxHV2 ICCBBrxHV2 ICCBBrxHV3 ICCBBrxC ICCBBrxHV3 ICCBBrxC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27 26 25 27 TBD TBD 25 27 25 26 28 TBD                                                                      | 38 38 38 41 TBD TBD 38 38 38 38 38 42 TBD                                                     | mA   |

| IO Power Supply Current Transmit, 1 slot ACL Transmit, 3 slot ACL Transmit, 5 slot ACL Transmit, HV1 Transmit, HV2 Transmit, HV3 Transmit, Continuous Receive, 1 slot ACL Receive, 3 slot ACL Receive, 5 slot ACL Receive, HV1 Receive, HV2 Receive, HV2 Receive, HV3 Receive, Continuous Standby Mode (No RF activity) Sniff Mode, 0.5s Sniff Mode, 1.0s Sniff Mode, 2.0s Hold Mode Inquiry Scan Mode, 1.28s interval Page Scan Mode, 1.28s interval Inquiry and Page Scan Mode, 1.28s interval | ICCIOtx1 ICCIOtx3 ICCIOtx5 ICCIOtxHV1 ICCIOtxHV2 ICCIOtxHV3 ICCIOtxC ICCIOtx1 ICCIOtx3 ICCIOtx5 ICCIOtx1 ICCIOtx3 ICCIOtx5 ICCIOtxHV1 ICCIOtxHV2 ICCIOtxHV2 ICCIOtxHV3 ICCIOtxC ICCIOtxHV3 ICCIOtxC ICCIO | 0.6<br>0.6<br>0.6<br>0.4<br>TBD<br>TBD<br>0.6<br>0.6<br>0.6<br>0.6<br>0.4<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD | 0.6<br>0.6<br>0.6<br>0.4<br>TBD<br>TBD<br>0.6<br>0.6<br>0.6<br>0.6<br>0.4<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD | mA   |

# Freescale Semiconductor, Inc. Electrical Characteristics

Table 6 shows the overall current consumed by the MC72000 in many well-known scenarios as well as detailed current in real-time specific modes.

The first row in Table 6 shows the maximum peak and typical average total current consumed by the device in most scenarios used by PDAs, cell phone design, and other audio-capable devices such as headsets. The current specified in this row is the total current consumed through the three power groups of the MC72000 (i.e., the voltage relationship between the three different supply voltages in these three groups are ignored). Power dissipated by the MC72000 may, therefore, be different than the direct power consumption calculated on the total current consumption.

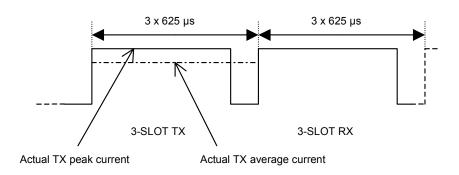

In order to find current values for special scenarios not covered by the typical values of total current consumption, the current consumed in each of the three power groups are also defined in a variety of usages. Each value represents the current consumed in between a repeatedly symmetrical timeframe, for example, the BB power supply current for transmitting one-slot ACL packets is defined as the time from start of TX burst to the start of RX burst, as the same current consumption is repeated again in the next TX slot. This also applies to all currents defined for receiving packets regardless of packet type. See example below in Figure 2. The repeatedly symmetrical pattern definition for the listed scenarios are shown in Table 7.

| Scenario                      | Defined as                                                    |

|-------------------------------|---------------------------------------------------------------|

| TX and RX, ACL, HV            | From TX burst to RX burst or vice versa                       |

| TX and RX Continuous          | Absolute value as there is no repeated pattern                |

| Standby Mode                  | Absolute value as there is no repeated pattern                |

| Sniff Mode                    | One sniff cycle with defined length in seconds                |

| Hold Mode                     | Total hold time from start to finish                          |

| Inquiry and/or Page Scan Mode | One page/inquiry scan interval with defined length in seconds |

**Table 7. Real-time Current Consumption Definitions**

Figure 2. Power Consumption Characteristics

### Table 8. Receiver AC Electrical Specifications

**Note:** (VCC\_RF = 2.7 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC,  $T_A = 25^{\circ}$  C, unless otherwise noted, Desired RF<sub>in</sub> = 2.441 GHz @  $f_{dev}$  = 157.5 kHz, Interferer  $f_{dev}$  = 160 kHz, Modulation = GFSK, BT = 0.5, Bit Rate = 1.0 Mbps, Modulating payload data for desired signal = PRBS9, Modulating data for interfering signal = PRBS15 continuously modulated, Measured BER = 0.1%, Reference Crystal = 13 MHz, Register bit settings according to Figure 94, unless otherwise noted. Measurements made from LNA<sub>in</sub> to Recovered Data out. See Figure 3.)

| Characteristics                                                                                                                                                                                                                                                                                                                                | Symbol                            | Min         | Тур                                                        | Max                                                                | BT<br>Spec            | Unit                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------|------------------------------------------------------------|--------------------------------------------------------------------|-----------------------|--------------------------|

| Receiver Sensitivity $T_A = 25^{\circ} C$ $T_A = -40 \text{ to } 85^{\circ} C$                                                                                                                                                                                                                                                                 | SENS <sub>min</sub>               | -           | -85<br>-80                                                 | -<br>-75                                                           | ≤ -70                 | dBm                      |

| Maximum Usable Signal Level T <sub>A</sub> = -40 to 85° C                                                                                                                                                                                                                                                                                      | SENS <sub>max</sub>               | -20         | > 0                                                        | -                                                                  | ≥ -20                 | dBm                      |

| Co-Channel Interference @ -60 dBm                                                                                                                                                                                                                                                                                                              | C/I co                            | -           | 9                                                          | 11                                                                 | <u>&lt;</u> 11        | dB                       |

| Adjacent Interference Adjacent (±1 MHz) Interference @ -60 dBm Adjacent (±2 MHz) Interference @ -60 dBm Adjacent (≥3 MHz) Interference @ -67 dBm                                                                                                                                                                                               | C/I 1MHz<br>C/I 2MHz<br>C/I =3MHz | -<br>-<br>- | -7<br>-33<br>-41                                           | -3<br>-30<br>-40                                                   | ≤ 0<br>≤ -30<br>≤ -40 | dB                       |

| Image Frequency Interference @ -67 dBm                                                                                                                                                                                                                                                                                                         | C/I Image                         | -           | -16                                                        | -12                                                                | <u>&lt;</u> -9        | dB                       |

| Adjacent Interference to In-Band Image Frequency @ -67 dBm                                                                                                                                                                                                                                                                                     | C/I Image ±1                      | -           | -32                                                        | -28                                                                | ≤ -20                 | dB                       |

| Spurious Response Frequencies                                                                                                                                                                                                                                                                                                                  |                                   | -           | 3                                                          | 5                                                                  | 5                     |                          |

| Intermodulation Performance <sup>1</sup>                                                                                                                                                                                                                                                                                                       |                                   | -39         | -33                                                        | -                                                                  | ≥ -39                 | dBm                      |

| Receiver Spurious Emissions -40 to 85° C Bluetooth 30 MHz to 1.0 GHz 1.0 GHz to 12.75 GHz GSM/DCS and UMTS downlink 2110 MHz - 2170 MHz (WCDMA-FDD)² 2010 MHz - 2025 MHz (WCDMA-TDD)² 1900 MHz - 1920 MHz (WCDMA-TDD)² 869 MHz - 894 MHz (GSM 850)³ 921 MHz - 960 MHz (GSM 900)³ 1805 MHz - 1880 MHz (DCS1800)³ 1930 MHz - 1990 MHz (PCS1900)³ |                                   |             | -66<br>-57<br>-186<br>-184<br>-184<br>-177<br>-177<br>-177 | -57<br>-47<br>-180<br>-180<br>-180<br>-163<br>-163<br>-170<br>-168 | ≤ -57<br>≤ -47        | dBm/<br>100kHz<br>dBm/Hz |

# Freescale Semiconductor, Inc. Electrical Characteristics

#### Table 8. Receiver AC Electrical Specifications (Continued)

**Note:** (VCC\_RF = 2.7 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC,  $T_A = 25^{\circ}$  C, unless otherwise noted, Desired RF<sub>in</sub> = 2.441 GHz @  $f_{dev}$  = 157.5 kHz, Interferer  $f_{dev}$  = 160 kHz, Modulation = GFSK, BT = 0.5, Bit Rate = 1.0 Mbps, Modulating payload data for desired signal = PRBS9, Modulating data for interfering signal = PRBS15 continuously modulated, Measured BER = 0.1%, Reference Crystal = 13 MHz, Register bit settings according to Figure 94, unless otherwise noted. Measurements made from LNA<sub>in</sub> to Recovered Data out. See Figure 3.)

| Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                | Symbol              | Min                                                                       | Тур                                                              | Max                                  | BT<br>Spec                       | Unit   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------|----------------------------------|--------|

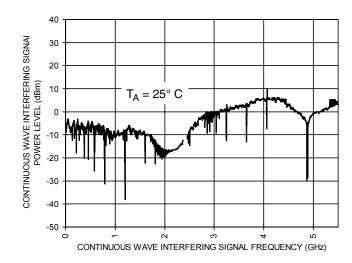

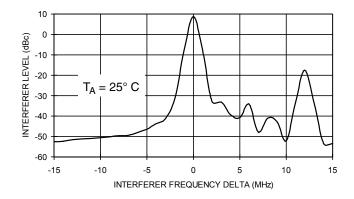

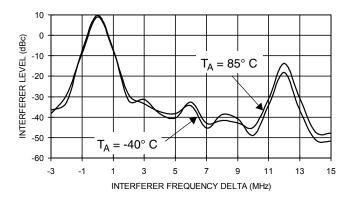

| Receiver Blocking Performance <sup>4</sup> (See Figure 11)  Bluetooth  30 MHz to 1.999 GHz  2.0 GHz to 2.399 GHz  2.498 GHz to 2.999 GHz  3.0 GHz to 12.75 GHz  GSM/DCS and UMTS uplink <sup>5</sup> 1920 MHz - 1980 MHz (WCDMA-FDD)  2010 MHz - 2025 MHz (WCDMA-TDD)  1900 MHz - 1920 MHz (WCDMA-TDD)  824 MHz - 849 MHz (GSM 850)  876 MHz - 915 MHz (GSM 900)  1710 MHz - 1785 MHz (DCS1800)  1850 MHz - 1910 MHz (PCS1900) |                     | TBD<br>TBD<br>TBD<br>TBD<br>-21<br>-20<br>-23<br>-18<br>-11<br>-16<br>-23 | -9<br>-16<br>TBD<br>TBD<br>-15<br>-16<br>-15<br>-10<br>-5<br>-11 | -<br>-<br>-<br>-<br>-<br>-<br>-<br>- | ≥ -10<br>≥ -27<br>≥ -27<br>≥ -10 | dBm    |

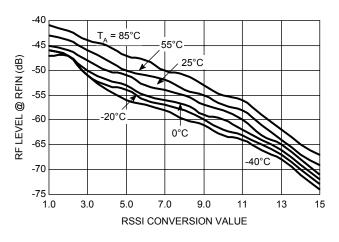

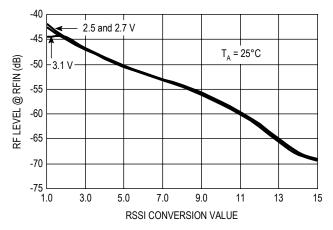

| RSSI Conversion Value, (R4/6 and R9/8 = 1) RF level at LNA input to maintain conversion value of: 1000 (binary) 1111                                                                                                                                                                                                                                                                                                           | RSSI                | -60<br>-                                                                  | -56<br>-70                                                       | -52<br>-66                           |                                  | dBm    |

| RSSI Resolution, (R4/6 and R9/8 = 1)                                                                                                                                                                                                                                                                                                                                                                                           | RSSI <sub>res</sub> | -                                                                         | 1.8                                                              | -                                    |                                  | dB/bit |

| RSSI Dynamic Range                                                                                                                                                                                                                                                                                                                                                                                                             |                     | 20                                                                        | -                                                                | -                                    |                                  | dB     |

| RSSI Average Supply Current, (R4/6 and R9/8 = 1)                                                                                                                                                                                                                                                                                                                                                                               |                     | -                                                                         | 40                                                               | -                                    |                                  | μΑ     |

- 1. Measured at f2 f1 = 5.0 MHz in accordance with Bluetooth specification.

- 2. Equivalent noise floor to 5 MHz bandwidth

- 3. Equivalent noise floor to 200 kHz bandwidth

- 4. As allowed by the Bluetooth specification, up to five exceptions may be taken for spurious response.

- Measured according to Bluetooth Specification, but using a correct modulated and bursting GSM/DCS/ UMTS interfering signal, based on one timeslot.

### Table 9. Transmitter AC Electrical Specifications

**Note:** (VCC\_RF = 2.7 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC,  $T_A$  = -40 to 85° C, unless otherwise noted, Modulation = GFSK, BT = 0.5, Bit Rate = 1.0 Mbps, Reference Crystal = 13 MHz, Register bit settings according to Figure 94, unless otherwise noted. Measurements made at PAout. See Figure 3.)

| Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Symbo                            | Min                             | Тур                                                                      | Max                                                                     | Bluetooth<br>Specificati<br>on   | Unit                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------|--------------------------|

| RF Transmit Output Power $T_A = 25^{\circ} C$ $T_A = 85^{\circ} C$ $T_A = -40^{\circ} C$                                                                                                                                                                                                                                                                                                                                                                                                   | P <sub>out</sub>                 | -3.5<br>-3.5<br>-3.5            | 1.5<br>-1.0<br>2.5                                                       | 4.0<br>4.0<br>4.0                                                       | - 6 to 4                         | dBm                      |

| -20 dBc Occupied Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | OccBW                            | -                               | 930                                                                      | 1000                                                                    | <u>&lt;</u> 1000                 | kHz                      |

| In-Band Spurious Emissions Adjacent Channel ±2 MHz Offset Adjacent Channel ±3 MHz Offset Adjacent Channel >3 MHz Offset                                                                                                                                                                                                                                                                                                                                                                    | Inb2<br>Inb3<br>Inbg3            | -<br>-<br>-                     | -53<br>-63<br>-65                                                        | -20<br>-40<br>-40                                                       | ≤ -20<br>≤ -40<br>≤ -40          | dBm/<br>100kHz           |

| In-Band Spurious Emission Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Inbex                            | -                               | 0                                                                        | 3                                                                       | <u>≤</u> 3                       |                          |

| Out of Band Spurious Emissions Bluetooth 30 MHz to 1.0 GHz 1.0 GHz to 12.75 GHz (2 <sup>nd</sup> Harmonic) 1.8 GHz to 1.9 GHz 5.15 GHz to 5.3 GHz GSM/DCS and UMTS downlink 2110 MHz - 2170 MHz (WCDMA-FDD) <sup>1</sup> 2010 MHz - 2025 MHz (WCDMA-TDD) <sup>1</sup> 1900 MHz - 1920 MHz (WCDMA-TDD) <sup>1</sup> 869 MHz - 894 MHz (GSM 850) <sup>2</sup> 921 MHz - 960 MHz (GSM 900) <sup>2</sup> 1805 MHz - 1880 MHz (DCS1800) <sup>2</sup> 1930 MHz - 1990 MHz (PCS1900) <sup>2</sup> | Outb1<br>Outb2<br>Outb3<br>Outb4 | -<br>-<br>-<br>-<br>-<br>-<br>- | -66<br>-17<br>-76<br>-77<br>-177<br>-190<br>-190<br>-175<br>-175<br>-175 | -36<br>-5<br>-47<br>-47<br>-168<br>-178<br>-182<br>-153<br>-156<br>-165 | ≤ -36<br>≤ -30<br>≤ -47<br>≤ -47 | dBm/<br>100kHz<br>dBm/Hz |

| Average Frequency Deviation                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Dev                              | 140                             | 160                                                                      | 175                                                                     | 140 to 175                       | kHz                      |

| Minimum Frequency Deviation                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DevMin                           | 115                             | 152                                                                      | -                                                                       | ≥ 115                            | kHz                      |

| High vs. Low Frequency Modulation<br>Percentage                                                                                                                                                                                                                                                                                                                                                                                                                                            | ModIn                            | 80                              | 95                                                                       | -                                                                       | ≥ 80                             | %                        |

| Initial Frequency Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | InitFA                           | -75                             | ± 5                                                                      | 75                                                                      | ± 75                             | kHz                      |

| Transmitter Center Frequency Drift One-slot packet Three-slot packet Five-slot packet                                                                                                                                                                                                                                                                                                                                                                                                      | d1<br>d3<br>d5                   | -25<br>-40<br>-40               | ±8<br>±12<br>±12                                                         | 25<br>40<br>40                                                          | ± 25<br>± 40<br>± 40             | kHz                      |

| Maximum Drift Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Dmax                             | -20                             | ± 8                                                                      | 20                                                                      | ± 20                             | kHz/ 50µs                |

| PA Output Impedance 25° C                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | S22                              | See Table 22                    |                                                                          |                                                                         |                                  | dB                       |

- 1. Equivalent noise floor to 5 MHz bandwidth

- 2. Equivalent noise floor to 200 kHz bandwidth

# Freescale Semiconductor, Inc. Electrical Characteristics

## Table 10. MC72000 Receive Characteristics

**Note:** (VCC\_RF = 2.7 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC, T<sub>A</sub> = -40 to 85° C, Reference Crystal = 13 MHz, Register bit settings according to Figure 94, unless otherwise noted. Interfering access code at the minimum Hamming distance of 14 according to Bluetooth specifications. See Figure 3.)

| Characteristics                                                                  | Symbol | Min | Тур | Max | Unit |

|----------------------------------------------------------------------------------|--------|-----|-----|-----|------|

| False Detection Rate In Presence of Noise In Presence of Interfering Access Code |        | -   | 0   | -   | %    |

| Actual Sensitivity     Actual Sensitivity + 10 dB                                |        | -   | 0   | -   |      |

| Missed Detection Rate                                                            |        |     |     |     | %    |

| @ Actual Sensitivity                                                             |        | -   | 0   | -   |      |

| @ Actual Sensitivity + 10 dB                                                     |        | -   | 0   | -   |      |

| @ Actual Sensitivity – 16 dB                                                     |        | -   | 100 | -   |      |

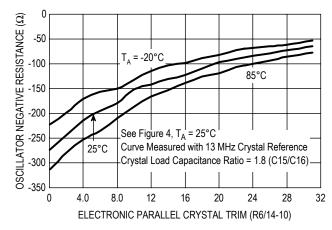

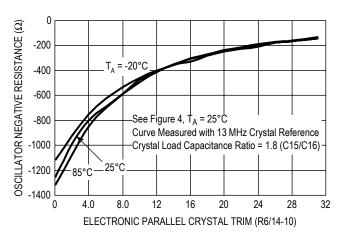

## **Table 11. Reference Oscillator Electrical Specifications**

**Note:** (VCC\_RF = 2.7 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC, T<sub>A</sub> = 25° C, Reference Crystal = 13 MHz, Register bit settings according to Figure 94, unless otherwise noted. See Figure 3.)

|                                                                                                                  |                      | 1           | 1              | 1           | 1               |

|------------------------------------------------------------------------------------------------------------------|----------------------|-------------|----------------|-------------|-----------------|

| Characteristics                                                                                                  | Symbol               | Min         | Тур            | Max         | Unit            |

| Crystal Frequency Range                                                                                          | f <sub>RefXTAL</sub> | 12          | -              | 15          | MHz             |

| External Drive Frequency Range                                                                                   | f <sub>RefXTAL</sub> | 12          | -              | 26          | MHz             |

| Oscillator Drive Level External Reference Crystal Reference                                                      |                      | 0.2         | - 0.8          | 1.0         | V <sub>pp</sub> |

| Crystal Load Capacitance (Resonant Parallel)                                                                     |                      | -           | 13             | -           | pF              |

| Maximum Crystal Equivalent Series Resistance (ESR)                                                               |                      | -           | -              | 100         | Ω               |

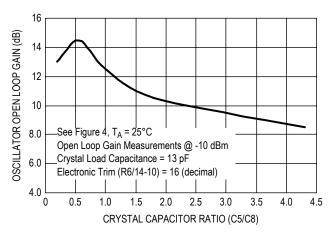

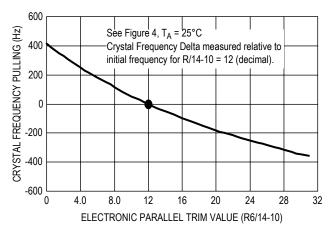

| Typical Crystal Adjustment Range                                                                                 |                      |             | See Fig        | jure 26     |                 |

| Recommended Crystal Tolerance over Temperature (-40 to +85° C)                                                   |                      | -           | ±10            | -           | ppm             |

| Electronic Parallel Trim Capacitance Range                                                                       | C <sub>PT</sub>      | -           | 0 to<br>9.3    | -           | pF              |

| Electronic Parallel Trim Capacitance Resolution                                                                  |                      | -           | 0.3            | -           | pF              |

| Oscillator Bias Current<br>(R11/0) = 0, (R11/4) = 0 or 1<br>(R11/0) = 1, (R11/4) = 0<br>(R11/0) = 1, (R11/4) = 1 |                      | -<br>-<br>- | 0<br>50<br>200 | -<br>-<br>- | μА              |

## Table 11. Reference Oscillator Electrical Specifications (Continued)

**Note:** (VCC\_RF = 2.7 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC,  $T_A = 25^{\circ}$  C, Reference Crystal = 13 MHz, Register bit settings according to Figure 94, unless otherwise noted. See Figure 3.)

| Characteristics                                                                                    | Symbol            | Min | Тур                         | Max          | Unit       |

|----------------------------------------------------------------------------------------------------|-------------------|-----|-----------------------------|--------------|------------|

| Input Impedance at XBASE (Reference Frequency = 12 to 26 MHz, R11/0 = 0 or 1) Parallel Capacitance | C <sub>P</sub>    | -   | 1.0 + Parallel Trim Capaci- | -            | pF         |

| Parallel Resistance                                                                                | R <sub>P</sub>    | -   | tance<br>20                 | -            | kΩ         |

| Input Phase Noise at XBASE (Reference Frequency = 12 to 26 MHz, R11/0 = 0 or 1)                    |                   |     |                             |              | dBc/<br>Hz |

| 100 Hz                                                                                             |                   | -   | -                           | -70          |            |

| 1 kHz                                                                                              |                   | -   | -                           | -90          |            |

| 10 kHz                                                                                             |                   | -   | -                           | -105         |            |

| 100 kHz<br>1 MHz                                                                                   |                   | -   | -                           | -110<br>-130 |            |

| Duty Cycle for External Reference                                                                  |                   | TBD | 50                          | TBD          | %          |

| Input Bias Voltage (XBASE)                                                                         |                   | -   | 1.2                         | -            | V          |

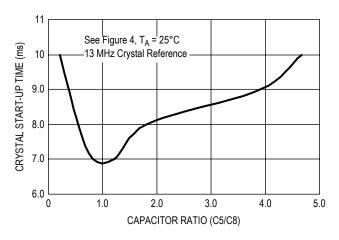

| Start-up Time (using Crystal)                                                                      | T <sub>WAIT</sub> | -   | 7.5                         | -            | Ms         |

## Table 12. Low Power Oscillator Electrical Specifications

**Note:**  $(VCC_RF = 2.7 \text{ VDC}, \text{VDD}_BB = 1.8 \text{ VDC}, \text{VDD}_IO = 3 \text{ VDC}, T_A = 25^{\circ} \text{ C}, \text{ Reference Crystal} = 13 \text{ MHz}, \text{ Register bit settings according to Figure 5, unless otherwise noted. See Figure 3.)}$

| Characteristics                                                                | Symbol           | Min      | Тур      | Max    | Unit |

|--------------------------------------------------------------------------------|------------------|----------|----------|--------|------|

| Crystal Frequency                                                              | fLPXTAL          |          | 32.768   | 8      | kHz  |

| External Drive Frequency Range                                                 | fLPXTAL          |          | 32.768   | 3      | kHz  |

| Oscillator Drive Level (DC or AC coupled) External Reference Crystal Reference |                  | TBD<br>- | -<br>TBD | VDD_BB | Vpp  |

| Crystal Load Capacitance (Resonant Parallel)                                   |                  | -        | TBD      | -      | pF   |

| XTAL Transconductance                                                          |                  | -        | 15       | -      | mA/V |

| XTAL Output Resistance (XTAL_BB)                                               | 9 <sub>mLP</sub> | -        | 250      | -      | kΩ   |

| Maximum Crystal Equivalent Series Resistance (ESR)                             | R <sub>oLP</sub> | -        | -        | TBD    |      |

| Recommended Crystal Tolerance over Temperature (-40 to +85°C)                  |                  | -        | ± 200    | -      | ppm  |

| Oscillator Bias Current                                                        |                  | -        | TBD      | -      | μA   |

# Freescale Semiconductor, Inc. Electrical Characteristics

## Table 12. Low Power Oscillator Electrical Specifications (Continued)

**Note:** (VCC\_RF = 2.7 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC,  $T_A = 25^{\circ}$  C, Reference Crystal = 13 MHz, Register bit settings according to Figure 5, unless otherwise noted. See Figure 3.)

| Characteristics                                                      | Symbol              | Min | Тур        | Max | Unit |

|----------------------------------------------------------------------|---------------------|-----|------------|-----|------|

| Input Impedance at EXTAL_BB Parallel Capacitance Parallel Resistance |                     |     | TBD<br>TBD |     |      |

| Duty Cycle for External Reference                                    |                     | TBD | 50         | TBD | %    |

| Start-up Time (using Crystal)                                        | T <sub>LPWAIT</sub> | 5   | -          | 700 | ms   |

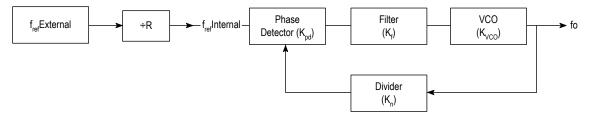

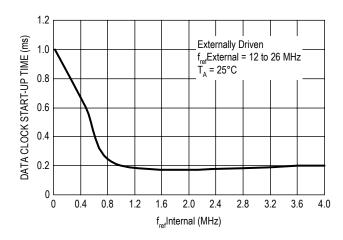

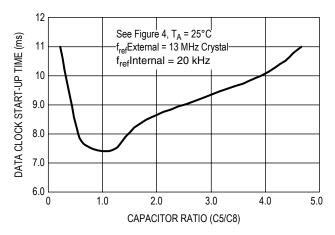

### Table 13. Data Clock PLL Electrical Specifications

**Note:** (VCC\_RF = 2.7 VDC, VDD\_BB = 1.8 VDC, VDD\_IO = 3 VDC, T<sub>A</sub> = 25° C, Reference Crystal = 13 MHz, Register bit settings according to Figure 94, unless otherwise noted. See Figure 3.)

| Characteristics                                    | Symbol           | Min | Тур        | Max  | Unit       |

|----------------------------------------------------|------------------|-----|------------|------|------------|

| Internal Reference Frequency                       |                  | -   | 20         | 4000 | kHz        |

| Data Clock Output Frequency                        |                  | -   | 24         | -    | MHz        |

| R Counter (R6/9-0) (Base 10)                       |                  | 3   | 650        | 1023 |            |

| N Counter (R7/10-0) (Base 10)                      |                  | 3   | 1200       | 2047 |            |

| Loop Filter Bandwidth                              |                  | -   | 1          | 200  | kHz        |

| Phase Detector Gain Constant                       | K <sub>pd</sub>  | -   | 15.9       | -    | μΑ/<br>rad |

| VCO Gain Constant                                  | K <sub>VCO</sub> | -   | 15         | -    | MHz/<br>V  |

| Start-up Time External Reference Crystal Reference |                  | -   | 1.0<br>7.5 | -    | Ms         |

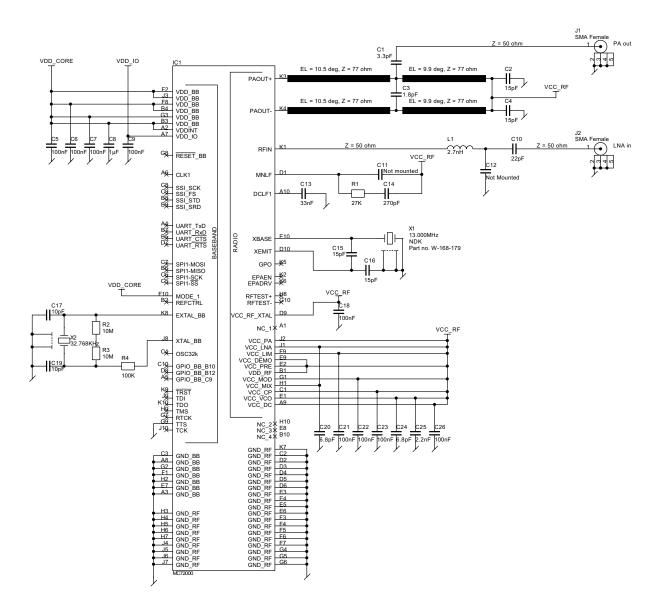

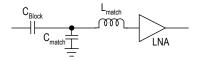

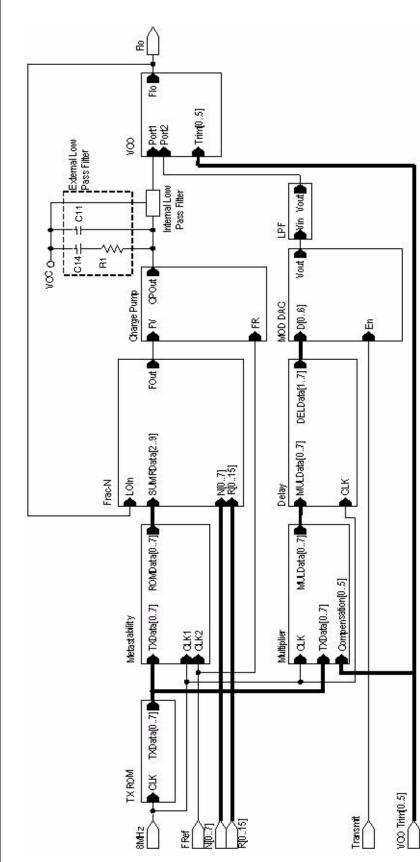

The following figure shows a typical test circuit schematic.

Figure 3. Typical Test Circuit Schematic

# 4 Package Pinout

#### NOTE:

Low power and small PCB footprints are critical for certain applications. Therefore, input pins not used must be pulled high using internal pull-ups to avoid floating nodes and the need for external pull-up resistors. Unused pins may also be tied to an external appropriate logic voltage level (for example, either VDD or GND). Weak pull-ups are available internally on all IO and BB pins (100k ohms typical case), pull-downs are available on RESET\_BB, TCK, TRST\_B pins. Internal level-shifters are used to accommodate the difference between BB and IO voltages. This provides glueless interface to peripherals.

# 4.1 Pin Assignment Listing

The following table (Table 9) shows the pin assignment listing for the MC72000 IC. The pins are organized into functional groups.

- The Pin Name and Functionality columns show the actual name and a brief description of each pin, with respect to the ball assignment in the column Ball #.

- The Power Group column lists the Supply Power Group assignment.

- The Pin Type column shows the type of internal circuitry to the chip.

- The Reset State column lists the pin input/output direction at chip RESET\_BB.

- The Alternate Function column lists each of the GPIO port alternate input and output selections available. Some selections are test- or development-mode specific.

Table 14. Pin Names and Functions

| Ball # | Pin Name       | Functionality             | Power<br>Group | Pin Type                 | Reset<br>State | Alternate<br>Function |

|--------|----------------|---------------------------|----------------|--------------------------|----------------|-----------------------|

| A1     | N/C            | Not connected             | -              | -                        | -              | -                     |

| A2     | VDD_BB         | Baseband interface supply | CORE           | Power line               | -              | -                     |

| A3     | GND_BB         | Baseband ground           | CORE           | Power line               | -              | -                     |

| A4     | UART_TXD       | UART - Transmit data      | I/O            | Digital tri-state output | Z/H            | GPIO_C0<br>CSPI0_REQ  |

| A5     | GPIO_BB_C<br>9 | General purpose I/O       | I/O            | Digital I/O              | Z/H            | XACK                  |

| A6     | CLK1           | Programmable clock output | I/O            | Digital I/O              | O/L            | GPIO_C8<br>TIM_0_O    |

| A7     | VDD_IO         | I/O port B and C supply   | I/O            | Power line               | -              | -                     |

| A8     | GND_IO         | I/O ground                | I/O            | Power line               | -              | -                     |

| A9     | VCC_DC         | RF Data clock supply      | RF             | Power line               | -              | -                     |

| A10    | DCLF1          | RF Data clock loop filter | RF             | Analog output            | -              | -                     |

Table 14. Pin Names and Functions (Continued)

|     |                 |                                     | 1    | , , , , , , , , , , , , , , , , , , , | 1   |                                          |

|-----|-----------------|-------------------------------------|------|---------------------------------------|-----|------------------------------------------|

| B1  | VDD_RF          | RF logic supply                     | RF   | Power line                            | -   | -                                        |

| B2  | REFCTRL         | RF reference clock control          | CORE | Digital output                        | O/L | -                                        |

| В3  | VDD_BB          | Baseband miscellaneous supply       | CORE | Power line                            | -   | -                                        |

| В4  | VDD_BB          | Baseband core supply                | CORE | Power line                            | -   | -                                        |

| B5  | UART_CTS        | UART - Clear to send                | I/O  | Digital tri-state output              | Z/H | GPIO_C1<br>CSPI1_REQ                     |

| В6  | SPI1_MISO       | SPI1 - Master in/Slave out          | I/O  | Digital I/O                           | O/L | GPIO_C6<br>ABORT                         |

| B7  | UART_RXD        | UART - Receive data                 | I/O  | Digital I/O                           | Z/H | GPIO_C2<br>TIM_0_I                       |

| B8  | SSI_STD         | SSI - Serial transmit data          | I/O  | Digital I/O                           | Z/H | GPIO_B2<br>BT_TP2                        |

| B9  | SSI_SRD         | SSI - Serial receive data           | I/O  | Digital I/O                           | Z/H | GPIO_B5<br>BT_TP5                        |

| B10 | N/C             | Not connected                       | -    | -                                     | -   | -                                        |

| C1  | VCC_CP          | RF Frac-N charge pump supply        | RF   | Power line                            | -   | -                                        |

| C2  | GND_RF          | RF front end ground                 | RF   | Power line                            | -   | -                                        |

| C3  | GND_BB          | Baseband miscellaneous ground       | CORE | Power line                            | -   | -                                        |

| C4  | OSC32K          | Buffered low power 32.768 kHz clock | I/O  | Digital I/O                           | O/L | GPIO_C10<br>TIM_1_O                      |

| C5  | SPI1_SS         | SPI1 - Slave select                 | I/O  | Digital output                        | O/H | GPIO_C4<br>SYSCLK                        |

| C6  | SPI1_SCK        | SPI1 - Serial clock                 | I/O  | Digital output                        | O/H | GPIO_C5<br>SH_STROB<br>E                 |

| C7  | SPI1_MOSI       | SPI1 - Master out/Slave in          | I/O  | Digital I/O                           | Z/H | GPIO_C7<br>REFCLK                        |

| C8  | SSI_SCK         | SSI - Serial clock                  | I/O  | Digital I/O                           | Z/H | GPIO_B0/<br>GPIO_B3<br>BT_TP0/<br>BT_TP3 |

| C9  | SSI_FS          | SSI - Frame sync                    | I/O  | Digital I/O                           | Z/H | GPIO_B1/<br>GPIO_B4<br>BT_TP1/<br>BT_TP4 |

| C10 | GPIO_BB_B<br>10 | General purpose I/O                 | I/O  | Digital I/O                           | Z/H | UART_TXD                                 |

| D1  | MNLF            | RF Main Frac-N loop filter          | RF   | Analog output                         | -   | -                                        |

Table 14. Pin Names and Functions (Continued)

| D2  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

|-----|-----------------|-------------------------------|------|---------------|-----|--------------------|

| D3  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| D4  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| D5  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| D6  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| D7  | UART_RTS        | UART - Request to send        | I/O  | Digital I/O   | Z/H | GPIO_C3<br>TIM_1_I |

| D8  | GPIO_BB_B<br>12 | General purpose I/O           | I/O  | Digital I/O   | Z/H | UART_RXD           |

| D9  | VCC_RF_XT<br>AL | RF crystal oscillator supply  | RF   | Power line    | -   | -                  |

| D10 | XEMIT           | RF crystal oscillator emitter | RF   | Analog output | -   | -                  |

| E1  | VCC_VCO         | RF VCO supply                 | RF   | Power line    | -   | -                  |

| E2  | VCC_PRE         | RF Frac-N prescaler supply    | RF   | Power line    | -   | -                  |

| E3  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| E4  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| E5  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| E6  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| E7  | GND_BB          | Baseband ground               | CORE | Power line    | -   | -                  |

| E8  | N/C             | Not connected                 | -    | -             | -   | -                  |

| E9  | VCC_DEMO        | RF demodulator supply         | RF   | Power line    | -   | -                  |

| E10 | XBASE           | Crystal oscillator base       | RF   | Analog input  | -   | -                  |

| F1  | GND_BB          | Baseband ground               | CORE | Power line    |     |                    |

| F2  | VDD_BB          | Baseband core supply          | CORE | Power line    | -   | -                  |

| F3  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| F4  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| F5  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| F6  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| F7  | GND_RF          | RF front end ground           | RF   | Power line    | -   | -                  |

| F8  | VDD_BB          | Baseband core supply          | CORE | Power line    | -   | -                  |

| F9  | VCC_LIM         | RF limiter supply             | RF   | Power line    | -   | -                  |

| F10 | MODE1           | Baseband boot mode select 1   | CORE | Digital input | I   | -                  |

**Table 14. Pin Names and Functions (Continued)**

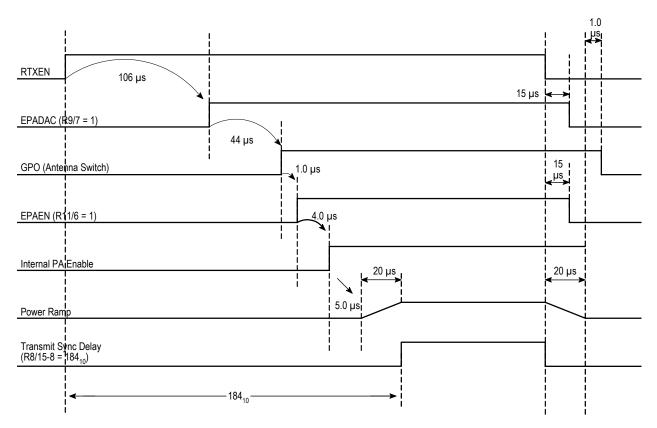

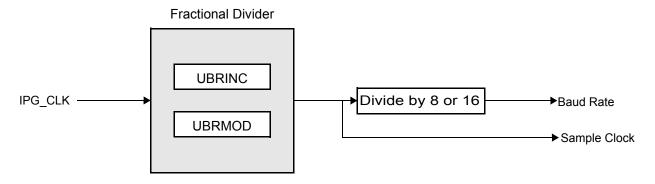

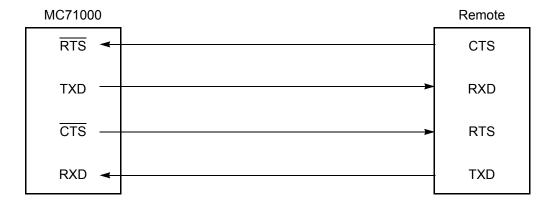

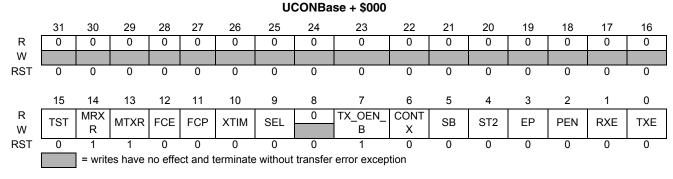

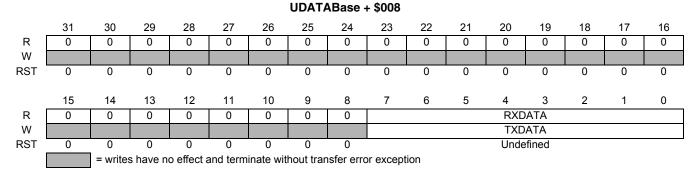

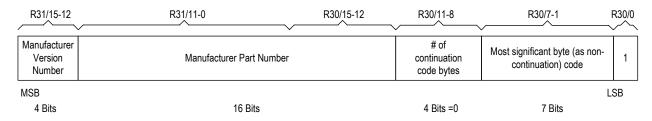

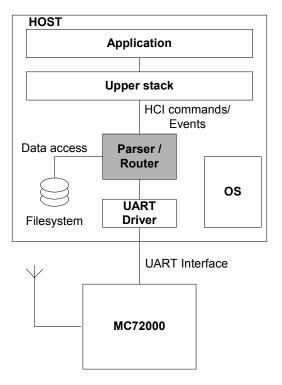

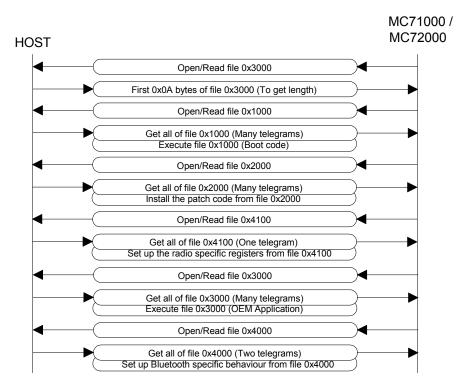

| G1  | VCC_MOD  | RF modulation DAC supply                                                                        | RF   | Power line                       | - | - |