# **R80515** 8-bit Microcontroller Megafunction

## **General Description**

The R80515 is a fast, single-chip, 8-bit microcontroller that executes all ASM51 instructions. It has the same instruction set as the 80C31, but executes operations an average of 8 times faster.

The R80515 provides software and hardware interrupts, extra timer features, power management, and Infinion peripherals support. On-chip debugging is an option.

The microcode-free, strictly synchronous design was developed for reuse in ASICs and FPGAs.

#### **Features**

- Single clock per machine cycle

- Reduced instruction cycle time up to 12 times

- 8-bit Control Unit

- 8-bit Arithmetic-Logic Unit

- Multiplication/Division Unit

- o 16 x 16-bit multiplication and division; 32 / 16-bit division

- Four 8-bit Input/Output ports

- Alternate port functions such as external interrupts & serial interface are separated, providing extra port pins when compared with the standard 8051

- Three 16-bit Timer/Counters

- Compare/Capture Unit

- Two Serial Peripheral Interfaces in full duplex mode

- Four priority/thirteen sources Interrupt Controller

- 15-bit Programmable Watchdog Timer

- Internal Data Memory interface can address up to 256 bytes of Read/Write Data Memory Space

- External Memory interface

- Can address up to 64 K bytes of External Program Memory Space

- Can address up to 64K bytes of External Data Memory Space

- o De-multiplexed address/data bus to allow easy connection to memories

- Variable length MOVX to access fast/slow RAM or peripherals

- Variable length code fetch and MOVC to access fast/slow program memory

- Dual data pointer for fast data block transfers

- Special Function Registers interface: serves up to 74 external registers

- Power Management Unit

- Optional JTAG debugging

# **Applications**

- Embedded microcontroller systems

- Data computation and transfer

- Communication systems

- Professional audio and video

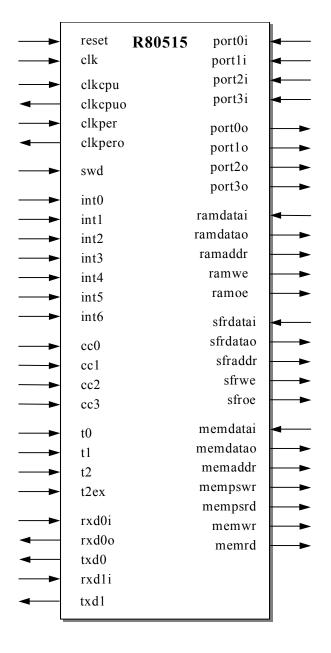

# **Symbol**

# **Pin Description**

| Name             | Туре      | Polarity/<br>Bus Size | Description                                                                                                                                                                                          |  |

|------------------|-----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| port0i<br>port0o | In<br>Out | 8 8                   | Port 0<br>8-bit bi-directional I/O<br>port with separated<br>inputs and outputs                                                                                                                      |  |

| port1i<br>port1o | In<br>Out | 8                     | Port 1 8-bit bi-directional I/O port with separated inputs and outputs                                                                                                                               |  |

| port2i<br>port2o | In<br>Out | 8 8                   | <b>Port 2</b> 8-bit bi-directional I/O port with separated inputs and outputs                                                                                                                        |  |

| port3i<br>port3o | In<br>Out | 8 8                   | Port 3 8-bit bi-directional I/O port with separated inputs and outputs                                                                                                                               |  |

| clk              | In        | Rising                | Clock A pulse for internal clock counters and all synchronous circuits                                                                                                                               |  |

| reset            | In        | High                  | Resets the device when this pin is held high for two clock cycles while the oscillator is running                                                                                                    |  |

| clkcpu           | In        | Rising                | Engine clock A pulse for internal circuits that are stopped when the R80515 is in the IDLE or STOP mode                                                                                              |  |

| clkcpuo          | Out       | Rising                | Is the gated clk clock. clkcpuo stays low when the R80515 enters into IDLE or STOP mode. The clkcpuo is dedicated to off-core connection to the clkcpu input                                         |  |

| clkper           | In        | Rising                | Peripheral clock A pulse for internal circuits that are stopped when the R80515 is in STOP mode                                                                                                      |  |

| clkpero          | Out       | Rising                | Peripheral clock<br>output is the gated<br>clk clock. clkpero stays<br>low when the R80515<br>enters into STOP<br>mode. The clkpero is<br>dedicated to off-core<br>connection to the<br>clkper input |  |

| NI                   |            |                             |                                               |  |  |  |

|----------------------|------------|-----------------------------|-----------------------------------------------|--|--|--|

| Name                 | Туре       | Polarity/<br>Bus Size       | Description                                   |  |  |  |

| swd                  | In         | High                        | Start Watchdog                                |  |  |  |

|                      |            | =                           | Timer                                         |  |  |  |

|                      |            |                             | A high on this pin                            |  |  |  |

|                      |            |                             | during reset starts the                       |  |  |  |

|                      |            |                             | watchdog timer                                |  |  |  |

|                      |            |                             | immediately after                             |  |  |  |

|                      |            |                             | reset is released                             |  |  |  |

| 1                    | _          |                             | External Interrupts                           |  |  |  |

| into                 | In         | Low/Falling                 | External interrupt 0                          |  |  |  |

| int1<br>int2         | In<br>In   | Low/Falling<br>Fall./Rising | External interrupt 1 External interrupt 2     |  |  |  |

| int3                 | In         | Fall./Rising                | External interrupt 2 External interrupt 3     |  |  |  |

| int4                 | In         | Rising                      | External interrupt 4                          |  |  |  |

| int5                 | In         | Rising                      | External interrupt 5                          |  |  |  |

| int6                 | In         | Rising                      | External interrupt 6                          |  |  |  |

|                      |            | rasing                      | Compare/Capture                               |  |  |  |

| ссо                  | In         | High                        | Compare/Capture 0                             |  |  |  |

| cc1                  | In         | High                        | Compare/Capture 1                             |  |  |  |

| cc2                  | In         | High                        | Compare/Capture 2                             |  |  |  |

| cc3                  | In         | High                        | Compare/Capture 3                             |  |  |  |

|                      |            |                             | Serial 0 interface                            |  |  |  |

| rxd0i                | In         | -                           | Serial 0 receive data                         |  |  |  |

| rxd0o                | Out        | -                           | Serial 0 transmit data                        |  |  |  |

| txd0                 | Out        | -                           | Serial 0 transmit data                        |  |  |  |

|                      |            |                             | or receive clock in                           |  |  |  |

|                      |            |                             | mode 0                                        |  |  |  |

|                      | _          |                             | Serial 1 interface                            |  |  |  |

| rxd1i                | In         | -                           | Serial 1 receive data                         |  |  |  |

| rxd1o                | Out        | -                           | Serial 1 transmit data                        |  |  |  |

| 10                   | T          | F-11:                       | Timer inputs                                  |  |  |  |

| t0<br>t1             | In<br>In   | Falling                     | Timer 0 external input Timer 1 external input |  |  |  |

| t2                   | In         | Falling<br>Falling          | Timer 1 external input Timer 2 external input |  |  |  |

| t2ex                 | In         | Falling                     | Timer 2 capture                               |  |  |  |

| LZEX                 | 111        | raining                     | trigger                                       |  |  |  |

|                      |            |                             | External Memory                               |  |  |  |

|                      |            |                             | interface                                     |  |  |  |

| memdatai             | In         | 8                           | Memory data input                             |  |  |  |

| memdatao             | Out        | 8                           | Memory data output                            |  |  |  |

| memaddr              | Out        | 16                          | Memory address                                |  |  |  |

| mempswr              | Out        | High                        | Program store write                           |  |  |  |

|                      |            |                             | enable                                        |  |  |  |

| mempsrd              | Out        | High                        | Program store read                            |  |  |  |

|                      |            |                             | enable                                        |  |  |  |

| memwr                | Out        | High                        | Data Memory write                             |  |  |  |

|                      |            |                             | enable                                        |  |  |  |

| memrd                | Out        | High                        | Data Memory read                              |  |  |  |

|                      |            |                             | enable                                        |  |  |  |

|                      |            |                             | Internal Data                                 |  |  |  |

| ramdata:             | In         | 0                           | Memory interface                              |  |  |  |

| ramdatai<br>ramdatao | In<br>Out  | 8                           | Data bus input<br>Data bus output             |  |  |  |

| ramdatao             | Out<br>Out | 8                           | Data bus output  Data file address            |  |  |  |

| ramwe                | Out        | 8<br>High                   |                                               |  |  |  |

| ramoe                | Out        | High                        | Data file output                              |  |  |  |

| 1411100              | Jul        | 111911                      | enable                                        |  |  |  |

| L                    | l          | I                           | Chabic                                        |  |  |  |

| Name     | Туре | Polarity/<br>Bus Size | Description         |  |

|----------|------|-----------------------|---------------------|--|

|          |      |                       | External Special    |  |

|          |      |                       | Function Registers  |  |

|          |      |                       | interface           |  |

| sfrdatai | I    | 8                     | SFR data bus input  |  |

| sfrdatao | 0    | 8                     | SFR data bus output |  |

| sfraddr  | 0    | 7                     | SFR address         |  |

| sfrwe    | 0    | High                  | SFR write enable    |  |

| sfroe    | 0    | High                  | SFR output enable   |  |

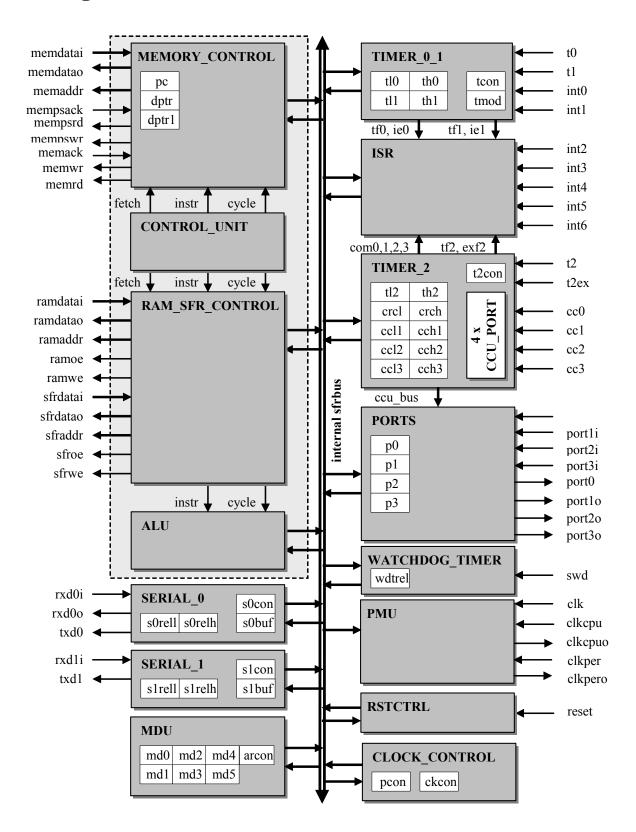

## **Block Diagram**

## **Verification Methods**

The R80515 core's functionality was verified by means of a proprietary hardware modeler. The same stimulus was applied to a hardware model that contained the original Intel 80C31 and Siemens SAB80C537 chips, and the results were compared with the core's simulation outputs.

## **Device Utilization & Performance**

| Supported  | Device   | Utilization |        |             | Performance      |

|------------|----------|-------------|--------|-------------|------------------|

| Family     | Tested   | LEs         | Memory | Memory bits | F <sub>max</sub> |

| Cyclone    | EP1C4-6  | 3696        | 3 M4K  | 10,240      | 38 MHz           |

| Stratix    | EP1S10-5 | 3726        | 3 M4K  | 10,752      | 39 MHz           |

| Stratix-II | EP2S5-3  | 3115        | 3 M4K  | 10,752      | 51 MHz           |

#### Notes:

- 1. Optimized for speed

- 2. Implemented with 256 bytes of RAM and 1KB of ROM

## **Deliverables**

- VHDL or Verilog HDL source code

- Post-synthesis EDIF netlist (netlist license)

- Testbench (self-checking)

- Vectors for testing the core

- Place & route scripts (netlist license)

- Simulation script

- Synthesis script

- Documentation

## **Contact Information**

CAST, Inc.

11 Stonewall Court

Woodcliff Lake, New Jersey 07677 USA

This megafunction developed by the processor experts at Evatronix SA

Copyright © CAST, Inc. 2004, All Rights Reserved. Contents subject to change without notice