# **OKI** Semiconductor

# MS82V32520

# **Preliminary**

This version:

Jul. 2001

524,288-Word × 32-Bit × 2-Bank FIFO-SGRAM

#### **GENERAL DESCRIPTION**

The MS82V32520 is a 32-Mbit system clock synchronous dynamic random access memory. In addition to the conventional random read/write access function, the MS82V32520 provides the automatic row address increment function and automatic bank switching function. Therefore, if once the row and column addresses are set, continuous serial accesses are possible while banks are automatically switched till input of the Precharge command. The MS82V32520 is ideal for digital camera and TV buffer memory applications.

#### **FEATURES**

- 524,288 words  $\times$  32 bits  $\times$  2 banks memory (2,048 rows  $\times$  256 columns  $\times$  32 bits  $\times$  2 banks)

- Single 3.3 V  $\pm 0.3$  V power supply

- LVTTL compatible inputs and outputs

- Programmable burst length (1, 2, 4, 8 and full page)

- Programmable CAS latency (2, 3)

- Automatic row address increment function and automatic bank switching function

- Power Down operation and Clock Suspend operation

- 4,096 refresh cycles/64 ms

- Auto refresh and self refresh capability

- Package:

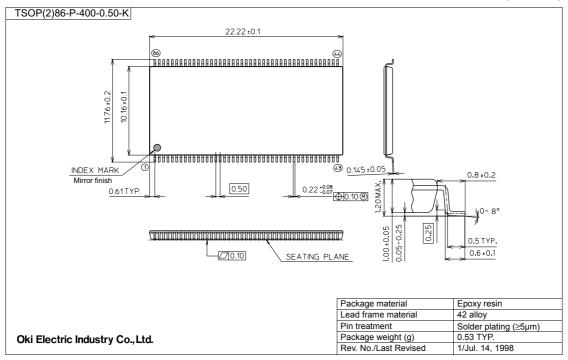

86-pin 400 mil plastic TSOP (II) (TSOP (2) 86-P-400-0.50-K)

(Product : MS82V32520-xxTA) xx indicates speed rank.

#### PRODUCT FAMILY

| Family        | Max. Operating Frequency | Access Time | Package                            |

|---------------|--------------------------|-------------|------------------------------------|

| MS82V32520-75 | 133 MHz                  | 5.5 ns      |                                    |

| MS82V32520-8  | 125 MHz                  | 6 ns        | 86-pin Plastic TSOP (II) (400 mil) |

| MS82V32520-10 | 100 MHz                  | 7 ns        |                                    |

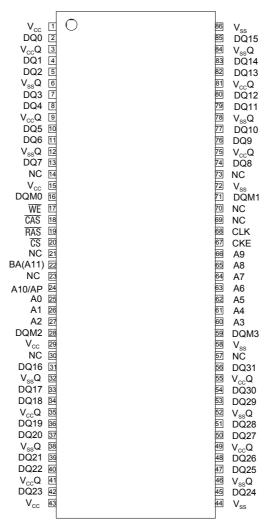

#### PIN CONFIGURATION (TOP VIEW)

86-Pin Plastic TSOP (II) (Type K)

| Pin Name | Function              | Pin Name    | Function              |

|----------|-----------------------|-------------|-----------------------|

| A0 – A10 | Row Address Inputs    | WE          | Write Enable          |

| A0 – A7  | Column Address Inputs | DQM0 – DQM3 | DQ Mask Enable        |

| BA(A11)  | Bank Address          | DQ0 - DQ31  | Data Inputs/outputs   |

| CLK      | System Clock Input    | $V_{CC}$    | Supply Voltage        |

| CKE      | Clock Enable          | $V_{SS}$    | Ground                |

| CS       | Chip Select           | $V_{cc}Q$   | Supply Voltage for DQ |

| RAS      | Row Address Strobe    | $V_{ss}Q$   | Ground for DQ         |

| CAS      | Column Address Strobe | NC          | No Connection         |

Note: The same power supply voltage must be provided to every  $V_{CC}$  pin and  $V_{CC}Q$  pin.

The same GND voltage level must be provided to every  $V_{SS}$  pin and  $V_{SS}Q$  pin.

For the four-bank 64Mb SDRAM, Pin 22 = BA0 and Pin 23 = BA1, and for the two-bank 64Mb SDRAM, Pin 22 = BA.

Therefore, when the MS82V32520 is used in place of a 64Mb SDRAM, care must be taken in bank address control.

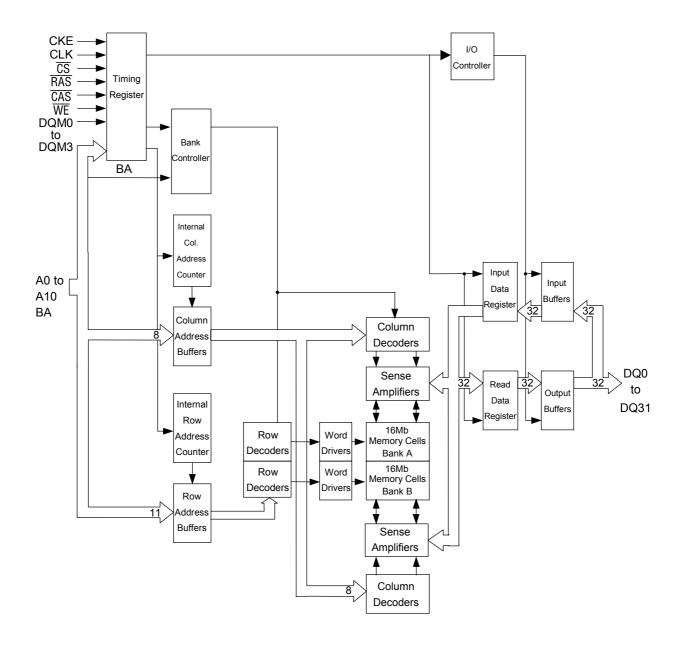

## **BLOCK DIAGRAM**

#### PIN DESCRIPTION

| Fetches all inputs at the "H" edge.                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disables or enables device operation by asserting or deactivating all inputs except CLK, CKE, DQM0, DQM1, DQM2 and DQM3.                                                                                                                                                                                                              |

| Masks system clock to deactivate the subsequent CLK operation.  If CKE is deactivated, system clock will be masked so that the subsequent CLK operation is deactivated. CKE should be asserted at least one cycle prior to a new command.                                                                                             |

| Row & column multiplexed. Row address: RA0 – RA10 Column address: CA0 – CA7                                                                                                                                                                                                                                                           |

| Selects bank to be activated during row address latch time and selects bank for precharge and read/write during column address latch time.  BA = "L": Bank A  BA = "H": Bank B                                                                                                                                                        |

| Functionality depends on the combination. For details, see the function truth table.                                                                                                                                                                                                                                                  |

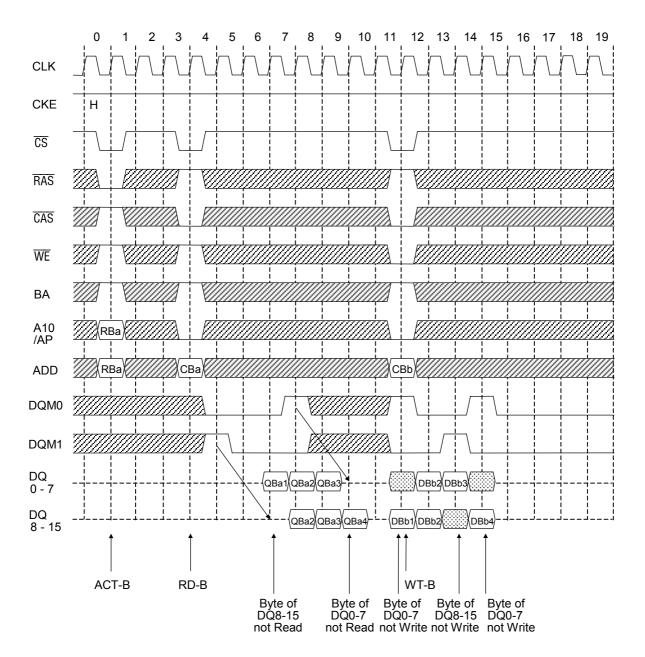

| Masks the read data of two clocks later when DQM0 - DQM3 are set "H" at the "H" edge of the clock signal.  Masks the write data of the same clock when DQM0 - DQM3 are set "H" at the "H" edge of the clock signal.  DQM0 controls DQ0 to DQ7, DQM1 controls DQ8 to DQ15, DQM2 controls DQ16 to DQ23, and DQM3 controls DQ24 to DQ31. |

| Data inputs/outputs are multiplexed on the same pin.                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                       |

<sup>\*</sup>Notes: 1. When  $\overline{\text{CS}}$  is set "High" at a clock transition from "Low" to "High", all inputs except CLK, CKE, DQM0, DQM1, DQM2, and DQM3 are invalid.

2. When issuing an active, read or write command, the bank is selected by BA.

| ВА | Active, read or write |

|----|-----------------------|

| 0  | Bank A                |

| 1  | Bank B                |

3. The auto precharge function is enabled or disabled by the A10/AP input when the read or write command is issued.

| A10/AP | BA | Operation                                                   |

|--------|----|-------------------------------------------------------------|

| 0      | 0  | After the end of burst, bank A holds the active status.     |

| 1      | 0  | After the end of burst, bank A is precharged automatically. |

| 0      | 1  | After the end of burst, bank B holds the active status.     |

| 1      | 1  | After the end of burst, bank B is precharged automatically. |

4. When issuing a precharge command, the bank to be precharged is selected by the A10/AP and BA inputs.

| A10/AP | ВА | Operation                          |

|--------|----|------------------------------------|

| 0      | 0  | Bank A is precharged.              |

| 0      | 1  | Bank B is precharged.              |

| 1      | ×  | Both banks A and B are precharged. |

#### **COMMAND OPERATION**

## Mode Register Set Command ( $\overline{CS}$ , $\overline{RAS}$ , $\overline{CAS}$ , $\overline{WE}$ = "Low")

The MS82V32520 has the mode register that defines the operation mode " $\overline{\text{CAS}}$  Latency, Burst Length, Burst Sequence". The Mode Register Set command should be executed just after the MS82V32520 is powered on. Before entering this command, all banks must be precharged. Next command can be issued after  $t_{RSC}$ .

The Auto Refresh command performs refresh automatically by the address counter. The refresh operation must be performed 4,096 times within 64 ms and the next command can be issued after  $t_{RC}$  from last Auto Refresh command. Before entering this command, all banks must be precharged.

The self refresh operation continues after the Self Refresh Entry command is entered, with CKE level left "low". This operation terminates by making CKE level "high". The self refresh operation is performed automatically by the internal address counter on the MS82V32520 chip.

In self refresh mode, no external refresh control is required. Before entering self refresh mode, all banks must be precharged. Next command can be issued after  $t_{RC}$ .

The Single Bank Precharge command triggers bank precharge operation. Precharge bank is selected by BA.

All Banks Precharge Command (

$$\overline{CS}$$

,  $\overline{RAS}$ ,  $\overline{WE}$  = "Low",  $\overline{CAS}$ , A10/AP = "High")

The All Bank Precharge command triggers precharge of both of the banks A and B. If this command is executed during special bank active mode, the special bank active mode is terminated.

Bank Active Command (

$$\overline{CS}$$

,  $\overline{RAS}$  = "Low",  $\overline{CAS}$ ,  $\overline{WE}$  = "High")

The Bank Active command activates the bank selected by BA. The Bank Active command corresponds to conventional DRAM's  $\overline{RAS}$  falling operation. Row addresses "A0 – A10 and BA" are strobed.

The Write command is required to begin burst write operation. Then burst access initial bit column address is strobed.

Write with Auto Precharge Command (

$$\overline{CS}$$

,  $\overline{CAS}$ ,  $\overline{WE}$  = "Low",  $\overline{RAS}$ , A10/AP = "High")

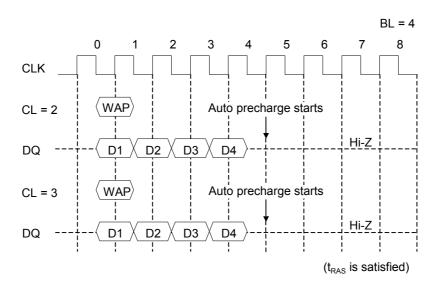

The Write with Auto Precharge command is required to begin burst write operation with automatic precharge after the burst write. Any command that interrupts this operation cannot be issued.

Read Command (

$$\overline{CS}$$

,  $\overline{CAS}$ , A10/AP = "Low",  $\overline{RAS}$ ,  $\overline{WE}$  = "High")

The Read command is required to begin burst read operation. Then burst access initial bit column address is strobed.

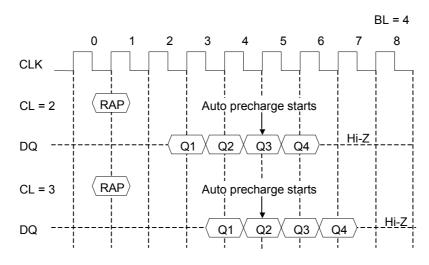

## Read with Auto Prechaege Command (CS, CAS = "Low", RAS, WE, A10/AP = "High")

The Read with Auto Precharge command is required to begin burst read operation with auto precharge after the burst read. Any command that interrupts this operation cannot be issued.

## No Operation Command ( $\overline{CS}$ = "Low", $\overline{RAS}$ , $\overline{CAS}$ , $\overline{WE}$ = "High")

The No Operation command does not trigger any operation.

## Device Deselect Command ( $\overline{CS}$ = "High")

The Device Deselect command disables the RAS, CAS, WE and Address input. This command does not trigger any operation.

#### Data Write/Output Enable Command (DQMi = "Low")

The Data Write/Output Enable command enables DQ0 - DQ31 in read or write. The each DQM0, 1, 2 and 3 corresponds to DQ0 - DQ7, DQ8 - DQ15, DQ16 - DQ23 and DQ24 - DQ31 respectively.

#### Data Mask/Output Disable Command (DQMi = "High")

The Data Mask/Output Disable command disables DQ0 - DQ31 in read or write. In read cycle output buffers are disabled after 2 clocks . In write cycle input buffers are disabled at the same clock. The each DQM0, 1, 2 and 3 corresponds to DQ0 - DQ7, DQ8 - DQ15, DQ16 - DQ23 and DQ24 - DQ31 respectively.

## Burst Stop Command ( $\overline{CS}$ , $\overline{WE}$ = "Low", $\overline{RAS}$ , $\overline{CAS}$ = "High")

The Burst Stop command stops burst access. After the Burst Stop command is entered, the output buffer goes into high impedance state.

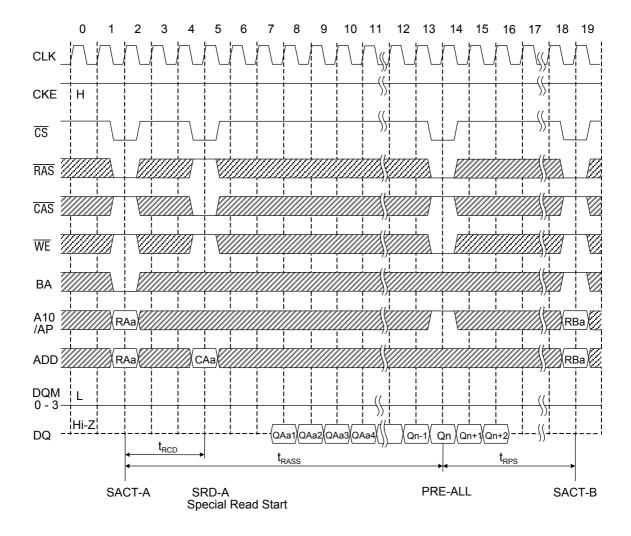

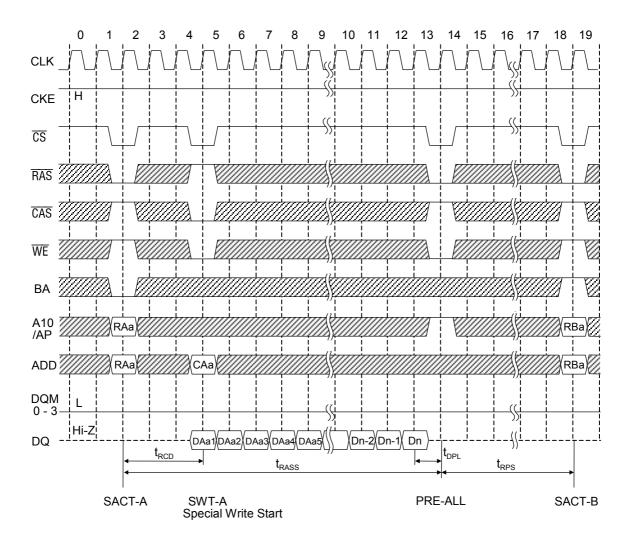

#### SPECIAL READ/WRITE OPERATION

The special read or write operation is activated by executing the Read or Write command after selecting the special page mode with the Mode Register command.

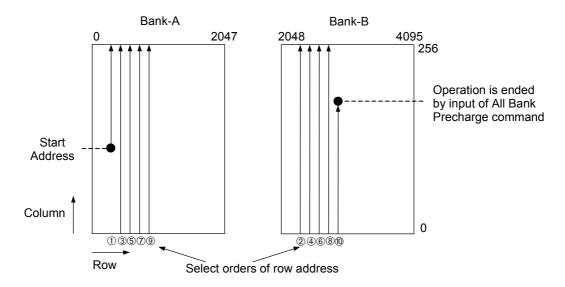

The automatic bank switching and automatic row address increment operations are activated by executing the Bank Active command during Special Page mode, and the serial access starts from the address fetched with the Read or Write command. The burst operation starts from the start address toward the column. When the last column address is reached, the bank is automatically switched and the row address is also automatically incremented and the serial access continues from the start column address. The automatic bank switching and automatic row address increment operations continue until the All Bank Precharge command is executed each time the last column address is reached.

Since the bank switching and row address increment are automatically made during the special read or write operation, the row address proceeds as shown in the following figure.

(1) When a select row address is n (n<2048),

$$n \rightarrow n + 2048 \rightarrow n + 1 \rightarrow n + 1 + 2048 \rightarrow n + 2 \rightarrow n + 2 + 2048 \cdots$$

(2) When a select row address is m (m>2047),

$$m \rightarrow m + 1 - 2048 \rightarrow m + 1 \rightarrow m + 2 - 2048 \rightarrow m + 2 \rightarrow m + 3 - 2048 \cdots$$

## TRUTH TABLE

# **Command Truth Table**

| Function                  | 00 | <u> </u> | 040 | WE | Address |         |              |  |

|---------------------------|----|----------|-----|----|---------|---------|--------------|--|

| Function                  | CS | RAS      | CAS | WE | ВА      | A10/AP  | A9 – A0      |  |

| Device Deselect           | Н  | ×        | ×   | ×  | ×       | ×       | ×            |  |

| No Operation              | L  | Н        | Н   | Н  | ×       | ×       | ×            |  |

| Mode Register Set         | L  | L        | L   | L  |         | OP. COD | E            |  |

| Auto Refresh              | L  | L        | L   | Н  | ×       | ×       | ×            |  |

| Bank Activate             | L  | L        | Н   | Н  | BA      | RA      |              |  |

| Read                      | L  | Н        | L   | Н  | BA      | L       | CA (A7 – A0) |  |

| Read with Auto Precharge  | L  | Н        | L   | Н  | ВА      | Н       | CA (A7 – A0) |  |

| Write                     | L  | Н        | L   | L  | ВА      | L       | CA (A7 – A0) |  |

| Write with Auto Precharge | L  | Н        | L   | L  | ВА      | Н       | CA (A7 – A0) |  |

| Precharge Select Bank     | L  | L        | Н   | L  | ВА      | L       | ×            |  |

| Precharge All Banks       | L  | L        | Н   | L  | ×       | Н       | ×            |  |

| Burst Stop                | L  | Н        | Н   | L  | ×       | ×       | ×            |  |

# **DQM Truth Table**

| Function                 | DQMi |

|--------------------------|------|

| Data Write/Output Enable | L    |

| Data Mask/Output Disable | Н    |

# **Function Truth Table (1/3)**

| Current State   | CS | RAS | CAS | WE | ВА | Address | Action                                     | Note<br>Note |

|-----------------|----|-----|-----|----|----|---------|--------------------------------------------|--------------|

| Idle            | Н  | ×   | ×   | ×  | ×  | ×       | NOP                                        | 1400         |

| 10.0            | L  | Н   | Н   | Н  | ×  | ×       | NOP                                        |              |

|                 | L  | Н   | Н   | L  | BA | ×       | ILLEGAL                                    | 2            |

|                 | L  | Н   | L   | ×  | BA | CA, A10 | ILLEGAL                                    | 2            |

|                 | L  | L   | Н   | Н  | BA | RA      | Row Active                                 |              |

|                 | L  | L   | L   | L  | L  | Op-Code | Mode Register Write                        |              |

|                 | L  | L   | Н   | L  | ВА | A10     | NOP                                        | 4            |

|                 | L  | L   | L   | Н  | ×  | ×       | Auto Refresh/Self refresh                  | 5            |

| Active (ACT)    | Н  | ×   | ×   | ×  | ×  | ×       | NOP                                        |              |

|                 | L  | Н   | Н   | ×  | ×  | ×       | NOP                                        |              |

|                 | L  | Н   | L   | Н  | ВА | CA, A10 | Read                                       |              |

|                 | L  | Н   | L   | L  | ВА | CA, A10 | Write                                      |              |

|                 | L  | L   | Н   | Н  | ВА | RA      | ILLEGAL                                    | 2            |

|                 | L  | L   | Н   | L  | ВА | A10     | Precharge                                  |              |

|                 | L  | L   | L   | ×  | ×  | ×       | ILLEGAL                                    |              |

| Active (Special | Н  | ×   | ×   | ×  | ×  | ×       | NOP                                        |              |

| Page Mode)      | L  | Н   | Н   | ×  | ×  | ×       | NOP                                        |              |

| (SACT)          | L  | Н   | L   | Н  | ВА | CA      | Serial Read                                |              |

|                 | L  | Н   | L   | L  | ВА | CA      | Serial Write                               |              |

|                 | L  | L   | Н   | Н  | ВА | RA      | ILLEGAL                                    |              |

|                 | L  | L   | Н   | L  | ВА | A10: L  | ILLEGAL                                    |              |

|                 | L  | L   | Н   | L  | ВА | A10: H  | Precharge                                  |              |

|                 | L  | L   | L   | ×  | ×  | ×       | ILLEGAL                                    |              |

| Read (RD)       | Н  | ×   | ×   | ×  | ×  | ×       | NOP (Continue Row Active after Burst ends) |              |

|                 | L  | Н   | Н   | Ι  | ×  | ×       | NOP (Continue Row Active after Burst ends) |              |

|                 | L  | Н   | Н   | Ш  | ×  | ×       | Burst Stop → Row Active                    |              |

|                 | L  | Н   | L   | Ι  | ВА | CA, A10 | Term Burst, new Read                       | 3            |

|                 | L  | Н   | L   | L  | ВА | CA, A10 | Term Burst, start Write                    | 3            |

|                 | L  | L   | Н   | Ι  | ВА | RA      | ILLEGAL                                    | 2            |

|                 | L  | L   | Н   | L  | ВА | A10     | Term Burst, execute Precharge              |              |

|                 | L  | L   | L   | ×  | ×  | ×       | ILLEGAL                                    |              |

| Write (WT)      | Н  | ×   | ×   | ×  | ×  | ×       | NOP (Continue Row Active after Burst ends) |              |

|                 | L  | Н   | Н   | Н  | ×  | ×       | NOP (Continue Row Active after Burst ends) |              |

|                 | L  | Н   | Н   | L  | ×  | ×       | Burst Stop → Row Active                    |              |

|                 | L  | Н   | L   | Н  | ВА | CA, A10 | Term Burst, start Read                     | 3            |

|                 | L  | Н   | L   | L  | ВА | CA, A10 | Term Burst, new Write                      | 3            |

|                 | L  | L   | Н   | Н  | ВА | RA      | ILLEGAL                                    | 2            |

|                 | L  | L   | Н   | L  | ВА | A10     | Term Burst, execute Precharge              | 3            |

|                 | L  | L   | L   | ×  | ×  | ×       | ILLEGAL                                    |              |

# **Function Truth Table (2/3)**

| N | ote |

|---|-----|

|---|-----|

| Current State   | CS | RAS | CAS | WE | ВА | Address | Action                                          | Note 1 |

|-----------------|----|-----|-----|----|----|---------|-------------------------------------------------|--------|

| Read with Auto  | Н  | ×   | ×   | ×  | ×  | ×       | NOP (Continue Burst to End and enter Precharge) |        |

| Precharge       | L  | Н   | Н   | Н  | ×  | ×       | NOP (Continue Burst to End and enter Precharge) |        |

| (RAP)           | L  | Н   | Н   | L  | ×  | ×       | ILLEGAL                                         |        |

|                 | L  | Н   | L   | Н  | BA | CA, A10 | ILLEGAL                                         |        |

|                 | L  | Н   | L   | L  | ВА | CA, A10 | ILLEGAL                                         |        |

|                 | L  | L   | Н   | Н  | ВА | RA      | ILLEGAL                                         | 2      |

|                 | L  | L   | Н   | L  | ВА | A10     | ILLEGAL                                         | 2      |

|                 | L  | L   | L   | ×  | ×  | ×       | ILLEGAL                                         |        |

| Write with Auto | Н  | ×   | ×   | ×  | ×  | ×       | NOP (Continue Burst to End and enter Precharge) |        |

| Precharge       | L  | Н   | Н   | Н  | ×  | ×       | NOP (Continue Burst to End and enter Precharge) |        |

| (WAP)           | L  | Н   | Н   | L  | ×  | ×       | ILLEGAL                                         |        |

|                 | L  | Н   | L   | Н  | ВА | CA, A10 | ILLEGAL                                         |        |

|                 | L  | Н   | L   | L  | ВА | CA, A10 | ILLEGAL                                         |        |

|                 | L  | L   | Н   | Н  | ВА | RA      | ILLEGAL                                         | 2      |

|                 | L  | L   | Н   | L  | ВА | A10     | ILLEGAL                                         | 2      |

|                 | L  | L   | L   | ×  | ×  | ×       | ILLEGAL                                         |        |

| Read (Special   | Н  | ×   | ×   | ×  | ×  | ×       | NOP (Continue serial read)                      |        |

| Page Mode)      | ┙  | Н   | Н   | Н  | ×  | ×       | NOP (Continue serial read)                      |        |

| (SRD)           | L  | Н   | Н   | L  | ×  | ×       | ILLEGAL                                         |        |

|                 | L  | Н   | L   | ×  | ВА | CA      | ILLEGAL                                         |        |

|                 | ┙  | L   | Н   | Н  | ВА | RA      | ILLEGAL                                         |        |

|                 | L  | L   | Н   | L  | ВА | A10: L  | ILLEGAL                                         |        |

|                 | L  | L   | Н   | L  | ВА | A10: H  | Precharging                                     |        |

|                 | L  | L   | L   | ×  | ×  | ×       | ILLEGAL                                         |        |

| Write (Special  | Н  | ×   | ×   | ×  | ×  | ×       | NOP (Continue serial write)                     |        |

| Page Mode)      | L  | Н   | Н   | Н  | ×  | ×       | NOP (Continue serial write)                     |        |

| (SWT)           | L  | Н   | Н   | L  | ×  | ×       | ILLEGAL                                         |        |

|                 | L  | Н   | L   | ×  | BA | CA      | ILLEGAL                                         |        |

|                 | L  | L   | Н   | Н  | BA | RA      | ILLEGAL                                         |        |

|                 | L  | L   | Н   | L  | BA | A10: L  | ILLEGAL                                         |        |

|                 | L  | L   | Н   | L  | BA | A10: H  | Precharging                                     |        |

|                 | L  | L   | L   | ×  | ×  | ×       | ILLEGAL                                         |        |

| Precharging     | Н  | ×   | ×   | ×  | ×  | ×       | $NOP \rightarrow Idle after t_{RP}$             |        |

| (PRE)           | L  | Н   | Н   | Н  | ×  | ×       | $NOP \rightarrow Idle after t_{RP}$             |        |

|                 | L  | Н   | Н   | L  | BA | ×       | ILLEGAL                                         | 2      |

|                 | L  | Н   | L   | ×  | ВА | CA      | ILLEGAL                                         | 2      |

|                 | L  | L   | Н   | Н  | BA | RA      | ILLEGAL                                         | 2      |

|                 | L  | L   | Н   | L  | BA | A10     | NOP                                             | 4      |

|                 | L  | L   | L   | ×  | ×  | ×       | ILLEGAL                                         |        |

## **Function Truth Table (3/3)**

Note 1

| Current State | CS | RAS | CAS | WE | ВА | Address | Action                            | Note |

|---------------|----|-----|-----|----|----|---------|-----------------------------------|------|

| Refreshing    | Н  | ×   | ×   | ×  | ×  | ×       | $NOP \to Idle \; after \; t_{RC}$ |      |

| (REF)         | L  | Н   | Н   | Н  | ×  | ×       | $NOP \to Idle \; after \; t_{RC}$ |      |

|               | L  | Н   | Н   | L  | BA | ×       | ILLEGAL                           |      |

|               | L  | Н   | L   | ×  | ВА | CA      | ILLEGAL                           |      |

|               | L  | L   | Н   | Н  | ВА | RA      | ILLEGAL                           |      |

|               | L  | L   | Н   | L  | BA | A10     | ILLEGAL                           |      |

|               | L  | L   | L   | ×  | ×  | ×       | ILLEGAL                           |      |

#### **ABBREVIATIONS**

BA = Bank Address

RA = Row Address

CA = Column Address

NOP = No Operation command

Notes: 1. All inputs are enabled when CKE is set high for at least 1 cycle prior to the inputs.

- 2. Illegal to bank in specified state, but may be legal in some cases depending on the state of bank selection.

- To avoid bus contention, satisfy t<sub>CCD</sub> and t<sub>DPL</sub>.

NOP to bank precharging or in idle state. Precharges activated bank by BA or A10/AP.

- 5. Illegal if any bank is not idle.

## **Function Truth Table for CKE**

| Current State (n) | CKEn-1 | CKEn | CS | RAS | CAS | WE | Address | Action                              | Note |

|-------------------|--------|------|----|-----|-----|----|---------|-------------------------------------|------|

| Self Refresh      | Н      | ×    | ×  | ×   | ×   | ×  | ×       | INVALID                             |      |

| (SREF)            | L      | Н    | Н  | ×   | ×   | ×  | ×       | Exit Self Refresh → ABI             |      |

|                   | L      | Н    | L  | Н   | Н   | Н  | ×       | Exit Self Refresh $\rightarrow$ ABI |      |

|                   | L      | Н    | L  | Н   | Н   | L  | ×       | ILLEGAL                             |      |

|                   | L      | Н    | L  | Н   | L   | ×  | ×       | ILLEGAL                             |      |

|                   | L      | Н    | L  | L   | ×   | ×  | ×       | ILLEGAL                             |      |

|                   | L      | L    | ×  | ×   | ×   | ×  | ×       | NOP (Maintain Self Refresh)         |      |

| Power Down (PD)   | Н      | ×    | ×  | ×   | ×   | ×  | ×       | INVALID                             |      |

|                   | L      | Н    | Н  | ×   | ×   | ×  | ×       | Exit Self Refresh $\rightarrow$ ABI |      |

|                   | L      | Н    | L  | Н   | Н   | Н  | ×       | Exit Self Refresh $\rightarrow$ ABI |      |

|                   | L      | Н    | L  | Н   | Н   | L  | ×       | ILLEGAL                             |      |

|                   | L      | Н    | L  | Н   | Ш   | ×  | ×       | ILLEGAL                             |      |

|                   | L      | Н    | L  | L   | ×   | ×  | ×       | ILLEGAL                             |      |

|                   | L      | L    | ×  | ×   | ×   | ×  | ×       | NOP (Continue power down mode)      |      |

| All Banks Idle    | Н      | Н    | ×  | ×   | ×   | ×  | ×       | Refer to Truth Table                | 6    |

| (ABI)             | Н      | L    | Н  | ×   | ×   | ×  | ×       | Enter Power Down                    | 6    |

|                   | Н      | L    | L  | Н   | Н   | Н  | ×       | Enter Power Down                    | 6    |

|                   | Н      | L    | L  | Н   | Н   | L  | ×       | ILLEGAL                             | 6    |

|                   | Н      | L    | L  | Н   | L   | ×  | ×       | ILLEGAL                             | 6    |

|                   | Н      | L    | L  | L   | Н   | L  | ×       | ILLEGAL                             | 6    |

|                   | Н      | L    | L  | L   | Ш   | Η  | ×       | Enter Self Refresh                  | 6    |

|                   | Н      | L    | L  | L   | L   | L  | ×       | ILLEGAL                             | 6    |

|                   | L      | L    | ×  | ×   | ×   | ×  | ×       | NOP                                 | 6    |

| Any State Other   | Н      | Н    | ×  | ×   | ×   | ×  | ×       | Refer to Truth Table                |      |

| than Listed Above | Н      | L    | ×  | ×   | ×   | ×  | ×       | Begin Clock Suspend Next Cycle      |      |

|                   | L      | Н    | ×  | ×   | ×   | ×  | ×       | Enable Clock of Next Cycle          |      |

|                   | L      | L    | ×  | ×   | ×   | ×  | ×       | Continue Clock Suspension           |      |

Note: 6. Power-down and self refresh can be entered only when all the banks are in an idle state.

#### **Mode Set Address Keys**

|      | Operation Code CAS Latency |                    |    | ency | В  | urst Type | Burst Length |            |    |    |    |              |          |

|------|----------------------------|--------------------|----|------|----|-----------|--------------|------------|----|----|----|--------------|----------|

| A8   | A7                         | TM                 | A6 | A5   | A4 | CL        | А3           | ВТ         | A2 | A1 | A0 | BT = 0       | BT = 1   |

| 0    | 0                          | Mode Setting       | 0  | 0    | 0  | Reserved  | 0            | Sequential | 0  | 0  | 0  | 1            | Reserved |

| 0    | 1                          | Vender             | 0  | 0    | 1  | Reserved  | 1            | Interleave | 0  | 0  | 1  | 2            | Reserved |

| 1    | 0                          | Use                | 0  | 1    | 0  | 2         |              |            | 0  | 1  | 0  | 4            | 4        |

| 1    | 1                          | Only               | 0  | 1    | 1  | 3         |              |            | 0  | 1  | 1  | 8            | 8        |

| Writ | e Bu                       | rst Length *Note 1 | 1  | 0    | 0  | Reserved  |              |            | 1  | 0  | 0  | Reserved     | Reserved |

| A9   |                            | Length             | 1  | 0    | 1  | Reserved  |              |            | 1  | 0  | 1  | Reserved     | Reserved |

| 0    |                            | Burst              | 1  | 1    | 0  | Reserved  |              |            | 1  | 1  | 0  | Special page | Reserved |

| 1    |                            | Single Bit         | 1  | 1    | 1  | Reserved  |              |            | 1  | 1  | 1  | Full Page    | Reserved |

<sup>\*</sup>Note 1: To select Special Page mode, set A9 to "L".

The write burst length during Special Page mode is set only for Burst.

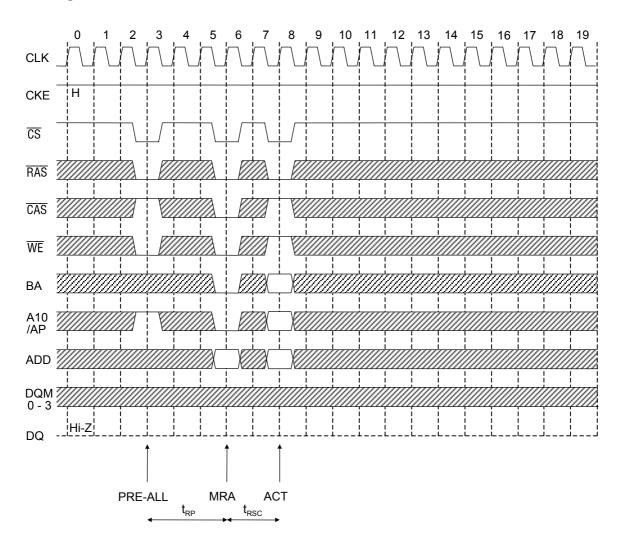

# POWER ON SEQUENCE

- 1. With CKE = "H", DQM = "H" and the other inputs in NOP state, turn on the power supply and start the system clock.

- 2. After the  $V_{\text{CC}}$  voltage has reached the specified level, pause for 200  $\mu s$  or more with the input kept in NOP state.

- 3. Issue the precharge all bank command.

- 4. Apply an Auto-refresh 8 or more times.

- 5. Enter the mode register command.

# **Burst Length and Sequence**

## BL = 2

| Starting Address (column address A0, binary) | Sequential Type | Interleave Type |

|----------------------------------------------|-----------------|-----------------|

| 0                                            | 0, 1            | Not supported   |

| 1                                            | 1, 0            | Not supported   |

## BL = 4

| Starting Address (column address A1, A0, binary) | Sequential Type | Interleave Type |

|--------------------------------------------------|-----------------|-----------------|

| 00                                               | 0, 1, 2, 3      | 0, 1, 2, 3      |

| 01                                               | 1, 2, 3, 0      | 1, 0, 3, 2      |

| 10                                               | 2, 3, 0, 1      | 2, 3, 0, 1      |

| 11                                               | 3, 0, 1, 2      | 3, 2, 1, 0      |

# BL = 8

| Starting Address<br>(column address A2 - A0, binary) | Sequential Type        | Interleave Type        |

|------------------------------------------------------|------------------------|------------------------|

| 000                                                  | 0, 1, 2, 3, 4, 5, 6, 7 | 0, 1, 2, 3, 4, 5, 6, 7 |

| 001                                                  | 1, 2, 3, 4, 5, 6, 7, 0 | 1, 0, 3, 2, 5, 4, 7, 6 |

| 010                                                  | 2, 3, 4, 5, 6, 7, 0, 1 | 2, 3, 0, 1, 6, 7, 4, 5 |

| 011                                                  | 3, 4, 5, 6, 7, 0, 1, 2 | 3, 2, 1, 0, 7, 6, 5, 4 |

| 100                                                  | 4, 5, 6, 7, 0, 1, 2, 3 | 4, 5, 6, 7, 0, 1, 2, 3 |

| 101                                                  | 5, 6, 7, 0, 1, 2, 3, 4 | 5, 4, 7, 6, 1, 0, 3, 2 |

| 110                                                  | 6, 7, 0, 1, 2, 3, 4, 5 | 6, 7, 4, 5, 2, 3, 0, 1 |

| 111                                                  | 7, 0, 1, 2, 3, 4, 5, 6 | 7, 6, 5, 4, 3, 2, 1, 0 |

BL = Special, Full : Sequential only

## READ/WRITE COMMAND INTERVAL

## **Read to Read Command Interval**

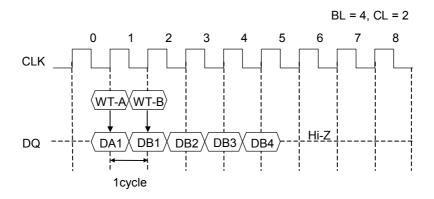

## Write to Write Command Interval

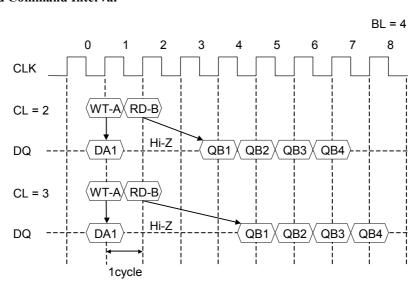

## Write to Read Command Interval

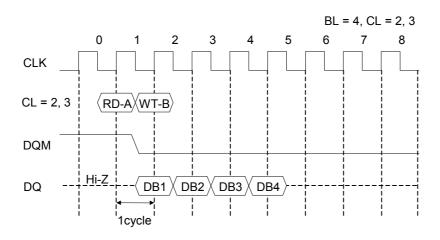

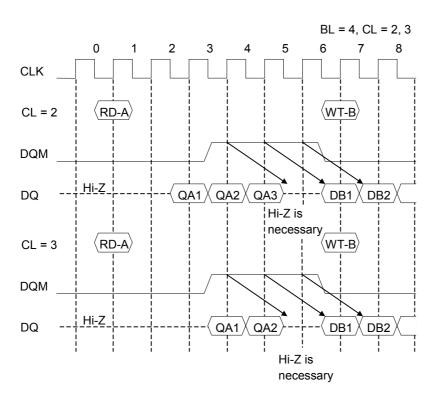

## **Read to Write Command Interval**

## **BURST TERMINATION**

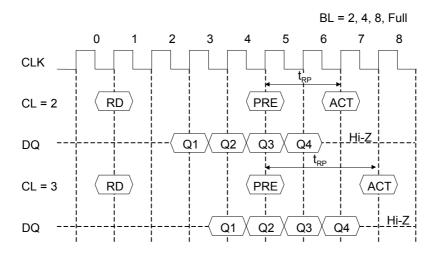

## **Burst Read Termination by Precharging in READ Cycle**

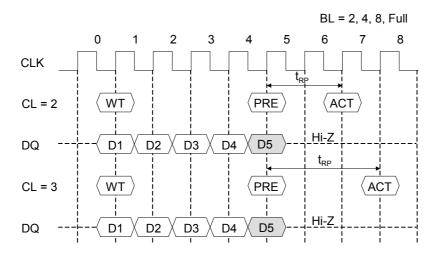

## **Burst Read Termination by Precharging in WRITE Cycle**

Note: D5 data will not be written

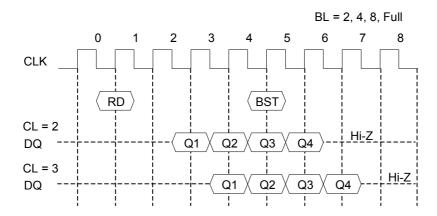

# **Read Burst Stop Command**

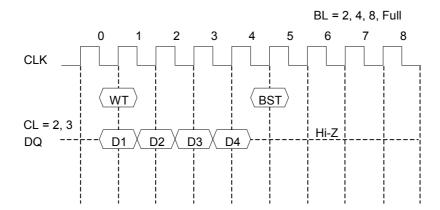

## **Write Burst Stop Command**

## **AUTO PRECHARGE**

## Read with Auto Precharge

$(t_{\text{RAS}} \text{ is satisfied})$

## Write with Auto Precharge

## **ELECTRICAL CHARACTERISTICS**

## **Absolute Maximum Ratings**

| Parameter                                   | Symbol            | Rating                           | Unit |

|---------------------------------------------|-------------------|----------------------------------|------|

| Voltage on Power Supply Pin Relative to GND | V <sub>cc</sub>   | -0.5 to 4.6                      | V    |

| Voltage on Input Pin Relative to GND        | $V_{IN}, V_{OUT}$ | $-0.5$ to $V_{CC} + 0.5 \le 4.6$ | V    |

| Short Circuit Output Current                | Ios               | 50                               | mA   |

| Power Dissipation                           | P <sub>D</sub> *  | 1                                | W    |

| Operating Temperature                       | T <sub>opr</sub>  | 0 to 70                          | °C   |

| Storage Temperature                         | T <sub>stg</sub>  | -55 to 150                       | °C   |

<sup>\*:</sup> Ta = 25 °C

# **Recommended Operating Conditions**

$(Ta = 0 \text{ to } 70^{\circ}C)$

| Parameter            | Symbol          | Min. | Тур. | Max.                  | Unit |

|----------------------|-----------------|------|------|-----------------------|------|

| Dowar Supply Voltage | V <sub>cc</sub> | 3.0  | 3.3  | 3.6                   | V    |

| Power Supply Voltage | V <sub>ss</sub> | 0    | 0    | 0                     | V    |

| Input High Voltage   | V <sub>IH</sub> | 2.0  | _    | V <sub>CC</sub> + 0.3 | V    |

| Input Low Voltage    | V <sub>IL</sub> | -0.3 | _    | 0.8                   | V    |

## Capacitance

$(V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}, \text{ Ta} = 25^{\circ}\text{C}, \text{ f} = 1 \text{ MHz})$

| Parameter                                                                                                                                         | Symbol           | Min. | Max. | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------|------|

| Input Capacitance (A0 – A10, BA)                                                                                                                  | C <sub>IN1</sub> | _    | 5    | pF   |

| Input Capacitance<br>(CLK, CKE, $\overline{\text{CS}}$ , $\overline{\text{RAS}}$ , $\overline{\text{CAS}}$ , $\overline{\text{WE}}$ DQM 0 – DQM3) | C <sub>IN2</sub> | _    | 5    | pF   |

| Output Capacitance<br>(DQ0 – DQ31)                                                                                                                | C <sub>OUT</sub> | _    | 6    | pF   |

## **DC** Characteristics

|                                              | 0 1 1                                                 |                       | Condition                                                                                                                                      | MS82V32520-75 |      | MS82V32520-8 |      | MS82V32520-10 |      | 11.20 | N1.1. |

|----------------------------------------------|-------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|--------------|------|---------------|------|-------|-------|

| Parameter                                    | Symbol                                                | CKE                   | Other                                                                                                                                          | Min.          | Max. | Min.         | Max. | Min.          | Max. | Unit  | Note  |

| Output High Voltage                          | V <sub>OH</sub>                                       | _                     | I <sub>OH</sub> = -2.0 mA                                                                                                                      | 2.4           | _    | 2.4          | _    | 2.4           | _    | V     |       |

| Output Low Voltage                           | V <sub>OL</sub>                                       | _                     | I <sub>OL</sub> = 2.0 mA                                                                                                                       | -             | 0.4  | _            | 0.4  | _             | 0.4  | V     |       |

| Input Leakage Current                        | I <sub>LI</sub>                                       | _                     | 1                                                                                                                                              | -10           | 10   | -10          | 10   | -10           | 10   | μΑ    |       |

| Output Leakage Current                       | I <sub>LO</sub>                                       | _                     | 1                                                                                                                                              | -10           | 10   | -10          | 10   | -10           | 10   | μΑ    |       |

| Operating Current<br>(1 Bank)                | I <sub>CC1</sub>                                      | CKE ≥ V <sub>IH</sub> | $\begin{aligned} &t_{\text{CK}} = t_{\text{CK}}  \text{min.} \\ &t_{\text{RC}} = t_{\text{RC}}  \text{min.} \\ &\text{No Burst} \end{aligned}$ | ı             | 200  | _            | 190  | _             | 180  | mA    | 1, 2  |

| Propherae Standby Current                    | I <sub>CC2P</sub>                                     | CKE ≤ V <sub>IL</sub> | $t_{CK} = t_{CK} min.$                                                                                                                         | 1             | 2    | _            | 2    | _             | 2    | mA    | 3     |

| Precharge Standby Current in Power Down Mode | I <sub>CC2PS</sub>                                    | CKE ≤ V <sub>IL</sub> | $CLK \le V_{IL}$ $t_{CK} = \infty$                                                                                                             |               | 2    | _            | 2    | _             | 2    | mA    | 2     |

| Precharge Standby Current                    | I <sub>CC2N</sub>                                     | CKE ≥ V <sub>IH</sub> | $\overline{\text{CS}} \ge V_{\text{IH}}$ $t_{\text{CK}} = t_{\text{CK}} \min$ .                                                                |               | 40   | _            | 40   | _             | 40   | mA    | 2     |

| in Non Power Down Mode                       | I <sub>CC2NS</sub>                                    | CKE ≥ V <sub>IH</sub> | $CLK \le V_{IL}$ $t_{CK} = \infty$                                                                                                             | ı             | 20   |              | 20   |               | 20   | mA    |       |

| Active Standby Current in                    | I <sub>CC3P</sub>                                     | $CKE \le V_{IL}$      | $t_{CK} = t_{CK} min.$                                                                                                                         |               | 3    | _            | 3    | _             | 3    | mΑ    | 3     |

| Power Down Mode                              | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 3                     | mA                                                                                                                                             | 3             |      |              |      |               |      |       |       |

| Active Standby Current in                    | I <sub>CC3N</sub>                                     | CKE ≥ V <sub>IH</sub> |                                                                                                                                                | 1             | 50   | _            | 50   | _             | 50   | mA    | 3     |

| Non Power Down Mode                          | I <sub>CC3NS</sub>                                    | CKE ≥ V <sub>IH</sub> |                                                                                                                                                | ı             | 30   | _            | 30   | _             | 30   | mA    | 3     |

| Operating Current (Burst Mode)               | I <sub>CC4</sub>                                      | CKE ≥ V <sub>IH</sub> | $t_{CK} = t_{CK} min.$                                                                                                                         | _             | 240  | _            | 220  | _             | 200  | mA    | 2     |

| Refresh Current                              | I <sub>CC5</sub>                                      | $CKE \ge V_{IH}$      | $t_{RC} \ge t_{RC} min.$                                                                                                                       | _             | 200  | _            | 190  | _             | 180  | mA    |       |

| Self Refresh Current                         | I <sub>CC6</sub>                                      | $CKE \le 0.2V$        |                                                                                                                                                |               | 3    | _            | 3    | _             | 3    | mΑ    |       |

Notes 1. The maximum value of power supply current is obtained with the output open.

2. Address and data are changed only one time during one cycle.

3. Address and data are changed only one time during two cycles.

## **AC Characteristics**

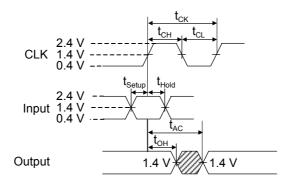

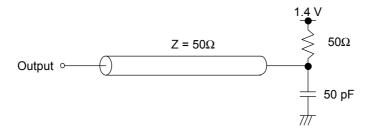

#### Test conditions

- AC measurements assume  $t_T$  = 1 ns. Reference level for measuring timing of input signals is 1.4 V. Transition times are measured between  $V_{IH}$  and

- If  $t_T$  is longer than 1 ns, reference level for measuring timing of input signals is  $V_{\rm IH\,(MIN.)}$  and  $V_{\rm IL\,(MAX)}$ .

An access time is measured at 1.4 V.

- Input levels at the AC testing are 2.4 V/0.4 V.

# **Synchronous Characteristics**

|                                            |                 |                  | MS82V3 | 32520-75 | MS82V | 32520-8 | MS82V32520-10 |      | Unit | N1.1. |

|--------------------------------------------|-----------------|------------------|--------|----------|-------|---------|---------------|------|------|-------|

| Paramet                                    | er              | Symbol           | Min.   | Max.     | Min.  | Max.    | Min.          | Max. | Unit | Note  |

| Clock Cyala Tima                           | CAS Latency = 3 | t <sub>CK3</sub> | 7.5    | _        | 8     | _       | 10            | _    | ns   |       |

| Clock Cycle Time                           | CAS Latency = 2 | t <sub>CK2</sub> | 12     | _        | 12    | _       | 15            | _    | ns   |       |

| Access Time from CLK                       | CAS Latency = 3 | t <sub>AC3</sub> | _      | 5.5      | _     | 6       | _             | 7    | ns   | 1     |

| Access Time Hom CLK                        | CAS Latency = 2 | t <sub>AC2</sub> | _      | 8        | _     | 8       | _             | 9    | ns   | 1     |

| CLK High Level Width                       |                 | t <sub>CH</sub>  | 3      | _        | 3     |         | 3.5           |      | ns   |       |

| CLK Low Level Width                        |                 | t <sub>CL</sub>  | 3      | _        | 3     | _       | 3.5           |      | ns   |       |

| Data-out Hold Time                         |                 | t <sub>oh</sub>  | 2.5    | _        | 2.5   | _       | 2.5           | _    | ns   |       |

| Data-out Low-impedance Time                |                 | t <sub>LZ</sub>  | 0      | _        | 0     | _       | 0             | _    | ns   |       |

| Data-out High-impedance Time               |                 | t <sub>HZ</sub>  | _      | 5.5      | _     | 6       | _             | 7    | ns   |       |

| Data-in Setup Time                         |                 | t <sub>DS</sub>  | 2.5    | _        | 2.5   | _       | 2.5           | _    | ns   |       |

| Data-in Hold Time                          |                 | t <sub>DH</sub>  | 1      | _        | 1     |         | 1             |      | ns   |       |

| Address Setup Time                         |                 | t <sub>AS</sub>  | 2.5    | _        | 2.5   | _       | 2.5           |      | ns   |       |

| Address Hold Time                          |                 | t <sub>AH</sub>  | 1      | _        | 1     | _       | 1             | _    | ns   |       |

| CKE Setup Time                             |                 | t <sub>CKS</sub> | 2.5    |          | 2.5   | _       | 2.5           | _    | ns   |       |

| CKE Hold Time                              |                 | t <sub>CKH</sub> | 1      | _        | 1     | _       | 1             | _    | ns   |       |

| Command (CS, RAS, CAS, WE, DQM) Setup Time |                 | t <sub>CMS</sub> | 2.5    |          | 2.5   |         | 2.5           | _    | ns   |       |

| Command (CS, RAS, CA                       | S, WE, DQM)     | t <sub>CMH</sub> | 1      | _        | 1     | _       | 1             | _    | ns   |       |

Note 1. Output load.

# **Asynchronous Characteristics**

| Barranta                                      | 0                 | MS82V32520-75 |      | MS82V | 32520-8 | MS82V32520-10 |      | 11.2 | N1.1. |

|-----------------------------------------------|-------------------|---------------|------|-------|---------|---------------|------|------|-------|

| Parameter                                     | Symbol            | Min.          | Max. | Min.  | Max.    | Min.          | Max. | Unit | Note  |

| REF to REF/ACT/SACT Command Period            | t <sub>RC</sub>   | 67.5          | _    | 72    | _       | 90            | _    | ns   |       |

| ACT to PRE Command Period                     | t <sub>RAS</sub>  | 45            | 120k | 48    | 120k    | 60            | 120k | ns   |       |

| SACT to PRE Command Period                    | t <sub>RASS</sub> | 6             | _    | 6     | _       | 6             |      | CLK  |       |

| PRE to ACT Command Period                     | t <sub>RP</sub>   | 22.5          |      | 24    |         | 30            |      | ns   |       |

| PRE-ALL (Special Page) to SACT Command Period | t <sub>RPS</sub>  | 9             |      | 9     |         | 9             | _    | CLK  |       |

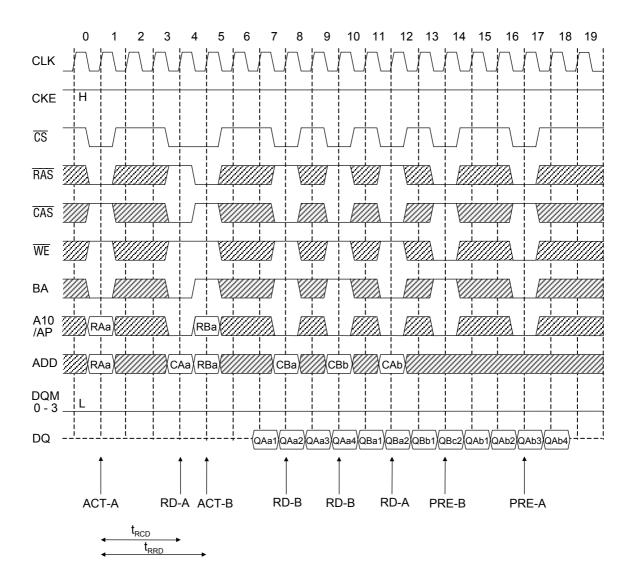

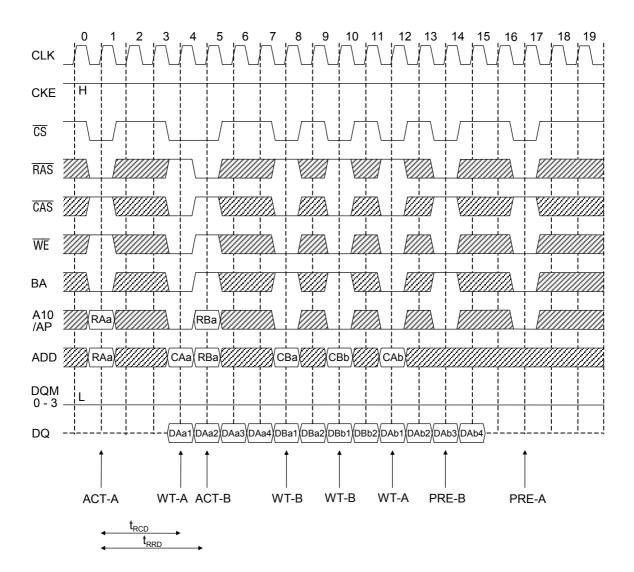

| Delay Time ACT/SACT to READ/WRITE Command     | t <sub>RCD</sub>  | 22.5          | _    | 24    | _       | 30            | _    | ns   |       |

| ACT (0) to ACT (1) Command Period             | t <sub>RRD</sub>  | 15            | _    | 16    | _       | 20            | _    | ns   |       |

| READ/WRITE to READ/WRITE Command Period       | t <sub>CCD</sub>  | 7.5           | _    | 8     | _       | 10            | _    | ns   |       |

| Data-in to PRE Command Period                 | t <sub>DPL</sub>  | 7.5           | _    | 8     | _       | 10            |      | ns   |       |

| Data Output to WRITE Command Input Time       | t <sub>OWD</sub>  | 15            | _    | 16    | _       | 20            | _    | ns   |       |

| Mode Register Set Cycle Time                  | t <sub>RSC</sub>  | 15            |      | 16    | _       | 20            |      | ns   |       |

| Transition Time                               | t <sub>T</sub>    | 1             | 30   | 1     | 30      | 1             | 30   | ns   |       |

| Refresh Time                                  | t <sub>REF</sub>  | _             | 64   | _     | 64      | _             | 64   | ms   |       |

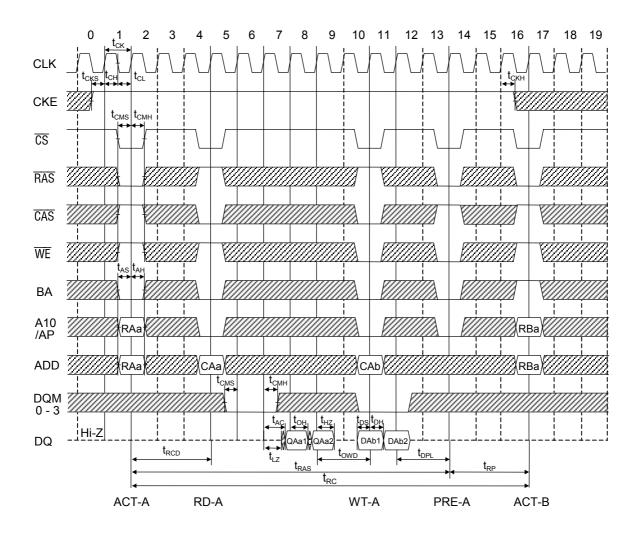

## TIMING WAVEFORM

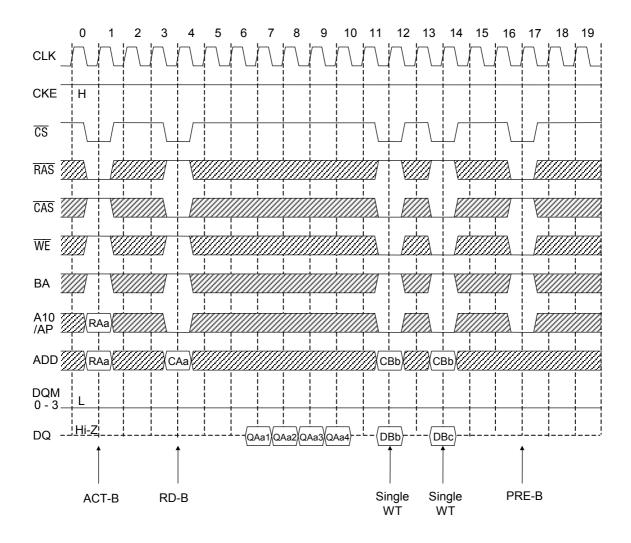

# READ/WRITE CYCLE (BL = 2, CL = 3)

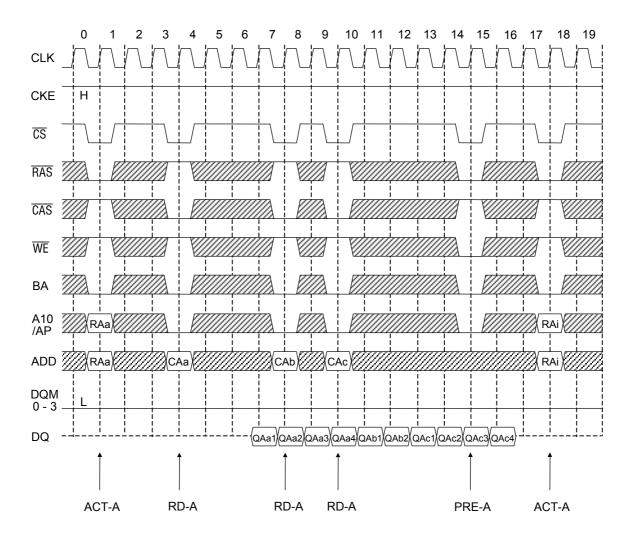

# Special READ CYCLE (BL = Special Page, CL = 3)

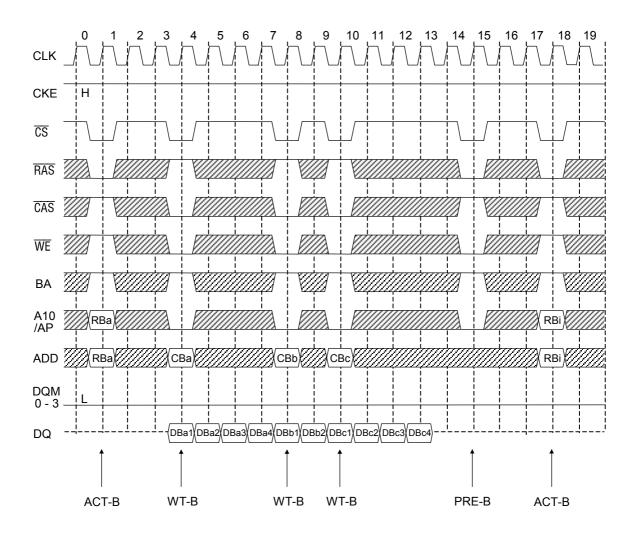

# Special WRITE CYCLE (BL = Special Page, CL = 3)

# **Mode Register Set**

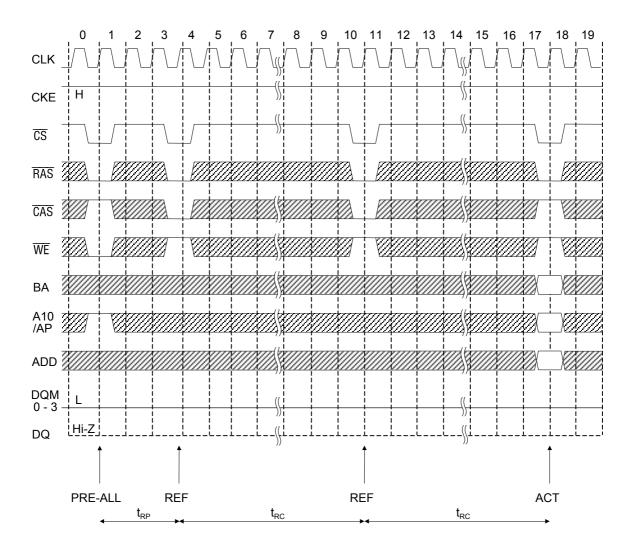

## **Auto Reflesh**

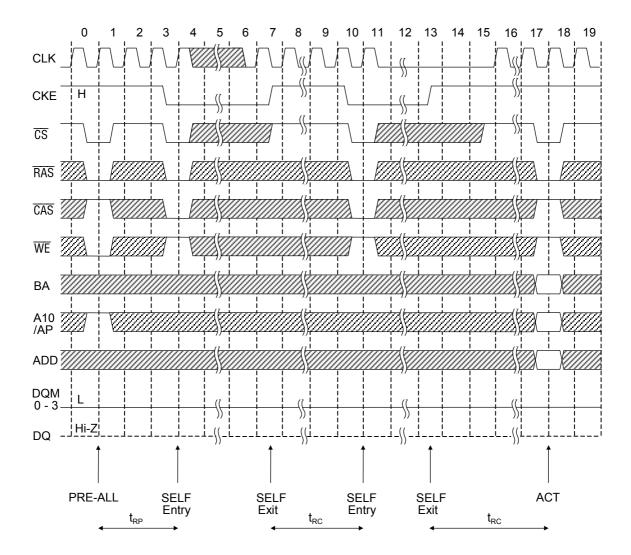

# Self Reflesh (Entry and Exit)

# **Burst Termination by Precharging (BL = 8, CL = 3)**

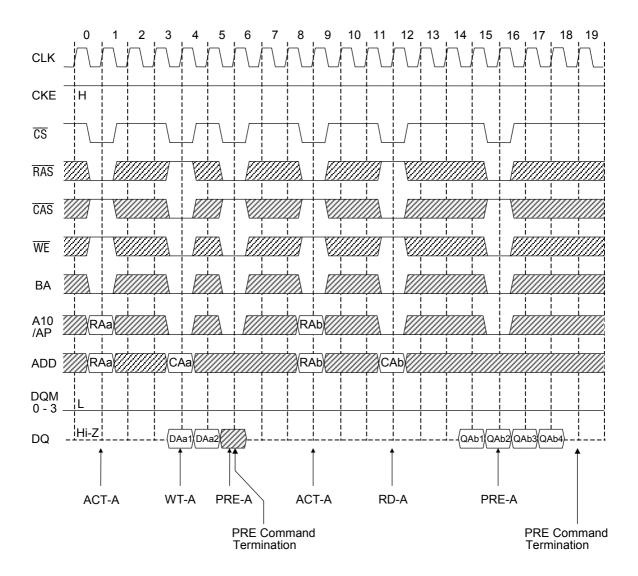

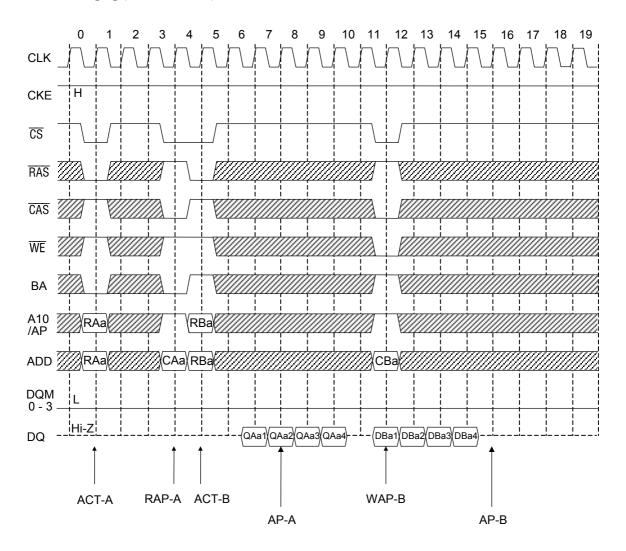

# Auto Precharging (BL = 4, CL = 3)

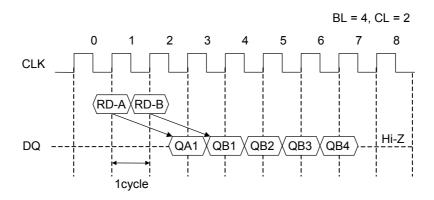

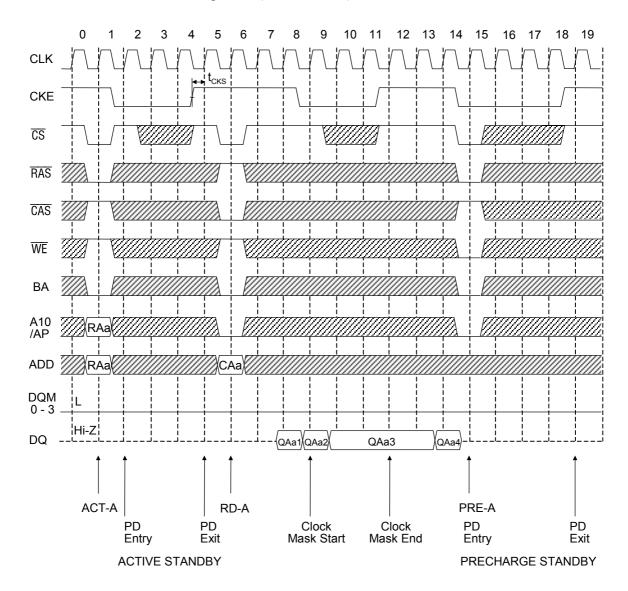

## Power Down Mode and Clock Suspension (BL = 4, CL = 2)

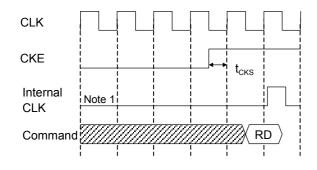

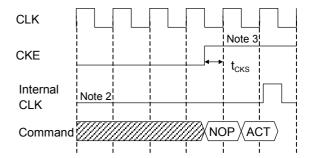

## **CLOCK Suspend Exit & Power Down Exit**

1) Clock Suspend (= Active Power Down) Exit

2) Power Down (= Precharge Power Down) Exit

Notes: 1. Active power down: one or both bank active state.

- 2. Precharge power down: both bank precharge state.

- 3. NOP should be issued. And new command can be issued after 1 Clock.

## Byte Read/Write Operation (by DQM) (BL = 4, CL = 3)

# Burst Read and Single Write (BL = 4, CL = 3)

# Random Column Read (Continuous Read of Same Bank) (BL = 4, CL = 3)

# Random Column Write (Continuous Write of Same Bank) (BL = 4, CL = 3)

# **Interleaved Column Read (BL = 4, CL = 3)**

# **Interleaved Column Write (BL = 4, CL = 3)**

#### PACKAGE DIMENSIONS

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

#### NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2001 Oki Electric Industry Co., Ltd.