# 10 AMP, 75 VOLT MOSFET SMART POWER 3-PHASE MOTOR DRIVE HYBRID

4303

M.S.KENNEDY CORP.

4707 Dey Road Liverpool, N.Y. 13088

(315) 701-6751

#### **FEATURES:**

- 75V, 10 Amp Capability

- Ultra Low Thermal Resistance Junction to Case 1.5 °C/W (Each MOSFET)

- · Self-Contained, Smart Lowside/Highside Drive Circuitry

- Bootstrap High-Side Supplies

- Under-Voltage Lockout

- Capable of Switching Frequencies to 25KHz

- Isolated Case Allows Direct Heat Sinking

- Bolt-down Design Allows Superior Heat Dissipation

MIL-PRF-38534 CERTIFIED

# **DESCRIPTION:**

The MSK 4303 is a 10 Amp, 3 Phase Bridge Smart Power Motor Drive Hybrid with a 75 volt rating on the output switches. The output switches are MOSFETs. This new smart power motor drive hybrid is 5.0 volt input logic compatible. Under-voltage lockout shuts down the bridge when the supply voltage gets to a point of incomplete turn-on of the output switches. The internal high-side bootstrap power supply derived from the +VB supply completely eliminates the need for 3 floating independent power supplies.

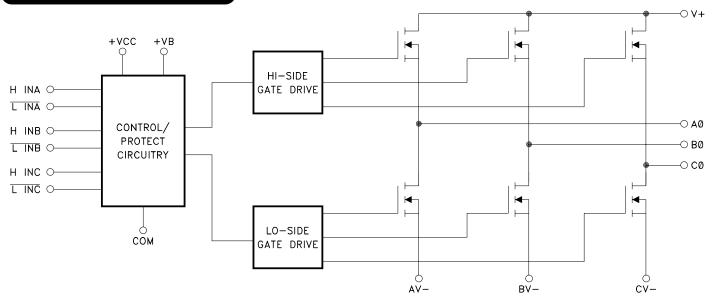

## **EQUIVALENT SCHEMATIC**

1

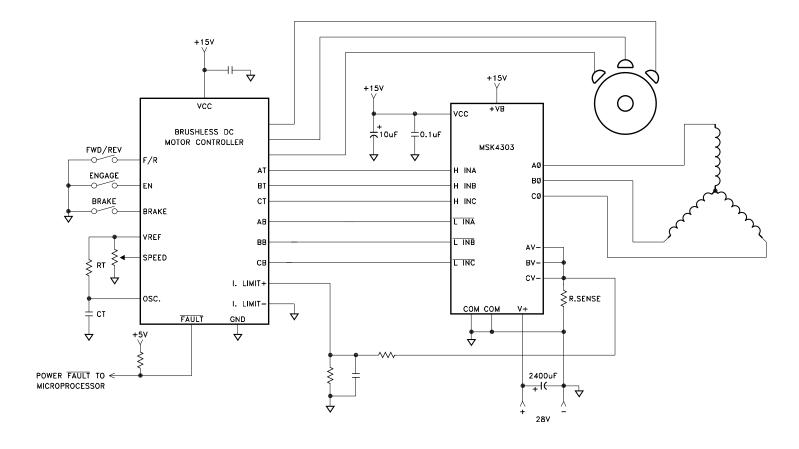

# TYPICAL APPLICATIONS

3 PHASE SIX STEP DC BRUSHLESS MOTOR DRIVE OR 3 PHASE SINUSOIDAL INDUCTION MOTOR DRIVE

# PIN-OUT INFORMATION

| 1 H INA | 20 | V + |

|---------|----|-----|

| 2 LINA  | 19 | N/C |

| 3 +VCC  | 18 | AV- |

| 4 H INB | 17 | ΑØ  |

| 5 L INB | 16 | N/C |

| 6 COM   | 15 | BV- |

| 7 COM   | 14 | ВØ  |

| 8 + VB  | 13 | N/C |

| 9 H INC | 12 | CV- |

| 10 LINC | 11 | CØ  |

# **ABSOLUTE MAXIMUM RATINGS**

| V + High Voltage Supply                     | TsT Storage Temperature Range65° to +150°C |

|---------------------------------------------|--------------------------------------------|

| Vcc Logic Supply                            | TLD Lead Temperature Range                 |

| IOUT Continuous Output Current 10A          | TC (10 Seconds)                            |

| IPK Peak Output Current                     | Case Operating Temperature                 |

| θJC Thermal Resistance @ 125°C              | MSK 430340°C to +85°C                      |

| (Output Switches)(Junction to Case) 1.5°C/W | MSK 4303H/E55°C to +125°C                  |

|                                             | TJ Junction Temperature + 150°C            |

# **ELECTRICAL SPECIFICATIONS**

| Parameters                                                           | Test Conditions                        | GROUP A<br>SUBGROUP<br>5 | MS<br>Min. |      | 3H/E ③<br>Max. |     | SK 43<br>Typ. | 03 ②<br>Max. | UNITS   |

|----------------------------------------------------------------------|----------------------------------------|--------------------------|------------|------|----------------|-----|---------------|--------------|---------|

| OUTPUT CHARACTERISTICS                                               |                                        |                          |            |      |                |     |               |              |         |

| Drain-Source ON Resistance ① (each MOSFET) (for thermal calculations |                                        | 1                        | 1          | -    | 0.013          | -   | -             | 0.013        | Ω       |

|                                                                      | $I_{\rm C} = 10$ A                     | 2                        | ı          | -    | 0.026          | -   | -             | -            | Ω       |

|                                                                      |                                        | 3                        | ı          | -    | 0.013          | -   | -             | -            | Ω       |

| Drain-Source Voltage (VDS(on)) (each MOSFET)                         | 1                                      | 1                        | -          | 0.56 | 1.2            | -   | 0.56          | 1.4          | volts   |

|                                                                      | Ic = 10A                               | 2                        | 1          | 0.78 | 1.5            | -   | -             | -            | volts   |

|                                                                      |                                        | 3                        | ı          | 0.42 | 1.0            | -   | -             | -            | volts   |

| Leakage Current (Each MOSFET                                         | V + = 75V                              | 1                        | ı          | 1    | 25             | -   | 1             | 25           | $\mu$ A |

|                                                                      | V + = 75V                              | 2                        | 1          | 10   | 250            | -   | -             | -            | mΑ      |

|                                                                      | V+ = 75V                               | 3                        | -          | 1    | 25             | -   | -             | -            | mΑ      |

| Reverse Recovery Time ①                                              | $ID = 10A$ , $di/dt = 100A/\mu S$      | -                        | -          | 120  | -              | -   | 120           | -            | nS      |

| BIAS SUPPLY CHARACTERISTIC                                           | S                                      |                          |            |      |                |     |               |              |         |

| + Vcc Bias Current                                                   | + Vcc = 15V                            | 1,2,3                    | -          | 12   | 20             | -   | 12            | 20           | mA      |

| + VB Bias Current                                                    | + V <sub>B</sub> = 15V                 | 1,2,3                    | -          | 6    | 9              | -   | 6             | 9            | mA      |

| INPUT SIGNAL CHARACTERISTIC                                          | CS                                     |                          |            |      |                |     |               |              |         |

| Positive Trigger Threshold Voltage                                   | + Vcc = 15V                            | -                        | 2.7        | -    | -              | 2.7 | -             | -            | volts   |

| Negative Trigger Threshold Voltage                                   | e 1 + Vcc = 15V                        | -                        | -          | -    | 0.8            | -   | -             | 0.8          | volts   |

| I LINGER-MOITAGE LACKOUT                                             | +Vcc Positive Going Threshold          | 1,2,3                    | 8.0        | 8.9  | 9.8            | 8.0 | 8.9           | 9.8          | volts   |

|                                                                      | + Vcc Negative Going Threshold         | 1,2,3                    | 7.4        | 8.2  | 9.0            | 7.4 | 8.2           | 9.0          | volts   |

| I Dead Time (I) —                                                    | Low Side Turn-off to High Side Turn-On | -                        | 280        | 400  | 520            | 280 | 400           | 520          | nSEC    |

|                                                                      | High Side Turn-off to Low Side Turn-On | -                        | 4          | 5    | 6              | 4   | 5             | 6            | μSEC    |

#### NOTES:

- ① Guaranteed by design but not tested. Typical parameters are representative of actual device performance but are for reference only.

- Qualitative by design but not tested. Typical parameters are representative of actual device performant and a unless otherwise specified.

Military grade devices ("H" suffix) shall be 100% tested to subgroups 1, 2 and 3.

Subgroups 5 and 6 testing available upon request.

Subgroup 1, 4 TA = TC = +25°C

- - 2, 5 TA = TC = +125 °C

- 3, 6 TA = TC = -55 °C

- (6) Continuous operation at or above absolute maximum ratings may adversely effect the device performance and/or life cycle.

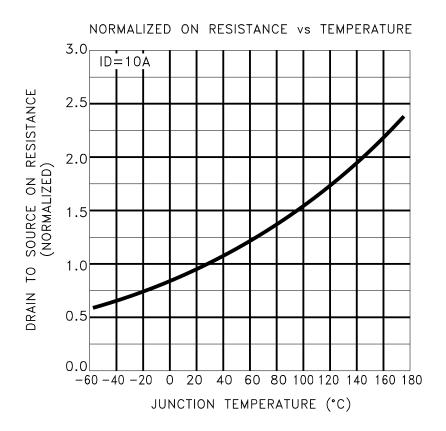

# TYPICAL PERFORMANCE CURVES

# **APPLICATION NOTES**

## **MSK 4303 PIN DESCRIPTIONS**

- +VCC Is the low voltage supply for all the internal logic and drivers. A 0.1  $\mu$ F ceramic capacitor in parallel with a 10 $\mu$ F tantalum capacitor is the recommended bypassing from the +VCC pin to the COM pin.

- H INA, H INB, H INC Are high active logic inputs for signalling the corresponding phase high-side switch to turn on. The logic inputs are compatible with standard CMOS or LSTTL outputs. These logic inputs are internally zener clamped at 5.2 volts.

- L INA, L INB, L INC Are low active logic inputs for signalling the corresponding phase low-side switch to turn on. The logic inputs are compatible with standard CMOS or LSTTL outputs. These logic inputs are internally zener clamped at 5.2 volts.

- AØ, BØ, CØ Are the pins connecting the 3 phase bridge switch outputs.

- AV-, BV-, CV- Are the connections from the bottoms of the three half bridges. These pins get connected to the COM pin. If current sensing is desired they may be connected to the COM pin through a low value sense resistor.

- $+\,$  VB Is the connection used to provide power to the floating high-side bootstrap supplies in the gate drive circuitry.

- **V**+ Is the high voltage positive rail connection to the tops of the three half bridges. Proper power supply bypassing must be connected from this pin to the COM pin for good filtering. This bypassing must be done as close to the hybrid as possible.

- **COM** Is the connection that all hybrid power supply connections are returned to and bypassed to.

# **TYPICAL SYSTEM OPERATION**

The MSK 4303 is designed to be used with a +28 volt high voltage bus, +15 volt low power bus and +5 volt logic signals. Proper derating should be applied when designing the MSK 4303 into a system. High frequency layout techniques with ground planes on a printed circuit board is the only method that should be used for circuit construction. This will prevent pulse jitter caused by excessive noise pickup on the current sense signal or the error amp signal.

Ground planes for the lower power circuitry and the high power circuitry should be kept separate. The connection between the bottom of the current sense resistor, COM pin and the high power ground, AV-, BV- and CV- pins are connected at this point. This is a critical path and high currents should not be flowing between the current sense and COM. Inductance in this path should be kept to a minimum. An RC filter (shown in 2 places) will filter out the current spikes and keep the detected noise for those circuits down to a minimum.

In the system shown a PWM pulse by pulse current limit scheme controlled by the motor controller is implemented.

When controlling the motor speed by the PWM method, it is required that the low side switches be PWM pulsed due to the bootstrap supplies used to power the high side switch drives. The higher the PWM speed the higher the current load on the drive supply. PWM of the low side will prevent sagging of the high side supplies. A separate pin (+VB) is provided for connecting an external floating power supply to power the bootstrap supplies.

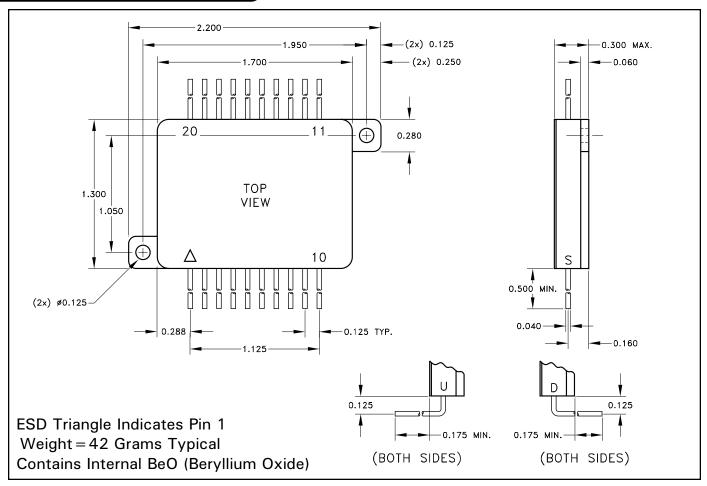

# **MECHANICAL SPECIFICATIONS**

All dimensions are  $\pm 0.01$  inches unless otherwise specified.

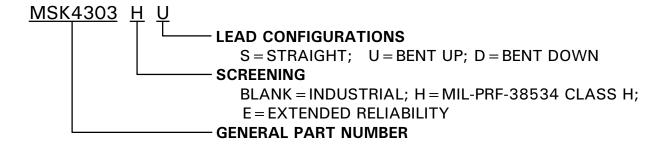

# ORDERING INFORMATION

M.S. Kennedy Corp.

4707 Dey Road, Liverpool, New York 13088

Phone (315) 701-6751

FAX (315) 701-6752

www.mskennedy.com

The information contained herein is believed to be accurate at the time of printing. MSK reserves the right to make changes to its products or specifications without notice, however and assumes no liability for the use of its products.

Please visit our website for the most recent version of this datasheet.