## Preliminary

#

- Quartz SAW Stabilized Differential Output Technology

- Very Low Jitter Fundamental-Mode Operation at 644.53125 MHz

- Voltage Tunable for Phase Locked Loop Applications

- Timing Reference for 10G Optical Ethernet Communications Systems

The OP4012B is a voltage-controlled SAW clock (VCSC) designed for phase-locked loop (PLL) applications in optical data communications systems. The differential outputs of the OP4012B are generated by high-Q, fundamental mode quartz surface acoustic wave (SAW) technology. This technique provides very low output jitter and phase noise, plus excellent immunity to power supply noise. The OP4012B differential outputs feature  $\pm 1\%$  symmetry, and can be DC-configured to drive a wide range of high-speed logic families. The OP4012B is packaged in a hermetic metal-ceramic LCC.

#### Absolute Maximum Ratings

| Rating           | Value      | Units |

|------------------|------------|-------|

| DC Suppy Voltage | 0 to 5.5   | Vdc   |

| Tune Voltage     | 0 to 5.5   | Vdc   |

| Case Temperature | -55 to 100 | °C    |

## OP4012B

## 644.53125 MHz Optical Timing Clock

#### **Electrical Characteristics**

|                                                    | Characteristic                                                                             | Sym             | Notes      | Minimum   | Typical    | Maximum | Units             |

|----------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------|------------|-----------|------------|---------|-------------------|

| Operating Frequency                                | Absolute Frequency                                                                         | f <sub>O</sub>  | 1          |           | 644.53125  |         | MHz               |

|                                                    | Tuning Range                                                                               |                 | 2          | ±100      |            |         | ppm               |

|                                                    | Tuning Voltage                                                                             |                 | 1          | 0         |            | 3.3     | Vdc               |

|                                                    | Tuning Linearity                                                                           |                 | 1, 8       |           | ±5         |         | %                 |

|                                                    | Tuning Sensitivity                                                                         | df/dv           | 2          | 100       |            | 260     | ppm/V             |

|                                                    | Modulation Bandwidth                                                                       |                 |            | 125       | 265        |         | kHz               |

| Q and Q Output                                     | Voltage into 50 $\Omega$ (VSWR $\leq$ 1.2)                                                 | Vo              | 1,3        | 0.60      |            | 1.1     | V <sub>P-P</sub>  |

|                                                    | Operating Load VSWR                                                                        |                 | 1,3        |           |            | 2:1     |                   |

|                                                    | Symmetry                                                                                   |                 | 3, 4, 5    | 49        |            | 51      | %                 |

|                                                    | Harmonic Spurious                                                                          |                 | 3, 4, 6    |           |            | -30     | dBc               |

|                                                    | Nonharmonic Spurious                                                                       |                 | 3, 4, 6, 7 |           |            | -60     | dBc               |

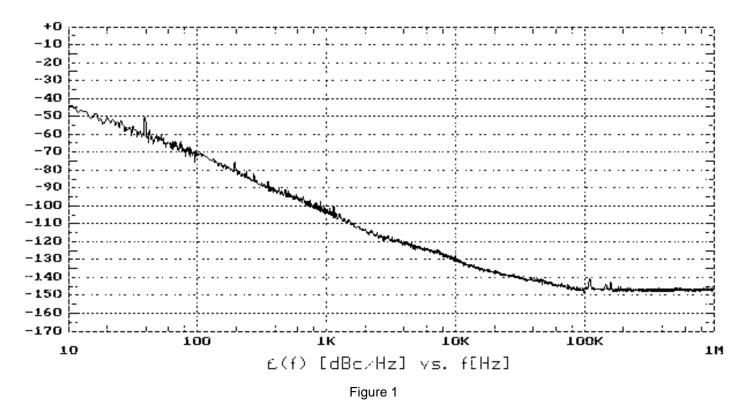

| Phase Noise                                        | @ 100 Hz offset                                                                            |                 | 3, 6       |           | -70        |         | dBc/Hz            |

|                                                    | @ 1 kHz offset                                                                             |                 | 3, 6       |           | -100       |         | dBc/Hz            |

|                                                    | @ 10 kHz offset                                                                            |                 | 3, 6       |           | -125       |         | dBc/Hz            |

|                                                    | Noise Floor                                                                                |                 | 3, 6       |           | -150       |         | dBc/Hz            |

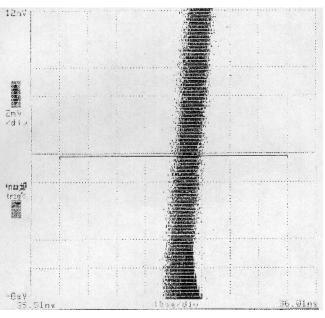

| Q and Q Jitter                                     | RMS Jitter                                                                                 |                 | 3, 4, 6, 7 |           | 2          |         | ps                |

|                                                    | No Noise on V <sub>CC</sub>                                                                |                 | 3, 4, 6, 7 |           | 12         |         | ps <sub>P-P</sub> |

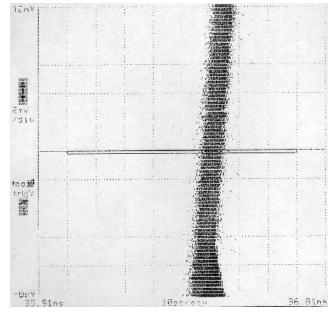

|                                                    | 200 mV <sub>P-P</sub> Noise, from 1 MHz to $\frac{1}{2}$ f <sub>O</sub> on V <sub>CC</sub> |                 | 3          |           | 12         |         | ps <sub>P-P</sub> |

| nput Impedence (Tunin                              | g Port)                                                                                    |                 |            | 1         |            |         | KΩ                |

| Output DC Resistance (between Q & $\overline{Q}$ ) |                                                                                            |                 | 1, 3       | 50        |            |         | KΩ                |

| DC Power Supply                                    | Operating Voltage                                                                          | V <sub>CC</sub> | 1, 3       | 3.13      | 3.3 or 5.0 | 5.25    | Vdc               |

|                                                    | Operating Current                                                                          | I <sub>CC</sub> | 1, 3       |           |            | 70      | mA                |

| Operating Case Temperature                         |                                                                                            | т <sub>с</sub>  | 1, 3       | -40°C     |            | +85°C   | °C                |

| Lid Symbolization (YY=Year, WW=Week)               |                                                                                            |                 |            | RFM OP401 | 2B YYWW    |         |                   |

CAUTION: Electrostatic Sensitive Device. Observe precautions for handling. COCOM CAUTION: Approval by the U.S. Department of Commerce is required prior to export of this device.

Notes:

1. Unless otherwise noted, all specifications include the combined effects of load VSWR,  $V_{CC}$  and  $T_{C}$ .

2. Net tuning range after tuning out the effects of initial manufacturing tolerances, VSWR pushing/pulling, V<sub>CC</sub>, T<sub>C</sub> and aging.

3. The internal design, manufacturing processes, and specifications of this device are subject to change without notice.

4. Specified only for a balanced load with a VSWR < 1.2 ( 50 ohms each side), and a  $V_{CC}$  = 3.0 Vdc.

5. Symmetry is defined as the width in (% of total period) measure at 50% of the peak-to-peak voltage of either output.

6. Jitter and other noise outputs due to power supply noise or mechanical vibration are not included in this specification except where noted.

7. Applies to period jitter of either differential output. Measured with a Tektronix CSA803 signal analyzer with at least 1000 samples.

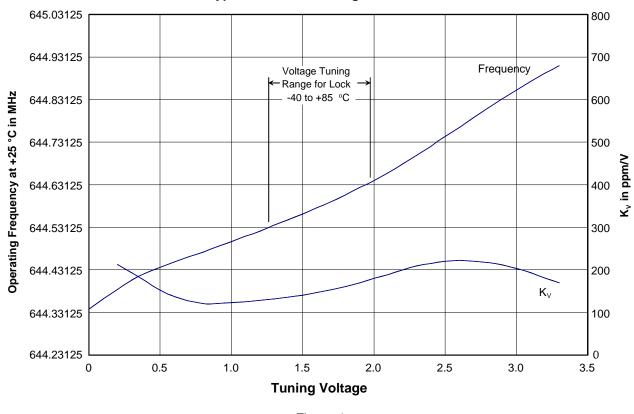

8. See Figure 4.

9. One or more of the following United States patents apply: 4, 616,197; 4,670,681; 4,760,352.

#### **OP4012B Performance Parameters**

The OP4012B has been developed to achieve high performance in five parameters critical to optical data communications applications:

Low Jitter and Phase Noise - low clock jitter (or low phase noise in the frequency domain) is critical to achieving low bit error rates in optical data communications systems. The OP4012B provides very low free-running jitter and phase noise as shown in Figures 1 and 2. This makes the OP4012B an excellent reference for the generation or regeneration of low-jitter clocks and data streams. The OP4012B achieves this performance over its full -40 to +85 °C operating temperature range using RFM's patented SAW oscillator architecture.

Single-Sideband Phase Noise

High Power Supply Noise Immunity - the OP4012B uses both differential active devices and differential SAW technology to minimize the effects of power supply noise on jitter and phase noise, as shown in Figures 2 and 3. Optical data communications circuits must switch relatively high levels of current, making power supply noise immunity an important clock requirement.

Controlled Tuning Characteristics - the OP4012B voltage tuning constant,  $K_V$ , is bounded between 100 and 260 ppm/V under locked conditions for reference signals with ±100 ppm or better stability over the OP4012B's full operating temperature and supply voltage range. This allows a PLL based on the OP4012B to be designed with a well-controlled loop bandwidth and damping factor, avoiding problems such a jitter peaking, etc. The voltage tuning characteristic of the OP4012B is monotonic from 0 to 3.3 V, supporting reliable acquisition of phase lock. Figure 4 shows typical OP4012B tuning characteristics.

**OP4012B Jitter Plot**

**No Power Supply Noise**

Figure 2

**OP4012B Jitter Plot**

200 mV of Power Supply Noise

Figure 3

#### **Typical OP4012B Tuning Characteristics**

*Differential Output Symmetry* - for balanced output loads, the differential output symmetry of the OP4012B is ±1%. This differential output symmetry meets the requirements of the most demanding high-speed logic families.

*Output DC Voltage Configurability* - the OP4012B differential outputs can be DC-configured to support a wide range of highspeed logic families and ASIC drive requirements by the selection of four resistors (see Configuring the OP4012B DC Output Voltage below) and a logic supply voltage. Each differential output of the OP4012B is AC-coupled to provide this flexibility.

#### **OP4005B** Tuning Details

The frequency tuning of the OP4012B is characterized over a voltage range of 0 to 3.3 V. The tuning voltage applied to the OP4012B should be limited to this range. Figure 4 shows the typical locked tuning range for operation over -40 or +85 °C. The frequency shift of a quartz SAW frequency control device with temperature has the shape of an inverted parabola, with the highest frequency occurring around +25 °C. At both -40 and +85 °C, there will be a 170 ppm downward shift in the frequency of the SAW device compared to +25 °C. Tuning to compensate for this temperature shift is the same as tuning 170 ppm higher at +25 °C. This is well within the tuning range of the OP4012B, as shown in Figure 4. Note that the voltage tuning constant,  $K_V$ , is bounded between 140 and 300 ppm/V under locked conditions for any temperature within the OP4012B's specified operating range.

The OP4012B tuning port presents a input impedance greater than 100 kilohms from DC to 50 kHz, and at least 1 kilohm for any RF frequency up to the operating frequency of the OP4012B. Most operational amplifiers used in active loop filters will be stable when driving the tuning port directly. Special care are should be taken to avoid ground loops in the path from the output of the phase detector though the loop filter to the tuning input of the OP4012B. For most applications, the bandwidth of the loop filter in a OP4012B PLL will be less than 50 Hz, as discussed in the example OP4012B PLL application section below.

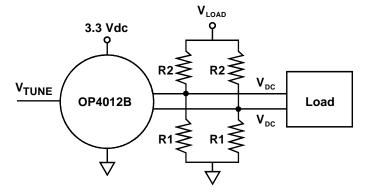

#### Configuring the OP4012B DC Output Voltage

Each differential output of the OP4012B is AC coupled, allowing the static DC level at each output to be set with a resistive divider to match the logic family being driven by the clock. The parallel-equivalent resistance of the two resistors in each divider should be approximately 50 ohms. The supply voltage to the dividers,  $V_{LOAD}$ , should be two to three times the value of the static DC voltage,  $V_{DC}$ .

Referring to Figure 5:

$$V_{DC} = V_{LOAD} * R1/(R1 + R2)$$

and

50 = R1\*R2/(R1 + R2)

The values of the resistors R2 and R1 are given directly as:

$R2 = 50^*V_{LOAD}/V_{DC}$

$$R1 = 1/(0.02 - (1/R2))$$

#### **OP4012B DC Output Voltage Adjustment**

Figure 5

Table 1 provides R1 and R2 values for six high-speed logic families commonly used in optical data communications systems. Note that the OP4012B can be used with logic families that run from a negative power supply voltage by simply using a negative V<sub>LOAD</sub> voltage.

| Load Type       | V <sub>DC</sub> | R1  | R2 | V <sub>LOAD</sub> |

|-----------------|-----------------|-----|----|-------------------|

| 10k 3.3 V PECL  | 1.95            | 120 | 91 | 3.3 V             |

| 100k 3.3 V PECL | 1.88            | 120 | 91 | 3.3 V             |

| 10k 5 V PECL    | 3.65            | 180 | 68 | 5.0 V             |

| 100k 5 V PECL   | 3.58            | 180 | 68 | 5.0 V             |

| 10k -5 V NECL   | -1.30           | 240 | 62 | -5.0 V            |

| 100k -5 V NECL  | -1.42           | 240 | 62 | -5.0 V            |

Table 1

#### OP4012B Enable/Disable

Pin 3 on the OP4012B is the enable/disable control pin for the clock outputs. When Pin 3 is grounded, full output power is available from the clock. When Pin 3 is pulled to Vcc, the power on the clock outputs is decreased at least 25 dB.

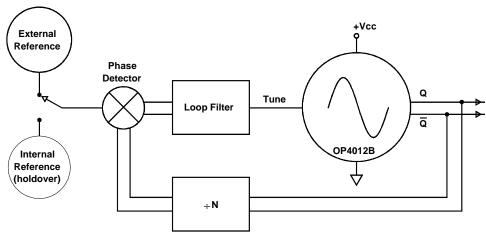

#### PLL for Generating a High Stability 644.53125 MHz Clock

#### Example OP4012B Phase-Locked Loop Application

One of the most important applications for the OP4012B is in a PLL circuit used to generate a very high quality 644.53125 MHz clock. The PLL combines the long-term stability of a precision external or internal 20.1416 MHz reference clock with the very low jitter and phase noise of the OP4012B. A block diagram of the PLL is shown in Figure 6. A sample of the OP4012B output is divided by 32 and is compared to 20.1416 MHz reference clock in the phase detector. The loop filter at the output of the phase detector is set to a very low bandwidth (less than 50 Hz typical). This imparts the long-term stability of the precision 20.1416 MHz reference to the OP4012B without degrading the OP4012B's low jitter and phase noise.

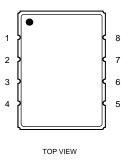

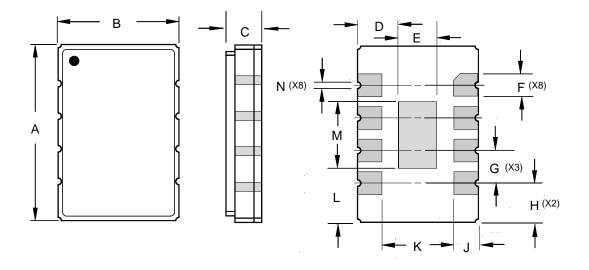

### SMC-8 8-Terminal Surface Mount Case

#### **ELECTRICAL CONNECTIONS**

| Terminal<br>Number | Connection      |  |

|--------------------|-----------------|--|

| 1                  | V <sub>CC</sub> |  |

| 2                  | Ground          |  |

| 3                  | Enable/Disable  |  |

| 4                  | Q Output        |  |

| 5                  | Q Output        |  |

| 6                  | Ground          |  |

| 7                  | Cround          |  |

| 8                  | Tuning Input    |  |

| LID                | Ground          |  |

| Dimen- | mm           |       | Inches        |       |  |

|--------|--------------|-------|---------------|-------|--|

| sion   | MIN          | MAX   | MIN           | MAX   |  |

| A      | 13.46        | 13.97 | 0.530         | 0.550 |  |

| В      | 9.14         | 9.66  | 0.360         | 0.380 |  |

| С      | 1.93 Nominal |       | 0.076 Nominal |       |  |

| D      | 3.56 Nominal |       | 0.141 Nominal |       |  |

| E      | 2.24 Nominal |       | 0.088 Nominal |       |  |

| F      | 1.27 Nominal |       | 0.050 Nominal |       |  |

| G      | 2.54 Nominal |       | 0.100 Nominal |       |  |

| н      | 3.05 Nominal |       | 0.120 Nominal |       |  |

| J      | 1.93 Nominal |       | 0.076 Nominal |       |  |

| к      | 5.54 Nominal |       | 0.218 Nominal |       |  |

| L      | 4.32 Nominal |       | 0.170 Nominal |       |  |

| М      | 4.83 Nominal |       | 0.190 Nominal |       |  |

| N      | 0.50 Nominal |       | 0.020 Nominal |       |  |

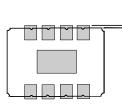

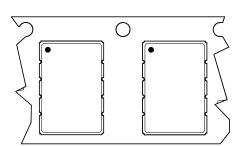

#### Typical Printed Circuit Board Land Pattern

A typical land pattern for a circuit board is shown on the right. Grounding of the metallic center pad is optional.

Typically 0.01" to 0.05" or 0.25 mm to 1.25 mm (8 Places)

(The optimum value of this dimension is dependent on the PCB assembly process employed.)

SMC-08 Case

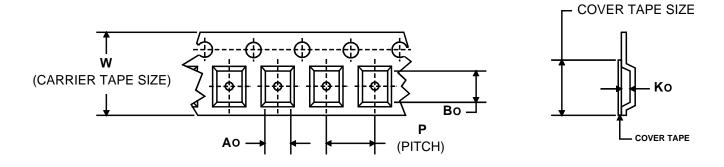

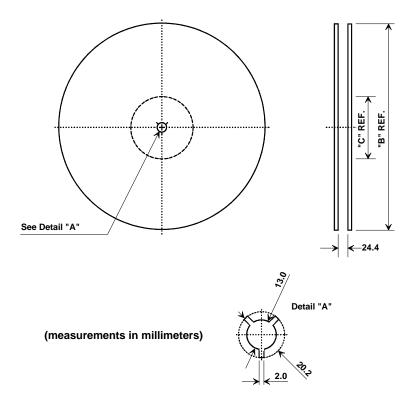

| Reel Size   |        |             | Quantity<br>Per Reel |      |

|-------------|--------|-------------|----------------------|------|

| "B" Nominal |        | "C" Nominal | Min                  | Max  |

| 13 Inch     | 330 mm | 100 mm      | 200                  | 1000 |

**Orientation in Tape Carrier as Shipped**

#### Dimensions

| Carrier Tape Dimer | Cover Tape         |        |

|--------------------|--------------------|--------|

| Ао                 | .383 ± .004 (9.7)  | 21.3mm |

| Во                 | .554 ± .004 (14.1) |        |

| Ко                 | .130 ± .004 (3.3)  |        |

| Р                  | 12mm               |        |

| W                  | 24mm               |        |

| Tape Length        | 60M                |        |

| Pockets/M          | 83/M               |        |