# **PI6CU877**

PLL Clock Driver for 1.8V DDR2 Memory

### Features

- PLL clock distribution optimized for DDR2 SDRAM applications.

- Distributes one differential clock input pair to ten differential clock output pairs.

- Differential Inputs (CLK, CLK) and (FBIN, FBIN)

- Input OE/OS: LVCMOS

- Differential Outputs (Y[0:9],  $\overline{Y[0:9]}$  and (FBOUT,  $\overline{FBOUT}$ )

- External feedback pins (FBIN, FBIN) are used to synchronize the outputs to the clock input.

- Operates at  $AV_{DD} = 1.8V$  for core circuit and internal PLL, and  $V_{DDQ} = 1.8V$  for differential output drivers

- Packaging (Pb-free & Green available):

52-ball VFBGA (NF)

# **Pin Configuration**

| - | 0                |                  |                  |                  |                  |                   |

|---|------------------|------------------|------------------|------------------|------------------|-------------------|

|   | 1                | 2                | 3                | 4                | 5                | 6                 |

| А | Y1               | Y <sub>0</sub>   | $\overline{Y_0}$ | $\overline{Y_5}$ | Y <sub>5</sub>   | Y <sub>6</sub>    |

| В | $\overline{Y_1}$ | GND              | GND              | GND              | GND              | $\overline{Y_6}$  |

| С | $\overline{Y_2}$ | GND              | NB               | NB               | GND              | $\overline{Y_7}$  |

| D | Y <sub>2</sub>   | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>DDQ</sub> | OS               | Y <sub>7</sub>    |

| Е | СК               | V <sub>DDQ</sub> | NB               | NB               | V <sub>DDQ</sub> | FBIN              |

| F | СК               | V <sub>DDQ</sub> | NB               | NB               | OE               | FB <sub>IN</sub>  |

| G | AGND             | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>DDQ</sub> | V <sub>DDQ</sub> | FBOUT             |

| Н | AV <sub>DD</sub> | GND              | NB               | NB               | GND              | FB <sub>OUT</sub> |

| J | Y3               | GND              | GND              | GND              | GND              | Y <sub>8</sub>    |

| k | <u>Y</u> 3       | $\overline{Y_4}$ | Y4               | Y9               | <u>Y9</u>        | $\overline{Y_8}$  |

|   |                  |                  |                  | -                |                  |                   |

|   |                  |                  |                  |                  |                  |                   |

# Description

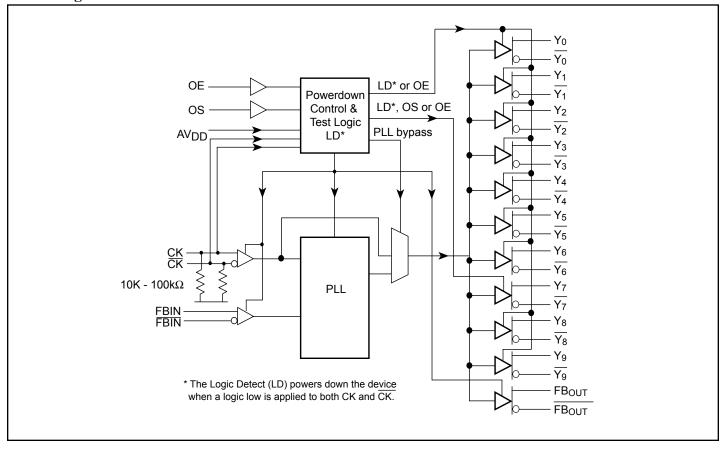

PI6CU877 PLL clock driver is developed for Registered DDR2 DIMM applications with 1.8V operation and differential data input and output levels.

The device is a zero delay buffer that distributes a differential clock input pair (CLK,  $\overline{CLK}$ ) to eleven differential pairs of clock outputs which includes feedback clock (Y[0:9],  $\overline{Y[0:9]}$ ; FBOUT, FBOUT).

The clock outputs are controlled by CLK/CLK, FBOUT, FBOUT, the LVCMOS (OE, OS) and the Analog Power input (AV<sub>DD</sub>). When OE is LOW the outputs except FBOUT, FBOUT, are disabled while the internal PLL continues to maintain its locked-in frequency. OS is a program pin that must be tied to GND or V<sub>DD</sub>. When OS is high, OE will function as described above. When OS is LOW, OE has no effect on Y7/ $\overline{Y7}$ , they are free running. When AV<sub>DD</sub> is grounded, the PLL is turned off and bypassed for test purposes.

When CLK/ $\overline{\text{CLK}}$  are logic low, the device will enter a low power mode. An input logic detection circuit will detect the logic low level and perform a low power state where all Y[0:9],  $\overline{\text{Y}[0:9]}$ ; FBOUT, FBOUT, and PLL are OFF.

PI6CU877 is a high performance, low skew, and low jitter PLL clock driver, and it is also able to track Spread Spectrum Clocking (SSC) for reduced EMI.

# **Block Diagram**

### **Pinout Table**

| Pin Name          | Characteristics      | Desctription                                                            |  |

|-------------------|----------------------|-------------------------------------------------------------------------|--|

| AGND              | Ground               | Analog ground                                                           |  |

| AV <sub>DD</sub>  | 1.8V nominal         | Analog power                                                            |  |

| СК                | Differential Input   | Clock input with a (10K - 100K $\Omega$ ) pulldown resistor             |  |

| CK                | Differential Input   | Complementary clock input with a $(10K - 100K\Omega)$ pulldown resistor |  |

| FBIN              | Differential Input   | Complementary feedback clock input                                      |  |

| FBIN              | Differential Input   | Feedback clock input                                                    |  |

| FB <sub>OUT</sub> | Differenital Output  | Complementary Feedback clock output                                     |  |

| FB <sub>OUT</sub> | Differential Output  | Feedback clock output                                                   |  |

| OE                | LVCMOS input         | Output enable (async.)                                                  |  |

| OS                | LVCMOS input         | Output select (tied to GND or V <sub>DDQ</sub> )                        |  |

| GND               | Ground               | Ground                                                                  |  |

| V <sub>DDQ</sub>  | 1.8V nominal         | Logic and output power                                                  |  |

| Y[0:9]            | Differential Outputs | Clock outputs                                                           |  |

| <u>Y[0:9]</u>     | Differential Outputs | Complementary clock outputs                                             |  |

| NB                |                      | No Ball (VFBGA only)                                                    |  |

# **Function Table**

|                  | Inputs |    |    |           | Outputs                            |                                    |              |              | PLL State  |

|------------------|--------|----|----|-----------|------------------------------------|------------------------------------|--------------|--------------|------------|

| AV <sub>DD</sub> | OE     | OS | СК | <b>CK</b> | Y                                  | Y                                  | FBOUT        | FBOUT        | PLL State  |

| GND              | Н      | Х  | L  | Н         | L                                  | Н                                  | L            | Н            | Bypass/Off |

| GND              | Н      | Х  | Н  | L         | Н                                  | L                                  | Н            | L            | Bypass/Off |

| GND              | L      | Н  | L  | Н         | $L(Z)^{(1)}$                       | $L(Z)^{(1)}$                       | L            | Н            | Bypass/Off |

| GND              | L      | L  | Н  | L         | L(Z) <sup>(1)</sup> ,<br>Y7 active | L(Z) <sup>(1)</sup> ,<br>Y7 active | Н            | L            | Bypass/Off |

| 1.8V (nom)       | L      | Н  | L  | Н         | $L(Z)^{(1)}$                       | $L(Z)^{(1)}$                       | L            | Н            | On         |

| 1.8V (nom)       | L      | L  | Н  | L         | L(Z) <sup>(1)</sup> ,<br>Y7 active | L(Z) <sup>(1)</sup> ,<br>Y7 active | Н            | L            | On         |

| 1.8V (nom)       | Н      | Х  | L  | Н         | L                                  | Н                                  | L            | Н            | On         |

| 1.8V (nom)       | Н      | Х  | Н  | L         | Н                                  | L                                  | Н            | L            | On         |

| 1.8V (nom)       | Х      | Х  | L  | L         | $L(Z)^{(1)}$                       | $L(Z)^{(1)}$                       | $L(Z)^{(1)}$ | $L(Z)^{(1)}$ | Off        |

| 1.8V (nom)       | Х      | Х  | Н  | Н         | Reserved                           |                                    |              |              |            |

#### Notes:

1. L<sub>(Z)</sub> means the outputs are disabled to a low state meeting the I<sub>ODL</sub> limit on DC Specification

#### Absolute Maximum Ratings (Over operating free-air temperature range)

| Symbol                              | Parameter                                                      |      | Max.                     | Units |

|-------------------------------------|----------------------------------------------------------------|------|--------------------------|-------|

| V <sub>DDQ</sub> , A <sub>VDD</sub> | I/O supply voltage range and analog /core supply voltage range | -0.5 | 2.5                      |       |

| VI                                  | I Input voltage range                                          |      | V <sub>DDQ</sub><br>+0.5 | V     |

| Vo                                  | Output voltage range                                           | -0.5 |                          |       |

| I <sub>IK</sub>                     | Input clamp current                                            | -50  | 50                       |       |

| I <sub>OK</sub>                     | Output clamp current                                           | -50  | 50                       |       |

| IO                                  | Continuous output current                                      | -50  | 50                       | mA    |

| I <sub>O(PWR)</sub>                 | Continuous current through each VDDQ or GND                    | -100 | 100                      |       |

| T <sub>STG</sub>                    | Storage temperature                                            | -65  | 150                      | °C    |

Note:

1. Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

#### **DC Specifications Recommended Operating Conditions**

| Symbol           | Parameter                                            | Parameter                                                          |                                | Тур.             | Max.                           | Units  |

|------------------|------------------------------------------------------|--------------------------------------------------------------------|--------------------------------|------------------|--------------------------------|--------|

| V <sub>DDQ</sub> | Output supply Voltage                                |                                                                    | 1.7                            | 1.8              | 1.9                            |        |

| AV <sub>DD</sub> | Supply voltage <sup>(4)</sup>                        |                                                                    |                                | V <sub>DDQ</sub> |                                |        |

| V <sub>IL</sub>  | Low-level input voltage <sup>(5)</sup>               | Low-level input voltage <sup>(5)</sup> OE, OS, CK, $\overline{CK}$ |                                |                  | 0.35 x<br>V <sub>DDQ</sub>     | V      |

| V <sub>IH</sub>  | High-level input voltage <sup>(5)</sup>              | OE, OS, CK, $\overline{CK}$                                        | 0.65 x<br>V <sub>DDQ</sub>     |                  |                                |        |

| I <sub>OH</sub>  | High-level output current, see Fig 2                 |                                                                    | -                              |                  | -9                             |        |

| I <sub>OL</sub>  | Low-level output current, see Fig. 2                 |                                                                    | -                              |                  | 9                              | mA     |

| V <sub>IX</sub>  | Input differential-pair crossing voltage             |                                                                    | (V <sub>DDQ</sub> /2)<br>-0.15 |                  | (V <sub>DDQ</sub> /2)<br>-0.15 | 1112 ¥ |

| V <sub>IN</sub>  | Input voltage level                                  |                                                                    | -0.3                           |                  | V <sub>DDQ</sub> +0.3          |        |

| V                | Lemma differential realizers $S_{ab} = E_{ab} = 0$   | DC                                                                 | 0.3                            |                  | V <sub>DDQ</sub> +0.4          | V      |

| V <sub>ID</sub>  | Input differenital voltage, See Fig 9 <sup>(5)</sup> | AC                                                                 | 0.6                            |                  | V <sub>DDQ</sub> +0.4          |        |

| T <sub>A</sub>   | Operating free air temperature                       | Operating free air temperature                                     |                                |                  | 70                             | °C     |

Notes:

4. The PLL is turned off and bypassed for test purposes when AV<sub>DD</sub> is grounded. During this test mode, V<sub>DDQ</sub> remains within the recommended operating conditions and no timing parameters are guaranteed.

5.  $V_{ID}$  is the magnitude of the difference between the input level on CK and the input level on  $\overline{CK}$ , see Figure 9 for definition. The CK and  $\overline{CK}$ ,  $V_{IH}$  and  $V_{IL}$  limits are used to define the DC low and high levels for the logic detect state.

| Symbol           | Description                                   | AV <sub>DD</sub> , V <sub>DDQ</sub> | Units |        |

|------------------|-----------------------------------------------|-------------------------------------|-------|--------|

| Symbol           | Decription                                    | Min.                                | Max.  | Units  |

| FCK              | Operation clock frequency <sup>(7, 8)</sup>   | 25                                  | 300   | MHz    |

| ГСК              | Application clock frequency <sup>(7, 9)</sup> | 160                                 | 270   | IVITIZ |

| t <sub>DC</sub>  | Input clock duty cycle                        | 40                                  | 60    | %      |

| tL               | Stabalization time <sup>(10)</sup>            |                                     | 15    | μs     |

| t <sub>OFF</sub> | Device power down <sup>(10)</sup>             |                                     | 8     | ns     |

#### Timing Requirements (Over recommended operating free-air temperature)

#### Notes:

7. The PLL is able to handle spread spectrum induced skew.

- 8. Operating clock frequency indicates a range over which the PLL is able to lock, but in which it is not required to meet the other timing parameters. (Used for low-speed debug).

- 9. Application clock frequency indicates a range over which the PLL must meet all timing parameters.

- 10. Stabilization time is the time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal after power up. During normal operation, the stabilization time is also the time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal when CK and CK go to a logic low state, enter the power-down mode and later return to active operation. CK and CK maybe left floating after they have been driven low for one complete clock cycle.

| Param-<br>eter    | Description                                                                               | Test Condition                                                                                | AV <sub>DD</sub> ,<br>V <sub>DDQ</sub> | Min.                     | Тур. | Max. | Units |

|-------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------|--------------------------|------|------|-------|

| V <sub>IK</sub>   | All Inputs                                                                                | I <sub>I</sub> = -18mA                                                                        | 1.7V                                   |                          |      | 1.2  |       |

| V <sub>OH</sub>   | HIGH output voltage                                                                       | $I_{OH} = -100 \mu A$                                                                         | 1.7 to<br>1.9V                         | V <sub>DDQ</sub><br>-0.2 |      |      | V     |

|                   |                                                                                           | $I_{OH} = -9mA$                                                                               | 1.7                                    | 1.1                      |      |      |       |

| I <sub>ODL</sub>  | Output disabled low current                                                               | $OE = L, V_{ODL} = 100mV$                                                                     |                                        | 100                      |      |      | μA    |

| V <sub>OD</sub>   | Output differenital voltage, the magn<br>between the true and complimentary<br>dimentions |                                                                                               | 1.7V                                   | 0.6                      |      |      | V     |

| T.                | CK, CK                                                                                    | $V_I = V_{DDQ}$ or GND                                                                        |                                        |                          |      | ±250 |       |

| II                | OE, OS, FB <sub>IN</sub> , FB <sub>IN</sub>                                               | $V_I = V_{DDQ}$ or GND                                                                        |                                        |                          |      | ±10  | μA    |

| I <sub>DDLD</sub> | Static Supple current, $I_{DDQ} + I_{ADD}$                                                | CK and $\overline{CK} = L$                                                                    | 1.9V                                   |                          |      | 500  |       |

| I <sub>DD</sub>   | Dynamic supply current, $I_{DDQ}$ + $I_{ADD}$ , see note 6 for CPD calculation            | CK and $\overline{CK} = 270 \text{MHz}$ ,<br>all outputs are open (not<br>connected to a PCB) |                                        |                          |      | 300  | mA    |

|                   | CK, CK                                                                                    | $V_I = V_{DDQ}$ or GND                                                                        |                                        | 2                        |      | 3    |       |

| CI                | FB <sub>IN</sub> , FB <sub>IN</sub>                                                       | $V_I = V_{DDQ}$ or GND                                                                        | 1.8V                                   | 2                        |      | 3    |       |

|                   | CK, CK                                                                                    | $V_{I} = V_{DDQ}$ or GND                                                                      | 1.0 V                                  |                          |      | 0.25 | pF    |

| $CI(\Delta)$      | FB <sub>IN</sub> , FB <sub>IN</sub>                                                       | $V_I = V_{DDQ}$ or GND                                                                        |                                        |                          |      | 0.25 |       |

### **DC Specifications**

#### Notes:

6. Total  $I_{DD} = I_{DDQ} + I_{ADD} = F_{CK} * C_{PD} * V_{DDQ}$ , solving for  $C_{PD} = (I_{DDQ} + I_{ADD})/(F_{CK} * V_{DDQ})$  where  $F_{CK}$  is the input frequency,  $V_{DDQ}$  is the power supply and  $C_{PD}$  is the Power Dissipation Capacitance.

### **AC Specifications**

Switching characteristics over recommended operating free-air temperature range (unless otherwise noted)<sup>(15)</sup>

| Parameter       | Description                                                 | Diagnam                                  | AV <sub>DD</sub>              | $V_{DDQ} = 1.8$ | SV ±0.1V                      | Units |  |

|-----------------|-------------------------------------------------------------|------------------------------------------|-------------------------------|-----------------|-------------------------------|-------|--|

| rarameter       | Description                                                 | Diagram                                  | Min.                          | Nom.            | Max.                          |       |  |

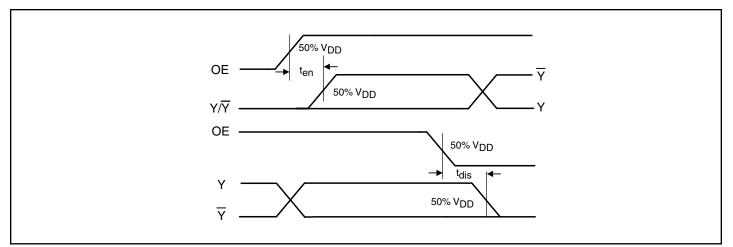

| ten             | $\overline{OE}$ to and Y/Y                                  | see Fig 11                               |                               |                 | 8                             |       |  |

| tdis            | $\overline{OE}$ to and Y/Y                                  | see Fig 11                               |                               |                 | 8                             | ns    |  |

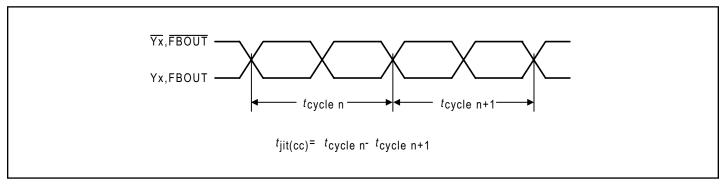

| tjit(cc+)       | Cuele te cuele iitter                                       | and Fig.4                                | 0                             |                 | 40                            |       |  |

| tjit(cc-)       | Cycle-to-cycle jitter                                       | see Fig 4                                | 0                             |                 | -40                           |       |  |

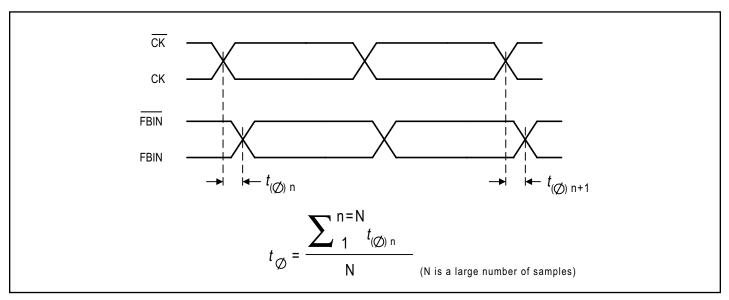

| t(Ø)            | Static phase offset <sup>(11)</sup>                         | see Fig 5                                | -50                           |                 | 50                            | 1     |  |

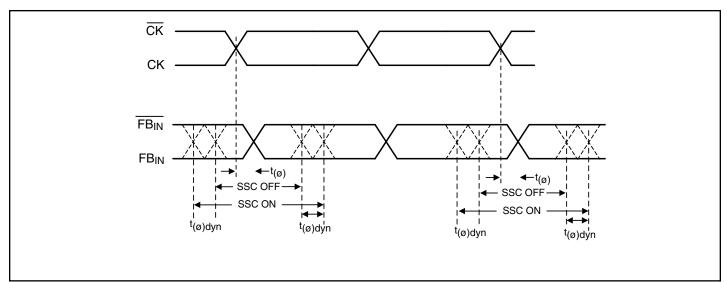

| t(Ø)dyn         | Dynamic phase offset                                        | see Fig 10                               | -50                           |                 | 50                            | ps    |  |

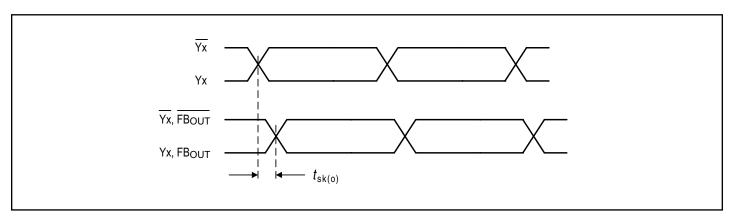

| tsk(o)          | Output clock skew                                           | see Fig 6                                |                               |                 | 40                            |       |  |

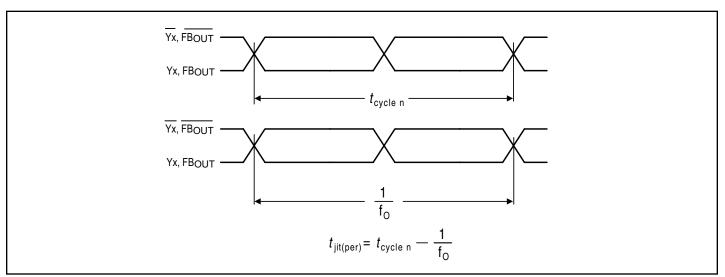

| tjit(per)       | Period jitter <sup>(12)</sup>                               | see Fig 7                                | -40                           |                 | 40                            |       |  |

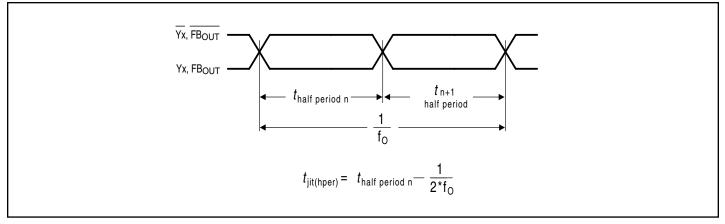

| tjit(hper)      | Halk period jitter <sup>(12)</sup>                          | see Fig 8                                | -75                           |                 | 75                            |       |  |

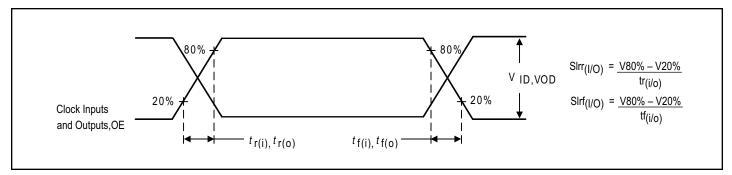

| alr(i)          | Input clock slew rate                                       | see Fig 9                                | 1                             | 2.5             | 4                             |       |  |

| slr(i)          | Output enable (OE)                                          | see Fig 9                                | 0.5                           |                 |                               | V/ns  |  |

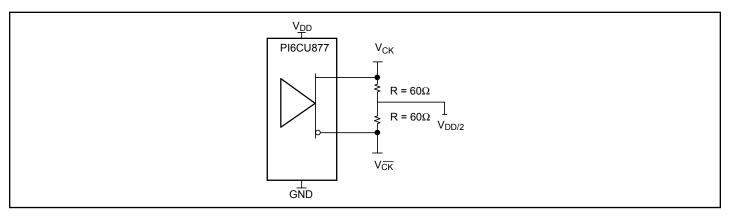

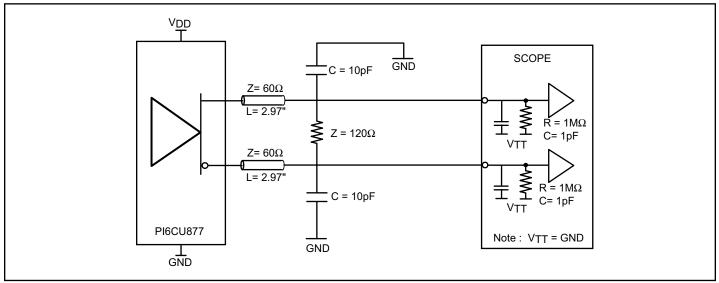

| slr(o)          | Output clock slew rate (14, 16)                             | see Fig 1, 9                             | 1.5                           | 2.5             | 3                             |       |  |

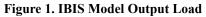

| V <sub>OX</sub> | Outpu differenital-pair cross voltage <sup>(13)</sup>       | see Fig 2                                | (V <sub>DDQ</sub> /2)<br>-0.1 |                 | (V <sub>DDQ</sub> /2)<br>+0.1 | v     |  |

| The             | PLL on the PI6CU877 is capable of meeting al<br>with the fo | l the above test pa<br>ollowing paramete |                               | e supporting    | SSC synthesire                | TS    |  |

|                 | SSC modulation frequency                                    |                                          |                               |                 | 33                            | kHz   |  |

|                 | SSC clock input frequency deviation                         |                                          | 0.00                          |                 | -0.50                         | %     |  |

|                 | PI6CU877 PLL design should target the                       | values below to r                        | ninimize the S                | CC induced      | skew:                         |       |  |

|                 | PLL Loop Bandwidth                                          |                                          | 2.0                           |                 |                               | MHz   |  |

Notes:

11. Static Phase Offset does not include Jitter

12. Period Jitter and Half-Period Jitter specifications are separate specifications that must be met independently of each other.

13. VOX specified at the DRAM clock input or the test load.

14. To eliminate the impact of input slew rates on static phase offset, the input slew rates of Reference Clock Input CK, CK and Feedback Clock Input FBIN, FBIN are recommended to be nearly equal. The 2.5V/ns slew rates are shown as a recommended target. Compliance with these Nom values is not mandatory if it can be adequately demonstrated that alternative characteristics meet the requirements of the registered DDR2 DIMM application.

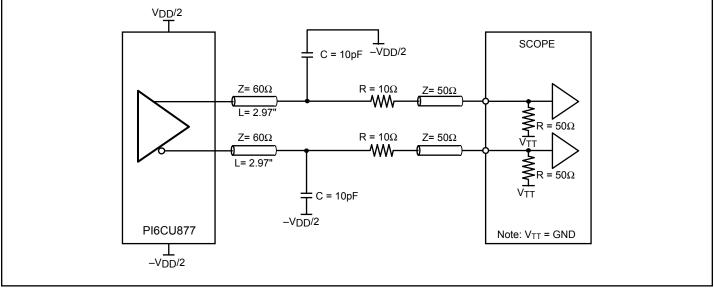

15. There are two terminations that are used with the above ac tests. The load/board in Figure 2 is used to measure the input and output differential-pair cross-voltage only. The load/board in Figure 3 is used to measure all other tests. For consistency, equal length cables should be used.

16. The Output slew rate is determined from IBIS model load shown in Figure 1. It is measured single-ended.

Figure 2. Output Load Test Circuit 1

Figure 3. Output Load Test Circuit 2

Figure 4. Cycle-to-Cycle Jitter

Figure 5. Static Phase Offset

### Figure 6. Output Skew

**Figure 7. Period Jitter** (fo = average input frequency measured at  $CK/\overline{CK}$ )

Figure 8. Half-Period Jitter

Figure 9. Input and Output Slew Rates

Figure 10. Dynamic Phase Offset

Figure 11. Time Delay Between Output Enable (OE) and Clock Output  $(\overline{Y}, Y)$

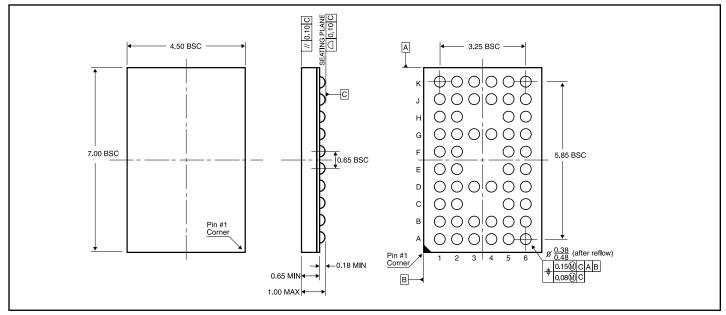

### Packaging Mechanical: 52-Pin VFBGA (NF)

### **Ordering Information**

| Ordering Code | Package Code | Package Description            |

|---------------|--------------|--------------------------------|

| PI6CU877NF    | NF           | 52-ball VFBGA                  |

| PI6CU877NFE   | NF           | Pb-free & Green, 52-ball VFBGA |

#### Notes:

1. Thermal characteristics can be found on the company web site at http://www.pericom.com/packaging/