SEMICONDUCTOR TM

# RM3283 Dual ARINC 429 Line Receiver

# Features

- Two separate analog receiver channels

- Converts ARINC 429 levels to serial data

- Built-in TTL compatible complete channel test inputs

- TTL and CMOS compatible outputs

- · Low power dissipation

- Internal bandgap

- · Short circuit protected

- Available in 20-Lead ceramic DIP

# Description

The RM3283 consists of two analog ARINC 429 receivers which take differentially encoded ARINC level data and convert it to serial TTL level data. The RM3283 provides two complete analog ARINC receivers and no external components are required. Input level shifting thin film resistors and bipolar technology allow ARINC input voltage transients up to  $\pm 100V$  without damage to the RM3283.

Each channel is identical, featuring symmetrical propagation delays for better high speed performance. Input common mode rejection is excellent and threshold voltage is stable, independent of supply voltage. Data outputs are TTL and CMOS compatible.

Two TTL compatible test inputs used to test the ARINC channels are available. They can be used to override the ARINC input data and set the channel outputs to a known state.

The Fairchild RM3182A line driver is the companion chip to the RM3283 line receiver. Together they provide the analog functions needed for the ARINC 429 interface. Digital data processing involving serial-to-parallel conversion and clock recovery can be accomplished using one of the ARINC interface IC's available or by an equivalent gate array implementation.

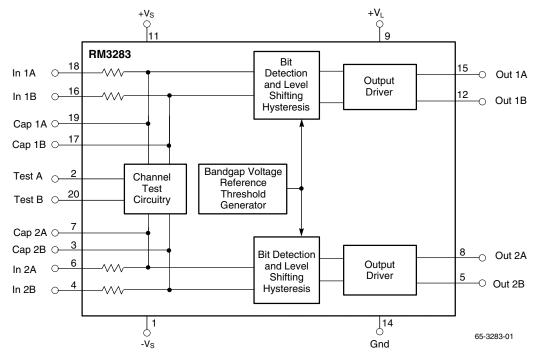

# **Block Diagram**

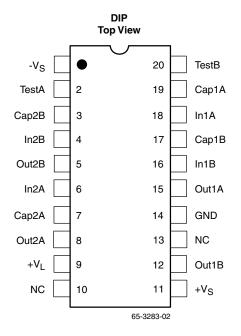

# **Pin Assignments**

# **Functional Description**

The RM3283 contains two discrete ARINC 429 receiver channels. Each channel contains three main sections: a resistor input network, a window comparator, and a logic output buffer stage. The first stage provides overvoltage protection and biases the signal using voltage dividers and current sources, providing excellent input common mode rejection. The test inputs are provided to set the outputs to a predetermined state for built-in channel test capability. If the test inputs are not used, they should be grounded. The window comparator section detects data from the resistor input network. A Logic 1 corresponds to ARINC "High" state (OUTA) and a Logic 0, to ARINC "Low" state (OutB). An ARINC "Null" state at the inputs forces both outputs to Logic 0. Threshold and hysteresis voltages are generated by a bandgap voltage reference to maintain stable switching characteristics over temperature and power supply variations.

The output stage generates a TTL compatible logic output capable of driving 3mA of load.

| Parameter                                            |                   | Min. | Max.         | Units |

|------------------------------------------------------|-------------------|------|--------------|-------|

| Supply Voltage (V <sub>CC</sub> to V <sub>EE</sub> ) |                   |      | +36          | V     |

| VLOGIC Voltage                                       |                   |      | +7           | V     |

| Logic Input Voltage                                  |                   | -0.3 | VLOGIC + 0.3 | V     |

| Temperature Range                                    | Storage           | -65  | +150         | °C    |

|                                                      | Operating         | -55  | +125         | °C    |

| Junction Temperature                                 |                   | -55  | +175         | °C    |

| Lead Soldering Temperature                           | 60 sec., DIP, LCC |      | +300         | °C    |

|                                                      | 10 sec., SOIC     |      | +260         | °C    |

# **Absolute Maximum Ratings**

### Thermal Characteristics (Still air, soldered on a PC board)

| Parameter                           | DIP                 |

|-------------------------------------|---------------------|

| Maximum Junction Temperature        | +175°C              |

| Thermal Resistance, $\theta_{JC}$   | 70°C/W              |

| Thermal Resistance, θ <sub>JC</sub> | 28°C/W <sup>1</sup> |

#### Note:

1. MIL-STD-1835.

### **DC Electrical Characteristics**

TA = -55°C to +125°C,  $\pm 12V \le VS \pm 15V$ , VL = +5V, unless otherwise noted.

| Symbol            | Parameter                               | Conditions                                     | Min. | Тур. | Max. | Units |

|-------------------|-----------------------------------------|------------------------------------------------|------|------|------|-------|

| ICC (+VS)         | Test inputs = 0V                        |                                                |      | 4.3  | 6.0  | mA    |

| IEE (-VS)         | Test inputs = 0V                        |                                                |      | 10.1 | 12.0 | mA    |

| IL (VL)           | Test inputs = 5V                        |                                                |      | 14.0 | 17.5 | mA    |

| VTL <sup>2</sup>  | V(A)-V(B)                               | Low threshold                                  | 4.7  | 5.0  | 5.3  | V     |

| VTH <sup>2</sup>  | V(A)-V(B)                               | High threshold                                 | 5.7  | 6.0  | 6.3  | V     |

| VIN               | V(A)-V(B)                               | OutA and OutB = 0                              | -2.5 | 0    | 2.5  | V     |

| VIC <sup>3</sup>  | V(A) and V(B)-GND                       | Maximum common mode<br>frequency = 80 kHz      |      | ±5   |      | V     |

| RI                | Input resistance, Input A to Input B    |                                                | 35   | 50   |      | kΩ    |

| RH                | Input resistance, Input A to Gnd        |                                                | 20   | 25   |      | kΩ    |

| RG                | Input resistance, B to Gnd              | Filter caps disconnected                       | 20   | 25   |      | kΩ    |

| Cl <sup>1,4</sup> | Input capacitance, A to B               |                                                |      |      | 10   | pF    |

| Сн <sup>1,4</sup> | Input capacitance, A to Gnd             | Filter caps disconnected                       |      |      | 10   | pF    |

| CG <sup>1,4</sup> | Input capacitance, B to Gnd             | Filter caps disconnected                       |      |      | 10   | pF    |

|                   | s (TestA, TestB)                        |                                                |      | •    |      |       |

| VIH <sup>5</sup>  | Logic 1 input voltage                   |                                                | 2.7  |      |      | V     |

| VIL <sup>5</sup>  | Logic 0 input voltage                   |                                                | 0    |      | 0.8  | V     |

| Ін                | Logic 1 input current                   | VIH = 5V                                       |      | 120  | 300  | μA    |

| lı∟               | Logic 0 input voltage                   | VIL = 0.8V                                     |      | 15   | 40   | μA    |

| Outputs           |                                         |                                                |      | •    |      |       |

| Voh               | IOH = 100 μA                            | TA = 25°C                                      | 4.0  | 4.3  |      | V     |

|                   | IOH = 2.8 mA                            | Full temperature range                         | 3.5  | 4.0  |      | V     |

| VOL               | IOL = 100 μA                            | TA = 25°C                                      |      | 0.02 | 0.1  | V     |

|                   | IOL = 2.0 mA                            | Full temperature range                         |      | 0    | 0.8  | V     |

| Tr <sup>6</sup>   | Rise Time                               | CL = 50 pF, @ 25°C                             |      | 50   | 70   | ns    |

| Tf <sup>6</sup>   | Fall Time                               | CL = 50 pF, @ 25°C                             |      | 40   | 70   | ns    |

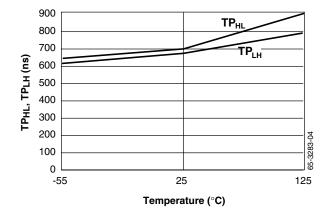

| TPLH              | Propagation delay<br>Output low to high | CL = 50 pF, f = 400 kHz<br>Filter caps = 39 pF |      | 700  |      | ns    |

| TPHL              | Output high to low                      | TA = 25°C                                      |      | 700  |      | ns    |

Notes:

1. As stated in ARINC429.

2. VT refers ot the threshold voltage at which the channels output switches from low to high or from high to low.

3. Common mode voltage present at both ARINC inputs.

4. Guaranteed by design.

5. Test inputs should be connected to ground if not used.

6. Sample tested.

# **Typical Performance Characteristics**

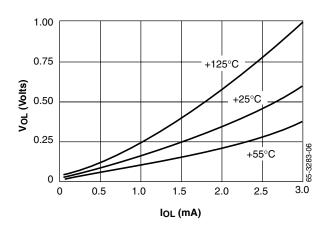

Figure 3. Output Voltage Low vs. Output Current

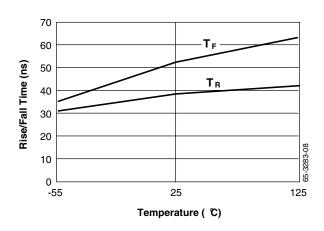

Figure 5. TR and TF vs. Temperature

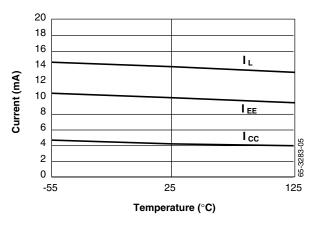

Figure 2. Supply Current vs. Temperature

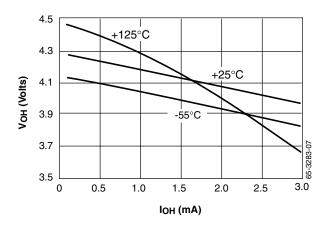

Figure 4. Output Voltage High vs. Output Current

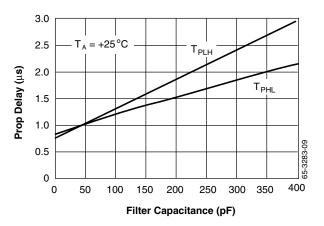

Figure 6. Propagation Delay vs. Filter Capacitance  $T_A = 25^{\circ}C$

### **AC Test Waveforms**

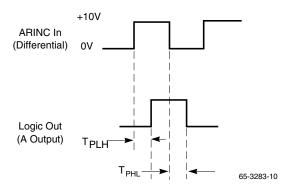

Figure 7. Propagation Delay

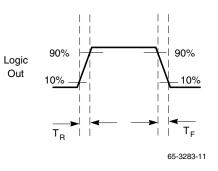

Figure 8. Rise/Fall Times

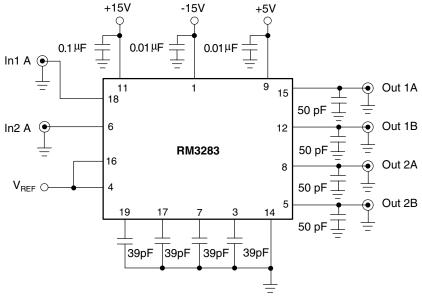

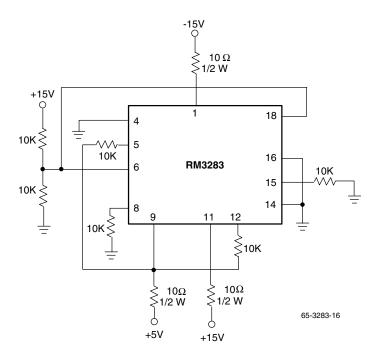

### **Test Circuit**

#### Notes:

- 1.  $V_{IN} = 400 \text{ kHz}$  square wave, -3.5V to +3.5V.

65-3283-12

- 2. Set V<sub>REF</sub> = +3.5 V to test V<sub>OUT1</sub> and V<sub>OUT3</sub>. Set V<sub>REF</sub> = -3.5 V to test V<sub>OUT2</sub> and V<sub>OUT4</sub>.

- 3. 50 pF load capacitance includes probe and wiring capacitance.

Figure 9. AC Test Schematic Diagram

| ARINC nputs | Test Inputs |       | Outputs |      | Output |  |

|-------------|-------------|-------|---------|------|--------|--|

| V(A) - V(B) | TESTA       | TESTB | OUTA    | OUTB | State  |  |

| Null        | 0           | 0     | 0       | 0    | Null   |  |

| Low         | 0           | 0     | 0       | 1    | Low    |  |

| High        | 0           | 0     | 1       | 0    | High   |  |

| Х           | 0           | 1     | 0       | 1    | Low    |  |

| Х           | 1           | 0     | 1       | 0    | High   |  |

| Х           | 1           | 1     | 0       | 0    | Null   |  |

#### **Truth Table**

# **Applications Discussion**

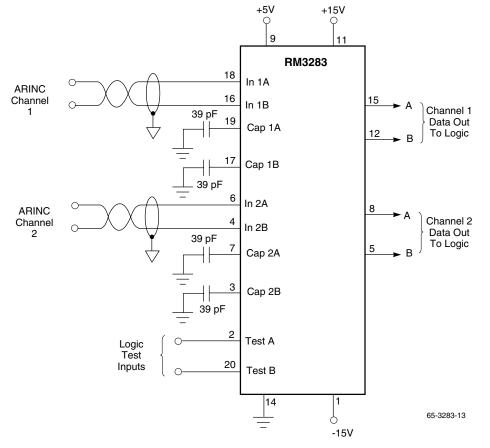

The standard connections for the RM3283 are shown in Figure 10. Dual supplies from  $\pm 12$  to  $\pm 15$  VDC are recommended for the  $\pm V_S$  supplies. Decoupling of all supplies should be done near the IC to avoid propagation of noise spikes due to switching transients. The ground connection should be sturdy and isolated from large switching currents to provide as quiet a ground reference as possible.

The noise filter capacitors are optional and are added to provide extra noise immunity by limiting bandwidth of the input signal before it reaches the window comparator stage. Two capacitors are required for each channel and they must all be the same value. The suggested capacitor value for a 100 kHz operation is 39 pF. For lower data rates, larger values of capacitance may be used to yield better node performance. To get optimum performance, the following equation can be used to calculate capacitor value for a specific data rate:

$$C_{\text{FILTER}} = \frac{3.95 \times 10^{-6}}{F_{\text{O}}}$$

Where C<sub>FILTER</sub> is the capacitor value in pF, and F<sub>O</sub> is the input frequency (10 kHz  $\leq$  F<sub>O</sub>  $\leq$  150 kHz).

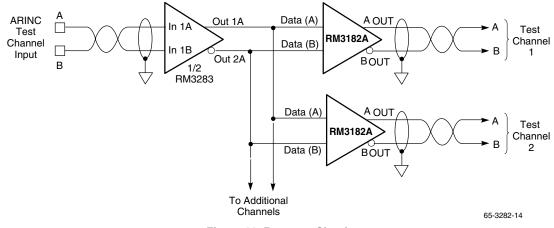

The RM3283 can be used with the Fairchild RM3182A line driver to provide a complete analog ARINC 429 interface. A simple application which can be used for systems requiring a repeater-type circuit for long transmissions is given in Figure 11. More RM3182A drivers may be added to test multiple ARINC channels, as shown.

# Applications

Figure 10. ARINC Receiver Standard Connections

### Applications (continued)

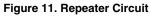

Figure 12. Four-Channel ARINC Receiver Circuit

Figure 13. Burn-In Circuit

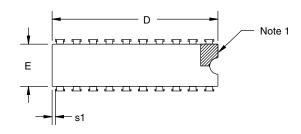

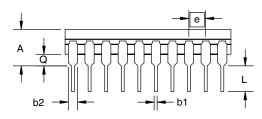

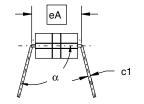

# **Mechanical Dimensions**

#### 20-Lead Ceramic DIP

| Symbol | Inc      | Inches Millimeters |      | neters | Notes |  |

|--------|----------|--------------------|------|--------|-------|--|

| Symbol | Min.     | Max.               | Min. | Max.   | Notes |  |

| А      | _        | .200               | -    | 5.08   |       |  |

| b1     | .014     | .023               | .36  | .58    | 8     |  |

| b2     | .045     | .065               | 1.14 | 1.65   | 2, 8  |  |

| c1     | .008     | .015               | .20  | .38    | 8     |  |

| D      |          | 1.060              |      | 25.92  | 4     |  |

| Е      | .220     | .310               | 5.59 | 7.87   | 4     |  |

| е      | .100 BSC |                    | 2.54 | BSC    | 5, 9  |  |

| eA     | .300     | BSC                | 7.62 | BSC    | 7     |  |

| L      | .125     | .200               | 3.18 | 5.08   |       |  |

| Q      | .015     | .060               | .38  | 1.52   | 3     |  |

| s1     | .005     | _                  | .13  |        | 6     |  |

| α      | 90°      | 105°               | 90°  | 105°   |       |  |

#### Notes:

- 1. Index area: a notch or a pin one identification mark shall be located adjacent to pin one. The manufacturer's identification shall not be used as pin one identification mark.

- 2. The minimum limit for dimension "b2" may be .023(.58mm) for leads number 1, 10, 11 and 20 only.

- 3. Dimension "Q" shall be measured from the seating plane to the base plane.

- 4. This dimension allows for off-center lid, meniscus and glass overrun.

- The basic pin spacing is .100 (2.54mm) between centerlines. Each pin centerline shall be located within ±.010 (.25mm) of its exact longitudinal position relative to pins 1 and 20.

- 6. Applies to all four corner's (leads number 1, 10, 11, and 20).

- 7. "eA" shall be measured at the center of the lead bends or at the centerline of the leads when " $\alpha$ " is 90°.

- 8. All leads Increase maximum limit by .003(.08mm) measured at the center of the flat, when lead finish is applied.

- 9. Eighteen spaces.

### **Ordering Information**

| Part Number | Package             | Operating Temperature Range |

|-------------|---------------------|-----------------------------|

| RM3283D     | 20 Lead Ceramic DIP | -55°C to +125°C             |

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com