SSOP8-P-0.50A

Weight: 0.01 g (typ.)

TOSHIBA CMOS Digital Integrated Circuits Silicon Monolithic

# TC9WMB1FK,TC9WMB2FK

TC9WMB1FK: 1024-Bit (128  $\times$  8 Bit) 2-Wire Serial E<sup>2</sup>PROM TC9WMB2FK: 2048-Bit (256  $\times$  8 Bit) 2-Wire Serial E<sup>2</sup>PROM

The TC9WMB1FK and TC9WMB2FK are electrically erasable/programmable nonvolatile memory (E<sup>2</sup>PROM).

#### **Features**

- 2-wire serial interface (I<sup>2</sup>C BUS<sup>TM</sup>) (Note 1)

- Single power supply

Read:  $V_{CC} = 1.8 \text{ to } 5.5 \text{ V}$ Write:  $V_{CC} = 2.3 \text{ to } 5.5 \text{ V}$

• Low power consumption: 5 μA (in standby state)

: 0.5 mA (in read state)

- Operating frequency: 400 kHz (V<sub>CC</sub> = 2.3 to 5.5 V)

- Byte write and page (8-byte) write

- Write protection

- · Sequential read

- Write time: 10 ms (V<sub>CC</sub> = 3.0 to 5.5 V) 12 ms (V<sub>CC</sub> = 2.3 to 2.7 V)

- Write endurance: 10<sup>5</sup> times

Data retention: 10 years

- Wide operating temperature range: -40 to 85°C

- Package: US8

Note 1: I<sup>2</sup>C BUS is a trademark of Royal Philips Electronics N.V.

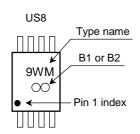

### **Product Marking**

## Pin Assignment (top view)

Purchase of TOSHIBA  $I^2C$  components conveys a license under the Philips  $I^2C$  Patent Rights to use these components in an  $I^2C$  system, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

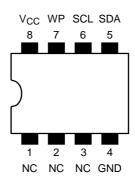

## **Block Diagram**

### **Pin Function**

| Pin Name | Input/Output | Description                                                                                                                    |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------|

| SCL      | Input        | Serial clock input  Data is fetched on a rising edge of SCL. Data is output on a falling edge of SCL.                          |

| SDA      | Input/output | Serial input/output  This pin must be pulled up with a resistor because it is configured as an N-ch open-drain pin for output. |

| WP       | Input        | Write protection input A high on this input disables writing. A low on this input enables writing.                             |

| NC       | _            | No connection (not connected internally)                                                                                       |

| Vcc      | Power supply | 1.8 to 5.5 V (for reading) 2.3 to 5.5 V (for writing)                                                                          |

| GND      |              | 0 V (GND)                                                                                                                      |

### **Functional Description**

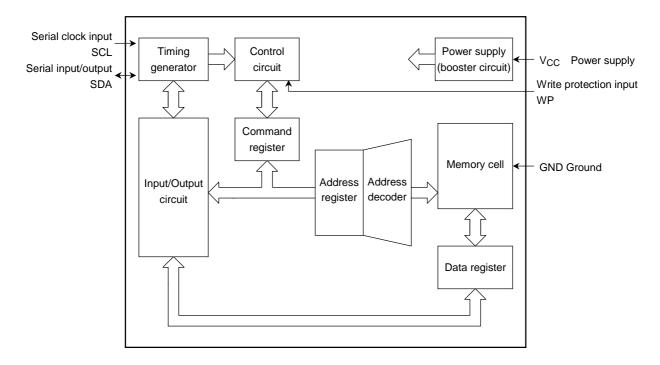

#### 1. Start and Stop Conditions

When SCL is high, pulling SDA low produces a start condition and pulling SDA high produces a stop condition. Every instruction is started when a start condition occurs and terminated when a stop condition occurs.

During a read, a stop condition causes the read to terminate and the chip to enter the standby state. During a write, a stop condition causes the fetching of write data to terminate, after which writing starts automatically. Upon the completion of writing, the chip enters the standby state.

Two or more start conditions cannot be entered consecutively.

Figure 1

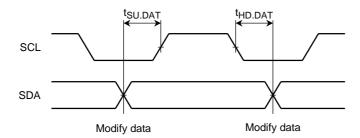

#### 2. Modifying Data

Data on the SDA input can be modified while SCL is low. When SCL is high, modifying the SDA input means a start or stop condition.

Figure 2

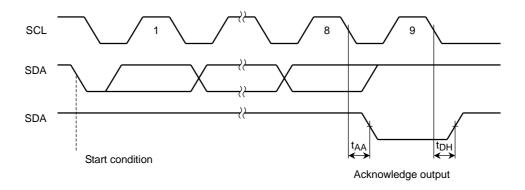

#### 3. Acknowledge

Data is transmitted and received in 8-bit units. The receiver sends an acknowledge signal by outputting a low on SDA in the 9th clock cycle, indicating that it has received data normally. The transmitter releases the bus in the 9th clock cycle to receive an acknowledge signal.

During a write, the chip is always the receiver so that it outputs an acknowledge signal each time it has received eight bits of data.

During a read, the chip outputs an acknowledge signal after it receives an address following a start condition. Then, it outputs read data and releases the bus to wait for an acknowledge signal from the master. When it detects an acknowledge signal, it outputs data at the next address if it does not detect a stop condition. If the chip does not detect an acknowledge signal, it stops read operation, and enters the standby state when a stop condition occurs subsequently.

If the chip does not detect an acknowledge signal nor a stop condition, it keeps the bus released.

Figure 3

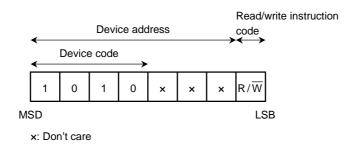

#### 4. Device Addressing

After a start condition occurs, a 7-bit device address and a 1-bit read/write instruction code are input to the chip.

The upper four bits are called device code, which must always be "1010". The next three bits are used to select a device on the bus. These three bits are not specified for this IC and can be set to any value.

The least significant bit ( $R/\overline{W}$ : READ/ $\overline{WRITE}$ ) indicates a read instruction when set to 1 and a write instruction when set to 0.

An instruction is not executed if the device address does not match the specified value.

Figure 4

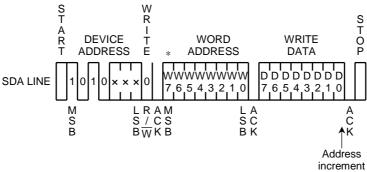

#### 5. Write Operation

#### (1) Byte write

A byte write writes data to a specified address. After a start condition, input a device address,  $R/\overline{W}$  (= 0), a word address, and write data.

When a stop condition is entered subsequently, write operation starts automatically, rewriting the data at the specified address with the input data. A next instruction cannot be accepted while write operation is in progress. Therefore, no acknowledge signal is returned. After writing the data, the chip automatically enters the standby state.

\*: Don't care for the TC9WMB1

Figure 5

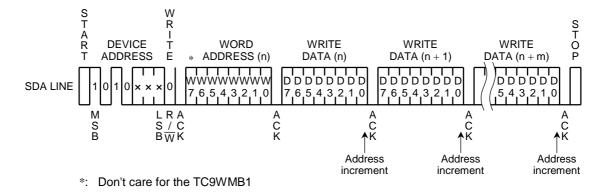

#### (2) Page write

A page write writes up to eight bytes of data collectively to a specified page. After a start condition, input a device address,  $R/\overline{W}$  (= 0), a word address (n), and write data (n), in the same way as for a byte write. Then, input write data (n + 1) immediately without entering a stop condition, while checking that an acknowledge signal is asserted (0).

The upper four bits (A3 to A6) of the word address are fixed and the lower three bits (A0 to A2) are automatically incremented so that up to eight bytes of data can be input.

When the last address within the page is reached, the lower three bits (A0 to A2) of the word address are rolled over to the first address of the page. If more than eight bytes of write data are input, the last eight bytes are valid.

When a stop condition is entered subsequently, write operation starts automatically, rewriting the data at the specified addresses with the input data.

Figure 6

#### (3) Acknowledge polling

Acknowledge polling is a feature for determining whether rewrite operation is in progress. During rewrite operation, input a start condition, a device address, and  $R/\overline{W}$  (= 0 or 1). The acknowledge feature does not output an acknowledge signal while rewrite operation is in progress. It outputs a low acknowledge signal if rewriting has already completed.

If the next instruction is a write, input a word address and write data subsequently. If the next instruction is a read, supply a stop condition and then start read operation.

#### (4) Write protection

Driving the write protection (WR) pin high causes the TC9WMB1FK to protect the entire memory area from being written and the TC9WMB2FK to protect the bottom half (80h to FFh) of the memory area from being written. Rewriting is allowed when the write protection pin is low. While a write is in progress, driving the WP pin high does not stop write operation.

Reading is always enabled regardless of whether the WP pin is high or low.

#### 6. Read Operation

Read operation is performed in one of three modes: current address read, random read, and sequential read.

For reading, enter a device address and R/W (= 1) after a start condition. After read data is output, terminate read operation by inputting a high acknowledge signal (or releasing the bus without supplying an acknowledge signal) and then supplying a stop condition.

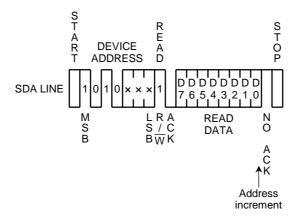

#### (1) Current address read

The internal address counter maintains the address that is next to the last accessed (read or written) word address (n). In current address read mode, data is read from address n + 1, as indicated by the address counter.

In current address read mode, entering a device address and R/W (= 1) after a start condition causes the chip to output a low acknowledge signal and then data at the address indicated by the internal address counter.

The address counter is incremented on a falling edge of the SCL pulse where the eighth bit is output. If the previous operation was reading data from the last address, the current address is rolled over to address 0. If the previous operation was writing data to the last address of the page, the address is rolled over to the first address of the page.

The current address is maintained in an internal register so that it is lost when the power is turned off. For the first read after power-up, specify an address by performing a random read.

Figure 7

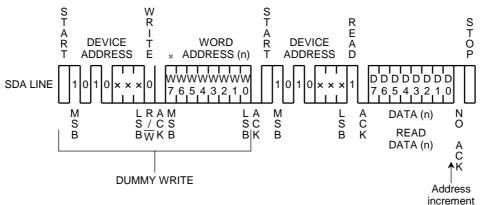

#### (2) Random read

A random read reads data at a specified address. A dummy write is necessary to specify an address. In random read mode, enter a device address, R/W (= 0), and a word address after a start condition. Unlike a byte or page write, where write data is entered immediately, a dummy write only specifies a word address. Then, supply a start condition and enter a device address and R/W (= 1) in the same way as for a current address read, to read data from the specified address.

\*: Don't care for the TC9WMB1

Figure 8

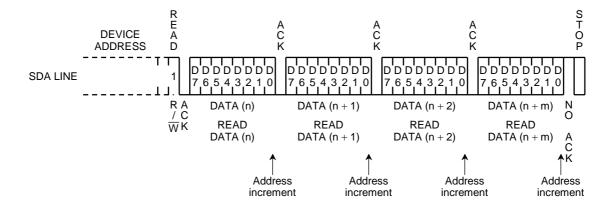

#### (3) Sequential read

A sequential read reads data sequentially from successive word addresses.

For either current address read or random read, after entering a start condition, a device address, and R/W (= 1), inputting a low acknowledge signal causes the word address to be incremented automatically to read data at the next address.

After the last address is reached, the word address is rolled over to address 0.

Figure 9

#### 7. Notes on Use

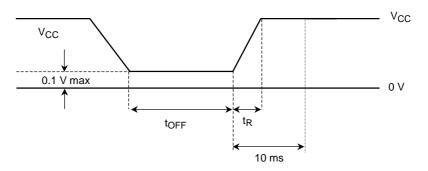

#### (1) Powering up the chip

This IC contains a power-on clear circuit, which initializes the internal circuit of the IC when the power is turned on. If initialization fails, the chip may malfunction. When powering up the chip, observe the following precautions to assure that the clear circuit will operate normally:

- (a) Pull SCL and SDA high.

- (b) The power rising time (tR) must be 10 ms or less.

- (c) After turning off the power, wait at least 100 ms (tOFF) before attempting to power up the chip again.

- (d) The supply voltage must rise from a voltage lower than 0.1 V.

- (e) After turning on the power, wait at least 10 ms before attempting to send an instruction to the chip.

Figure 10

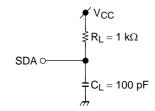

#### (2) Pulling up the SDA and SCL pins

This IC requires the SDA and SCL pins to be pulled up with an external resistor. The recommended pull-up resistance range is  $1 \text{ k}\Omega$  to  $10 \text{ k}\Omega$ .

#### (3) Noise elimination time for the SDA and SCL pins

This IC contains a low-pass filter for eliminating noise on the SDA and SCL pins. Its guaranteed value corresponds to the noise suppression time Ti, given in the AC characteristics table.

# Maximum Ratings (GND = 0 V)

| Characteristics       | Symbol           | Rating                     | Units |

|-----------------------|------------------|----------------------------|-------|

| Supply voltage        | V <sub>CC</sub>  | -0.3~7.0                   | V     |

| Input voltage         | V <sub>IN</sub>  | -0.3~V <sub>CC</sub> + 0.3 | V     |

| Output voltage        | V <sub>OUT</sub> | -0.3~V <sub>CC</sub> + 0.3 | ٧     |

| Power dissipation     | PD               | 200 (25°C)                 | mW    |

| Storage temperature   | T <sub>stg</sub> | -55~125                    | °C    |

| Operating temperature | T <sub>opr</sub> | -40~85                     | °C    |

# Recommended Operating Conditions (GND = 0 V, $T_{opr}$ = -40 to 85°C)

| Characteristics              | Symbol          | Test Condition                                        | Min                      | Max                      | Unit  |  |

|------------------------------|-----------------|-------------------------------------------------------|--------------------------|--------------------------|-------|--|

| Supply voltage (for reading) | V <sub>CC</sub> | _                                                     | 1.8                      | 5.5                      | V     |  |

| Supply voltage (for writing) | V <sub>CC</sub> | _                                                     | 2.3                      | 5.5                      | V     |  |

| High level input voltage     | VIH             | 2.3 V ≤ V <sub>CC</sub> ≤ 5.5 V                       | 0.7 ×<br>V <sub>CC</sub> | V <sub>CC</sub>          | V     |  |

| High-level input voltage     | VIH             | $1.8 \text{ V} \le \text{V}_{CC} < 2.3 \text{ V}$     | 0.8 ×<br>V <sub>CC</sub> | V <sub>CC</sub>          | v     |  |

| Low-level input voltage      | V <sub>IL</sub> | 2.3 V ≤ V <sub>CC</sub> ≤ 5.5 V                       | 0                        | 0.3 ×<br>V <sub>CC</sub> | V     |  |

| Low-level input voltage      | VIL.            | $1.8 \text{ V} \le \text{V}_{CC} < 2.3 \text{ V}$     | 0                        | 0.2 ×<br>V <sub>CC</sub> | V     |  |

| Operating frequency          | face            | $2.3 \text{ V} \leq \text{V}_{CC} \leq 5.5 \text{ V}$ | 0                        | 400                      | 1.11= |  |

|                              | fscl            | $1.8 \text{ V} \le \text{V}_{CC} < 2.3 \text{ V}$     | 0                        | 100                      | kHz   |  |

#### **Electrical Characteristics**

## DC Characteristics (GND = 0 V, $T_{opr} = -40$ to 85°C)

| Characteristics             | Symbol            | Test                      | $1.8 \le V_{CC} < 2.3 \text{ V}$ |      | $2.3 \le V_{CC} \le 3.6 \text{ V}$ |     | $4.5 \le V_{CC} \le 5.5 \text{ V}$ |     | - Unit |

|-----------------------------|-------------------|---------------------------|----------------------------------|------|------------------------------------|-----|------------------------------------|-----|--------|

| Characteristics             | Symbol            | Condition                 | Min                              | Max  | Min                                | Max | Min                                | Max | Offic  |

| Input current               | ILI               | _                         | _                                | ±1   | _                                  | ±1  | _                                  | ±1  | μА     |

| Output leakage current      | I <sub>LO</sub>   | _                         | _                                | ±1   | _                                  | ±1  | _                                  | ±1  | μА     |

| Low-level output voltage    | l V <sub>OI</sub> | $I_{OL} = 3.2 \text{ mA}$ | _                                | _    | _                                  | 0.4 | _                                  | 0.4 | V      |

| Low-level output voltage    |                   | $I_{OL} = 1.5 \text{ mA}$ | _                                | 0.5  | _                                  | _   | _                                  | _   | V      |

| Quiescent supply current    | I <sub>CC1</sub>  | _                         | _                                | 5    | _                                  | 5   | _                                  | 5   | μА     |

| Supply current during read  | I <sub>CC2</sub>  | f = 400 kHz               | _                                | 0.2* | _                                  | 0.3 | _                                  | 0.5 | mA     |

| Supply current during write | I <sub>CC3</sub>  | f = 400 kHz               | _                                | _    | _                                  | 1.5 | _                                  | 2.0 | mA     |

<sup>\*</sup>f = 100 kHz

## AC Characteristics (GND = 0 V, $T_{opr}$ = -40 to 85°C)

#### **Test Conditions**

| Input pulse voltage          | $0.1 \times V_{CC} \sim 0.9 \times V_{CC}$ |  |  |

|------------------------------|--------------------------------------------|--|--|

| Input rise/fall time         | 20 ns                                      |  |  |

| Input/output testing voltage | 0.5 × V <sub>CC</sub>                      |  |  |

| Output load                  | 100 pF + 1 kΩ pull-up resistor             |  |  |

| Characteristics            | Symbol              | 1.8 ≦ V <sub>C</sub> | <sub>C</sub> < 2.3 V | $2.3 \le V_{CC} \le 3.6 \text{ V}$ |     | 4.5 ≦ V <sub>C</sub> | C ≦ 5.5 V | Unit  |

|----------------------------|---------------------|----------------------|----------------------|------------------------------------|-----|----------------------|-----------|-------|

| Gharacteristics            | Symbol              | Min                  | Max                  | Min                                | Max | Min                  | Max       | Offic |

| SCL clock frequency        | f <sub>SCL</sub>    | 0                    | 100                  | 0                                  | 400 | 0                    | 400       | kHz   |

| SCL clock "low" time       | t <sub>LOW</sub>    | 4.7                  | _                    | 1.2                                | _   | 1.2                  | _         | μS    |

| SCL clock "high" time      | tHIGH               | 4.0                  | _                    | 0.6                                | _   | 0.6                  | _         | μS    |

| Noise suppression time     | t <sub>l</sub>      | _                    | 100                  | _                                  | 50  | _                    | 50        | ns    |

| SDA output delay           | t <sub>AA</sub>     | 0.1                  | 4.5                  | 0.1                                | 0.9 | 0.1                  | 0.9       | μS    |

| Bus free time              | t <sub>BUF</sub>    | 4.7                  | _                    | 1.2                                | _   | 1.2                  | _         | μS    |

| Start condition hold time  | t <sub>HD.STA</sub> | 4.0                  | _                    | 0.6                                | _   | 0.6                  | _         | μS    |

| Start condition setup time | tsu.sta             | 4.7                  | _                    | 0.6                                | _   | 0.6                  | _         | μS    |

| Data input hold time       | t <sub>HD.DAT</sub> | 0                    | _                    | 0                                  | _   | 0                    | _         | ns    |

| Data input setup time      | t <sub>SU.DAT</sub> | 250                  | _                    | 200                                | _   | 200                  | _         | ns    |

| SCL, SDA input rise time   | t <sub>R</sub>      | _                    | 1.0                  | _                                  | 0.3 | _                    | 0.3       | μS    |

| SCL, SDA input fall time   | t <sub>F</sub>      | _                    | 0.3                  | _                                  | 0.3 | _                    | 0.3       | μS    |

| Stop condition setup time  | tsu.sto             | 4.7                  | _                    | 0.6                                | _   | 0.6                  | _         | μS    |

| SDA output hold time       | t <sub>DH</sub>     | 100                  |                      | 50                                 | _   | 50                   | _         | ns    |

# E<sup>2</sup>PROM Characteristics (GND = 0 V, 2.3 V $\leq$ V<sub>CC</sub> $\leq$ 2.7 V, T<sub>opr</sub> = -40 to 85°C)

| Characteristics     | Symbol           | Test Condition | Min                 | Тур. | Max | Unit  |

|---------------------|------------------|----------------|---------------------|------|-----|-------|

| Write time          | t <sub>WR</sub>  | _              | _                   | _    | 12  | ms    |

| Rewrite endurance   | N <sub>EW</sub>  | _              | 1 × 10 <sup>5</sup> | _    | _   | Times |

| Data retention time | t <sub>RET</sub> | _              | 10                  | _    | _   | Years |

# E<sup>2</sup>PROM Characteristics (GND = 0 V, 2.7 V < $V_{CC} \le 5.5$ V, $T_{opr} = -40$ to $85^{\circ}$ C)

| Characteristics     | Symbol           | Test Condition | Min                 | Тур. | Max | Unit  |

|---------------------|------------------|----------------|---------------------|------|-----|-------|

| Write time          | t <sub>WR</sub>  | _              | _                   | _    | 10  | ms    |

| Rewrite endurance   | N <sub>EW</sub>  | _              | 1 × 10 <sup>5</sup> | _    | _   | Times |

| Data retention time | t <sub>RET</sub> | _              | 10                  | _    | _   | Years |

## **Capacitance Characteristics (Ta = 25°C)**

| Characteristics    | Symbol          | Test Condition | V <sub>CC</sub> (V) | Тур. | Unit |

|--------------------|-----------------|----------------|---------------------|------|------|

| Input capacitance  | C <sub>IN</sub> | _              | 5.0                 | 4    | pF   |

| Output capacitance | CO              | _              | 5.0                 | 3    | pF   |

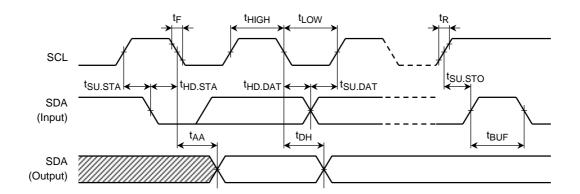

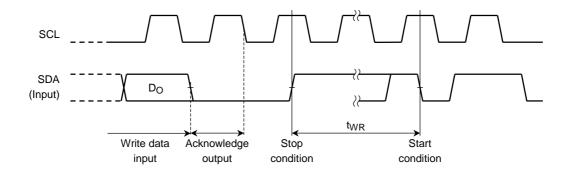

## **AC Characteristics Timing Charts**

Figure 11 Bus Timing

Figure 12 Write Cycle Timing

# **Input/Output Circuits of Pins**

| Pin | Туре         | Input/Output Circuit | Remarks           |

|-----|--------------|----------------------|-------------------|

| WP  | Input        |                      |                   |

| SCL | Input        |                      | _                 |

| SDA | Input/output |                      | Open-drain output |

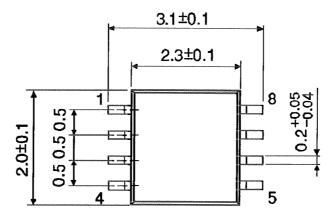

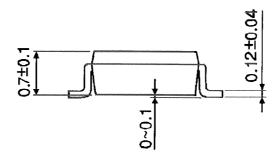

## **Package Dimensions**

SSOP8-P-0.50A Unit: mm

Weight: 0.01 g (typ.)

#### **RESTRICTIONS ON PRODUCT USE**

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No

responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other

rights of the third parties which may result from its use. No license is granted by implication or otherwise under

any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.