TOSHIBA BIPOLAR DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TD7614F

# 3-WIRE BUS, 1.3GHz-FREQUENCY SYNTHESIZER IC

#### **FEATURES**

- 3-wire bus system (software-compatible with TD6380 series).

- Built-in 4-band switch transistor.

- Built-in tuning amp (high withstanding voltage of 35V).

- Select switch can be selection of 31.25kHz, 50kHz or 62.5kHz frequency steps.

(Selected by open, V<sub>C</sub> or GND)

- Effects on sound signal suppressed by raising reference frequency.

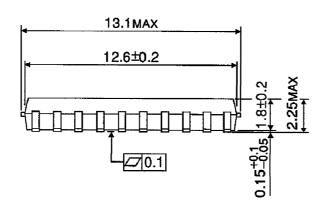

- Compact flat package: 20-pin FP (1.27mm pitch).

- Pin layout is mirror image of TD6380 series.

Weight: 0.25g (Typ.)

| FREQUENCY STEPS | CRYSTAL OSCILLATOR | SELECT SWITCH   |

|-----------------|--------------------|-----------------|

| 31.25kHz        | 4.0MHz             | GND             |

| 50.0kHz         | 3.2MHz             | V <sub>CC</sub> |

| 62.5kHz         | 4.0MHz             | Open            |

(Note) This product is susceptible to surge voltages, so should be used with extreme care.

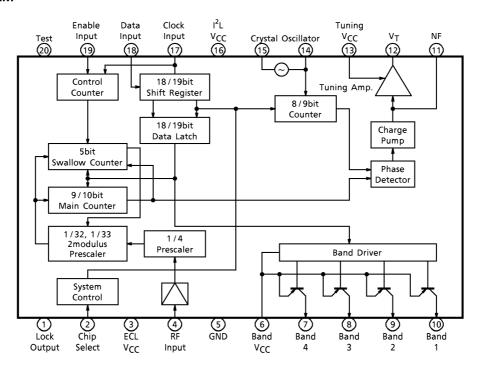

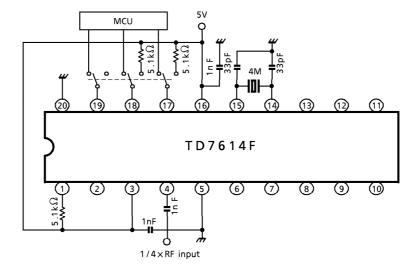

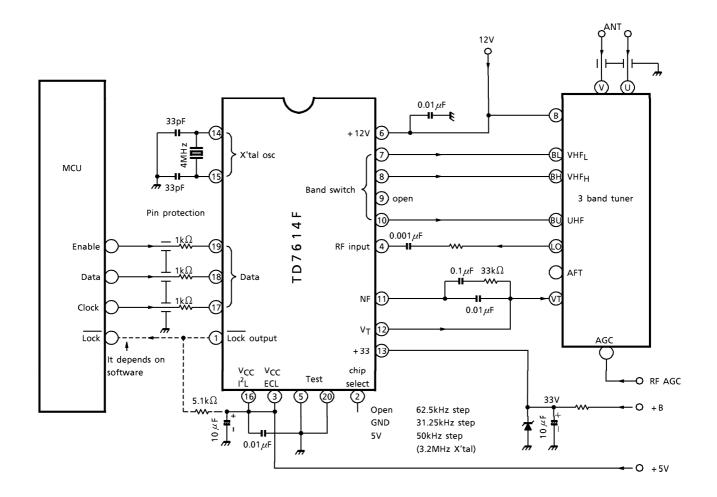

#### **BLOCK DIAGRAM**

## **TERMINAL FUNCTION**

| PIN<br>No. | PIN NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | INTERFACE CIRCUIT                                                       |

|------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 1          | Lock Output         | In normal use, connecting a $5.1k\Omega$ pull-up resistor to $V_{CC}$ sets this output to low level when the phase-locked loop (PLL) is locked. When the phase error of phase comparator continues less than $2\mu s$ and more than three cycles, the loop is regarded as locked. In test modes, this terminal switches test mode 1 or 2. In test mode 3, this pin functions as an output pin for the frequency divided (1/128) by the prescaler. When measuring the input sensitivity of the prescaler, connect a $1k\Omega$ pull-up resistor to the 0.4V power supply. The incoming current fluctuates the internal GND therefore avoid the apparent drop in input sensitivity. | C S I I VCC                                                             |

| 2          | Chip Select         | The internal reference frequency varies depending on the voltage applied. There are two internal thresholds; 1/3 V <sub>CC</sub> and 2/3 V <sub>CC</sub> . With open, the internal bias becomes 1/2 V <sub>CC</sub> . The frequency steps are as follows.  Open  : 4.0MHz ÷ 2 <sup>8</sup> × 4 = 62.5kHz  GND  : 4.0MHz ÷ 2 <sup>9</sup> × 4 = 31.25kHz  V <sub>CC</sub> : 3.2MHz ÷ 2 <sup>8</sup> × 4 = 50.0kHz                                                                                                                                                                                                                                                                  | ECL VCC  (2) (3) (3) (4) (4) (5) (7) (7) (7) (7) (7) (7) (7) (7) (7) (7 |

| 3          | ECL V <sub>CC</sub> | This teminal supplies current to the prescaler. Connect a capacitor to reduce impedance and thus eliminate power supply ripples.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                       |

| PIN<br>No. | PIN NAME              | FUNCTION                                                                                                                                                                                                        | INTERFACE CIRCUIT                                 |

|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 4          | RF Input              | Unlike current ICs, this IC has no reference terminal for input. Therefore, the GND and V <sub>CC</sub> impedance must be reduced sufficiently to suppress input terminal bias fluctuation due to interference. | 1.9V                                              |

| 5          | GND                   | Since the current for all blocks flows out of GND, be sure to make the pattern line as wide and short as possible, and certain to connect a capacitor to the power supply line.                                 | _                                                 |

| 6          | Band V <sub>C</sub> C | Due to the structure of the band driver circuit, use a voltage of between 8V and 14V.                                                                                                                           |                                                   |

| 7          | Band 4                | Can be driven at up to maximum 50mA per band. The voltage drop is below 0.15V (when V <sub>CC</sub> is 12V). Do not drive more than 2 bands                                                                     | <del>- ↑                                   </del> |

| 8          | Band 3                | simultaneously because of heat due to power consumption.  These terminals are built in                                                                                                                          | 7 1kΩ<br>8 9                                      |

| 9          | Band 2                | overcurrent protection circuits. When the terminal voltage drops below 4.5V, the internal                                                                                                                       | 260 D                                             |

| 10         | Band 1                | comparator is activated and driving stops. This mode continues until the terminal is no longer overloaded.                                                                                                      | π <i>π</i>                                        |

| 11         | NF                    | This terminal provides negative feedback for the active filter. The filtered current is amplified by the Darlington transistor then passed to the tuning amp.                                                   | ECL VCC                                           |

| PIN<br>No. | PIN NAME                         | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                       | INTERFACE CIRCUIT                        |

|------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 12         | VT                               | This terminal is for high-withstanding-voltage tuning amp output. There is no output voltage drop when V <sub>CC</sub> = 33V is applied.                                                                                                                                                                                                                                                                                       | 12 X Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z |

| 13         | Tuning V <sub>C</sub> C          | This terminal supplies current to the 30V tuning amp. Connect a capacitor between this terminal and GND.                                                                                                                                                                                                                                                                                                                       | _                                        |

| 14         | Countries Consideration          | These are crystal oscillator terminals used to generate the reference signal. The circuit consists of an inverter amp with a transistor. Since the reference                                                                                                                                                                                                                                                                   | 2 9.9kΩ 1000Ω 12·L VCC                   |

| 15         | Crystal Oscillator               | signal is transmitted forward from<br>the base of the transistor, when<br>the reference signal is derived<br>from other than the crystal<br>oscillator, connect them to pin 14.<br>Pin 15 is not used.                                                                                                                                                                                                                         |                                          |

| 16         | I <sup>2</sup> L V <sub>CC</sub> | This terminal supplies current to the logic. Connect a capacitor between this terminal and GND.                                                                                                                                                                                                                                                                                                                                | _                                        |

| 17         | Clock Input                      | In normal use, this terminal is used to input clock pulses. Since the input is received by the base of a PNP transistor, the incoming current is extremely small. In test modes 1 and 2, this terminal is used to output the reference signal obtained by dividing the crystal oscillator frequency. In test mode 3, the reference signal can be input externally, and the operation of the phase comparator can be monitored. |                                          |

| PIN<br>No. | PIN NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                         | INTERFACE CIRCUIT |

|------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 18         | Data Input   | Input interface circuit is the same as clock pin. In test modes 1 and 2, this terminal is used for main counter output.  In test mode 3, this terminal is used to input comparison signal of the phase comparator in order to compare the phase with that of the signal input from pin 17. (Data are output to the NF terminal). |                   |

| 19         | Enable Input | Input interface circuit is the same as clock terminal. In normal use, this terminal counts clocks from rise to fall of the enable signal. Clocks other than 18 or 19 are ignored. In the case of test mode, this terminal switches test modes.                                                                                   | 19 1kΩ 12L VCC    |

| 20         | Test         | Setting this terminal to low level (GND or open) results in normal tuning. Setting this terminal to high level (V <sub>CC</sub> : 5V) switches mode to test mode, enabling tests 1-3.                                                                                                                                            | 20kΩ<br>20 ¥ 20kΩ |

## **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL           | RATING          | UNIT |

|-----------------------|------------------|-----------------|------|

| Supply Voltage 1      | V <sub>CC1</sub> | 6.0             | V    |

| Supply Voltage 2      | V <sub>CC2</sub> | 6.0             | V    |

| Supply Voltage 3      | V <sub>CC3</sub> | 15              | V    |

| Supply Voltage 4      | V <sub>CC4</sub> | 35              | V    |

| Power Dissipation     | PD               | 925             | mW   |

| Operating Temperature | T <sub>opr</sub> | <b>- 20∼75</b>  | °C   |

| Storage Temperature   | T <sub>stg</sub> | <b>-</b> 55∼150 | °C   |

(Note) When using the device at above  $Ta = 25^{\circ}C$ , decrease the power dissipation by 7.4mW for each increase of 1°C.

## **RECOMMENDED SUPPLY VOLTAGE**

| PIN<br>No. | PIN NAME                         | MIN. | TYP. | MAX. | UNIT |

|------------|----------------------------------|------|------|------|------|

| 3          | ECL V <sub>CC</sub>              | 4.5  | 5.0  | 5.5  | V    |

| 16         | I <sup>2</sup> L V <sub>CC</sub> | 4.5  | 5.0  | 5.5  | V    |

| 6          | Band Driver V <sub>CC</sub>      | 8    | 12   | 13.2 | V    |

| 13         | Tuning V <sub>C</sub> C          | _    | 33   | 34   | V    |

## **ELECTRICAL CHARACTERISTICS** (Unless otherwise specified, V<sub>CC1</sub> = 5V, V<sub>CC2</sub> = 12V, V<sub>CC3</sub> = 33V, Ta = 25°C)

| CHARACTERIS                        |               | SYMBOL              | TEST<br>CIR-<br>CUIT | TEST CONDITION                     | MIN. | TYP. | MAX. | UNIT         |

|------------------------------------|---------------|---------------------|----------------------|------------------------------------|------|------|------|--------------|

| Supply Current 1                   |               | l <sub>CC1</sub>    |                      | ECL                                | 20   |      | 50   |              |

| Supply Current 2                   |               | l <sub>CC2</sub>    | 1                    | I <sup>2</sup> L                   |      |      | 25   |              |

| Supply Current 3                   |               | ICC3                | 1                    | Turns on a band driver             |      | 55   | 65   |              |

| Supply Current 4                   |               | I <sub>CC4</sub>    |                      |                                    |      | 5    | 10   | mA           |

| Band Driver Driver<br>Current      | e             | I <sub>BD</sub>     | 1                    |                                    |      | 50   | 55   |              |

| Band Driver Driver Voltage Drop    | e             | V <sub>BD</sub> SAT | 1                    | I <sub>BD</sub> = 50mA             |      |      | 0.15 | V            |

| Tuning Amp Out<br>Low-Level Voltag | •             | V <sub>TOUT</sub>   | 2                    |                                    |      | 0.6  |      | v<br>        |

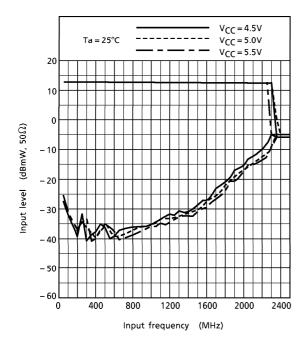

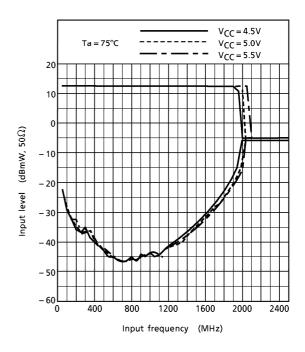

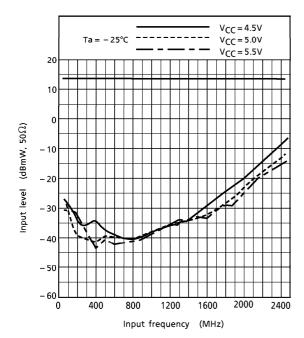

| Prescaler Input                    |               | V <sub>IN1</sub>    |                      | f = 80~150MHz                      | - 20 |      | 3    | dBmW         |

| Sensitivity                        |               | V <sub>IN2</sub>    | 3                    | f = 150~1000MHz                    | - 27 | _    | 3    | $(50\Omega)$ |

| Sensitivity                        |               | V <sub>IN3</sub>    |                      | f = 1.0~1.3GHz                     | - 20 | _    | 3    | (3022)       |

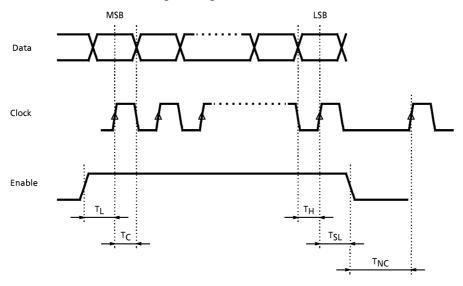

| Clock Pulse Widt                   | h             | T <sub>C</sub>      |                      | duty = 50%                         | 3    |      |      |              |

| Data Hold Time                     |               | TH                  |                      | duty = 50%                         | 3    |      |      | ] <b> </b>   |

| Enable Set Up Ti                   |               | TL                  | 2                    |                                    | 10   |      |      | ,,,          |

| <b>Enable Hold Tim</b>             | e             | T <sub>SL</sub>     |                      |                                    | 3    |      |      | $\mu$ s      |

| Next Clock Disab<br>Time           | le            | T <sub>NC</sub>     |                      |                                    | 7    |      |      |              |

| Selector Switch<br>Threshold       | High<br>Level | V <sub>th</sub> H   | 2                    |                                    | 3.0  | 3.3  | 3.6  | V            |

| Voltage                            | Low<br>Level  | V <sub>th</sub> L   |                      |                                    | 1.4  | 1.7  | 2.0  | V            |

| Bus Interface<br>Pin Input         | High<br>Level | I <sub>BI</sub> H   | 2                    | Applies to enable, data, and clock |      |      | 10   |              |

| Current                            | Low<br>Level  | I <sub>BI</sub> L   | _                    | Applies to enable, data, and clock | - 20 |      |      | $\mu$ A      |

| Bus Interface<br>Pin Input         | High<br>Level | V <sub>BI</sub> H   | 2                    | Applies to enable, data, and clock | 3.0  |      |      | V            |

| Voltage                            | Low<br>Level  | V <sub>BI</sub> L   |                      | Applies to enable, data, and clock |      |      | 0.8  | V            |

| CHARACTERIS                  | STIC          | SYMBOL            | TEST<br>CIR-<br>CUIT | TEST CONDITION                   | MIN. | TYP. | MAX. | UNIT        |

|------------------------------|---------------|-------------------|----------------------|----------------------------------|------|------|------|-------------|

| Output Mode                  | High<br>Level | V <sub>LO</sub> H | 4                    | Applies to lock, data, and clock | 3.0  |      |      | V           |

| Output Voltage               | Low<br>Level  | V <sub>LO</sub> L | 4                    | Applies to lock, data, and clock |      |      | 0.8  | <b>&gt;</b> |

| Selector Switch C<br>Voltage | Open          | V <sub>th</sub> O | 2                    |                                  | 2.2  | 2.5  | 2.8  | ٧           |

#### **TEST MODE OPERATION**

Setting the test terminal (pin 20) to high level enters test modes. There are three kinds of test modes as follows:

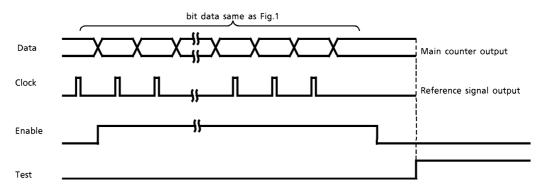

#### (1) Test modes 1 and 2

Test modes 1 and 2 are used to test the PLL lock state. After data are input to the main counter and swallow counter, set the test terminal (pin 20) to high level while keeping the enable terminal (pin 19) at low level. In this state, the comparison frequency signal is output to the clock terminal (pin 17) and main counter division signal to the data terminal (pin 18). The high-frequency signal is input from the RF input terminal (pin 4).

The prescaler divider ratio can be switched by changing the voltage applied to the lock output terminal (pin 1).

Lock output (pin 1) applied voltage at high level: 1/4 divider ratio Lock output (pin 1) applied voltage at low level: 1/1 divider ratio

#### (2) Test mode 3

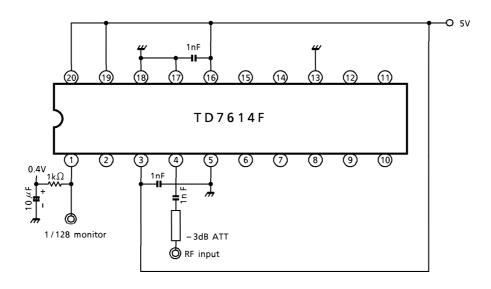

Test mode 3 is used to test the prescaler, phase comparator, and charge pump. Setting both the test terminal (pin 20) and the enable terminal (pin 19) to high level enters test mode 3. The comparison frequency signal of phase comparator is input from the clock terminal (pin 17), the comparated frequency signal is input from the data terminal (pin 18), and the prescaler output (fixed at 1/128 divider ratio) is output to the lock output terminal (pin 1).

The output polarity of phase comparator is as follows.

| INPUT FREQUENCY                                                                 | NF OUTPUT PIN (pin 11) |

|---------------------------------------------------------------------------------|------------------------|

| Input frequency>programmed frequency                                            | High level             |

| Input frequency <programmed frequency<="" td=""><td>Low level</td></programmed> | Low level              |

### **TEST MODE**

| PIN NAME              | MODE 1                                                            | MODE 2                                                                         | MODE 3                                                    |

|-----------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------|

| Lock output (pin 1)   | High level                                                        | Low level                                                                      | 1/128                                                     |

| RF input (pin 4)      | RF input<br>(1/4 normal mode<br>frequency input)                  | RF input                                                                       | RF input                                                  |

| Clock input (pin 17)  | Select switch (pin 2) Open: 15.625kHz VCC: 12.5kHz GND: 7.8125kHz | Select switch (pin 2) Open: 15.625kHz V <sub>CC</sub> : 12.5kHz GND: 7.8125kHz | The reference signal input of phase comparator            |

| Data input (pin 18)   | Main counter output                                               | Main counter output                                                            | The comparated frequency signal input of phase comparator |

| Enable input (pin 19) | Low level                                                         | Low level                                                                      | High level                                                |

| Test (pin 20)         | High level                                                        | High level                                                                     | High level                                                |

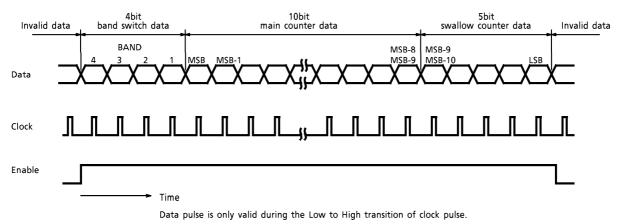

#### TIMING OF DATA INPUT

The method of inputting data will be indicated in the diagram 1.

## **COMPUTATION OF LOCK FREQUENCY**

Lock frequency is calculated as follows:

$f_{OSC} = f_r \times 4 \times (32M + S)$

fOSC: The oscillation frequency of VCO (the input frequency signal of a prescaler)

$f_{\Gamma}\ \ :\ Reference\ frequency\ :\ it\ will\ be\ 1/2^{8}\ or\ 1/2^{9}\ of\ the\ oscillation\ frequency\ of\ a\ crystal$

oscillator.

M : Preset value of Main counter.

S : Preset value of Swallow counter.

| SELECTION (Pin 2)   | OPEN                  | V <sub>CC</sub>         | GND                   |

|---------------------|-----------------------|-------------------------|-----------------------|

| Main Counter        | 9bit                  | 10bit                   | 10bit                 |

| Swallow Counter     | 5bit                  | 5bit                    | 5bit                  |

| Reference Frequency | 15.625kHz             | 12.5kHz                 | 7.8125kHz             |

|                     | 4MHz / 2 <sup>8</sup> | 3.2MHz / 2 <sup>8</sup> | 4MHz / 2 <sup>9</sup> |

| Frequency Step      | 62.5kHz               | 50kHz                   | 31.25kHz              |

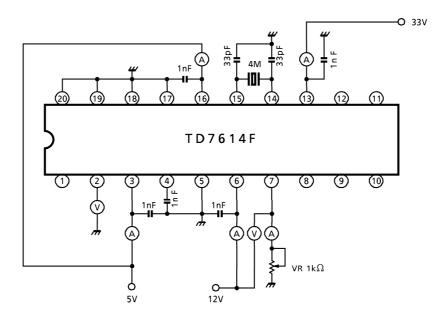

Fig.1 Normal use

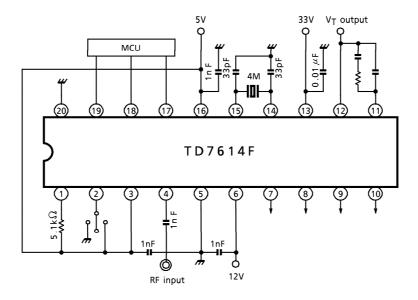

Fig.2 Test mode (mode 1, 2)

Fig.3 Timing chart of 3 wire-bus (rising timing)

**TEST CIRCUIT 1.** Supply test circuit

TEST CIRCUIT 2. AC operating test circuit

TEST CIRCUIT 3. Input sensitivity test circuit

## TEST CIRCUIT 4. Output mode test circuit

## APPLICATION CIRCUIT EXAMPLE OF FREQUENCY SYNTHESIZER

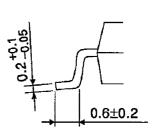

Unit: mm

## **PACKAGE DIMENSIONS**

SOP20-P-300-1.27

Weight: 0.25g (Typ.)

#### RESTRICTIONS ON PRODUCT USE

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.