TH8082

# Single LIN Bus Transceiver

### Features and Benefits

- □ Single wire LIN transceiver

- □ Compatible to LIN Protocol Specification, Rev. 1.1

- □ Compatible to ISO9141 functions

- Control Output for voltage regulator

- Up to 20 kbps bus speed

- Low RFI due to slew rate control

- Fully integrated receiver filter

- Protection against load dump, jump start

- Bus terminals proof against short-circuits and transients in the automotive environment

- □ Very low (25 µA) typical power consumption in sleep mode

- Thermal overload and short circuit protection

- □ High impendance Bus pin in case of loss of ground and undervoltage condition

- $\Box$  ± 4kV ESD protection on bus pin

### Ordering Information

| Part No.   | Temperature Range | Package       |

|------------|-------------------|---------------|

| TH8082 JDC | -40°C125°C        | SOIC8, 150mil |

### General Description

The TH8082 is a physical layer device for a single wire data link capable of operating in applications where high data rate is not required and a lower data rate can achieve cost reductions in both the physical media components and in the microprocessor which use the network. The TH8082 is designed in accordance to the physical layer definition of the LIN Protocol Specification , Rev. 1.2 . The IC furthermore can be used in ISO9141 systems.

Because of the very low current consumption of the TH8082 in the recessive state it's particularly suitable for ECU applications with hard standby current requirements. An advanced sleep mode capability allows a shutdown of the whole application . The included wake-up function detects incoming dominant bus messages and enables the voltage regulator.

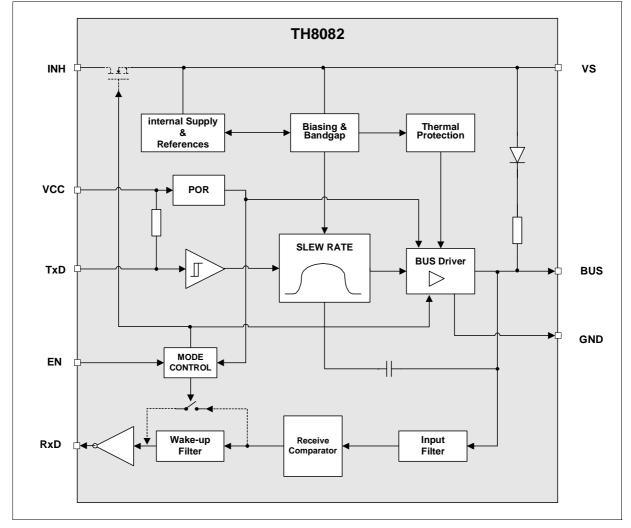

## Functional Diagram

Figure 1 - Block Diagram

## Functional Description

After *power on* the chip automatically enters the  $V_{BAT}$ stanby mode . In this intermediate mode the INH output will become HIGH (V<sub>s</sub>) and therefore the voltage regulator will provide the  $V_{CC}$  - supply . The transceiver will remain the  $V_{BAT}$ -stanby mode until the controller sets it to *normal operation* (EN = High). Only in this mode bus communication is possible. The TH8082 switches itself in the  $V_{BAT}$ -stanby mode if  $V_{CC}$  is missing or below the threshold.

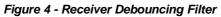

The *sleep mode* (EN = LOW) can only be reached from normal mode and permits a very low power consumtion because the transceiver and even the external voltage regulator get disabled. If the V<sub>CC</sub> has been switched off a

wake-up request from the bus line will cause the TH8082 to enter the  $V_{BAT}$ -stanby mode ( $V_{CC}$  is present again) and sets the RxD output to low until the device enters the normal operation mode (active LOW interrupt at RxD). If the INH pin is not connected to the regulator or the inhibitable external regulator is not the one that provides the  $V_{CC}$  – supply, the normal mode is directly accessible by a logic high on the EN pin.

In order to prevent an unintended wake-up caused by disturbances of the automotiv environment incoming dominant signals from the bus have to exceed the wake-up delay time.

| EN | VCC | Comment                                                                                                                              | INH      | RxD                                                 |

|----|-----|--------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------|

| 0  | 0   | $V_{\text{BAT}}\text{-}\text{standby}$ , power on                                                                                    | Vs       | 0                                                   |

| 0  | 1   | $V_{\text{BAT}}\mbox{-standby}$ , $V_{\text{CC}}$ on , wake up condition after power on                                              | Vs       | Active LOW<br>wake-up interrupt                     |

| 1  | 1   | Normal mode , $V_{CC}$ on                                                                                                            | Vs       | 1 = recessive bus<br>0 = dominant bus               |

| 1  | 0   | $V_{\text{BAT}}\text{-}\text{standby}$ , VCC missing (V_{CC} < V_{\text{CCUV}})                                                      | Vs       | V <sub>cc</sub>                                     |

| 0  | 0   | Sleep mode, switch to $V_{\text{BAT}}$ -standby in case of wake-up request                                                           | floating | Active LOW wake-up interrupt if $V_{CC}$ is present |

| 0  | 1   | Sleep mode, regulator not disabled, switch to $V_{BAT}$ -standby in case wake-up request, directly switch to normal mode with EN = 1 | floating | Active LOW<br>wake-up interrupt                     |

#### Mode Control of TH8082

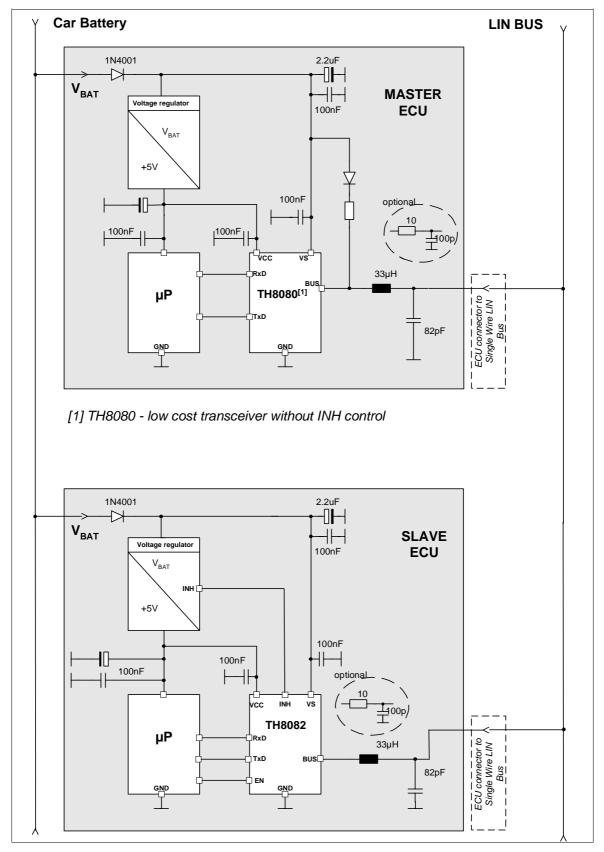

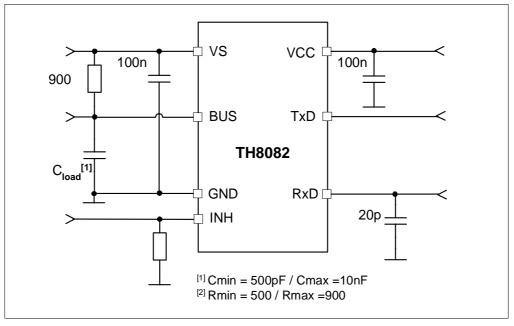

## Application Circuit

Figure 2 - Application Circuit

## Electrical Specification

All voltages are referenced to ground (GND). Positive currents flow into the IC. The absolute maximum ratings given in the table below are limiting values that do not lead to a permanent damage of the device but exceeding any of these limits may do so. Long term exposure to limiting values may affect the reliability of the device. Reliable operation of the TH8082 is only specified within the limits shown in "Operating conditions".

### **Operating Conditions**

| Parameter                           | Symbol          | Min | Max  | Unit |

|-------------------------------------|-----------------|-----|------|------|

| Battery voltage                     | Vs              | 6   | 18   | V    |

| Supply voltage                      | V <sub>cc</sub> | 4.5 | 5.5  | V    |

| Operating ambient temperature       | T <sub>A</sub>  | -40 | +125 | °C   |

| Junction temperature <sup>[1]</sup> | T <sub>Jc</sub> |     | +150 | °C   |

#### Absolute Maximum Ratings

| Parameter                                  | Symbol               | Conditions                                                 | Min.       | Max. | Unit |

|--------------------------------------------|----------------------|------------------------------------------------------------|------------|------|------|

| Batterry Supply Voltage                    | Vs                   | t < 1 min                                                  | -0.3       | +30  | V    |

| Supply Voltage                             | V <sub>cc</sub>      |                                                            | -0.3       | +7   | V    |

| Short-term supply voltage                  | $V_{\text{S.Id}}$    | Load dump; t<500ms                                         |            | +40  | V    |

| Transient supply voltage                   | V <sub>S.tr1</sub>   | ISO 7637/1 pulse 1 <sup>[1]</sup>                          | -150       |      | V    |

| Transient supply voltage                   | V <sub>S.tr2</sub>   | ISO 7637/1 pulses 2 <sup>[1]</sup>                         |            | +100 | V    |

| Transient supply voltage                   | V <sub>S.tr3</sub>   | ISO 7637/1 pulses 3A, 3B                                   | -150       | +150 | V    |

| BUS voltage                                | V <sub>BUS</sub>     | t < 500 ms, V <sub>S</sub> = 20 V<br>V <sub>S</sub> = 20 V | -20<br>-40 | +40  | V    |

| Transient bus voltage                      | V <sub>BUS.tr1</sub> | ISO 7637/1 pulse 1 [2]                                     | -150       |      | V    |

| Transient bus voltage                      | V <sub>BUS.tr2</sub> | ISO 7637/1 pulses 2 <sup>[2]</sup>                         |            | +100 | V    |

| Transient bus voltage                      | V <sub>BUS.tr3</sub> | ISO 7637/1 pulses 3A, 3B <sup>[2]</sup>                    | -150       | +150 | V    |

| DC voltage on pins TxD, RxD                | V <sub>DC</sub>      |                                                            | -0.3       | +7   | V    |

| ESD capability of pin BUS                  | ESD <sub>BUSHB</sub> | Human body model, equivalent                               | -4         | +4   | kV   |

| ESD capability of any other pins           | ESD <sub>HB</sub>    | Human body model, equivalent                               | -2         | +2   | kV   |

| Maximum latch – up free current at any Pin | I <sub>LATCH</sub>   |                                                            | -500       | +500 | mA   |

| Maximum power dissipation                  | P <sub>tot</sub>     | At T <sub>amb</sub> = +125 °C                              |            | 197  | mW   |

| Thermal impedance                          | $\Theta_{JA}$        | in free air                                                |            | 152  | K/W  |

| Storage temperature                        | T <sub>stg</sub>     |                                                            | -55        | +150 | °C   |

| Junction temperature                       | T <sub>vj</sub>      |                                                            | -40        | +150 | °C   |

### Static Characteristics

$(V_S = 6 \text{ to } 18V, V_{CC} = 4.5 \text{ to } 5.5V, T_A = -40 \text{ to } +125^{\circ}C, \text{ unless otherwise specified})$ All voltages are referenced to ground (GND), positive currents are flow into the IC.

| Parameter                                  | Symbol                      | Conditions                                                      | Min                          | Тур                  | Max                  | Unit |

|--------------------------------------------|-----------------------------|-----------------------------------------------------------------|------------------------------|----------------------|----------------------|------|

| PIN VS,VCC                                 |                             |                                                                 |                              |                      |                      |      |

| Supply current, dominant                   | I <sub>Sd</sub>             | V <sub>S</sub> = 18V,V <sub>CC</sub> = 5.5V, TxD=L              |                              |                      | 50                   | μA   |

| Supply current, dominant                   | I <sub>CCd</sub>            | $V_{S} = 18V, V_{CC} = 5.5V, TxD=L$                             |                              |                      | 1                    | mA   |

| Supply current, recessive                  | I <sub>Sr</sub>             | $V_{S} = 18V, V_{CC} = 5.5V TxD = H$                            |                              | 8                    | 20                   | μA   |

| Supply current, recessive                  | I <sub>CCr</sub>            | $V_{S} = 18V, V_{CC} = 5.5V TxD = H$                            |                              | 20                   | 30                   | μA   |

| V <sub>CC</sub> undervoltage lockout       | V <sub>CC_UV</sub>          | EN = H, TxD = L                                                 | 2.75                         |                      | 4.3                  | V    |

| Supply current, sleep mode                 | I <sub>Ss1</sub>            | $V_{S}$ = 18V, $V_{CC}$ = 0V TxD open                           |                              | 25                   | 50                   | μA   |

| PIN BUS / TRANSMITTER                      |                             |                                                                 |                              |                      |                      |      |

| Bus output voltage, dominant               | $V_{\text{ol}\_\text{BUS}}$ | TxD=L , $I_{BUS}$ = 40mA, $V_S$ > 7.3V                          |                              |                      | 1.2                  | V    |

| Bus output voltage, recessive              | $V_{\text{oh}\_\text{BUS}}$ | TxD=open                                                        | 0.8*<br>V <sub>S</sub> + 0.7 |                      |                      | V    |

| Bus short circuit current                  | I <sub>BUS_SHORT</sub>      | TxD=L , $V_{BUS} > 1.2V$ , $V_{S} > 7.3V$                       | 40                           |                      | 200                  | mA   |

| Bus input current, recessive               | I <sub>BUS_leakp</sub>      | TxD open , $V_{BUS} = Vs$                                       | -20                          |                      | 20                   | μA   |

| Bus reverse polarity curr., rec.           | I <sub>BUS_leakn</sub>      | Loss of GND , $V_S$ =12V, $V_{BUS}$ =0                          | -1                           |                      | 1                    | mA   |

| Bus pull up resistor                       | R <sub>BUS_pu</sub>         | TxD open, V <sub>BUS</sub> =0                                   | 20                           | 30                   | 47                   | kΩ   |

| PIN BUS / RECEIVER                         |                             |                                                                 |                              |                      |                      |      |

| Bus input threshold, recessive to dominant | $V_{\text{ihBUS}_{rd}}$     | TxD open ,<br>-8V <v<sub>BUS &lt; V<sub>ihBUS_rd</sub></v<sub>  | 0.4x V <sub>S</sub>          | 0.45* V <sub>S</sub> |                      | V    |

| Bus input threshold, dominant to recessive | $V_{\text{ihBUS}_{rd}}$     | TxD open ,<br>V <sub>ihBUS_rd</sub> <v<sub>BUS &lt; 18V</v<sub> |                              | 0.55* V <sub>S</sub> | 0.6*V <sub>s</sub>   | V    |

| Bus input hysteresis                       | $V_{BUS\_hys}$              |                                                                 | 20                           |                      |                      | mV   |

| PIN TXD, EN                                |                             |                                                                 |                              |                      |                      |      |

| High level input voltage                   | V <sub>ih</sub>             | Rising edge                                                     |                              |                      | 0.7* V <sub>CC</sub> | V    |

| Low level input voltage                    | V <sub>il</sub>             | Falling edge                                                    | 0.3* V <sub>CC</sub>         |                      |                      | V    |

| TxD pull up current, high level            | I <sub>IH_TXD</sub>         | $V_{TxD} = 4V$                                                  | -125                         | -50                  | -25                  | μA   |

| TxD pull up current, low level             | I <sub>IL_TXD</sub>         | V <sub>TxD</sub> = 1V                                           | -500                         | -250                 | -100                 | μA   |

| EN pull down current, high level           | I <sub>IH_EN</sub>          | $V_{EN} = 4V, V_{CC} = 0V$                                      | 50                           | 125                  | 250                  | μA   |

| EN pull down current, low level            | I <sub>IL_EN</sub>          | $V_{EN} = 1V, V_{CC} = 0V$                                      | 12                           | 25                   | 50                   | μA   |

## Static Characteristics (continued)

| Parameter                 | Symbol              | Conditions                | Min                  | Тур                  | Мах | Unit |

|---------------------------|---------------------|---------------------------|----------------------|----------------------|-----|------|

| PIN RXD                   |                     |                           |                      |                      |     |      |

| Low level output voltage  | V <sub>ol_rxd</sub> | I <sub>RxD</sub> = 1.25mA |                      |                      | 0.9 | V    |

| High level output voltage | V <sub>oh_rxd</sub> | I <sub>RxD</sub> = -250μA | V <sub>cc</sub> -0.9 |                      |     | V    |

| PIN INH                   |                     |                           |                      |                      |     |      |

| High level output voltage | $V_{oh\_INH}$       | I <sub>RxD</sub> = -180μA | V <sub>S</sub> -0.8V | V <sub>S</sub> -0.5V |     | V    |

| Leakage current           | V <sub>INH_Ik</sub> | $EN = L, V_{INH} = 0V$    | -5                   |                      | 5   | μA   |

| Thermal protection        |                     |                           |                      |                      |     |      |

| Thermal shutdown          | $T_{sd}$            |                           | 150                  |                      | 180 | °C   |

| Hysteresis                | T <sub>hys</sub>    |                           | 5                    |                      | 25  | °C   |

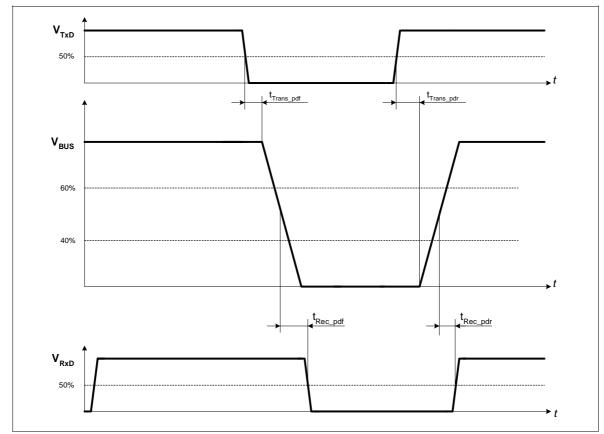

# **Dynamic Characteristics**

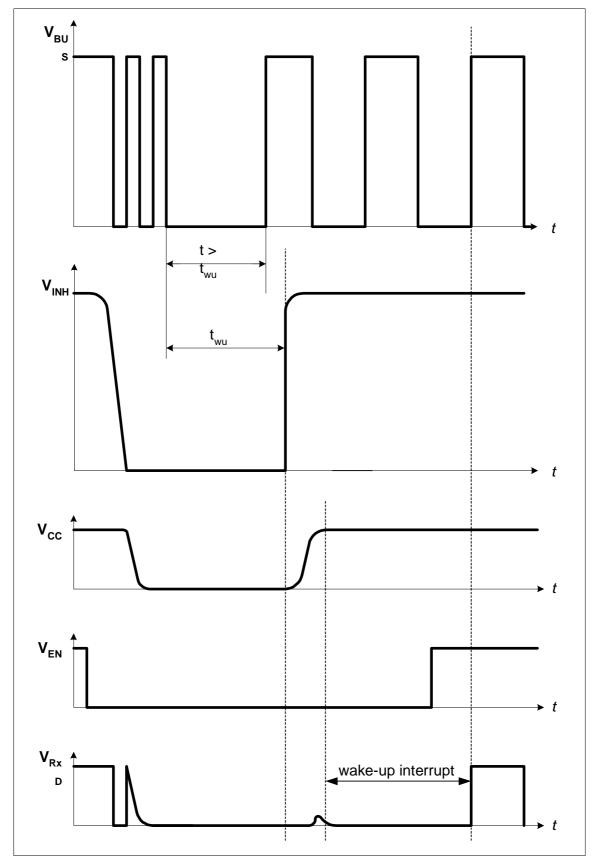

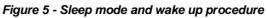

All dynamic values of the table below refer to the test-schematic schown in Figure - Timing Diagram  $6V \le V_S \le 18V$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , unless otherwise specified

| Parameter                                    | Symbol                 | Conditions                                                | Min | Тур | Max | Unit |

|----------------------------------------------|------------------------|-----------------------------------------------------------|-----|-----|-----|------|

| Slew rate falling edge                       | t <sub>SRF</sub>       | 80% < VBUS < 20% ,<br>minimum & maximum bus<br>load       | -3  | -2  | -1  | V/µs |

| Slew rate rising edge                        | t <sub>SRR</sub>       | 20% < VBUS < 80% ,<br>minimum bus load <sup>[1]</sup>     | 1   | 2   | 3   | V/µs |

| Propagation delay transmitter<br>( TxD->BUS) | t <sub>trans_pdf</sub> | TxD high to low transition <sup>[2]</sup>                 |     |     | 4   | μs   |

| Propagation delay transmitter<br>( TxD->BUS) | t <sub>trans_pdr</sub> | TxD low to high transition <sup>[2]</sup>                 |     |     | 4   | μs   |

| Propagation delay transmitter symmetry       | t <sub>trans_sym</sub> | Calculate t <sub>trans_pdf</sub> - t <sub>trans_pdr</sub> | -2  |     | 2   | μs   |

| Propagation delay receiver<br>(BUS->RxD)     | t <sub>rec_pdf</sub>   | BUS recessive to dominant [2]                             |     |     | 6   | μs   |

| Propagation delay receiver<br>(BUS->RxD)     | t <sub>rec_pdr</sub>   | BUS dominant to recessive <sup>[2]</sup>                  |     |     | 6   | μs   |

| Propagation delay receiver symmetry          | t <sub>rec_sym</sub>   | Calculate t <sub>trans_pdf</sub> - t <sub>trans_pdr</sub> | -2  |     | 2   | μs   |

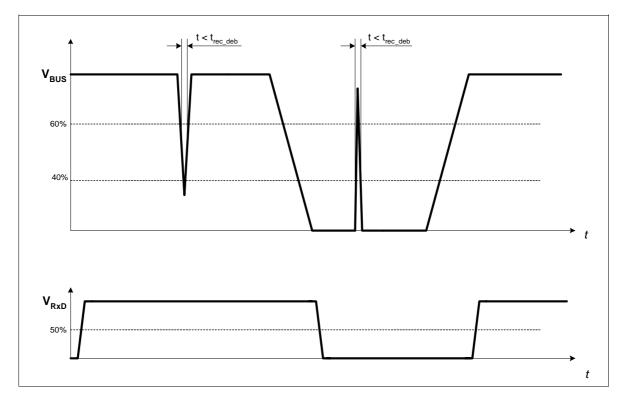

| Receiver debounce time                       | t <sub>rec_deb</sub>   | BUS rising & falling edge <sup>[3]</sup>                  | 1.2 |     | 3.1 | μs   |

| Wake-up filter time                          | t <sub>wu</sub>        | BUS rising & falling edge <sup>[4]</sup>                  | 25  |     | 90  | μs   |

| EN debauncing time                           | t <sub>en_deb</sub>    | Normal to sleep mode <sup>]</sup>                         | 10  | 20  | 40  | μs   |

<sup>[1]</sup> Minimum slew rate of the rising edge is determined by the network time constant

<sup>[2]</sup> See timing diagram figure 3

<sup>[3]</sup> See timing diagram figure 4

<sup>[4]</sup> See timing diagram figure 5

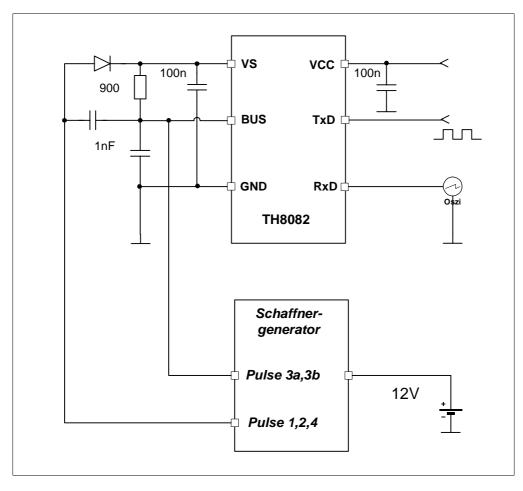

## **Timing Diagrams**

Figure 3 - Input/Output Timing

### **Timing Diagrams (continued)**

### **Test Circuit for Dynamic Characteristics**

Figure 5 - Test Circuit for Dynamic Characteristics

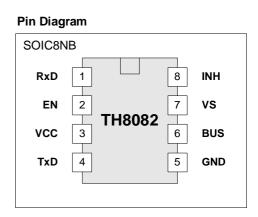

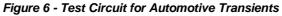

## Pin Description

| Pin | Name | I/O | Function                                              |

|-----|------|-----|-------------------------------------------------------|

| 1   | RXD  | 0   | Receive data from BUS to core, LOW in dominant state  |

| 2   | EN   | I   | Enables the normal operation mode when HIGH           |

| 3   | VCC  |     | 5V supply input                                       |

| 4   | TXD  | I   | Transmit data from core to BUS, LOW in dominant state |

| 5   | GND  |     | Ground                                                |

| 6   | BUS  | I/O | Single wire bus pin, LOW in dominant state            |

| 7   | VS   |     | Battery input voltage                                 |

| 8   | INH  | 0   | Control output for voltage regulator                  |

## Mechanical Specifications

#### 8 Η Ε Н Н Н -H 1 2 3 D 1**A1** Π Π Π α L b e

## SOIC8 Package Dimensions

### Small Outline Integrated Circiut (SOIC), SOIC 8, 150 mil

| All Dimension in mm, coplanarity < 0.1 mm |                                             |       |       |       |       |       |       |       |    |

|-------------------------------------------|---------------------------------------------|-------|-------|-------|-------|-------|-------|-------|----|

|                                           | D                                           | Е     | н     | Α     | A1    | е     | b     | L     | α  |

| min                                       | 4.8                                         | 3.80  | 10.00 | 5.80  | 0.10  | 4.07  | 0.33  | 0.40  | 0° |

| max                                       | 5.0                                         | 4.00  | 10.65 | 6.20  | 0.25  | 1.27  | 0.51  | 1.27  | 8° |

| All Dimension in inc                      | All Dimension in inch, coplanarity < 0.004" |       |       |       |       |       |       |       |    |

| min                                       | 0.189                                       | 0.150 | 0.228 | 0.053 | 0.004 | 0.050 | 0.013 | 0.016 | 0° |

| max                                       | 0.197                                       | 0.157 | 0.244 | 0.069 | 0.010 | 0.050 | 0.020 | 0.050 | 8° |

Notes

For the latest version of this document, go to our website at:

www.melexis.com

Or for additional information contact Melexis direct:

| 0e                       |

|--------------------------|

| +32 13 67 04 95          |

| sales_europe@melexis.com |

|                          |

|                          |

|                          |

All other locations +1 603 223 2362 Phone:

| E-mail: | sales_usa@melexis.com |

|---------|-----------------------|

#### **Important Notice**

Devices sold by Melexis are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. Melexis makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Melexis reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with Melexis for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by Melexis for each application. The information furnished by Melexis is believed to be correct and accurate. However, Melexis shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interrupt of business or indirect, special incidental or

consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of Melexis' rendering of technical or other services.

© 2000 Melexis GmbH. All rights reserved.