## CMOS 4-BIT MICROCONTROLLER

## TMP47C858F

The 47C858 is a high performance 4-bit single chip microcomputer based on the TLCS-470 series. The 47C858 has plentiful operating modes (SLOW, SLEEP, HOLD) intended to save the power, with LCD driver and DTMF generator which are highly suitable for application in telephones.

| PART No.   | ROM          | RAM         | PACKAGE | PIGGYBACK  |

|------------|--------------|-------------|---------|------------|

| TMP47C858F | 8192 × 8-bit | 512 x 4-bit | QFP100  | TMP47C058G |

#### **FEATURES**

- ♦4-bit signal chip mocrocomputer

- ♦Instruction execution time:

8.3µs (at 960KHz), 244µs (at 32.8KHz)

- ◆Low voltage operation: 2.7V min.

- ♦92 basic instrutions

- **◆**Table look-up instructions

- ◆Subroutine nesting: 15 levels max.

- ♦6 interrupt sources (External: 2, Internal: 4)

All sources have independent latchs each, and multiple interrupt control is available.

5pins

- ♦1/O port (36pins)

- Input 2ports

- 1/O 8ports 31pins

- ♦Interval Timer (22 stages)

- ♦Two 12-bit Timer/Counters

Timer, event counter, and pulse width measurement mode

◆Serial Interface with 8-bit buffer

External/internal clock, and leading/trailing edge shift, and 4/8-bit mode

**♦**LCD driver

LCD direct drive is available (440 dots display, 1/10 duty)

- ◆DTMF (Dual Tone Multi Frequency) output

- DTMF output with one instrution

- Single tone output function

- ◆Dual-clock operation

High-speed/Low-power-consumption operating mode

- **♦** HOLD function

- Battery/Capacitor back-up

- **♦** SLEEP function

- Battery/Capacitor back-up

- LCD is displaying

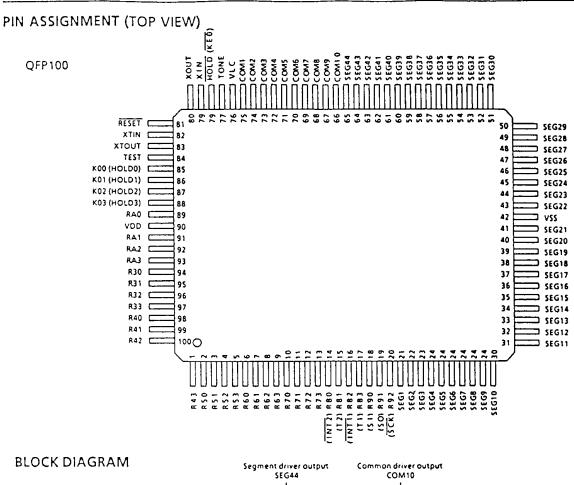

## PIN FUNCTION

| PIN NAME                        | Input/Output  | FUNC                                                                                         | TIONS                                                    |  |  |  |

|---------------------------------|---------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|

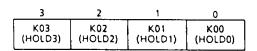

| K03 (HOLD3)<br>'<br>K00 (HOLD0) | Input (Input) | 4-bit input port                                                                             | HOLD and SLEEP request/release signal input (Active "H") |  |  |  |

| R33 - R30                       |               |                                                                                              | L                                                        |  |  |  |

| R43 - R40                       |               | 4-bit I/O port with latch.                                                                   |                                                          |  |  |  |

| R53 - R50                       | 1/0           | When used as input port, the latch must be                                                   | 2 (of to *1*                                             |  |  |  |

| R63 - R60                       |               | The same as impact port, the later mast be                                                   |                                                          |  |  |  |

| R73 - R70                       |               |                                                                                              |                                                          |  |  |  |

| R83 (T1)                        |               |                                                                                              | Timer/Counter 1 external input                           |  |  |  |

| R82 (INT1)                      |               | 4-bit I/O port with latch. When used as input port, external                                 | External interrupt 1 input                               |  |  |  |

| R81 (T2)                        | I/O (Input)   | interrupt input pin, or Timer/counter                                                        | Timer/Counter 2 external input                           |  |  |  |

| R80 (INT2)                      |               | xternal input pin, the latch must be set  p 11. External interrupt 2 input  Serial clock I/O |                                                          |  |  |  |

| R92 ( <del>ŠČK</del> )          | 1/0 (1/0)     | 3-bit I/O port with latch.                                                                   | Serial clock I/O                                         |  |  |  |

| R91 (SO)                        | I/O (Output)  | When used as input port or serial port, he latch must be set to "1".                         |                                                          |  |  |  |

| R90 (SI)                        | VO (Input)    | the ratch must be set to 1.                                                                  | Serial data input                                        |  |  |  |

| RA3 - RA0                       | vo            | 4-bit VO port with latch. When used as input port, the latch must be                         | e set to "1".                                            |  |  |  |

| SEG44 - SEG1                    |               | LCD segment driver output                                                                    |                                                          |  |  |  |

| COM10 - COM1                    | Output        | LCD common driver output                                                                     |                                                          |  |  |  |

| TONE                            | Output        | Tone output                                                                                  |                                                          |  |  |  |

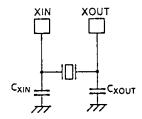

| XIN                             | Input         | Resonator connecting pins (High frequenc                                                     | v) .                                                     |  |  |  |

| XOUT                            | Output        | For inputting external clock, XIN is used an                                                 |                                                          |  |  |  |

| XTIN                            | Input         | Oscillator connecting pins (Low frequency)                                                   | ).                                                       |  |  |  |

| хтоит                           | Output        | For inputting external clock, XTIN is used a                                                 |                                                          |  |  |  |

| RESET                           | Input         | Reset signal input                                                                           |                                                          |  |  |  |

| HOLD (KEO)                      | Input (Input) | HOLD and SLEEP request/release signal input                                                  | Sense input                                              |  |  |  |

| TEST                            | Input         | Test pin for out-going test. Be opened or fix                                                | red to low level.                                        |  |  |  |

| VDD                             |               | + 2.7V to 6.0V                                                                               |                                                          |  |  |  |

| VSS                             | Power Supply  | OV (GND)                                                                                     |                                                          |  |  |  |

| VLC                             |               | LCD drive power supply                                                                       |                                                          |  |  |  |

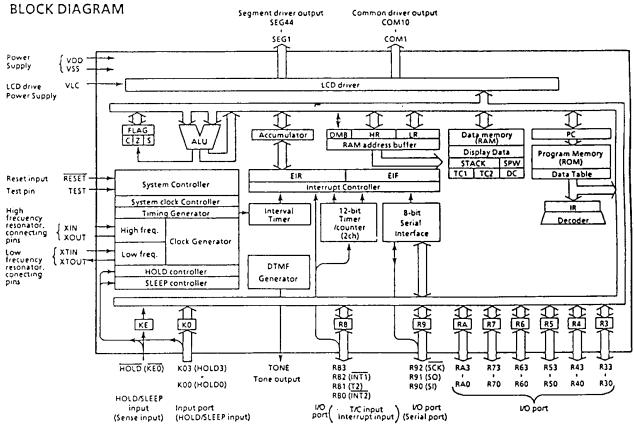

#### OPERATIONAL DESCRIPTION

Concerning the 47C858 the configuration and functions of hardwares are described. As the description has been provided with priority on those parts differing from the 47C800, the technical data sheets for the 47C800 shall also be referred to.

#### SYSTEM CONFIGURATION

(1) CPU Core functions

Except for the systemcontrol circuit, the CPU core functions are the same as those of the 47C800.

- (2) Periferal Hardware Functions

- ① I/O Ports

(5) LCD Driver

2 Interval Timer

(6) DIHF Generator

③ Timer/Counter

- 7 Serial Interface

- ① One-second Signal Detection Circuit

The following are explanations of functions 1 and 4-6 which have been added to the 47C858 or which are different from those of the 47C800, and the system clock control circuit.

### 2 CPU CORE FUNCTIONS

#### 2. 1 SYSTEM CONTROL CIRCUIT

It is possible to shift from the SLOW operating mode to the SLEEP operating mode to further reduce power consumption: and still maintain the internal status. In the SLEEP mode, all operations execpt for the timing generator(TG) binary counter and LCD driver are suspended.

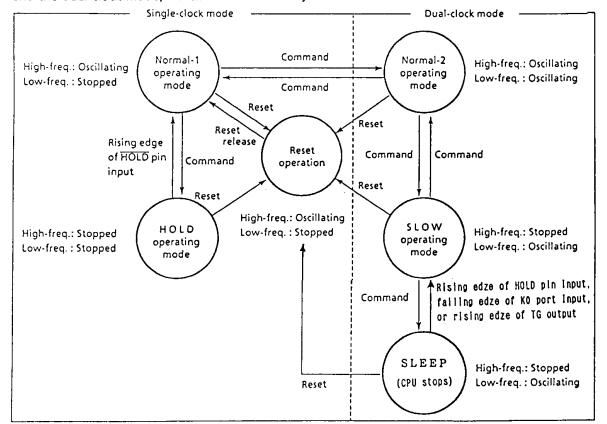

## 2.1.1 System Clock Controller

The system clock controller starts or stops the high-frequency and low-frequency clock oscillator and switches between the basic clocks. The operating mode is generally divided into the single-clock mode and the dual-clock mode, which are controlled by command.

Figure 2-1 Operating Mode Transition Diagram

#### (1) Control of System Clock

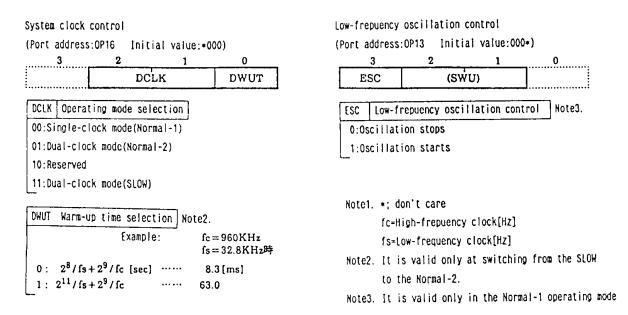

The system clock is controlled by the command register (OP16). Dureing a reset, the command register is reset to "0" and the single clock mode is selected. Oscillation of the low-frequency clock is started in the single clock mode by setting bit 3 of OP13.

Figure 2-2. System Clock Control Command Register

#### 2.1.2 Operating Hode

There are two operating modes: the Single-clock mode and the Dual-clock mode.

#### (1) Single-clock Hode

Canceling a reset starts the Normal-1 operating mode. Oscillation of the low-frequency clock can be started and stopped in this mode. To shift to the Dual-clock mode, start oscillation with the low-frequency oscillation control command register (OP13) and then switch to the Norma-2 operating mode with the system clock control command register (OP16).

There is also a HOLD operating mode used for low power consumption operation. To switch to HOLD operation, stop oscillation of the low-frequency clock(OP13) and then switch with the HOLD operation mode command register(OP10).

## (2) Dual-clock Hode

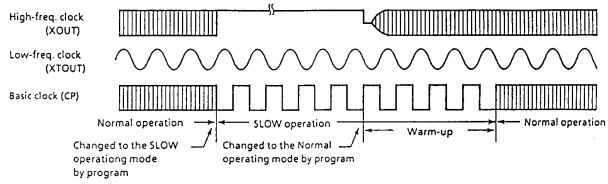

In the Dual-clock mode, the instruction cycle is normally generated with the high-frequency clock(fc) and then the Normal-2 operating mode is used. When necessary, the SLOW operating mode can be used by generating the low-frequency clock(fs). In addition, the SLEEP operation mode, in which all operations except the low-frequency clock and LCD driver are suspended, can also be used. Switching between Normal-2 operation, SLOW operation and SLEEP operation in the Dual-clock mode is explained below. During a reset, the command register is initialized to the Single-clock mode. At this time, the low-frequency clock is not being oscillated; therefore, start oscillation of the low-frequency clock first and then switch to Normal-2 operation in the Dual-clock mode.

a) Switching from the Normal-2 operation to the SLOW operation

Setting DCLK(bit2 of OP16) to "1" switches to SLOW operation, but several seconds are required for low-frequency clock oscillation to stabilize. Consequently, when there is a possibility of switching to SLOW operation immediately after shifting to Normal-2 operation, it is necessary to wait until oscillation of the low-frequency clock stabilizes. Oscillation of the high-frequency clock will stop at this time.

b)Returning from the SLOW operation to the Normal-2 operation

When DCLK(bit 2 of OP16) is cleared to "O", the warm-up time for resetting to DWUT(bit 0 of of OP16) is set at

the same time. Normal-2 operation starts after the set warm-up time has elapsed.

Figure 2-3. System Clock Swithing Timing

c)Shifting from the SLOW operation to the SLEEP operation

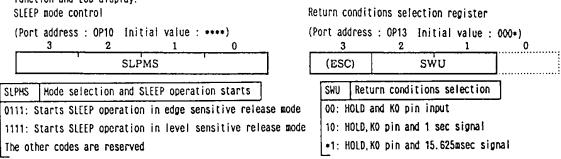

After selecting the return conditions using the return conditions selection register(OP13), shift to SLEEP operation (refer to the SLEEP operation mode explanation) by setting the command in the command register(OP10). Occurrence of the selected condition returns to SLOW operation.

Note1. The command register(OP10) is used for both HOLD operation control and SLEEP operation control. This register is used for HOLD operation control when accessed during Normal-1 operation and for SLEEP operation control when accessed during SLOW operation.

Note2. During SLOW operation and SLEEP operation. oscillation of the high-frequency clock is automatically halted to enable low power supply voltage operation and low power consumption operation. However, while less power is consumed by the oscillator and internal hardwaer, the amount of power consumed by the pin interface (dependent on external circuitry and programs) is not directly related to the low power consumption operation mode; therefore, caution is required during system design and interface circuit design. Also, the execution of instructions is not interrupted by switching to SLOW operation but, in some cases, there is influence on some of the peripheral hardwaer functions; therefore, refer to the explanations of the various operations.

#### 2.1.3 HOLD Operation Hode

HOLD operation suspends system operation and holds the internal status immediately before the suspension with

HOLD operating mode control

(Port address:OP10 Initial value:\*0\*\*)

| 3  | 2    | 1  | 0   |

|----|------|----|-----|

| HI | LDMS | нч | TUV |

HLDHS | Hode select/HOLD operation start |

O1: Starts HOLD operation in edze sensitive release mode

11: Starts HOLD operation in level sesitive release mode

\*0: Reserved

Note1. \*: don't care

Note2. Do not access command register OP10 unless the HOLD operation mode is being used

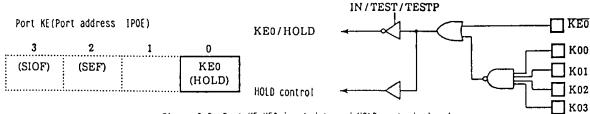

Figure 2-4. Command Register

low power consumption. This mode is started by setting the command in the command register(OP10) in the Normal-1 operation mode, but it is necessary to stop the low-frequency clock(by clearing bit 3 of OP13) before accessing OP10. Hold control is possible not only from the HOLD pin but from the KO port as well. Figure 2-5 shows the relationship between the KE port, KEO input data and the HOLD control signal. The KE port is assigned to the lowest bit of port address IPOE and is read as the result of the logical operation of the KEO pin and KO pin input. When the KEO pin is "L" and all four KO pins are "H", for example, the KEO input data is read as "I". "O" is read at all other times.

Figure 2-5. Port KE, KEO input data and HOLD control signal

The HOLD operation mode is released when a hold control signal rise from "0" to "1" is sensed. Consequently, if the hook switch is connected to the HOLD pin and the key switch is connected to the KO pin, it is possible to release HOLD operation by either turning off the hook switch or by pressing a key. Thus, an on-hook dialing function can easily be implemented. Other than that, the HOLD operation mode is the same as for the 47C800. For details, refer to the 47C800 technical data.

#### 2.1.4 SLEEP operation mode

The SLEEP operation mode suspends all SLOW operation operations except for the low-frequency clock, TG binary counter and LCD driver, and retains the internal status with low power consumption without stopping the clock function and LCD display.

Figure 2-6. Command Register, Return Conditions Selection register.

Operation in the edge relese mode and level release mode is the same as in the HOLD operation mode. To start SLEEP operation, select the return conditions during SLOW operation with the return conditions selection register(OP13) and then set the start command in the command register(OP10). SLEEP operation is then return to SLOW operation when the conditions selected with the return conditions selection register occur.

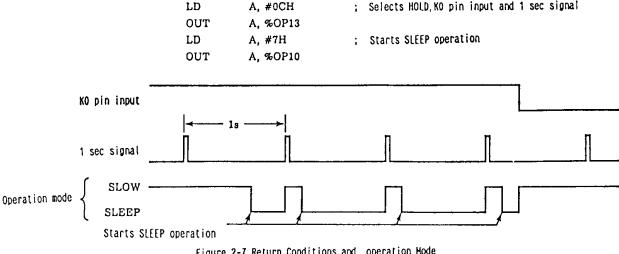

Example: Starting SLEEP operation using the HOLD and KO pin input, and the 1 sec signal as return condition.

Figure 2-7 Return Conditions and operation Hode

## 3. PERIPHERAL HARDWARE FUNCTION

#### 3.1 I/O Ports

The 47C452A has 10 ports (36 pins) each as follows:

- Ф ко

- 2 R4, R5, R6

- 3 R3, R7, RA

- @ R8

- **5** R9

- **6** KE

Table 3-1 lists the port address assignments and the I/O instructions that can access the ports.

(1) Port K0 (K03-K00)

The 4-bit input port with pull-up resistors, shared by hold request/release signal input.

Port K0 (Port address IP00)

Figure 3-1. Port KO

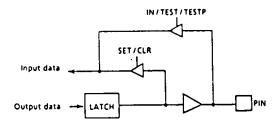

(2) R3 (R33~R30), R7 (R73~R70), RA (RA3~RA0)

The 4-bit I/O port with latch. When used as an input port, the latch must be set to "1". The latch is initialized to "1" during reset.

Figure 3-2. R3, R7, RA

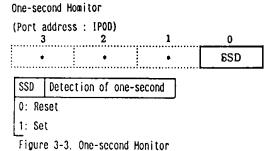

### 3.2 One-second Signal Detection Circuit

A one-second signal detection circuit is built-in to enable clock functions. A flip-flop construction is used which is set by the rise (one second) of the TG final stage output and which is reset by accessing port address OPOD. The one-second detection circuit can be used in Normal-2 operation, SLOW operation and SLEEP operation mode.

Example 1. Reads F/F

IN %IPOD, A

[xample 2. Rescts F/F

OUT A, %OPOD

| Port            | 4                     | Port                               |                            |                       | Input      | Input/Output instructions | tions    |           |                            |

|-----------------|-----------------------|------------------------------------|----------------------------|-----------------------|------------|---------------------------|----------|-----------|----------------------------|

| Address (••)    | Input (IP.+)          | Output (OP**)                      | IN %p, A OUT IN %p, @HLOUT | OUT A,%p<br>OUT@HL,%p | OUT #k,%p  | OUTB @HL                  | SET %p,b | TEST %p,b | SET @L<br>CLR @L<br>TEST@L |

| H <sub>00</sub> | K0 input port         | 1                                  | 0                          |                       |            |                           |          | C         |                            |

| 01              | ROW register          | ROW register                       | 0                          | С                     | С          | C                         | · C      | ) C       | l 1                        |

| 05              | COLUMN register       | COLUMN register                    | 0                          | C                     | ) C        | (Note 2)                  |          | ) C       | l i                        |

| 03              | R3 input port         | R3 output port                     | 0                          | 0                     | 0          | ) !                       | ) C      | ) C       | l I                        |

| 04              | R4input port          | R4 output port                     | 0                          | ·C                    | ) C        | ı                         | ) C      | -<br>) C  |                            |

| 05              | R5 input port         | R5 output port                     | 0                          | ) C                   | ) C        | 1                         | )(       | )(        | )(                         |

| 90              | R6 input port         | R6 output por:                     | 0                          | ) C                   | ) C        | i                         | ) C      | ) C       | )(                         |

| 0.7             | R7 input port         | R7 output port                     | 0                          | ) C                   | ) C        |                           | -<br>) C | ) C       | )(                         |

| 80              | R8 input port         | R8 output port                     | C                          | ) C                   | ) C        |                           | )(       | ) C       | )                          |

| 60              | R9 input port         | R9 output port                     | С                          | ) C                   | ) C        | I !                       | )(       | ) (       | ı                          |

| 0A              | RAinput port          | RA output port                     | С                          | ) C                   | ) C        |                           | ) (      | ) (       | ı                          |

| 0.13            | 1                     |                                    | )                          | )                     | )          | l                         | )        | )         | 1                          |

| ပ္ပ             |                       | ļ                                  | : !                        | l                     | l          | ı                         | ı        | ı         | ı                          |

| 00              | 1 sec signal status   | Resets E/F                         | ı C                        | ı (                   | 1 (        | i                         | i        | ı         | i                          |

| OE              | status                |                                    | ) C                        | ) 1                   | )          | l                         | 1        | ı (       | ı                          |

| OF              | Serial receive buffer | Serial transmit buffer             | 0                          | С                     | · C        | l                         | 1 1      | )         | t i                        |

| 10 <sub>H</sub> | Undefined             | Hold operating mode control        | 1                          | 0                     | )          | \                         | 1 1      | 1 1       |                            |

| 11              | Undefined             |                                    | ı                          | ) [                   | ı          | ı                         | ı        |           |                            |

| 12              | Undefined             | Single tone control                | ı                          | 0                     |            | ۱ ۱                       |          | 1 1       | 1 1                        |

| 13              | Undefined             | Slow clock/SLEEP operation control | 1                          | 0                     | ı          | !                         | ı        | ı         | 1                          |

| 14              | Undefined             |                                    | 1                          | ı                     | I          | ı                         | ı        |           |                            |

| 15              | Undefined             | -                                  | ı                          | ı                     | ı          | ı                         |          |           | 1 1                        |

| 16              | Undefined             | System clock control               | ı                          | С                     | ı          | ı                         | ı        | 1         | · I                        |

| 17              | Undefined             |                                    | ı                          | )                     | ı          | 1                         | ı        | 1         | ı                          |

| 18              | Undefined             |                                    | ı                          | 1                     |            |                           | l        | l         | ı                          |

| 19              | Undefined             | Interval Timer interrupt control   | I                          | C                     |            |                           |          | ı         | ı                          |

| 14              | Undefined             |                                    | ı                          | )                     |            | l                         | l        | I         | I                          |

| 118             | Undefined             | LCD driver control 2               | ı                          | C                     | <b>i</b> i | 1 1                       | l        | ì         | I                          |

| 10              | Undefined             | Timer/Counter 1 control            | ı                          | ) C                   |            |                           |          |           | I                          |

| 10              | Undefined             | Timer/Counter 2 control            | Ì                          | ) C                   | · I        | 1 1                       | 1 1      | I         | I I                        |

| 1E              | Undefined             | Serial interface control 1         | J                          | ) C                   | <b> </b>   | 1 1                       | 1 1      | ı         | l I                        |

| 1F              | Undefined             | Serial interface control 2         | ı                          | 0                     | ı          | 1                         | 1        | 1         | <b> </b>                   |

"——" means the reserved state. Unavailable for the user program. The 5-bit to 8-bit data conversion instruction [OUT8 @HL], automatic access to ROW register and Column register. Note 1. Note 2.

Table 3-1. Port Address Assignments and Available I/O Instructions

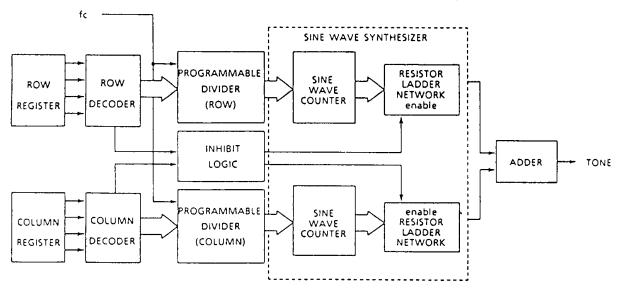

#### 3.3 DTMF Generator

The 47C858 has a built-in DTMF generator which generates dialing signals for tone dialing type telephones. There are two groups of tone dial signals, one group of 4 sine wave low frequencies and another group of 4 sine wave high frequencies. All of these frequencies can be selected individually and combined with a frequency from the other group for a total of 16 different DTMF composite waves.

(DTMF; Dual Tone Multi Frequency)

## 3.3.1 Configuration of DTMF Generator

Figure 3-4 shows configuration of the DTMF generator. The 47C858—generates two stepped, quasi sine waves for tone dial signals which can be combined and output. The high or low group of frequencies is selected by setting frequency selection codes into the ROW and COLUMN registers.

Figure 3-4. Configuration of DTMF Generator

## 3.3.2 Control of DTMF Generator

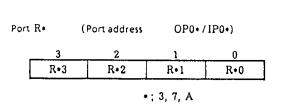

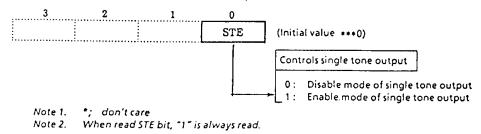

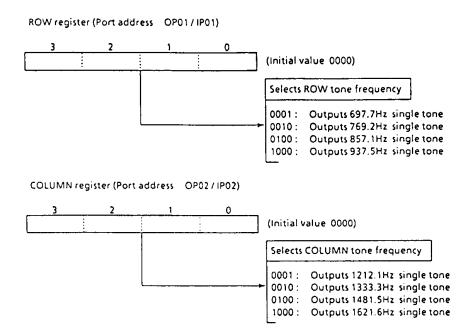

Tone output is controlled by ROW register (OP01/IP01) and COLUMN register (OP02/IP02). And single tone is controlled by TONE command register (OP12). ROW register, COLUMN register and TONE command register are initialized to "0" during the reset.

TONE command register (Port address OP12)

Figure 3-5. TONE command register

Figure 3-6. ROW, COLUMN Register

Tones are outputted by loading the frequency selection codes shown in Figure 3-6 into the ROW and COLUMN registers. In the enable mode of single tone output and either ROW or COLUMN register is disabled, another register remains to be enabled, and so single tone can be outputted, by loading an ineffective code into the register. When both the registers are enabled, dual tone can be outputted. In the disable mode of single tone output, effective codes are loaded into both ROW and COLUMN registers and then dual tone can be outputted. At this time, an ineffective code is loaded into ROW or COLUMN register and then the 47C858 has no tone output signal.

The [OUTB @HL] instruction can set 8-bit data into both registers (the upper 4 bits of the ROM data go to the COLUMN register and the lower 4 bits go to the ROW register) at the same time, and DTMF signal is outputted without single tone output.

Example 1: To output 1481.5Hz single tone

OUT #8,%OPOD; Sets the enable mode of single tone output.

OUT #0,%OPO1; Sets an ineffective code into ROW register.

OUT #4,%OPO2; Sets data "4" into COLUMN register

Example 2: 8 bits data corresponding to the 5 bits of data linking the content of carry flag and the contents of data memory RAM1 address 90<sub>H</sub> are read from the ROM, frequency selection codes are loaded into ROW and COLUMN registers, and dual tone is outputted.

LD HL,#90H; HL←90H (Sets the address of the data memory)

OUTB GHL; Sets the ROM data into the ROW and COLUMN register.

Table 3-2 shows the corresponding frequency selection codes of the ROW and COLUMN registers for the telephone dial keys. Table 3-3 shows the deviation between the 47C858 tone output frequency and standard frequency.

|              |                          | COLUM          | N register (OP0 | 2 / IPO2) |

|--------------|--------------------------|----------------|-----------------|-----------|

|              | Frequency selection code | 0001<br>(1209) | 0010<br>(1336)  | 0100      |

|              | 0001 (697)               | 1              | 2               | 3         |

|              | 0010 (770)               | 4              | 5               | 6         |

| ROW register | 0100 (852)               | 7              | 8               | 9         |

| (OP01/IP01)  | 1000 (941)               | •              | 0               | #         |

|              |                          | Standa         | rd telephone d  | ial key   |

Contents of ( ) are standard frequencies, unit: Hz

Table 3-2. Corresponding frequency selection codes of the ROW and COLUMN registers for the telephone dial keys

|             |         |             |           | ROW Tone                   |                               |               |

|-------------|---------|-------------|-----------|----------------------------|-------------------------------|---------------|

| Freque<br>3 | ncy sel | ection<br>1 | code<br>0 | Tone output frequency [Hz] | Standard<br>frequency<br>[Hz] | Deviation [%] |

| 0           | 0       | 0           | 1         | 697.7                      | 697                           | + 0.10        |

| 0           | 0       | 1           | 0         | 769.2                      | 770                           | - 0.10        |

| 0           | 1       | 0           | 0         | 857.1                      | 852                           | + 0.60        |

| 1           | 0       | 0           | 0         | 937.5                      | 941                           | - 0.37        |

|        |         |             |           | COLUMN Tone                |                               |                  |

|--------|---------|-------------|-----------|----------------------------|-------------------------------|------------------|

| Freque | ncy sel | ection<br>1 | code<br>0 | Tone output frequency [Hz] | Standard<br>frequency<br>[Hz] | Deviation<br>[%] |

| 0      | 0       | 0           | 1         | 1212.1                     | 1209                          | + 0.26           |

| 0      | 0       | 1           | 0         | 1333.3                     | 1336                          | - 0.20           |

| 0      | 1       | 0           | 0         | 1481.5                     | 1477                          | + 0.30           |

| 1      | 0       | 0           | 0         | 1621.6                     | 1633                          | - 0.70           |

Table 3-3. Tone output frequencies and Deviation from standard

# 3.3.3 Test mode for tone output

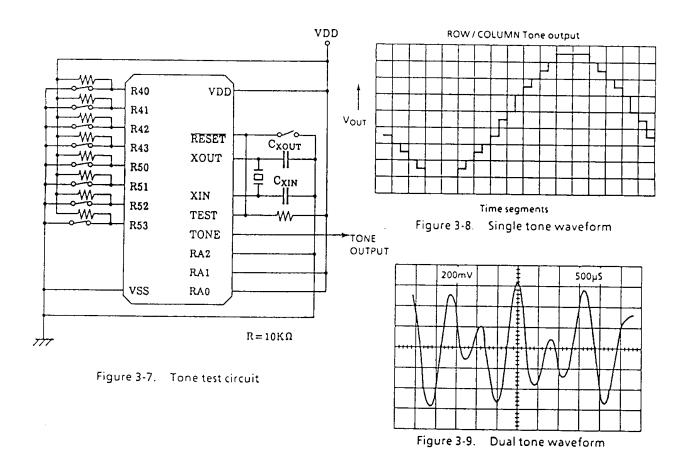

The 47C85E includes a test mode for checking tone output waveforms. Tones can be outputted by the curcuit shown in Figure 3-7. ROW data are inputted from the R4 port and COLUMN data are inputted from the R5 port, and any desired single or dual tones can be outputted by setting the frequency selection codes shown in Figure 3-6. Figure 3-8 shows a single tone waveform and Figure 3-9 shows a dual tone waveform.

#### 3.4 Display

## 3.4.1 Setting Display RAH

The data is stored in the display data area of RAM. Commands perform the processing which converts standard data into LCD display data (using mainly ROH data reference commands).

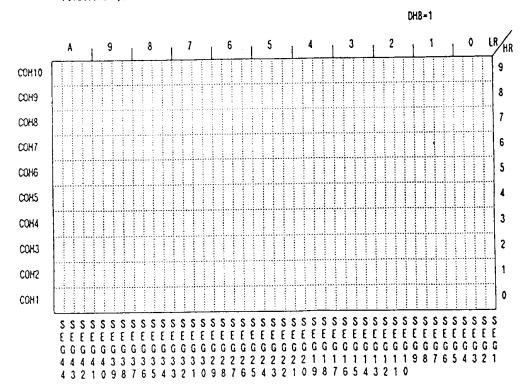

Display data is converted and stored in the area, and its data are automatically transferred to LCD drive circuit without any relation to program.

Each bit in the display data area of RAH and the LCD segment(dot) is in a one-to-one relationship.

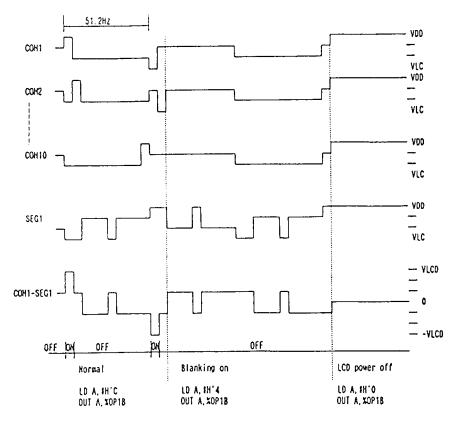

## 3.4.2 LCD Drive Control

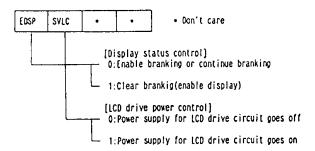

There are 2-selecter circuit as LCD drive control. One is "Display status control", and the other is "LCD drive power control".

These code are selected by accessing the port resister address "OPIB".

(It is reset to "0" at initialization operation)

## port resister address "OP18"

MOTE1:blanking-- COM1-COM10 goes into "non-light opration level". SEG1-SEG44 continues in normal operating status.

MOTE2: When the SYLC is "O", COM1-COM10 and SEG1-SEG44 go into VDD level.

#### Display output

Example of display output from the LCD drive circuit are given below.

#### (1/10 duty 1/3 bias)

Note: VLCO-VDD-VLC

# ELECTRICAL CHARACTERISTICS

ABSOLUTE MAXIMUM RATINGS

$(V_{SS} = 0V)$

| PARAMETER                       | SYMBOL           | PINS                       | RATINGS                        | UNIT       |

|---------------------------------|------------------|----------------------------|--------------------------------|------------|

| Supply Voltage                  | V <sub>D</sub>   |                            | – 0.3 to 7                     | V          |

| Supply Voltage (LCD drive)      | V <sub>LC</sub>  |                            | - 0.3 to V <sub>DD</sub> + 0.3 | V          |

| Input Voltage                   | V <sub>IN</sub>  |                            | - 0.3 to V <sub>DD</sub> + 0.3 | V          |

| Output Voltage                  | Vouti            | Except sink open drain pin | - 0.3 to V <sub>DD</sub> + 0.3 | l          |

| Output voitage                  | Voutz            | Sink open drain pin        | - 0.3 to 10                    | \          |

| Output Current (Per 1 pin)      | lout             |                            | 3.2                            | mA         |

| Power Dissipation [Topr = 70°C] | PD               |                            | 600                            | mW         |

| Soldering Temperature (time)    | T <sub>sid</sub> |                            | 260 (10sec)                    | *c         |

| Storage Temperature             | Tstg             |                            | - 55 to 125                    | <b>•</b> c |

| Operating Temperature           | Topr             |                            | - 30 to 60                     | •c         |

RECOMMENDED OPERATING CONDITIONS

$(V_{SS} = 0V, T_{opr} = -30 \text{ to } 60^{\circ}\text{C})$

| PARAMETER          | SYMBOL           | PINS                    | CONDITIONS             | Min.                   | Max.                                                                        | דואט |

|--------------------|------------------|-------------------------|------------------------|------------------------|-----------------------------------------------------------------------------|------|

|                    |                  |                         | In the Normal<br>mode  |                        | V <sub>DD</sub> × 0.3 V <sub>DD</sub> × 0.25 V <sub>DD</sub> × 0.1 960 34.0 |      |

| Supply Voltage     | V <sub>DD</sub>  |                         | In the SLOW mode       | 2.7                    |                                                                             | V    |

|                    |                  |                         | in the SLEEPmode       |                        |                                                                             |      |

|                    |                  |                         | In the HOLD mode       | 2.0                    | 7                                                                           |      |

|                    | V <sub>IH1</sub> | Except Hysteresis Input |                        | V <sub>DD</sub> × 0.7  |                                                                             |      |

| Input High Voltage | V <sub>IH2</sub> | Hysteresis Input        | V <sub>DD</sub> ≥4.5V  | V <sub>DD</sub> × 0.75 | V <sub>DD</sub>                                                             | V    |

|                    | V <sub>IH3</sub> |                         | V <sub>DO</sub> < 4.5V | V <sub>DO</sub> × 0.9  |                                                                             |      |

|                    | V <sub>IL1</sub> | Except Hysteresis Input |                        |                        | $V_{DD} \times 0.3$                                                         |      |

| Input Low Voltage  | V <sub>IL2</sub> | Hysteresis Input        | V <sub>DD</sub> ≥4.5V  | 0                      | V <sub>DD</sub> × 0.25                                                      | ] v  |

|                    | V <sub>IL3</sub> |                         | V <sub>DD</sub> < 4.5V |                        | $V_{DD} \times 0.1$                                                         |      |

|                    | fc               | XIN, XOUT               |                        |                        | V <sub>DD</sub> × 0.3<br>V <sub>DD</sub> × 0.25<br>V <sub>DD</sub> × 0.1    | KHz  |

| Clock Frequency    | fs               | XTIN, XTOUT             |                        | 30.0                   | 34.0                                                                        | KHz  |

D.C. CHARACTERISTICS

$(V_{SS} = 0V, T_{opr} = -30 \text{ to } 60^{\circ}\text{C})$

| PARAMETER                             | SYMBOL            | PINS                           | CONDITIONS                                                                                           | Min. | Тур. | Max.     | UNIT |

|---------------------------------------|-------------------|--------------------------------|------------------------------------------------------------------------------------------------------|------|------|----------|------|

| Hysteresis Voltage                    | V <sub>H</sub> s  | Hysteresis Input               |                                                                                                      | _    | 0.7  | -        | v    |

| Input Current                         | <sup>‡</sup> IN1  | Port KO, TEST, RESET, HOLD     | V <sub>OD</sub> = 5.5V,                                                                              | _    |      | ± 2      |      |

|                                       | I <sub>IN2</sub>  | Open drain R port              | V <sub>IN</sub> = 5.5V / 0V                                                                          |      |      | <u> </u> | μΑ   |

| Input Low Current                     | I <sub>IL</sub>   | Push-pull R port               | $V_{DD} = 5.5V, V_{IN} = 0.4V$                                                                       | -    | _    | - 2      | mA   |

| Input Registance                      | R <sub>IN1</sub>  | Port K0 with pull-up/pull-down |                                                                                                      | 30   | 70   | 150      |      |

| inpot Kegistance                      | R <sub>IN2</sub>  | RESET                          |                                                                                                      | 100  | 220  | 450      | ΚΩ   |

| Output Leakage<br>Current             | ILO               | Open drain ports P, R          | V <sub>DD</sub> = 5.5V, V <sub>OUT</sub> = 5.5V                                                      | _    | -    | 2        | μΑ   |

| Output High Voltage                   | Voн               | Push-pull R port               | V <sub>DD</sub> = 4.5V, I <sub>OH</sub> = -200μA                                                     | 2.4  | -    | _        | ٧    |

| Output Low Voltage                    | V <sub>OL</sub> 2 | Except XOUT                    | V <sub>DD</sub> = 4.5V, I <sub>OL</sub> = 1.6mA                                                      | -    | _    | 0.4      |      |

| Segment Output<br>Registance          | Ros               | SEG pin                        |                                                                                                      |      |      |          |      |

| Common Output<br>Registance           | Roc               | COM pin                        |                                                                                                      | -    | 20   | _        | ΚΩ   |

| Segment/Common                        | VOZ/3             |                                | $V_{DD} = 5V$ , $V_{DD} - V_{LC} = 3V$                                                               | 3.8  | 4.0  | 4.2      |      |

| Output Voltage                        | Vois              | SEG / COM pin                  |                                                                                                      | 2.8  | 3.0  | 3.2      | ٧    |

| Supply Current                        | IDD               |                                | $V_{DD} = 5.5V, V_{LC} = V_{SS}$<br>fc = 960KHz                                                      | -    | 1.2  | 2.2      |      |

| (in the Nomal mode)                   | lopt              |                                | V <sub>DD</sub> = 5.5V, V <sub>LC</sub> = V <sub>SS</sub><br>fc = 960KHz<br>When tone is oscillating | -    | 3.0  | 5.0      | mA . |

| Supply Current<br>(in the SLOW mode)  | loos              |                                | $V_{DD} = 3V$ , $V_{LC} = V_{SS}$                                                                    | -    | 30   | 60       |      |

| Supply Current<br>(in the SLEEP mode) | loosp             |                                | fs = 32.768KHz                                                                                       | -    | 15   | 25       | μА   |

| Supply Current<br>(in the HOLD mode)  | Грон              |                                | V <sub>DD</sub> = 5.5V                                                                               | -    | 0.5  | 10       | •    |

Note 1. Typ. values show those at  $T_{opr} = 25^{\circ}C$ ,  $V_{DD} = 5V$ .

Note 2. Input Current I<sub>IN1</sub>; The current through resistor is not included, when the input resistor (pull-up/pull-down) is contained.

Note 3. Output Resistance Ros, Roc; Shows on-resistance at the level switching.

Note 4. V<sub>O2/3</sub>; Shows 2/3 level output voltage. V<sub>O1/3</sub>; Shows 1/3 level output voltage.

Note 5. Supply Current IDD;  $V_{IN} = 5.3V/0.2V$

> The KO port is open when the input resistor is contained. The voltage applied to the R port is within the valid range.

Note 6. Supply Current  $I_{DDS}$ ;  $V_{IN} = 2.8V/0.2V$ . Only low frequency clock is only osillated (connecting XTIN, XTOUT).

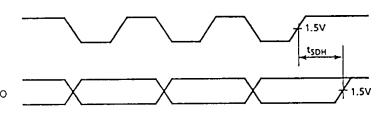

A.C. CHARACTERISTICS

$(V_{SS} = 0V, V_{DD} = 2.7 \text{ to } 6.0V, T_{opr} = -30 \text{ to } 60^{\circ}\text{C})$

| PARAMETER                    | SYMBOL | CONDITIONS         | Min.                     | Тур. | Max. | UNIT |

|------------------------------|--------|--------------------|--------------------------|------|------|------|

| January Mina Cordo Timo      |        | In the Normal mode | 8.3                      | 3    |      | μs   |

| Instruction Cycle Time       | tcy    | In the SLOW mode   | 235                      |      | 267  | μς   |

| High level Clock pulse Width | twch   | External clock     | 80                       | _    | _    | ns   |

| Low level Clock pulse Width  | twcL   | external clock     |                          |      |      |      |

| Shift Data Hold Time         | tson   |                    | 0.5t <sub>cy</sub> - 300 | -    |      | ns   |

Note. Shift Data Hold Time:

External Circuit for SCK pin and SO pin. Serial port (completion of transmission)

TONE OUTPUT CHARACTERISTICS

$(V_{SS} = 0V, V_{DD} = 2.7 \text{ to } 6.0V, T_{opr} = -30 \text{ to } 60^{\circ}\text{C})$

| PARAMETER                        | SYMBOL            | CONDITIONS                       | Min. | Тур. | Max. | UNIT  |

|----------------------------------|-------------------|----------------------------------|------|------|------|-------|

| Tone Output Voltage (ROW)        | V <sub>TONE</sub> | RL≥ 10KΩ, V <sub>DD</sub> = 2.7V | 125  | 185  | 250  | mVrms |

| Pre-emphasis High Band (COL/ROW) | РЕНВ              | PEHB = 20log (COL/ROW)           | 1    | 2    | 3    | d8    |

| Output Distortion                | DIS               |                                  | _    | -    | 10   | %     |

| Frequency Stability              | Δf                | Except error of osc. frequency   | _    | _    | 0.7  | %     |

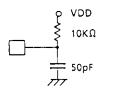

RECOMMENDED OSCILLATING CONDITIONS

$(V_{SS} = 0V, VDD = 2.7 \text{ to } 6.0V, Topr = -30 \text{ to } 60^{\circ}\text{C})$

960KHz Ceramic Resonator

## (2) I/O Ports

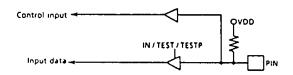

The input/output circuitries of the 47C858 I/O ports are shown below, any one of the circuitries can be chosen by a code (WB, WE, WH) as a mask option.

| PORT                 | 1/0   | INPUT/OUTPUT CIRCUITRY and CODE |                             | REMARKS                                                                            |

|----------------------|-------|---------------------------------|-----------------------------|------------------------------------------------------------------------------------|

| K0                   | Input | R <sub>IN</sub> X               |                             | Pull-up resistor $R_{IN} = 70K\Omega \text{ (typ.)}$ $R = 1K\Omega \text{ (typ.)}$ |

| R3<br>R4<br>R5<br>R6 | 1/0   | Initial "Hi-Z"                  | WE, WH  Initial "High"  VDD | Sink open drain or push-pull output R = 1KΩ (typ.)                                 |

| R7<br>RA             | I/O   | Initial "Hi-Z"                  | Initial "High" OVDD         | Sink open drain  or  push-pull output  R = 1KΩ (typ.)                              |

| R8                   | 1/0   |                                 |                             | Sink open drain<br>Initial "Hi-Z"<br>Hysteresis input<br>R = 1KΩ (typ.)            |

| R9                   | 1/0   | WB, WE                          | Initial "High" OVDD         | Sink open drain  or  push-pull output  Hysteresis input  R = 1KΩ (typ.)            |