# TSC 55

# **TS3404**

# Single Synchronous Buck PWM Controller

SOP-8

Pin assignment

1. Boot 8. Phase

2. Ugate 7. COMP

3. Gnd 6. FB

4. Lgate 5. Vcc

Oscillator Frequency up to 300KHz

0.8V Internal Reference

Drives N-Channel MOSFETs

## General Description

The TS3405 makes simple work out of implementing a complete control and protection scheme for a DC-DC step-down converter. Designed to drive N-channel MOSFETs in a synchronous buck topology, the TS3405 integrates the control, output a adjustment, monitoring and protection functions.

The TS3405 provides simple, single feedback loop, voltage mode control with fast transient response. The output voltage can be precisely regulated to as low as 0.8V, with a maximum tolerance of ±1.5% over temperature and line voltage variations. A fixed frequency oscillator reduces design complexity, while balancing typical application cost and efficiency.

The error amplifier features a 15MHz gain-bandwidth product and 8V/uS slew rate, which enables high converter bandwidth for fast transient performance. The resulting PWM duty cycles range from 0% to 100%. The protection from over current conditions is provided by monitoring the Rds(on) of the lower MOSFET to inhibit PWM operation appropriately. This approach simplifies the implementation and improves efficiency by eliminating the need for a current sense resistor.

## **Features**

- ♦ Buck converter Vin operate from 3.3V ~ 14V

- ♦ Vcc operate from 3.75V ~ 6V

- ♦ Buck converter Vin can be greater than Vcc

- ♦ 0.8V to Vin output voltage

- ♦ Simple single –loop control design

- ♦ Voltage-mode PWM control

- Loss less, programmable over current protection uses lower MOSFET's Rds(on)

- Internal soft start

- Converter can source and sink current

- → Fixed oscillator frequency 300KHz

# **Applications**

- Power supplies for microprocessors

- Subsystem power supplies

- ♦ Cable modems, set-top box, DSL modems

- ♦ DSP and core communications processor supplies

- ♦ Memory supplies

- Personal computer peripherals

- Industrial power supplies

- ♦ Low-voltage distributed power supplies

## Ordering Information

| Part No. | Operating Temp. | Package |

|----------|-----------------|---------|

| TS3405CS | -40 ~ +85 °C    | SOP-8   |

## Absolute Maximum Rating

| Supply Voltage                                     | V <sub>CC</sub>                      | 6                    | V  |

|----------------------------------------------------|--------------------------------------|----------------------|----|

| Operating Supply Voltage                           | V <sub>CC</sub>                      | 4.5 ~ 5.5            | V  |

| Absolute Boot Voltage                              | $V_{BOOT}$                           | 20                   | V  |

| Upper Driver Supply Voltage                        | V <sub>BOOT</sub> V <sub>PHASE</sub> | 20                   | V  |

| Input, Output or I/O Voltage                       |                                      | Gnd-0.3V to Vcc+0.3V | V  |

| Operating Junction Temperature Range               | T <sub>J</sub>                       | -40 ~ +125           | °C |

| Ambient Temperature Range                          | TJ                                   | -40 ~ +85            | °C |

| Storage Temperature Range                          | T <sub>STG</sub>                     | -65 ~ +150           | °C |

| Lead Temperature 1.6mm(1/16") from case for 10Sec. | T <sub>LEAD</sub>                    | 260                  | °C |

TS3405 1-10 2003/12 rev. A

| Pin D | escriptions |                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.   | Pin.        | Descriptions                                                                                                                                                                                                                                                                                                                                            |

| 1     | Boot        | This pin provides ground referenced bias voltage to the upper MOSFET driver. A bootstrap circuit is used to create a voltage suitable to drive a logic-lever N-channel MOSFET. It can take 20V as the maximum voltage. It can be powered by a DC power supply or powered by a boost strap circuit.                                                      |

| 2     | Ugate       | This pin provides the PWM controlled gate driver for the upper MOSFET. It is also monitored by the adaptive shoot-through protection circuitry to determine when the upper MOSFET can be turned on. The sourcing Rds(on) is $15\Omega$ and the sink Rds(on) is $7\Omega$ . Ugate can handle high voltage up to maximum 20V.                             |

| 3     | Gnd         | This pin represents the signal and power ground for the IC. Tie this pin to the ground island/plane through the lowest impedance connection available.                                                                                                                                                                                                  |

| 4     | Lgate       | This pin provides the PWM controlled gate drive for the lower MOSFET. This pin is also monitored by the adaptive shoot-through protection circuitry to determine when the lower MOSFET can be turned on.                                                                                                                                                |

| 5     | Vcc         | This pin provides the bias supply for the TS3405, as well as the lower MOSFET's gate.  Connect a well-decoupled 5V supply to this pin.                                                                                                                                                                                                                  |

| 6     | FB          | This pin is the inverting input of the internal error amplifier. Use this pin in combination with the COMP Pin to compensate the voltage-control feedback loop of the converter.                                                                                                                                                                        |

| 7     | COMP        | During soft start and all the time during normal converter operation, this pin represents the output of the error amplifier. Use this pin in combination with the FB pin to compensate the voltage control feedback loop of the converter. Pulling COMP to a level below 0.3V enables soft start process. The whole soft start process takes about 5mS. |

| 8     | Phase       | This pin is used to monitor the voltage drop across the lower MOSFET for over current protection. The OCP threshold is –30mV. If Phases is less thean –300mV, the upper MOSFET cannot be turned-on in the next cycle.                                                                                                                                   |

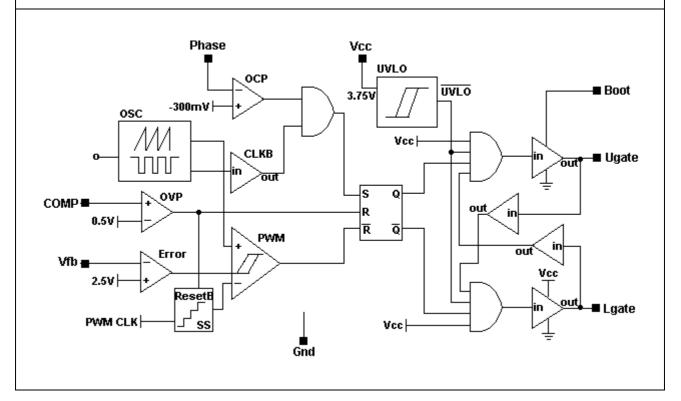

# Block Diagram

TS3405 2-10 2003/12 rev. A

| Parameter                    | Symbol                 | Test Conditions                                     | Min  | Тур  | Max  | Unit  |

|------------------------------|------------------------|-----------------------------------------------------|------|------|------|-------|

| Vcc supply current           |                        |                                                     |      |      |      |       |

| Nominal supply               | IVcc                   |                                                     | 2.6  |      | 3.8  | mA    |

| Power-on reset               |                        |                                                     |      |      |      |       |

| Rising Vcc power-on reset    |                        |                                                     | 3.8  | 4.0  | 4.2  |       |

| threshold                    | POR                    |                                                     |      |      |      | - V   |

| Vcc power-on reset threshold | FOR                    |                                                     | 0.24 | 0.25 | 0.30 | \ \ \ |

| Hysteresis                   |                        |                                                     |      |      |      |       |

| Oscillator                   |                        |                                                     |      |      |      |       |

| Frequency                    | Fosc                   | Vcc= 5V                                             | 250  | 300  | 340  | KHz   |

| Ramp amplitude               | $\Delta V_{OSC}$       |                                                     |      | 1.5  |      | V     |

| Reference                    |                        |                                                     |      |      |      |       |

| Reference voltage Tolerance  | .,                     |                                                     |      |      | 1.5  | %     |

| Nominal reference voltage    | V <sub>REF</sub>       |                                                     |      | 8.0  |      | V     |

| Error Amplifier              |                        |                                                     |      |      |      |       |

| DC Gain                      |                        |                                                     |      | 82   |      | dB    |

| Gain-bandwidth product       | GBWP                   |                                                     | 14   |      |      | MHz   |

| Slew rate                    | SR                     | COMP= 10pF                                          | 4.65 | 8.0  | 9.2  | V/uS  |

| Gate Drivers                 |                        |                                                     |      |      |      |       |

| Upper gate source driver     | I <sub>UGATE-SRC</sub> | V <sub>BOOT</sub> = 10V, I <sub>UGATE</sub> = 100mA |      | 15   |      | Ω     |

| Upper gate sink driver       | I <sub>UGATE-SNK</sub> |                                                     |      | 7    |      |       |

| Lower gate source driver     | I <sub>LGATE-SRC</sub> | V <sub>VCC</sub> = 5V, I <sub>LGATE</sub> = 100mA   |      | 9.5  |      | Ω     |

| Lower gate sink driver       | I <sub>LGATE-SNK</sub> |                                                     |      | 3.5  |      |       |

| Protection / Disable         |                        |                                                     |      |      |      |       |

| OCP threshold                | V <sub>OCP</sub>       | V <sub>VCC</sub> = 5V, sweep Phase                  |      | -300 |      | mV    |

| Disable threshold            | $V_{DISABLE}$          | Sweep COMP                                          |      | 0.3  |      | V     |

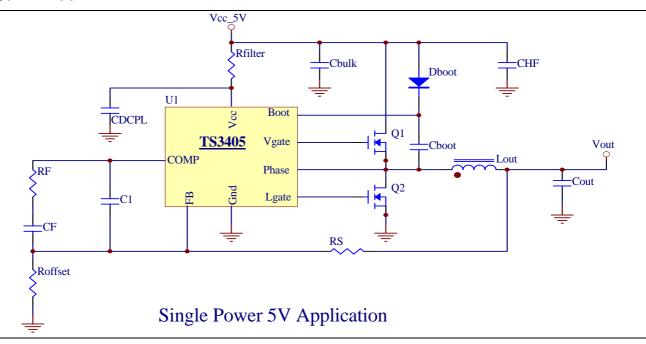

# Typical Application

TS3405 4-10 2003/12 rev. A

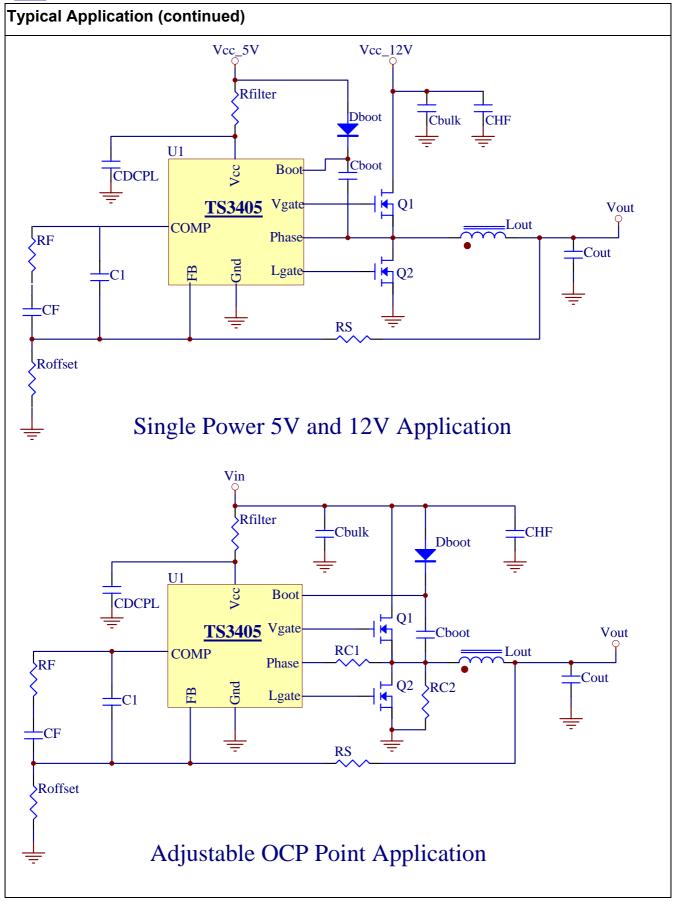

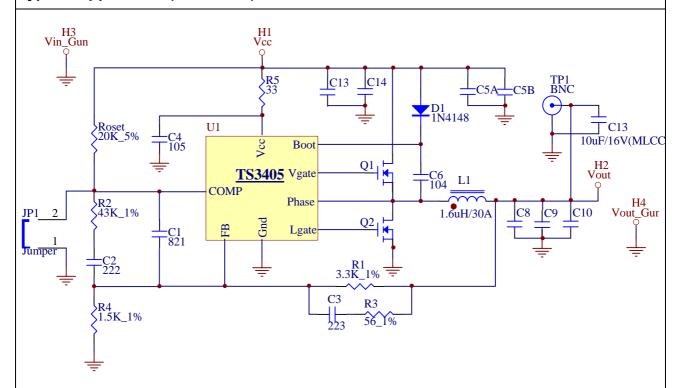

# Typical Application (continued)

| Commonant                   | Deference design | Maximum load current |                |                |  |

|-----------------------------|------------------|----------------------|----------------|----------------|--|

| Component                   | Reference design | 5A                   | 10A            | 15A            |  |

| MOSFET                      | Q1、Q2            | Rds(on) < 30mΩ       | Rds(on) < 20mΩ | Rds(on) < 10mΩ |  |

| Inductor                    | L1               | 5uF                  | 3uF            | 1.6uF          |  |

| No. of input capacitor      | C13、C14          | 1                    | 1              | 2              |  |

| No. of output capacitor     | C8、C9、C10        | 1                    | 2              | 3              |  |

| No. of decoupling capacitor | C5A、C5B          | 1                    | 1              | 2              |  |

Reference design capacitor : 1500uF(ESR=33)

Reference design decoupling capacitor : 10uF(MLCC)

TS3405 5-10 2003/12 rev. A

## Functional Description

#### Start Up

The TS3405 automatically initializes upon receipt of power. The Power-On Reset (POR) function continually monitors the bias voltage at the Vcc pin. The POR function initiates the Soft Start (SS) operation after the supply voltage exceeds its POR threshold.

### **Over Current Protection (OCP)**

The over current function protects the converter from a shorted output by using the lower MOSFET's on-resistance, Rds(on), to monitor the current. Therefore, even the power input voltage is greater than Vcc, TS3405 still can support this. This method enhances the converter's efficiency and reduces cost by eliminating a current sensing resistor.

The TS3405's OCP threshold is a fixed value, -300mV, when Phase voltage is less -300mV, the next on-cycle will not be initialized.

### **Over Voltage Protection (OVP)**

An over voltage protection comparator is monitoring the COMP. When COMP voltage is less than 0.3V, the Soft Start (SS) process is initiated.

### Soft Start (SS)

Both POR and OVP initiate the soft start sequence after the over current set point has been sampled. Soft Start clamps virtually the error amplifier output (COMP pin) and reference input (non-inverting terminal of the error amp) to the internally generated Soft Start voltage. The oscillator's triangular waveform is compared to the ramping error amplifier voltage. This generates Phase pulses of increasing width that charge the output capacitor(s). when the internally generated Soft Start voltage exceeds the COMP pin voltage, the output voltage is in regulation. This method provides a rapid and controlled output voltage rise. The entire startup sequence typically takes about 5mS.

## **Current Sinking**

The TS3405 incorporates a MOSFET shoot-through protection method which allows a converter to sink current as well as source current. Care should be exercised when designing a converter with the TS3405 when it is known that the converter may sink current.

When the converter is sinking current, it is behaving as a boost converter that is regulating its input voltage. This means that the converter is boosting current into the buck converter input power, if the buck converter input power has the same supply source which supplies the bias voltage, Vcc to the TS3405. If there is nowhere for this current to go, such as to other distributed loads on the Vcc rail, through a voltage limiting protection device, or other methods, the capacitance on the Vcc bus will absorb the current. This situation will allow voltage level of the Vcc rail to increase. If the voltage level of the rail is boosted to a level that exceeds the maximum voltage rating of the TS3405, then the IC will experience an irreversible failure and the converter will no longer be operational. Ensuring that there is a path for the current to follow other than the capacitance on the rail will prevent this failure mode.

TS3405 6-10 2003/12 rev. A

## Application Guidelines

## **Component Selection**

#### **Input Capacitor**

Use a mix of input bypass capacitors to control the voltage overshoot across the MOSFETs. Use small ceramic capacitors for high frequency decoupling and bulk capacitors to supply the current needed each time Q1 turn on. Place the small ceramic capacitors physically close to the MOSFETs and between the drain of high side MOSFET (Q1) and the source of low side MOSFET (Q2).

The important parameters for the bulk input capacitor are the voltage rating and the RMS current rating. For reliable operation, select the bulk capacitor with voltage and current rating above the maximum input voltage and largest RMS current required by the circuit. The capacitor voltage rating should be at least 1.25 times greater than the maximum input voltage and a voltage rating of 1.5 times is a conservative guideline. The RMS current rating requirement for the input capacitor of a buck regulator is approximately 1/2 the DC load current.

For a through hole design, several electrolytic capacitors may be needed. For surface mount designs, solid tantalum capacitors can be used, but caution must be exercised with regard to the capacitor surge current rating. These capacitors must be capable of handling the surge-current at power-up. Some capacitor series available from reputable manufacturers are surge current tested.

## MOSFET

The TS3405 requires 2 N-channel power MOSFETs. These should be selected based upon Rds(on), gate vlagus requirements. and thermal management requirements. In high-current applications, the MOSFET power dissipation, package selection and heatsink are the dominant design factors. The power dissipation includes two loss components; conduction loss and switching loss. The conduction losses are the largest component of power dissipation for both the upper and the lower MOSFETs. These losses are distributed between the two MOSFETs according to duty factor. The switching losses seen when sourcing current will be different from the switching losses seen when sinking current. When sourcing current, the upper MOSFET realizes most of the switching losses. The lower switch realizes most of the switching losses when the converter is sinking current (see the equations below).

These equations assume linear voltage current transitions and do not adequately model power loss due

the reverse-recovery of the upper and lower MOSFET's body diode. The gate-charge losses are dissipated by the TS3405 and do not heat the MOSFETs. However, large gate-charge increases the switching interval,  $t_{\rm SW}$  which increases the MOSFET switching losses. Ensure that both MOSFETs are within their maximum junction temperature at high ambient temperature by calculating tempature rise according to package thermal-resistance specifications. a separate heatsink may be necessary depending upon MOSFET power, package type, ambient temperature and air flow.

Losses while sourcing current:

$P_{UPPER} = Io^2 x Rds(on) x D + \frac{1}{2} Io x Vin x t_{SW} x F_S$  $P_{LOWER} = Io^2 x Rds(on) x (1-D)$

Losses while sinking current:

$P_{UPPER} = Io^2 x Rds(on) x D$

$P_{LOWER}$ =  $Io^2$  x Rds(on) x (1-D) +  $\frac{1}{2}$  Io x Vin x  $t_{SW}$  x  $F_S$

Where: **D** is the duty cycle = Vout / Vin

t<sub>sw</sub> is the combined switch ON and OFF time

**F**<sub>S</sub> is the switching frequency

Given the reduced available gate bias voltage (5V), logic-level or sub-logic-level transistors should be used for both N-MOSFETs. Caution should be exercised with devices exhibiting very low Vgs(on) characteristics. The shoot through protection present aboard the TS3405 may be circumvented by there MOSFETs if they have large parasitic impedances and /or capacitances that would inhibit the gate of the MOSFET from being discharged below it's threshold level before the complementary MOSFET is turned on.

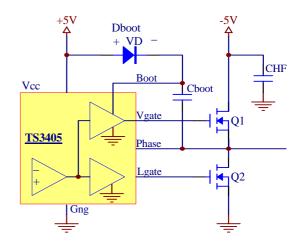

FIGURE 5. Upper Gate drive bootstrap.

Fig. 5 shows the upper gate drive (Boot pin) supplied by a bootstrap circuit from Vcc. The boot capacitor.  $C_{BOOT}$ , develops a floating supply voltage referenced to the Phase pin. The supply is refreshed to a voltage of Vcc less the boot diode drop ( $V_{DP}$ ) each time the lower MOSFET turns on.

TS3405 7-10 2003/12 rev. A

## **Application Guidelines (continued)**

#### **Output Inductor**

The output inductor is selected to meet the output voltage ripple requirements and minimize the converter's response time to the load transient. The inductor value determines the converter's ripple current and the ripple voltage is a function of the ripple current. The ripple voltage and current are approximated by the following equations:

$\Delta I = (Vin - Vout) / F_S x L x (Vout / Vin)$  $\Delta Vout = \Delta I x ESR$

Increasing the value of inductance reduces the ripple current and voltage. However, the large inductance values reduce the converter's response time to a load transient. One of the parameters limiting the converter's response to a load transient is the time required to change the inductor current. Given a sufficiently fast control loop design, the TS3405 will provide either 0% or 100% duty cycle in response to a load transient. The response time is the time required to slew the inductor current from an initial current value to the transient current level. During this interval the difference between the inductor current and the transient current level must be supplied by the output capacitor to minimizing the response time can minimize the output capacitance required.

The response time to a transient is different for the application of load and the removal of load. The following equations give the approximate response time interval for application and removal of a transient load:

$t_{RISE} = (L \times I_{TRAN}) / (Vin - Vout)$   $t_{FALL} = (L \times I_{TRAN}) / Vout$ where:

$I_{\text{TRAN}}$  is the transient load current step

$\ensuremath{t_{\text{RISE}}}$  is the response time to the application of load

$t_{\sf FALL}$  is the response time to the removal of load the worst case response time can be either at the equations at the minimum and maximum output levels for the worst case response time.

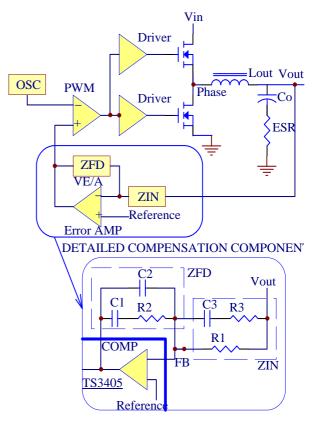

#### **Feedback Compensation**

Fig. 6 highlights the voltage-mode control loop for a synchronous-rectified buck converter. The output voltage (Vout) is regulated to the reference voltage level. The error amplifier (Error Amp) output (VE/A) is compared with the oscillator (OSC) triangular wave to provide a pulse-width modulated (PWM) wave with a amplitude of Vin at the Phase node. The PWM wave is smoothed by the output filter (Lo and Co).

The modulator transfer function is the small-signal transfer function of Vout /  $V_{\text{E/A}}$ . This function is dominated by a DC Gain and the output filter (Lo and Co), with a double pole break frequency at  $F_{\text{LC}}$  and a zero at  $F_{\text{ESR}}$ . The DC Gain of the modulator is simply the imput voltage (Vin) divided by the peak-to-peak oscillator voltage  $V_{\text{OSC}}$ .

### Modulator Break Frequency Equations

$F_{LC} = 1 / 2\pi x \sqrt{Lo x Co}$  $F_{ESR} = 1 / 2\pi x ESR x Co$

### **Compensation Break Frequency Equations**

$F_z = 1 / 2\pi \times R_2 \times C_1$

$F_{P1} = 1 / 2\pi \times R_2 \times [(C_1 \times C_2) / (C_1 + C_2)]$

$F_{Z1} = 1 / 2\pi \times (R_1 + R_3) \times C_3$

$F_{P2} = 1 / 2\pi \times R_3 \times C_3$

The compensation network consists of the error amplifier (internal to the TS3405) and the impedance networks ZIN and ZFB. The goal of the compensation network is to provide a closed loop transfer function with the highest 0dB crossing frequency (f0dB) and adequate phase margin. Phase margin is the difference between the closed loop phase at f0dB and 180 degrees.

FIGURE 6. Voltage-mode buck converter compensation design.

TS3405 8-10 2003/12 rev. A

#### **Application Guidelines (continued)**

The equations below relate the compensation network's poles, zeros and gain to the components ( $R_1$ ,  $R_2$ ,  $R_3$ ,  $C_1$ ,  $C_2$  and  $C_3$ ) in Fig. 7. Use these guidelines for locating the poles and zeros of the compensation network:

- 1. Pick Gain  $(R_2/R_1)$  for desired converter bandwidth.

- 2. Place 1<sup>st</sup> zero below filter's double pole (~75% F<sub>LC</sub>)

- 3. Place 2<sup>nd</sup> zero at filter's double pole.

- 4. Place 1st pole at the ESR zero.

- 5. Place 2<sup>nd</sup> pole at half the switching frequency

- 6. Check gain against error amplifier's open-loop gain.

- 7. Estimate phase margin repeat if necessary.

#### **Output Capacitor Selection**

An output capacitor is required to filter the output and supply the load transient current. The filtering requirements are a function of the switching frequency and the ripple current. The load transient requirements are a function of the slew rate (di/dt) and the magnitude of the transient load current. These requirements are generally met with a mix of capacitors and careful layout. Modern components and loads are capable of producing transient load rates above 1A/nS. High frequency capacitors initially supply the transient and slow the current load rate seen by the bulk capacitors. The bulk filter capacitor values are generally determined by the ESR (Effective Series Resistance) and voltage rating requirements rather than actual capacitance requirements.

High frequency decoupling capacitors should be placed as close to the power pins of the load as physically possible. Be careful not to add inductance in the circuit board wiring that could cancel the usefulness of these low inductance components. Consult with the manufacturer of the load on specific decoupling requirements.

Use only specialized low-ESR capacitors intended for switching-regulator applications for the bulk capacitors. The bulk capacitor's ESR will determine the output ripple voltage and the initial voltage drop after a high slew-rate transient. An aluminum electrolytic capacitor's ESR value is related to the case size with lower ESR available in larger case sizes. However, the equivalent Series inductance (ESL) of these capacitors increases with case size and can reduce the usefulness of the capacitor to high slew-rate transient loading. Unfortunately, ESL is not a specified parameter. Work with your capacitor supplier and measure the capacitor's impedance with frequency to select a suitable component.

In most cases, multiple electrolytic capacitors of small case size perform better than a single large case capacitor.

#### **Feedback Divider**

The reference of TS3405 is 0.8V. the output voltage can be set by  $R_1$  and  $R_4$  as shown in Fig. 4. The equation is following:

## Vout = $0.8 \times (1 + R_1 / R_4)$

The R1 should be between  $2k\Omega$  to  $5k\Omega$ . put the R<sub>1</sub>, R<sub>4</sub> and others compensation component as close to TS3405 as possible.

#### Shutdown

Pulling low the COMP pin can shutdown the TS3405 PWM controller. You can use a small single transistor as switch like as JP1 shown in Fig. 4.

### **Compensation Break Frequency Equations**

As in any high frequency switching converter, layout is very important. Switching current from one power device to another can generate voltage transients across the impedances of the interconnecting bond wires and circuit traces. Using wide, short printed circuit traces should minimize these interconnecting impedances. The critical components should be located as close together as possible, using ground plane construction or single point grounding.

To minimize the voltage overshoot, the interconnecting wires indicated by heavy lines should be part of a ground or power plane in a printed circuit board. Locate the TS3405 within 3 inches of the MOSFETs. Q1 and Q2. The circuit traces for the MOSFETs' gate and source connections from the TS3405 must be sized to handle up to 1A peak current. Provide local Vcc decoupling between Vcc and Gnd pins. Locate the capacitor,  $C_{\rm BOOT}$  as close as practical to the Boot and Phase pins. All components used for feedback compensation should be located as close to the IC a practical.

TS3405 9-10 2003/12 rev. A

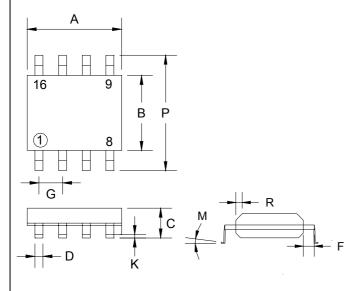

# SOP-8 Mechanical Drawing

| SOP-8 DIMENSION |                    |                    |                      |                      |  |

|-----------------|--------------------|--------------------|----------------------|----------------------|--|

| DIM             | MILLIMETERS        |                    | INCHES               |                      |  |

|                 | MIN                | MAX                | MIN                  | MAX                  |  |

| Α               | 4.80               | 5.00               | 0.189                | 0.196                |  |

| В               | 3.80               | 4.00               | 0.150                | 0.157                |  |

| С               | 1.35               | 1.75               | 0.054                | 0.068                |  |

| D               | 0.35               | 0.49               | 0.014                | 0.019                |  |

| F               | 0.40               | 1.25               | 0.016                | 0.049                |  |

| G               | 1.27 (typ)         |                    | 0.05 (typ)           |                      |  |

| K               | 0.10               | 0.25               | 0.004                | 0.009                |  |

| М               | 0°                 | 7°                 | 0°                   | 7°                   |  |

| Р               | 5.80               | 6.20               | 0.229                | 0.244                |  |

| R               | 0.25               | 0.50               | 0.010                | 0.019                |  |

| K<br>M<br>P     | 0.10<br>0°<br>5.80 | 0.25<br>7°<br>6.20 | 0.004<br>0°<br>0.229 | 0.009<br>7°<br>0.244 |  |