1

## Qualpack TS87C51RD2/TS83C51RD2

# Qualification Package TS87C51RD2 / TS83C51RD2 CMOS 0.5µm

TS87C51RD2 / TS83C51RD2 CMOS 0.5 µm JUNE 2001

# 1 Contents

| 1 | 1 CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 2 | 2 GENERAL INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3 |

| 3 | 3 TECHNOLOGY INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4 |

|   | <ul> <li>3.1 WAFER PROCESS TECHNOLOGY</li> <li>3.2 PRODUCT DESIGN</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| 4 | 4 QUALIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6 |

|   | <ul> <li>4.1 QUALIFICATION FLOW.</li> <li>4.2 WAFER PROCESS QUALIFICATION.</li> <li>4.2.1 Process Module Reliability.</li> <li>4.2.1.1 Hot carrier qualification</li> <li>4.2.1.2 Electro-migration</li> <li>4.2.1.3 Time Dependent Dielectric Breakdown</li> <li>4.2.1.3.1 Field oxide.</li> <li>4.2.1.3.2 High Voltage MOS Gate oxide transistors</li> <li>4.3 T87C51RD2 QUALIFICATION TESTS</li> <li>4.3.1 Design tests</li> <li>4.3.2 Package tests</li> <li>4.3.3 Qualification status.</li> </ul> |   |

| 5 | 5 ENVIRONMENTAL INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| 6 | 6 OTHER DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

|   | <ul> <li>6.1 ISO9001 AND QS900 CERTIFICATES</li> <li>6.2 DATA BOOK REFERENCE</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

## Qualpack TS87C51RD2/TS83C51RD2

# 2 General Information

| Product Name:<br>Function:                                                                                                                                                                                           | TS87C51RD2<br>8 Bits Microcontroller, 64K bytes memory                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                      | TS87C51RD2: 64k EPROM<br>TS83C51RD2: 64k ROM                                                                                                                                                                                                                                                                                                  |

| Wafer Process:                                                                                                                                                                                                       | CMOS 0.5um                                                                                                                                                                                                                                                                                                                                    |

| Available Package Types                                                                                                                                                                                              | PLCC 44, VQFP 44 1.4, PDIL 40, PLCC 68, VQFP 64 1.4                                                                                                                                                                                                                                                                                           |

| Other Forms:                                                                                                                                                                                                         | Die, Wafer                                                                                                                                                                                                                                                                                                                                    |

| Locations:<br>Process Development,<br>Product Development<br>Wafer Plant<br>QC Responsibility<br>Probe Test<br>Assembly<br>Final Test<br>Lot Release<br>Shipment Control<br>Quality Assurance<br>Reliability Testing | ATMEL Nantes , France<br>ATMEL Nantes , France<br>ATMEL Nantes , France<br>ATMEL Nantes , France<br>ATMEL Nantes , France<br>Dependant upon Package<br>Dependant upon Package<br>ATMEL Nantes, France<br>GLOBAL LOGISTICS CENTER, Philippines<br>ATMEL Nantes, France<br>ATMEL Nantes, France<br>ATMEL Nantes, France<br>ATMEL Nantes, France |

ATMEL Nantes, France

Failure Analysis

Quality Assurance Management ATMEL Nantes, France

Signed: Pascal LECUYER

# 3 Technology Information

#### 3.1 Wafer Process Technology

| Process Type (Name):                                                                                  | Z94 (SCMOS3 Non Volatile - EPROM)<br>Z92 (SCMOS3 - ROM)                                     |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Base Material:<br>Wafer Thickness (final)<br>Wafer Diameter                                           | Bulk<br>475µm<br>150 mm                                                                     |

| Number Of Masks                                                                                       | Z94: 22<br>Z92: 14                                                                          |

| Gate Oxide (Logic transistors)<br>Material<br>Thickness                                               | Silicon Dioxide<br>110 A                                                                    |

| Gate Oxide (EPROM cell)<br>Material<br>Thickness                                                      | Silicon Dioxide<br>220 A                                                                    |

| Polysilicon<br>Number of Layers<br>Thickness Poly 1<br>Thickness Poly 2                               | 2 (Z94), 1 (Z92)<br>2000A<br>3000A                                                          |

| Metal<br>Number of Layers<br>Material:<br>Layer 1 Thickness<br>Layer 2 Thickness<br>Layer 3 Thickness | 2<br>AlCu<br>5150A<br>5150A<br>7650A                                                        |

| Passivation<br>Material<br>Thickness                                                                  | Z94: SiO2 / Nitride Oxide – Z92: SiO2 / Nitride<br>Z94: 3000A / 15000A – Z92: 2600A / 6400A |

# Qualpack TS87C51RD2/TS83C51RD2

### 3.2 Product Design

| Die Size                       | 4260µm * 4300µm (17.47mm2) |

|--------------------------------|----------------------------|

| Pad Size Opening               | 80µm * 80µm                |

| Logic Effective Channel Length | 0.5µm                      |

| Gate Poly Width (min.)         | 0.50μm                     |

| Gate Poly Spacing (min.)       | 0.60μm                     |

| Metal 1 Width                  | 0.60μm                     |

| Metal 1 Spacing                | 0.70μm                     |

| Metal 2 Width                  | 0.80μm                     |

| Metal 2 Spacing                | 0.70μm                     |

| Metal 3 Width                  | 0.80μm                     |

| Metal 3 Spacing                | 0.70μm                     |

| Contact size                   | 0.60µm                     |

| Via 1 size                     | 0.60µm                     |

| Via 2 size                     | 0.60µm                     |

### 4 Qualification

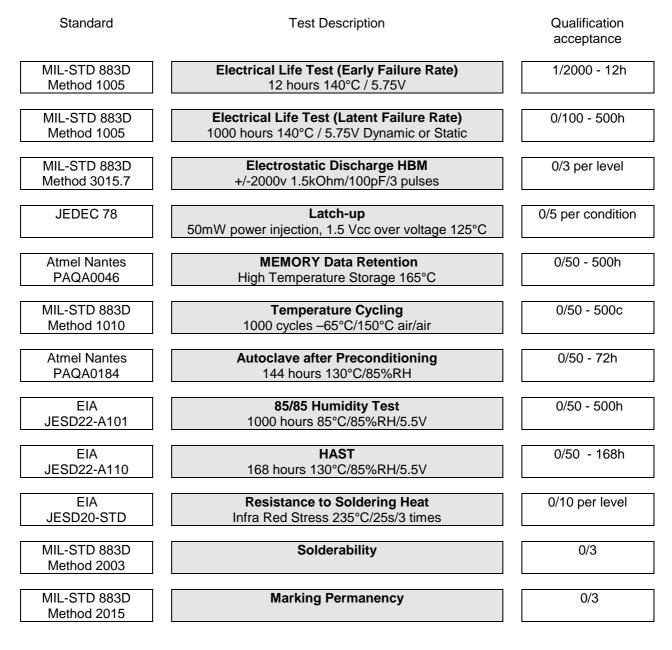

### 4.1 Qualification Flow

General Requirements for Plastic packaged CMOS IC

### 4.2 Wafer Process Qualification

#### 4.2.1 Process Module Reliability

This chapter contains all the information relative to the reliability of the SCMOS3 NV technology. Results presented in the following sections concern the reliability of the basic process steps which build up the technology.

### 4.2.1.1 Hot carrier qualification

#### STATIC NMOS DEGRADATION

| Channel length in µm                                  | 0.5   | 0.55  | 0.6   | 0.65  | 0.7   | 0.5     |

|-------------------------------------------------------|-------|-------|-------|-------|-------|---------|

| Process corner                                        | Fast  | Fast  | Fast  | Fast  | Fast  | Typical |

| Substrate current in µA/µm<br>VD=5.5V, VG=2.25V       | 17    | 15    | 13.4  | 12.1  | 11.1  | 14.7    |

| Substrate current in µA/µm<br>VD=3.6V, VG=1.6V        | 0.35  | 0.3   | 0.25  | 0.22  | 0.2   | 0.3     |

| Lifetime in seconds for 10% shift of<br>Gm at VD=5.5V | 3.2e3 | 3.7e3 | 4.2e3 | 4.7e3 | 5.2e3 | 3.8e3   |

| Lifetime in seconds for 10% shift of<br>Gm at VD=3.6V | 8e7   | 10e7  | 12e7  | 14e7  | 16e7  | 10e7    |

#### STATIC PMOS DEGRADATION

| Channel length in µm                               | 0.5    | 0.55   | 0.6    | 0.65   | 0.7    | 0.5     |

|----------------------------------------------------|--------|--------|--------|--------|--------|---------|

| Process corner                                     | Fast   | Fast   | Fast   | Fast   | Fast   | Typical |

| Substrate current in µA/µm<br>VD=5.5V, VG=2.25V    | 0.31   | 0.28   | 0.25   | 0.22   | 0.21   | 0.24    |

| Substrate current in µA/µm<br>VD=3.6V VG=1.25V     | 2.3e-3 | 1.9e-3 | 1.6e-3 | 1.4e-3 | 1.1e-3 | 1.6e-3  |

| Lifetime in seconds for 10% shift of Gm at VD=5.5V | 2.7e4  | 3.1e4  | 3.5e4  | 3.9e4  | 4.3e4  | 3.5e4   |

| Lifetime in seconds for 10% shift of Gm at VD=3.6V | 2e7    | 2.5e7  | 3e7    | 3.8e7  | 4.6e7  | 3.2e7   |

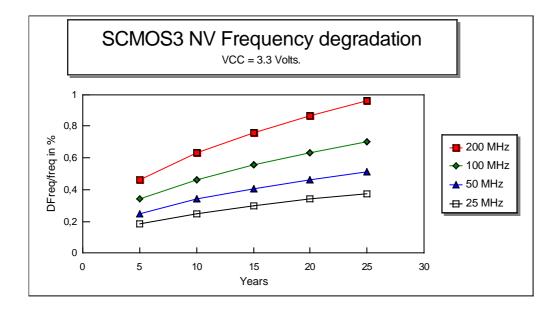

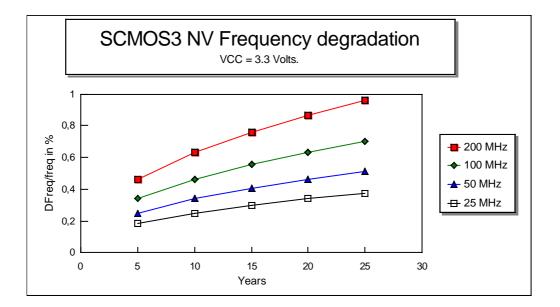

EXPERIMENTAL RESULTS IN DYNAMIC MODE : hot carrier degradation effects on inverter propagation time have been measured on oscillators running at 75 MHz at 7V and 6.5V. Accelerator factor in voltage is then carried out and expected degradation laws at 5V and 3.3V derived. The following graphs show the frequency degradation of oscillators running at 5V and 3.3V.

# Qualpack TS87C51RD2/TS83C51RD2

### 4.2.1.2 Electro-migration

#### Characterization

Stresses of electro-migration are achieved for 1000 hours on 32 packaged metal line running on flat with a current density of  $2x10^6$  A/cm<sup>2</sup> at a temperature of 200°C. Lines are declared to be failed for a shift of the initial resistance by 20%. Results are summarized in the table below.

| Level  | W/L/T(1)    | Structure       | Failures |

|--------|-------------|-----------------|----------|

| Metal1 | 2/2000/0.50 | Ti/TiN/AICu/TiN | no       |

| Metal2 | 2/2000/0.50 | Ti/TiN/AICu/TiN | no       |

| Metal3 | 2/2000/0.70 | Ti/TiN/AICu/TiN | no       |

### (1) W/L/T=Width/Length/Thickness of the metal line in microns

Lifetime projection

The objective of reliability is to reach less than 10 FIT on metal line within 10 years at a temperature of 150°C. As no failures have been found at 1000 hours in the above stress conditions a lifetime projection in FIT is meaningless.

However, assuming for AlCu metalization an activation energy in temperature Ea of 0.60eV and an activation in current with a power-law coefficient n of 2, the current density which guarantees no failures within 10 years at 150°C can be extrapolated.

With these assumptions the projected current density for no failures at 150°C within 10 years is calculated as  $5x10^{5}$ A/cm<sup>2</sup> which is much higher than the current density of  $2x10^{5}$ A/cm<sup>2</sup> specified in the design rules.

### 4.2.1.3 Time Dependent Dielectric Breakdown

#### 4.2.1.3.1 Field oxide

#### QBD MEASUREMENT:

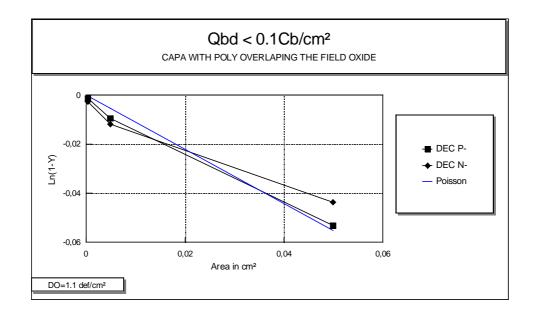

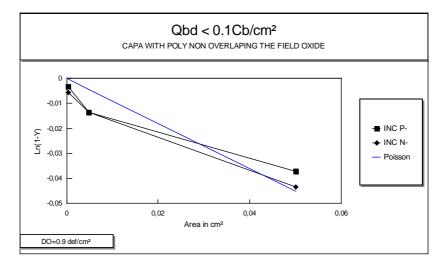

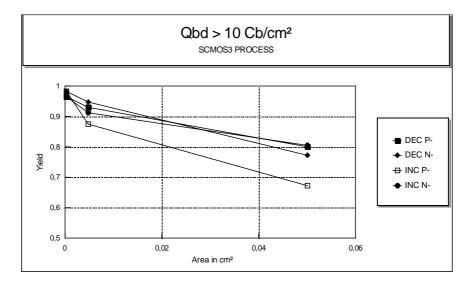

The critical charge, supported by the thin oxide and related to the extrinsic and intrinsic defects, is measured on TOX/P- and TOX/N- capacitors. The tested capacitor areas are varying from  $4.10^{-4}$  to  $5.10^{-2}$  cm<sup>2</sup>. Two types of capacitors with poly overlaping the field oxide (DEC) and poly non overlaping the field oxide (INC) are measured. The distributions have been obtained from 750 measurements for each area and type of capacitors on 10 different lots.

#### Extrinsic defects:

The two graphs here after represent the % of failures vs area for Qbd below or equal to 0.1 Cb/cm<sup>2</sup>. The law of Poisson is used to determine the D0 defect density of the extrinsic defects: X=1 exp(Area \* D0)

#### Poly overlaping the Field oxide on Tox/P- and Tox/N-:

The DO is found to be 1.1 def/cm<sup>2</sup>. This result is in agreement with the goal for DO of 1 def/cm<sup>2</sup>.

Poly non overlaping the Field oxide on Tox/P- and Tox/N-:

The DO is found to be 0.9def/cm<sup>2</sup>. This result is in agreement with the goal for DO of 1 def/cm<sup>2</sup>.

#### Intrinsic defects:

The graph here after represents the percentage of failure for a Qbd > 10 Cb/cm<sup>2</sup> vs the area. The worst case given by the bigest capacitors shows that 67% of the total distribution has a Qbd > 10 Cb/cm<sup>2</sup>. This result guarantees a good reliability behaviour. The critical charge, supported by thin oxide and related to the extrinsic defects, is measured on TOX/P- capacitors of 42570µm<sup>2</sup> and TOX/N- capacitors of 85140µm<sup>2</sup>. Following are the average results obtained on recent lots from a distribution of about 60 sites per wafer. The minimum specification limit is 10C/cm<sup>2</sup>.

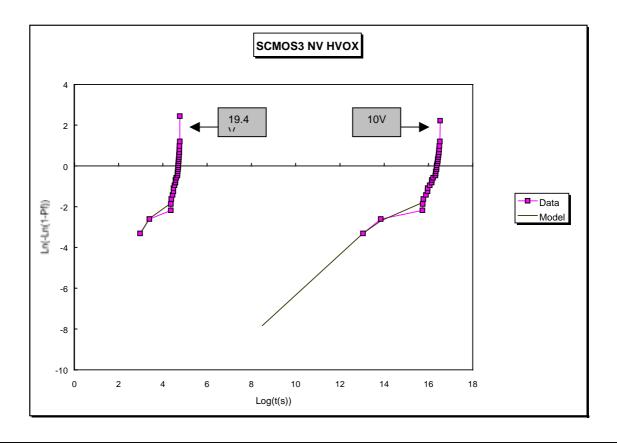

### 4.2.1.3.2 High Voltage MOS Gate oxide transistors

High voltage gate oxide transistors are used within the EPROM circuits to increase the external programming voltage up to 14.5 Volts. This operation is needed to reach the appropriate programming conditions. As a result, the maximum voltage between gate and source/drain of high voltage MOS transistors can be about 10 Volts .

The experiment consists of the application of an accelerated constant voltage stress until the breakdown of the oxide is reached. The time of the breakdown is then extrapolated for nominal voltage condition.

The capacitor is made with a 20nm oxide growth on P- substrate and the electrode is phosphorus doped poly : the capacitor area is 0.23 mm<sup>2</sup>.

The Time Dependant Dielectric Breakdown is accelerated in voltage and temperature. The temperature is set to 150°C so no acceleration factor depending on temperature is needed for the extrapolation of product lifetime. An unique accelerated electrical field of 9 MV/cm (19.4V for this oxide thickness) has been applied.

The experiment has been performed on capacitors issued from 3 wafers coming from 3 different lots : a set of 28 capacitors has been stressed.

A cumulative plot of failures obtained first at 19.4V and the second one projected to 10V with the relevant model are presented on the following figure :

The model predicts a failure level of about 1 ppm for 640 seconds at 150°C far above the specification of 0.01% then the High Voltage MOS gate oxide is qualified.

#### Conclusion:

The QBD results demonstrate high reliability level of SCMOS3 NV thin oxide.

### 4.3 T87C51RD2 Qualification Tests

This section summarizes the cumulated package level qualification data of the TS87C51RD2.

### 4.3.1 Design tests

| Lots                                | Device Type                   | Test Description      | Step           | Result         | Comment       |

|-------------------------------------|-------------------------------|-----------------------|----------------|----------------|---------------|

| <b>Z28303C</b><br>Z34922E<br>Z33543 | <b>TS87C51RD2</b><br>PLCC44   | EFR Dynamic Life Test | 12h            | 0/900          | EFR: 0 ppm    |

|                                     |                               | LFR Dynamic Life Test | 500h<br>1000h  | 0/300<br>0/300 | LFR: 19 fit   |

|                                     |                               | Data Retention 165°c  | 500h<br>1000h  | 0/150<br>0/150 |               |

| Z28882                              | <b>TS83C51RD2</b><br>DIL 40.6 | ESD                   | 3000v<br>4000v | 0/3<br>0/3     | Class 3       |

|                                     |                               | Latch-up              | 50mW<br>7.5v   | 0/5<br>0/5     | Latch-up free |

### 4.3.2 Package tests

| Lots              | Device Type | Test Description         | Step  | Result | Comment                  |

|-------------------|-------------|--------------------------|-------|--------|--------------------------|

| Z28303C           | TS87C51RD2  | 85/85 Humidity           | 500h  | 0/150  |                          |

| Z34922E<br>Z33543 | PLCC44      |                          | 1000h | 0/150  |                          |

|                   |             | Thermal Cycles           | 500c  | 0/150  |                          |

|                   |             |                          | 1000c | 0/150  |                          |

|                   |             | Moisture preconditioning | CSAM  | 0/30   | Pass level 1 of JEDEC 20 |

|                   |             | Level 1                  | Test  | 0/180  |                          |

|                   |             | Thermal Sh65°c/150°c     | 15ts  | 0/150  |                          |

|                   |             | HAST 130°c/85%rh         | 72h   | 0/150  |                          |

|                   |             |                          | 144h  | 0/150  |                          |

| Z25873C           | PLCC44      | Marking permanency       | -     | 0/3    |                          |

|                   |             | (resistance to solvents) |       |        |                          |

|                   |             | Solderability            | -     | 0/3    |                          |

### 4.3.3 Qualification status

The TS87C51RD2 and TS83C51RD2 have been qualified in July 1999.

### 5 Environmental Information

The Atmel Nantes Environmental Policy aims are :

- Reducing the use of harmful chemicals in its processes

- Reducing the content of harmful materials in its products

- Using re-cyclable materials wherever possible

- Reducing the energy content of its products

As part of that plan, Ozone Depleting Chemicals are being replaced either by Atmel Nantes or its sub-contractors' process.

Atmel Nantes site is ISO14001 certified since May 2000.

### Qualpack TS87C51RD2/TS83C51RD2

### 6 Other Data

6.1 ISO9001 and QS900 Certificates

### 6.2 Data Book Reference

The data sheet is available upon request to sales representative or upon direct access on ATMEL Wireless and Microcontrollers web site:

http://www.atmel-wm.com/

TS87C51RD2 8-bit Microcontroller

Address References All inquiries relating to this document should be addressed to the following:

ATMEL Nantes BP70602 44306 Nantes Cedex 3 France Telephone (33) 2 40 18 18 18 Telefax (33) 2 40 18 19 00

Or direct contact Pascal LECUYER Product Assurance Manager Telephone (33) 2 40 18 17 73 Telefax (33) 2 40 18 19 00

#### **Remarks:**

The information given in this document is believed to be accurate and reliable. However, no responsibility is assumed by Atmel for its use. No specific guarantee or warranty is implied or given by this data unless agreed in writing elsewhere.

Atmel reserves the right to update or modify this information without notification, at any time, in the interest of providing the latest information.

Parts of this publication may be reproduced without special permission on the condition that our author and source are quoted and that two copies of such extracts are placed at our disposal after publication. Before use of such reproduced material the user should check that the information is current.

Written permission must be obtained from the publisher for complete reprints or translations.