# 512K - 1 SERIAL FLASH

## **GENERAL DESCRIPTION**

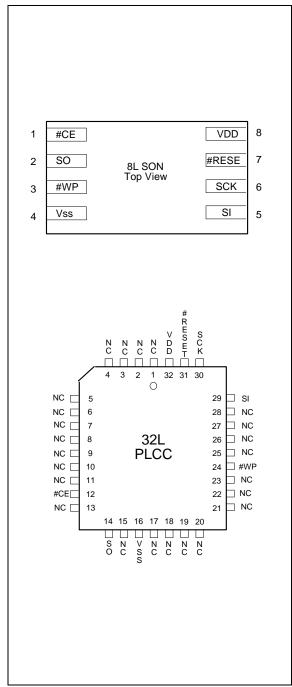

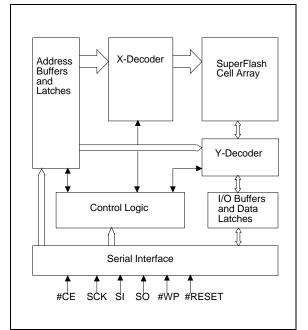

The W45B512 is manufactured with Winbonds high performance CMOS WinFlash technology. The Serial Flash is organized as 16 sectors of 4096 Bytes for the W45B512. The memory is accessed for Read or Erase/Program by the SPI bus compatible serial protocol. The bus signals are: serial data input (SI), serial data output (SO), serial clock (SCK), write protect (#WP), chip enable (#CE), and hardware reset (#RESET). This device is offered in 8L SON and 32L PLCC package.

## FEATURES

- Single 2.7 3.6V Read and Write Operations

- Serial Interface Architecture

SPI Compatible: Mode 0 and Mode 3

- Byte Serial Read with Single Command

- Superior Reliability

- Endurance: 10,000 Cycles (Typ.)

- 20 years Data Retention

- Low Power Consumption

- Active Current: 30 mA (Max.)

- Standby Current: 15 µA (Max.)

- Sector or Chip-erase Capability

- Uniform 4 KByte sectors

- Fast Erase and Byte-program

- Chip-erase Time: 100 mS (Max.)

- Sector-erase Time: 25 mS (Max.)

- Byte-program Time: 50 µS (Max.)

- Automatic Write Timing

- Internal VPP Generation

- End-of-Write Detection

- Software Status

- 20 MHz Max Clock Frequency

- Hardware Reset Pin (#RESET)

- Resets the device to Standby Mode

- TTL Compatibility

- Hardware Data Protection

- Protects/Unprotects the device from Write operation

- Packages Available

- 8L SON (5 x 6 mm), 32L PLCC

#### **PIN CONFIGURATIONS**

## **BLOCK DIAGRAM**

#### **PIN DESCRIPTION**

| SYMBOL | PIN NAME           |  |  |  |

|--------|--------------------|--|--|--|

| #CE    | Chip Enable        |  |  |  |

| SI     | Serial Data Input  |  |  |  |

| SO     | Serial Data Output |  |  |  |

| SCK    | Serial Clock       |  |  |  |

| #WP    | Write Protect      |  |  |  |

| #RESET | Reset              |  |  |  |

| Vdd    | Power Supply       |  |  |  |

| Vss    | Ground             |  |  |  |

# **PRODUCT IDENTIFICATION**

|                    | BYTE   | DATA |

|--------------------|--------|------|

| Manufacturers ID   | 0000 h | DA h |

| Device ID: W45B512 | 0001 h | 98 h |

## FUNCTIONAL DESCRIPTION

#### **Device Operation**

The W45B512 uses bus cycles of 8 bits each for commands, data, and addresses to execute operations. The operation instructions are listed in the table below. All instructions are synchronized off a high to low transition of #CE. The first low to high transition on SCK will initiate the instruction sequence. Inputs will be accepted on the rising edge of SCK starting with the most significant bit. Any low to high transition on #CE before the input instruction completes will terminate any instruction in progress and return the device to the standby mode.

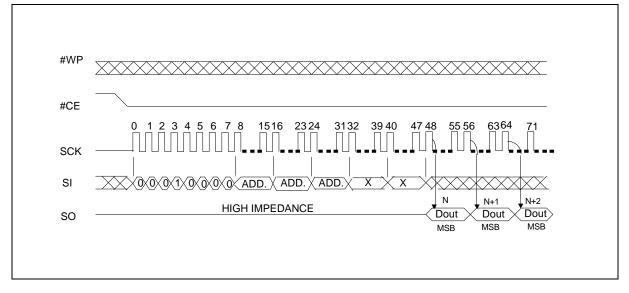

#### Read

The Read operation outputs the data in order from the initial accessed address. While SCK is input, the address will be incremented automatically until end (top) of the address space, then the internal address pointer automatically increments to beginning (bottom) of the address space (00000h), and data out stream will continue. The read data stream is continuous through all addresses until terminated by a low to high transition on #CE.

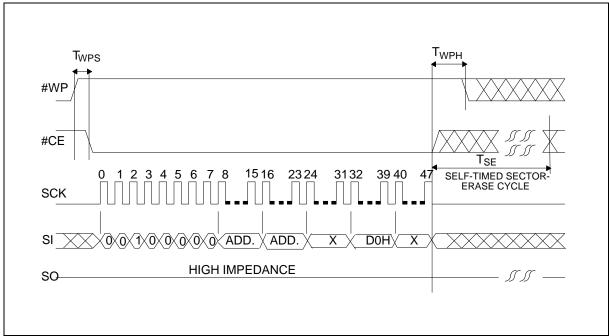

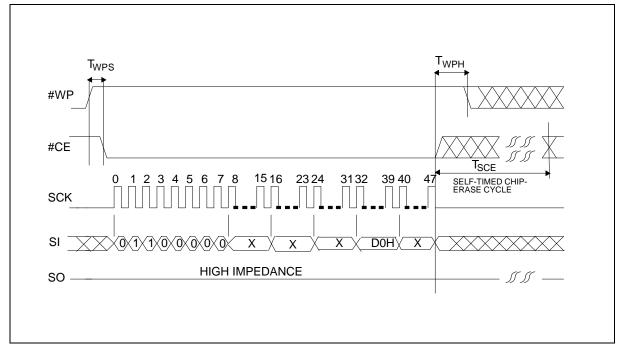

#### Sector/Chip-erase Operation

The Sector-Erase operation clears all bits in the selected sector to 'FF". The Chip -Erase instruction clears all bits in the device to 'FF".

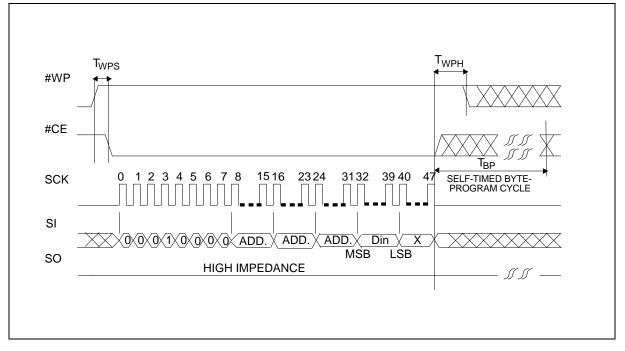

#### Byte-program Operation

The Byte-Program operation programs the bits in the selected byte to the desired data. The selected byte must be in the erased state ('FF') when initiating a Program operation. The data is input from bit 7 to bit 0 in order.

#### Software Status Operation

The Status operation determines if an Erase or Program operation is in progress. If bit 0 is at a '0' an Erase or Program operation is in progress, the device is busy. If bit 0 is at a '1' the device is ready for any valid operation. The status read is continuous with ongoing clock cycles until terminated by a low to high transition on #CE.

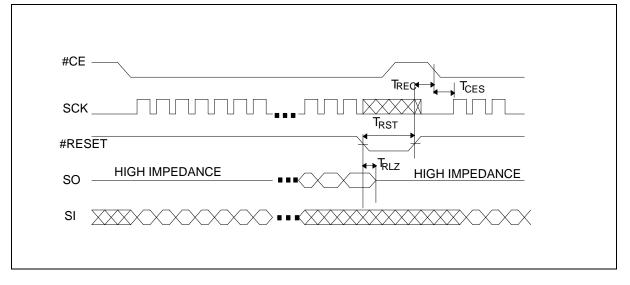

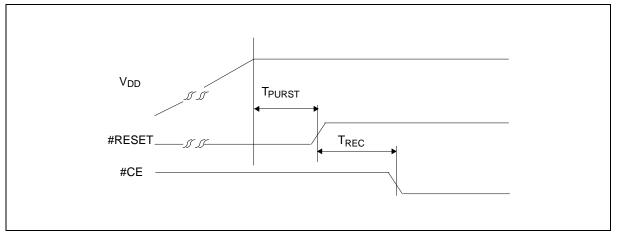

#### Reset

Reset will terminate any operation, e.g., Read, Erase and Program, in progress. It is activated by a high to low transition on the #RESET pin. The device will remain in reset condition as long as #RESET is low. Minimum reset time is 10  $\mu$ S. See Figure 14 for reset timing diagram. #RESET is internally pulled-up and could remain unconnected during normal operation. After reset, the device is in standby mode, a high to low transition on #CE is required to start the next operation. An internal power-on reset circuit protects against accidental data writes. Applying a logic level low to #RESET during the power-on process then changing to a logic level high when VDD has reached the correct voltage level will provide additional protection against accidental writes during power on.

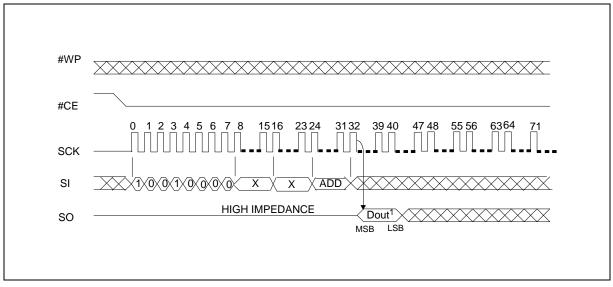

#### Read WINBOND ID/Read Device ID

The Read Manufacturer ID and Read Device ID operations read the JEDEC assigned manufacturer identification and the manufacturer assigned device identification codes. These codes may be used to determine the actual device resident in the system.

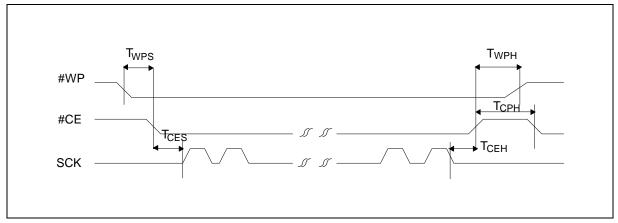

#### Write Protect

The #WP pin provides inadvertent write protection. The #WP pin must be held high for any Erase or Program operation. The #WP pin is 'dont care' for all other operations. In typical use, the #WP pin is connected to VSS with a standard pull-down resistor. #WP is then driven high whenever an Erase or Program operation is required. If the #WP pin is tied to VDD with a pull-up resistor, then all operations may occur and the write protection feature is disabled. The #WP pin has an internal pull-up and could remain unconnected when not used.

| BUS CYCLE                   | 1       | 2                    | 3        | 4       | 5    | 6     | 7    |

|-----------------------------|---------|----------------------|----------|---------|------|-------|------|

| Operation/Type              | Command | Address <sup>1</sup> | Address  | Address | Data | Dummy | Data |

| Read                        | FFh     | A23 - A16            | A15 – A8 | A7 – A0 | Х    | Х     | Dout |

| Sector-erase <sup>2</sup>   | 20h     | A23 - A16            | A15 – A8 | Х       | Dout | Х     |      |

| Chip-erase                  | 60h     | Х                    | Х        | Х       | Dout | Х     |      |

| Byte-program                | 10h     | A23 – A16            | A15 – A8 | A7 – A0 | Din  | Х     |      |

| Software-status             | 9Fh     | Dout                 |          |         |      |       |      |

| Read Manufacture ID         | 90h     | Х                    | Х        | A0 = 0  | DAh  |       |      |

| Read Device ID <sup>3</sup> | 90h     | Х                    | Х        | A0 = 1  | 98h  |       |      |

# **DEVICE OPERATION INSTRUCTION**

Notes:

1. A23 - A16 are 'Don't Care" for device.

2. A15 – A12 are used to determine sector address, A11 – A8 are don't care.

3. With A15 - A1 = 0, W45B512 Device ID = 98h, is read with A0 = 1.

# **DEVICE OPERATION TABLE**

| OPERATION           | SI  | SO   | #CE <sup>1</sup> | #WP  | #RESET |

|---------------------|-----|------|------------------|------|--------|

| Read                | Х   | Dout | Low              | Х    | High   |

| Sector-erase        | Х   | X    | Low              | High | High   |

| Chip-erase          | Х   | X    | Low              | High | High   |

| Byte-program        | Din | Х    | Low              | High | High   |

| Software-status     | Х   | Dout | Low              | Х    | High   |

| Reset <sup>2</sup>  | Х   | Х    | Х                | Х    | Low    |

| Read Manufacture ID | Х   | Dout | Low              | Х    | High   |

| Read Device ID      | Х   | Dout | Low              | Х    | High   |

Notes:

1. A high to low transition on #CE will be required to start any device operation except for Reset.

2. The #RESET low will return the device to standby and terminate any Erase or Program operation in progress.

# **DC CHARACTERISTICS**

#### **Absolute Maximum Stress Ratings**

(Applied conditions greater than those listed under "Absolute maximum Stress Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions or conditions greater than those defined in the operational sections of this data sheet is not implied. Exposure to absolute maximum stress rating conditions may affect device reliability.)

| PARAMETER                                                    | RATING           | UNIT |

|--------------------------------------------------------------|------------------|------|

| Temperature Under Bias                                       | -55 to +125      | °C   |

| Storage Temperature                                          | -65 to +150      | °C   |

| D. C. Voltage on Any Pin to Ground Potential                 | -0.5 to VDD +0.5 | V    |

| Transient Voltage (<20 nS) on Any Pin to Ground Potential    | -1.0 to VDD +1.0 | V    |

| Package Power Dissipation Capability ( $TA = 25^{\circ} C$ ) | 1.0              | W    |

| Surface Mount Lead Soldering Temperature (3 Seconds)         | 240              | °C   |

| Output Short Circuit Current 1                               | 50               | mA   |

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.

## **DC Operating Characteristics**

(VDD =2.7V - 3.6V, Vss = 0V, TA = 0 to 70  $^{\circ}$  C)

| PARAMETER            | SYM. | TEST CONDITION                   |               |      | LIMITS   |       |

|----------------------|------|----------------------------------|---------------|------|----------|-------|

|                      |      |                                  |               | MIN. | MAX.     | UNITS |

| Power Supply Current | Idd  | f = 20 MHz                       | Program/Erase | -    | 30       | mA    |

|                      |      | #CE = VIL,<br>VDD = VDD Max.     | Read          | -    | 20       | mA    |

| Standby Current      | ISB  | #CE = VIHC, VDD = VI             | -             | 15   | μΑ       |       |

| Input Leakage        | ILI  | VIN = GND to VDD, VDD = VDD Max. |               | -    | 2        | μA    |

| Output Leakage       | Ilo  | VOUT = GND to VDD,               |               | 2    | μA       |       |

| Input Low Voltage    | VIL  |                                  | -0.2          | 0.6  | V        |       |

| Input High Voltage   | Vін  |                                  |               | 2.0  | VDD +0.3 | V     |

| Output Low Voltage   | Vol  | IOL = 1.6 mA                     | -             | 0.4  | V        |       |

| Output High Voltage  | Vон  | Юн = -0.4 mA                     |               | 2.4  | -        | V     |

Note: Outputs shorted for no more than one second. No more than one output shorted at a time.

# CAPACITANCE

$(VDD = 2.7V \sim 3.6V, TA = 25^{\circ} C, f = 1 MHz)$

| PARAMETER              | SYMBOL            | CONDITIONS | MAX. | UNIT |

|------------------------|-------------------|------------|------|------|

| Output Pin Capacitance | COUT <sup>1</sup> | VDQ = 0V   | 12   | pF   |

| Input Pin Capacitance  | CIN <sup>1</sup>  | VIN = 0V   | 6    | pF   |

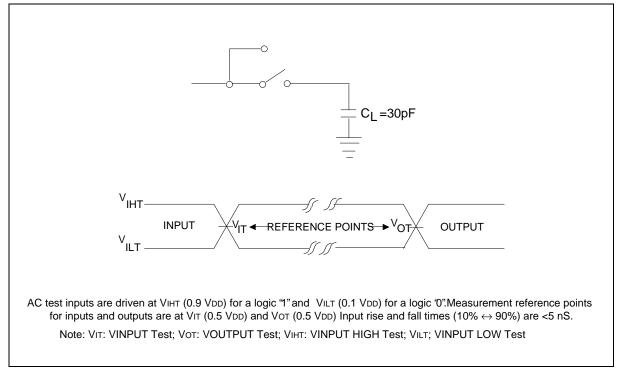

# **AC CHARACTERISTICS**

#### **AC Test Conditions**

$(VDD = 2.7V \sim 3.6V)$

| PARAMETER                 | CONDITIONS        |

|---------------------------|-------------------|

| Input Rise/Fall Time      | <5 nS             |

| Input/Output Timing Level | 0.5 VDD / 0.5 VDD |

| Output Load               | CL = 30 pF        |

## AC Test Load and Waveform

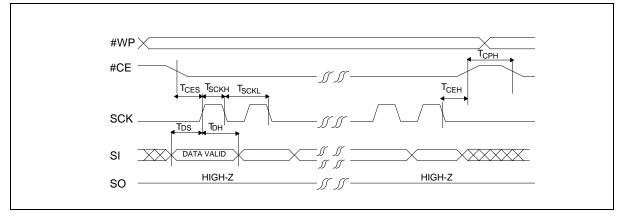

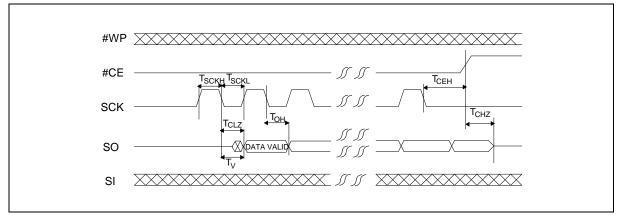

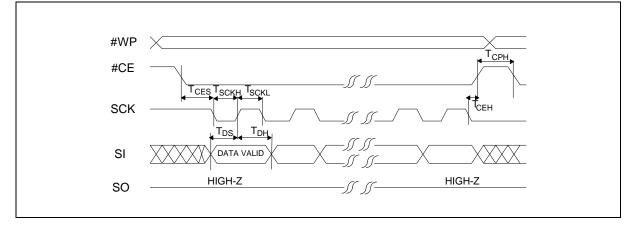

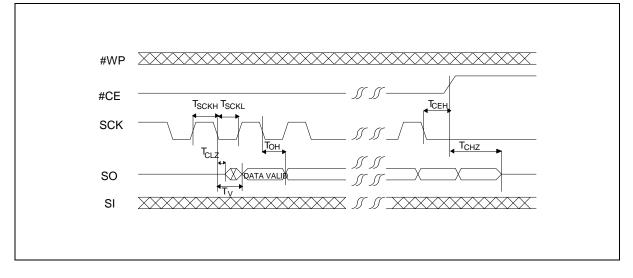

# **AC Operating Characteristics**

(VDD = 2.7V ~ 3.6V)

| PARAMETER                   | SYMBOL | LIMITS |      |       |

|-----------------------------|--------|--------|------|-------|

|                             |        | MIN.   | MAX. | UNITS |

| Serial Clock Frequency      | FCLK   |        | 20   | MHz   |

| Serial Clock High Time      | Тѕскн  | 22     | -    | nS    |

| Serial Clock Low Time       | TSCKL  | 22     | -    | nS    |

| #CE Setup Time              | TCES   | 10     | -    | nS    |

| #CE Hold Time               | Тсен   | 10     | -    | nS    |

| #CE High Time               | Тсрн   | 50     | -    | nS    |

| #CE High to High-Z Output   | Тснг   | -      | 20   | nS    |

| #CE Low to Low-Z Output     | Tclz   | 0      | -    | nS    |

| #RESET Low to High-Z Output | Trlz   | -      | 20   | nS    |

| Data In Setup Time          | TDS    | 5      | -    | nS    |

| Data In Hold Time           | Трн    | 5      | -    | nS    |

| Output Hold from SCK Change | Тон    | 0      | -    | nS    |

| Output Valid from SCK       | Τv     | -      | 25   | nS    |

| Write Protect Setup Time    | Twps   | 10     | -    | nS    |

| Write Protect Hold Time     | Тwрн   | 10     | -    | nS    |

| Sector-erase                | TSE    | -      | 25   | mS    |

| Chip-erase                  | TSCE   | -      | 100  | mS    |

| Byte-program                | Твр    | -      | 50   | μS    |

| Reset Pulse Width           | Trst   | 10     | -    | μS    |

| Reset Recovery Time         | TREC   | -      | 1    | μS    |

| Reset Time After Power-up   | TPURST | 10     | -    | μS    |

# TIMING WAVEFORMS

# Serial Input Timing Diagram (Inactive Serial Clock Low - Mode 0)

## Serial Output Timing Diagram (Inactive Serial Clock Low - Mode 0)

## Serial Input Timing Diagram (Inactive Serial Clock High - Mode 3)

# Serial Output Timing Diagram (Inactive Serial Clock High - Mode 3)

# Sector-erase Timing Diagram

# Chip-erase Timing Diagram

# Byte-program Timing Diagram

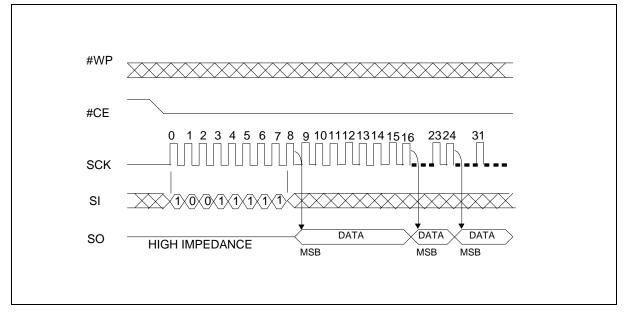

## **Read Timing Diagram**

# Read-Id Timing Diagram

- 11 -

Note: 1. Manufacturer's ID = DAh is read with A 0 = 0 Device ID = 98h is read with A 0 = 1

# Software-Status Timing Diagram

## Reset Timing Diagram (Inactive Clock Polarity Low Shown)

# Power-on Reset Timing Diagram

# Write Protect Timing Diagram

# **ORDERING INFORMATION**

| PART NO. | OPERATING<br>VOLTAGE<br>(V) | POWER<br>SUPPLY<br>CURRENT<br>MAX. (mA) | STANDBY<br>Vdd<br>CURRENT<br>MAX. (111A) | PACKAGE           | CYCLING | OPERATING<br>TEMP.<br>(°C) |

|----------|-----------------------------|-----------------------------------------|------------------------------------------|-------------------|---------|----------------------------|

| W45B512Z | 2.7V – 3.6V                 | 30                                      | 15                                       | 8L SON (5 x 6 mm) | 10K     | 0°C – 70°C                 |

| W45B512P | 2.7V - 3.6V                 | 30                                      | 15                                       | 32L PLCC          | 10K     | 0°C – 70°C                 |

Notes:

1. Winbond reserves the right to make changes to its products without prior notice.

2. Purchasers are responsible for performing appropriate quality assurance testing on products intended for use in applications where personal injury might occur as a consequence of product failure.

# HOW TO READ THE TOP MARKING

Example: The top marking of 32L-PLCC W45B512

1<sup>st</sup> line: winbond logo

2<sup>nd</sup> line: the part number: W45B512Z

- 3<sup>rd</sup> line: the lot number

- $4^{th}$  line: the tracking code: <u>149 O B SA</u>

149: Packages made in 01, week 49

O: Assembly house ID: A means ASE, O means OSE, ... etc.

B: IC revision; A means version A, H means version H, ... etc.

SA: Process code

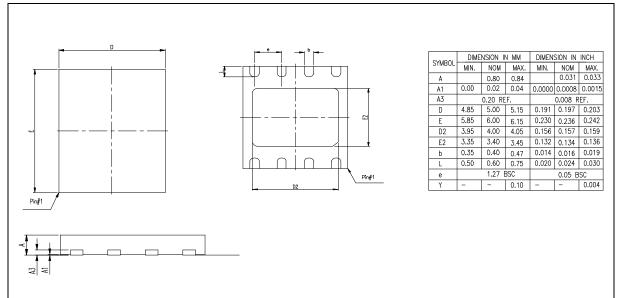

# PACKAGE DIMENSIONS

# 8L SON (5 x 6 mm)

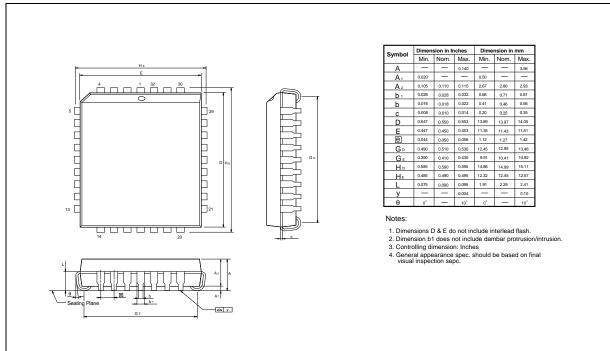

32L PLCC

#### **VERSION HISTORY**

| VERSION | DATE          | PAGE | DESCRIPTION    |

|---------|---------------|------|----------------|

| A1      | Feb. 21, 2002 | -    | Initial Issued |

**Headquarters** No. 4, Creation Rd. III, Science-Based Industrial Park, Hsinchu, Taiwan TEL: 886-3-5770066 FAX: 886-3-5665577 http://www.winbond.com.tw/

Taipei Office 9F, No.480, Rueiguang Rd., Neihu Chiu, Taipei, 114, Taiwan, R.O.C. TEL: 886-2-8177-7168 FAX: 886-2-8751-3579

Winbond Electronics Corporation America 2727 North First Street, San Jose, CA 95134, U.S.A. TEL: 1-408-9436666 FAX: 1-408-5441798

Winbond Electronics Corporation Japan 7F Daini-ueno BLDG, 3-7-18 Shinyokohama Kohoku-ku, Yokohama, 222-0033 TEL: 81-45-4781881 FAX: 81-45-4781800

Winbond Electronics (Shanghai) Ltd. 27F, 2299 Yan An W. Rd. Shanghai, 200336 China TEL: 86-21-62365999 FAX: 86-21-62365998

Winbond Electronics (H.K.) Ltd. Unit 9-15, 22F, Millennium City, No. 378 Kwun Tong Rd., Kowloon, Hong Kong TEL: 852-27513100 FAX: 852-27552064

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.