## **VIDEO AMPLIFIER WITH DC RESTORATION**

#### **DEVICE DESCRIPTION**

The ZXFV4089 is a DC restored video amplifier (black-level clamp) in an 8pin SOIC package. It integrates a high performance video amplifier with a nulling sample and hold amplifier specially designed to provide brightness level stability.

The input video signal is AC coupled to the main amplifier and this AC coupling capacitor also acts as the holding capacitor for the sample and hold amplifier. This configuration reduces both pin count and external components over traditional solutions.

Typically, during the back-porch interval of an analog video waveform the sample and hold amplifier forces the input of the video amplifier to the reference voltage. The video waveform is now referenced to the new reference voltage for the remainder of the line-scan interval.

The video amplifier has been optimised for video applications and as such drives back-terminated 75 Ω loads with good differential gain and phase errors. The current feedback architecture allows the bandwidth to remain fixed over a wide range of gains, and is set by two external resistors.

The ZXFV4089 is specified for operation at  $\pm$ 5V and over the -40°C to +85°C temperature range and is pin compatible with the industry standard EL4089.

#### **ORDERING INFORMATION**

| Part Number  | Container | Increment | Part mark |

|--------------|-----------|-----------|-----------|

| ZXFV4089N8TA | Reel 7"   | 500       | ZXFV4089  |

| ZXFV4089N8TC | Reel 13"  | 2500      | ZXFV4089  |

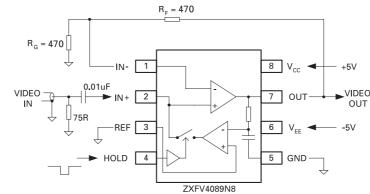

### **CONNECTION DIAGRAM**

#### FEATURES AND BENEFITS

- Complete analog video dc level restoration system

- Supports various TV systems

- PAL, NTSC, SECAM

- Excellent video performance

- 0.08% differential gain

- 0.1° differential phase

- 30 MHz 0.1 dB bandwidth

- 210 MHz -3 dB bandwidth

- 400V/μs slewrate

- TTL/CMOS logic compatible HOLD input

- Pin and function compatible with industry standard EL4089

### **APPLICATIONS**

- Black Level Clamp, providing stable intensity in video systems such as:

- cameras

- image capture

- video mixing

- displays

- DC restoration of other high frequency signals

ABSOLUTE MAXIMUM RATINGS - Over operating free-air temperature (unless otherwise stated)<sup>1</sup>

| Positive supply voltage V <sub>CC</sub> to GND | -0.5V to +5.5V         |

|------------------------------------------------|------------------------|

| Negative supply Voltage VEE to GND             | -5.5V to +0.5V         |

| Input voltage, pins 1,2,3 to GND               | VEE -0.5V to VCC +0.5V |

| Differential Input Voltage2, pin 1 to pin 2    | ±3 V                   |

| Output current, pin 7 (continuous, TJ < 110°C) | ±60 mA                 |

| Internal power dissipation                     | See note 3             |

| Input current, IN- pin 1                       | ±5 mA                  |

| Current into IN+ and HOLD, pins 2 and 4        | ±5 mA                  |

| Operating ambient temperature range            | -40°C to 85°C          |

| Storage temperature range                      | -65°C to 150°C         |

| Operating junction temperature TJMAX           | 150°C                  |

Notes:

- Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. At high closed loop gains and low gain setting resistors care must be taken if large input signals are applied to the device which cause the output stage to saturate for extended periods of time.

- 3. The power dissipation of the device when loaded must be designed to keep the device junction temperature below TJMAX, de-rated according to the Theta-ja for the SO8 package, which is typically 168°C/W, i.e. 0.74W at 25°C.

- \* During power-up and power-down, these voltage ratings require that signals be applied only when the power supply is connected.

ESD: This device is sensitive to static discharge and proper handling precautions are required.

## **ELECTRICAL CHARACTERISTICS**

$V_{CC} = 5V$ ,  $V_{EE} = -5V$ , G = 1,  $R_F = 1k\Omega$ ,  $R_{LOAD} = 1k\Omega$ , Tamb = 25°C unless otherwise stated.

| PARAME           | TER                                                                          | CONDITIONS                                     | MIN   | ТҮР  | MAX | UNIT |

|------------------|------------------------------------------------------------------------------|------------------------------------------------|-------|------|-----|------|

| I <sub>ссн</sub> | Positive supply current, holding                                             | HOLD = HIGH                                    | 5     | 8    | 10  | mA   |

| I <sub>ccs</sub> | Positive supply current, sampling                                            | HOLD = LOW                                     | 5     | 8.5  | 11  | mA   |

| I <sub>EEH</sub> | Negative supply current, holding                                             | HOLD = HIGH                                    | 5     | 8    | 10  | mA   |

| I <sub>EES</sub> | Negative supply current, sampling                                            | HOLD = LOW                                     | 5     | 8.5  | 11  | mA   |

| Amplifie         | r section, Hold Input = High unless other                                    | wise stated                                    | •     |      |     |      |

| Vos              | Input offset voltage                                                         |                                                |       | 1    | 10  | mV   |

| I <sub>B+</sub>  | + input bias current                                                         | $V_{IN+} = 0V$                                 |       | 1    | 5   | μA   |

| I <sub>B-</sub>  | – input bias current                                                         |                                                |       | 1    | 10  | μA   |

| R <sub>OL</sub>  | Trans-impedance                                                              | $V_{IN+} = \pm 3V$                             |       | 1800 |     | kΩ   |

| R <sub>IN+</sub> | + input resistance                                                           |                                                | 1     | 2    |     | MΩ   |

| Vo               | Output voltage swing                                                         | $V_{IN+} = \pm 3V, I_{OUT} = \mp 40 \text{mA}$ | ±2.95 | ±3.0 |     | V    |

| Ι <sub>Ο</sub>   | Output drive current                                                         |                                                | 40    |      |     | mA   |

| +PSRR            | Positive power supply rejection ratio                                        | $V_{CC} = 5V \pm 5\%$ , $V_{EE} = -5V$         | 49    | 57   |     | dB   |

| -PSRR            | Negative power supply rejection ratio                                        | $V_{CC} = 5V, V_{EE} = -5V \pm 5\%$            | 51    | 58   |     | dB   |

| V <sub>CMR</sub> | Common mode input voltage range <sup>(1)</sup>                               |                                                | ±3    |      |     | V    |

| CMRR             | Common mode rejection ratio                                                  | $V_{IN} = \pm 3V$                              | 48    | 57   |     | dB   |

| Restore          | section, HOLD = Low unless otherwise st                                      | ated                                           |       | •    |     |      |

| VOSCOMP          | Composite input offset voltage, from V <sub>REF</sub><br>to amplifier output | V <sub>REF</sub> = 0V                          |       | 0.3  | 7   | mV   |

| I <sub>REF</sub> | V <sub>REF</sub> input bias current                                          | $V_{REF} = 0V$                                 |       | 3    | 12  | μA   |

| I <sub>OUT</sub> | Input restore current available, pin 2                                       |                                                | 180   | 300  | 600 | μA   |

|                  | V <sub>REF</sub> input voltage range                                         |                                                | ±2    |      |     | V    |

| CMRR             | Common mode rejection ratio                                                  | $V_{\text{REF}} = \pm 2V$                      | 54    | 90   |     | dB   |

| +PSRR            | Positive power supply rejection ratio                                        | $V_{CC} = 5V \pm 5\%$ , $V_{EE} = -5V$         | 50    | 60   |     | dB   |

| -PSRR            | Negative power supply rejection ratio                                        | $V_{CC} = 5V, V_{EE} = -5V \pm 5\%$            | 50    | 60   |     | dB   |

| $V_{Hmin}$       | HOLD pin high logic level                                                    |                                                | 2     |      |     | V    |

| $V_{Lmax}$       | HOLD pin low logic level                                                     |                                                |       |      | 0.8 | V    |

| $I_{\rm IL}$     | Logic low input current                                                      | HOLD = LOW                                     |       | 40   | 100 | μA   |

| IIH              | Logic high input current                                                     | HOLD = HIGH                                    |       | 12   |     | μA   |

NOTES:

1. The voltage at the input to pin 2 should be limited to +2.7V for the best DC restoration accuracy. See later explanation under "Common-mode input range."

## **AC ELECTRICAL CHARACTERISTICS**

$V_{CC}=5V,\,V_{EE}=-5V,\,R_F=470\Omega,\,G=2,\,R_{LOAD}=150\Omega,\,C_{LOAD}=10\,\,pF,\,T_{AMB}=25^{\circ}C\,\,unless\,\,otherwise\,\,stated.$

| PARAMETER                                             |                              | CONDITIONS                                      | MIN | ТҮР  | MAX | UNIT |  |  |

|-------------------------------------------------------|------------------------------|-------------------------------------------------|-----|------|-----|------|--|--|

| Amplifier section HOLD = high unless otherwise stated |                              |                                                 |     |      |     |      |  |  |

| SR                                                    | Slew Rate                    | V <sub>OUT</sub> = 2V <sub>PP</sub>             |     | 400  |     | V/µs |  |  |

| BW <sub>-3</sub>                                      | Bandwidth, -3dB              | $V_{OUT} = 0.2V_{PP}, G = 2$                    |     | 210  |     | MHz  |  |  |

| BW <sub>-3</sub>                                      | Bandwidth, -3dB              | $V_{OUT} = 0.2V_{PP}, G = 1, R_{f} = 820\Omega$ |     | 210  |     | MHz  |  |  |

| BW <sub>0.1</sub>                                     | Bandwidth, ±0.1dB            | $V_{OUT} = 0.2V_{PP}$                           |     | 30   |     | MHz  |  |  |

| dG                                                    | Differential gain, NTSC      | f = 3.58 MHz, V <sub>IN</sub> = 280mV pk-pk,    |     | 0.08 |     | %    |  |  |

| dP                                                    | Differential phase, NTSC     | DC = -714 to +714 mV                            |     | 0.1  |     | deg  |  |  |

| Restore                                               | section HOLD = low unless of | therwise stated                                 |     |      |     |      |  |  |

| SR                                                    | Slew rate                    | $V_{OUT} = 2V_{PP}, C_{HOLD} = 0.01 \mu F^*$    |     | 25   |     | V/µs |  |  |

| t <sub>ENH</sub>                                      | Time to enable hold          |                                                 |     | 25   |     | ns   |  |  |

| t <sub>DISH</sub>                                     | Time to disable hold         |                                                 |     | 40   |     | ns   |  |  |

\* Slew rate is dependent on the ac coupling hold capacitor connected to pin 2.

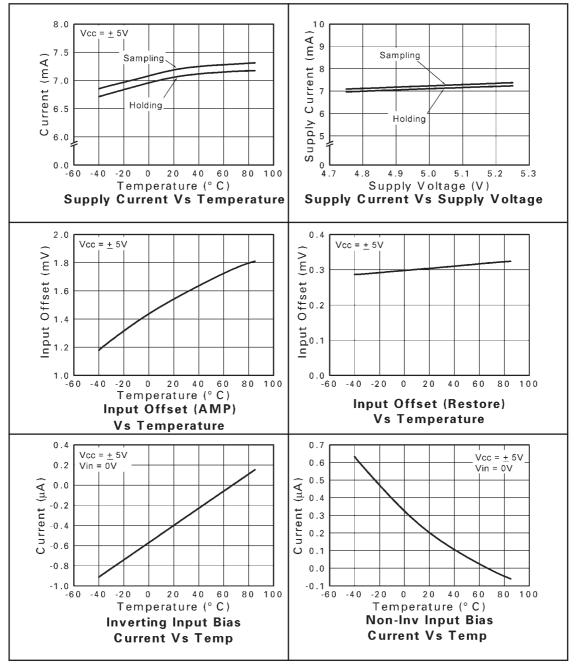

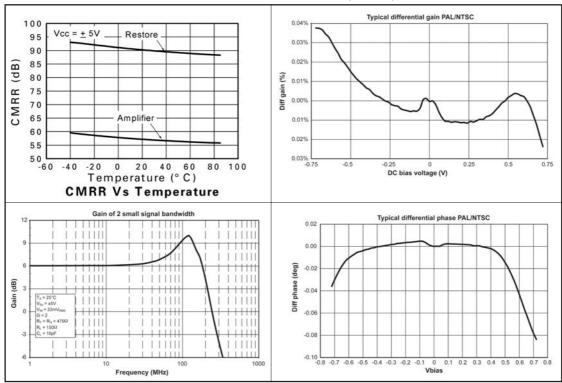

### **TYPICAL CHARACTERISTICS**

## **TYPICAL CHARACTERISTICS (CONT.)**

## **ZXFV4089 DETAILED OPERATING NOTES**

#### Introduction

This device provides an uncommitted video feed-back amplifier together with a sample-hold system to allow restoration or level-shifting of the input waveform to a controlled DC level.

The Connection Diagram, Figure 1 (page 1) shows a typical video signal application. No output termination is shown in the diagram, but if desired the output can drive a 75  $\Omega$  cable via a 75  $\Omega$  series terminating resistor.

#### **Amplifier configuration**

The main amplifier uses current feedback in a non-inverting configuration. Two external resistors are required to set the gain.

An external reference, VREF, normally ground, is used to set the new DC level of the video signal. The input video signal is applied via an external input AC coupling capacitor, which is used to store a DC control level when the sample-hold switch is open. Typically an external sampling pulse (active low) is applied to the HOLD input. During this pulse, the sample-hold switch is closed. This completes the DC feedback loop and the stored level is driven towards a new value. At the end of the sampling pulse, the switch opens again and the DC level remains close to the new established value until the next sample pulse. The sample-hold charging current is limited to 300  $\mu$ A. Therefore the convergence towards the steady condition is typically slow, but after several HOLD pulse cycles, the DC level settles closely to the Reference level at the VREF input.

The sample-hold loop contains the video amplifier within its path, and also includes an additional sample-hold sense amplifier that compares  $V_{\text{REF}}$  with the output voltage using an internal low-pass filter. In the high state, the switch is open and the average DC level remains fixed apart from a small drift due to the input bias current of the amplifier and switch leakage (see below).

#### **DC** restoration

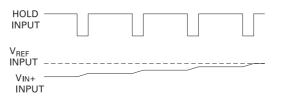

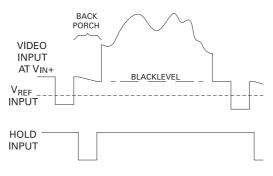

The HOLD input is a TTL compatible signal that is buffered and controls the sample-hold switch. A logic LOW state closes the switch and so enables the feedback control loop to set the output level equal to VREF (usually ground). The level of DC shift is maintained when the logic control returns to the HIGH state and the switch opens. In this way the whole waveform is conditionally level shifted, or 'restored' to the new DC level. Figure 2 shows the response of the circuit to a stationary or very slowly varying waveform with an initial voltage offset difference between V+ and VREF, applied to the input coupling capacitor, when the HOLD input is cycled with a repetitive pulse waveform. When the HOLD input is at a logic LOW level, the signal input V+ is driven towards VREF. After a number of cycles, the waveform settles to the DC stabilised value. The waveform is unaffected during the logic HIGH interval of the HOLD input.

#### Figure 2: RESPONSE TO SLOW INPUT SIGNAL

Figure 3 shows a portion of a typical video waveform, where the sample pulse is synchronised to fall within the back porch interval. This can for example be achieved using the Zetex ZXFV4583 Sync Separator to derive the pulse as in the Evaluation Circuit described in the data sheet for that part. Again, during the logic LOW period of the HOLD input, the waveform is driven towards VREF. Eventually, after a few line scans, the video waveform is stabilised with the back porch level equal to VREF and this condition is maintained despite any small changes in the input waveform.

#### Figure 3: RESPONSE TO TYPICAL VIDEO SIGNAL

In the video application, the HOLD input state will be HIGH during the picture line sweep and a negative-going sampling pulse of typically 1.2 µs duration will be applied during a central portion of the Back Porch interval, so that the Back Porch or 'Black' level is clamped to VREF (typically ground).

If desired, by changing the external pulse timing the signal may be restored such that the sync tip voltage is clamped to V<sub>REF</sub> instead of the back porch.

In either case, for each line scan, this gives a brightness level consistent with that of the original camera signal, despite the AC coupling. The value of the coupling capacitor affects two main characteristics of the circuit:

- 1. DC level acquisition change

- 2. DC Level droop

#### **DC Level Acquisition change**

In the restore mode the available charging current, together with the capacitor value, determines the maximum DC voltage correction which can be applied at each sample. For a charging current limit of  $300 \,\mu\text{A}$  applied for 1.2  $\mu$ s, the charge injected is:

Qmax = 300 µA x 1.2 µs = 360 pC

Then the maximum voltage shift correction is:

$Vmax = Qmax/C = 360 \text{ pC} / 0.01 \mu\text{F}$

= 36 mV

#### **DC Level Droop**

In the hold state, a small voltage drift is caused by leakage from the **Sample-hold** circuit and bias current from the main amplifier charging or discharging the coupling capacitor.

The drift rate is equal to the bias/leakage current of up to about 1  $\mu$ A divided by the coupling capacitor value. For a coupling capacitor of 0.01  $\mu$ F the drift rate is then up to ±100  $\mu$ V/ $\mu$ s.

For a typical video line scan the switch remains open for the rest of the scan duration, or about  $62 \ \mu s$ . The drift at the end of the line scan has therefore accumulated to about  $6.2 \ mV$ .

This is acceptable for most applications, but if desired it can be reduced by increasing the value of the coupling capacitor. This will result in a proportionately smaller value of the maximum available correction voltage at each scan as described above. Normally, once settled, the video system requires only a very small correction at each scan, so this will not present any problem.

#### Supply filtering & printed circuit layout

In the applied circuit, the power filtering and printed layout design needs special attention as is appropriate for a high-speed analog circuit. For each supply lead, use a leadless ceramic chip capacitor placed very close to the device power pin. A value of 0.1µF is recommended. In addition, a larger value capacitor, which should be ceramic or solid tantalum construction, with a value of 1 to 10 µF, is also recommended for connection to each supply fairly close to the device. The layout naturally requires some short interconnections on the component side (top copper layer) and a continuous ground plane should be provided on another layer with plated via holes providing low inductance ground connections for the device and other components. The amplifier frequency response is affected to some extent by stray capacitance at the inverting input at pin 1. This effect can be minimised by providing a small cut-out area in the ground plane and other layers around pin 1, though this may not always be necessary for the application.

#### **Further Applications Information**

The ZXFV4089 is a high speed device requiring the appropriate care in the layout of the application printed circuit board. A continuous ground plane construction is preferred. Suitable power supply decoupling suggested includes a 100nF leadless ceramic capacitor close to the power supply connections at pin 8 and pin 6.

As stated earlier the main video amplifier of the ZXFV4089 is a current feedback amplifier. Compared to a voltage-feedback amplifier, current feedback provides better bandwidths at higher gains and also much faster slew rates. To optimise performance from a current feedback amplifier choice of feedback resistor is very important. In this case, typically the device will be used with a voltage gain of two, using two resistors of 1kΩ as in Figure 1. Stray capacitance at the inverting input node of this circuit can affect frequency and pulse response, so the printed circuit layout should take account of this. Place the feedback resistors as close as possible to the inverting input pin and minimise the printed metal connected to this pin.

#### Common-mode input range

The signal input voltage range is determined partly by the common-mode input range of the main amplifier. The amplifier configuration is non-inverting, and so the inverting input will follow the signal input voltage. It is also necessary to observe the maximum limit on the value of VREF ( $\pm 2V$ ) which is less than the amplifier input voltage range. Therefore the input range of the system is limited to this value. In addition the restore amplifier voltage input range is restricted to a similar value.

Attention is drawn to the footnote of the DC Electrical Characteristics Table, regarding input signal amplitude. The video signal is ac coupled into the main amplifier and clamped to VREF. As a result of this the actual voltage seen by the device input at pin 2 is the sum of VREF plus the video input signal voltage excursion above VREF (when clamping the back porch, this excursion is normally the luminance waveform of up to about 0.72V white level). At a particular positive value at pin 2 close to 2.7V, the leakage current of the Sample-hold switch increases causing an increase in the droop rate. Therefore, for example, a reference voltage of 2V with a peak white video signal of 0.7V peak voltage the DC restoration accuracy could be affected and care should be taken in this respect. When using 0.7V luminance, this is consistent with the maximum recommended reference voltage of +2V.

#### **Evaluation Circuit**

An evaluation circuit is available to allow demonstration of the video black-level clamping function. The circuit uses the Zetex ZXFV4583 Sync Separator circuit to provide the HOLD function timing signal. This circuit is described in the data sheet for ZXFV4583. To order the evaluation board, ask for ZXFV4583EV.

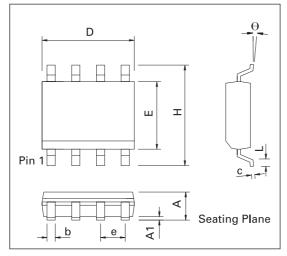

## **PACKAGE OUTLINE**

Controlling dimensions are in millimeters. Approximate conversions are given in inches

### PACKAGE DIMENSIONS

| DIM | Millin | neters | Inc  | hes  | DIM | Millimeters |       | Inches |      |

|-----|--------|--------|------|------|-----|-------------|-------|--------|------|

|     | Min    | Мах    | Min  | Мах  |     | Min         | Мах   | Min    | Max  |

| А   | 0.053  | 0.069  | 1.35 | 1.75 | е   | 0.050       | BSC   | 1.27   | BSC  |

| A1  | 0.004  | 0.010  | 0.10 | 0.25 | b   | 0.013       | 0.020 | 0.33   | 0.51 |

| D   | 0.189  | 0.197  | 4.80 | 5.00 | с   | 0.008       | 0.010 | 0.19   | 0.25 |

| н   | 0.228  | 0.244  | 5.80 | 6.20 | θ   | 0°          | 8°    | 0°     | 8°   |

| E   | 0.150  | 0.157  | 3.80 | 4.00 | h   | 0.010       | 0.020 | 0.25   | 0.50 |

| L   | 0.016  | 0.050  | 0.40 | 1.27 | -   | -           | -     | -      | -    |

#### © Zetex Semiconductors plc 2005

| Europe                      | Americas                    | Asia Pacific                | Corporate Headquarters      |

|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| Zetex GmbH                  | Zetex Inc                   | Zetex (Asia) Ltd            | Zetex Semiconductors plc    |

| Streitfeldstraße 19         | 700 Veterans Memorial Hwy   | 3701-04 Metroplaza Tower 1  | Zetex Technology Park       |

| D-81673 München             | Hauppauge, NY 11788         | Hing Fong Road, Kwai Fong   | Chadderton, Oldham, OL9 9LL |

| Germany                     | USA                         | Hong Kong                   | United Kingdom              |

| Telefon: (49) 89 45 49 49 0 | Telephone: (1) 631 360 2222 | Telephone: (852) 26100 611  | Telephone (44) 161 622 4444 |

| Fax: (49) 89 45 49 49 49    | Fax: (1) 631 360 8222       | Fax: (852) 24250 494        | Fax: (44) 161 622 4446      |

| europe.sales@zetex.com      | usa.sales@zetex.com         | <u>asia.sales@zetex.com</u> | hq@zetex.com                |

These offices are supported by agents and distributors in major countries world-wide.

This publication is issued to provide outline information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned. The Company reserves the right to alter without notice the specification, design, price or conditions of supply of any product or service.

For the latest product information, log on to www.zetex.com